Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                        |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | CANbus, SCI, UART/USART                                                       |

| Peripherals                | POR, WDT                                                                      |

| Number of I/O              | 36                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | Mask ROM                                                                      |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x8/10b                                                                   |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-LQFP                                                                       |

| Supplier Device Package    | 48-LQFP (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-gs-245 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 10. I/O Map

| Address                  | Register<br>Abbreviation | Register                                                    | Read/<br>Write | Resource                  | Initial Value |

|--------------------------|--------------------------|-------------------------------------------------------------|----------------|---------------------------|---------------|

| 00000н                   |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000001н                  | PDR1                     | Port 1 data register                                        | R/W            | Port 1                    | XXXXXXXXB     |

| 000002н                  | PDR2                     | Port 2 data register                                        | R/W            | Port 2                    | XXXXXXXXB     |

| 00003н                   | PDR3                     | Port 3 data register                                        | R/W            | Port 3                    | XXXXXXXXB     |

| 000004н                  | PDR4                     | Port 4 data register                                        | R/W            | Port 4                    | XXXXXXXXB     |

| 000005н                  | PDR5                     | Port 5 data register                                        | R/W            | Port 5                    | XXXXXXXXB     |

| 000006н<br>to<br>000010н |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000011н                  | DDR1                     | Port 1 direction data register                              | R/W            | Port 1                    | 0000000в      |

| 000012н                  | DDR2                     | Port 2 direction data register                              | R/W            | Port 2                    | 0000000в      |

| 000013н                  | DDR3                     | Port 3 direction data register                              | R/W            | Port 3                    | 000Х0000в     |

| 000014н                  | DDR4                     | Port 4 direction data register                              | R/W            | Port 4                    | ХХХ00000в     |

| 000015н                  | DDR5                     | Port 5 direction data register                              | R/W            | Port 5                    | 0000000в      |

| 000016н<br>to<br>00001Ан |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00001Bн                  | ADER                     | Analog input permission register                            | R/W            | 8/10-bit A/D<br>converter | 11111111в     |

| 00001Cнto<br>000025н     |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000026н                  | SMR1                     | Serial mode register 1                                      | R/W            | UART1                     | 0000000в      |

| 000027н                  | SCR1                     | Serial control register 1                                   | R/W, W         |                           | 00000100в     |

| 000028н                  | SIDR1/<br>SODR1          | Serial input data register 1/ Serial output data register 1 | R, W           |                           | XXXXXXXXB     |

| 000029н                  | SSR1                     | Serial status data register 1                               | R, R/W         |                           | 00001000в     |

| 00002Ан                  |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00002Вн                  | CDCR1                    | Communication prescaler control register 1                  | R/W            | UART1                     | 0ХХХ0000в     |

| 00002Cнto<br>00002Fн     |                          | (Reserve                                                    | ed area) *     |                           | ·             |

| 000030н                  | ENIR                     | DTP/External interrupt permission register                  | R/W            | DTP/External<br>interrupt | 0000000в      |

| 000031н                  | EIRR                     | DTP/External interrupt permission register                  | R/W            |                           | XXXXXXXXB     |

| 000032н                  | ELVR                     | Detection level setting register                            | R/W            | 1                         | 0000000в      |

| 000033н                  |                          |                                                             | R/W            | 1                         | 0000000в      |

| 000034н                  | ADCS                     | A/D control status register                                 | R/W            | 8/10-bit A/D              | 0000000в      |

| 000035н                  |                          |                                                             | R/W, W         | converter                 | 0000000в      |

| 000036н                  | ADCR                     | A/D data register                                           | W, R           | 1                         | XXXXXXXXB     |

| 000037н                  |                          |                                                             | R              | 1                         | 00101XXXв     |

| Address                  | Register<br>Abbreviation | Register                           | Read/<br>Write | Resource       | Initial Value                                    |

|--------------------------|--------------------------|------------------------------------|----------------|----------------|--------------------------------------------------|

| 003С38н,<br>003С39н      | DLCR4                    | DLC register 4                     | R/W            | CAN controller | XXXXXXXXB,<br>XXXXXXXB                           |

| 003С3Ан,<br>003С3Вн      | DLCR5                    | DLC register 5                     | R/W            |                | XXXXXXXXB,<br>XXXXXXXB                           |

| 003C3Cн,<br>003C3Dн      | DLCR6                    | DLC register 6                     | R/W            |                | XXXXXXXXB,<br>XXXXXXXB                           |

| 003C3Eн,<br>003C3Fн      | DLCR7                    | DLC register 7                     | R/W            |                | XXXXXXXXB,<br>XXXXXXXB                           |

| 003C40н<br>to<br>003C47н | DTR0                     | Data register 0                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C48н<br>to<br>003C4Fн | DTR1                     | Data register 1                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C50н<br>to<br>003C57н | DTR2                     | Data register 2                    | R/W            | -              | XXXXXXXXB<br>to<br>XXXXXXXB                      |

| 003C58н<br>to<br>003C5Fн | DTR3                     | Data register 3                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C60н<br>to<br>003C67н | DTR4                     | Data register 4                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C68н<br>to<br>003C6Fн | DTR5                     | Data register 5                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C70н<br>to<br>003C77н | DTR6                     | Data register 6                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C78н<br>to<br>003C7Fн | DTR7                     | Data register 7                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C80н<br>to<br>003CFFн |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D00н,<br>003D01н      | CSR                      | Control status register            | R/W, R         | CAN controller | 0XXXX001в,<br>00XXX000в                          |

| 003D02н                  | LEIR                     | Last event display register        | R/W            |                | 000XX000 <sub>B</sub>                            |

| 003D03н                  |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D04н,<br>003D05н      | RTEC                     | Send/receive error counter         | R              | CAN controller | 0000000в,<br>0000000в                            |

| 003D06н,<br>003D07н      | BTR                      | Bit timing register                | R/W            |                | 11111111 <sub>в</sub> ,<br>Х1111111 <sub>в</sub> |

| 003D08н                  | IDER                     | IDE register                       | R/W            |                | XXXXXXXXB                                        |

| 003D09н                  |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D0Aн                  | TRTRR                    | Send RTR register                  | R/W            | CAN controller | 0000000в                                         |

| 003D0Bн                  |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D0CH                  | RFWTR                    | Remote frame receive wait register | R/W            | CAN controller | XXXXXXXXB                                        |

| Address                  | Register<br>Abbreviation | Register                                      | Read/<br>Write | Resource       | Initial Value                |  |  |  |

|--------------------------|--------------------------|-----------------------------------------------|----------------|----------------|------------------------------|--|--|--|

| 003D0Dн                  | (Reserved area) *        |                                               |                |                |                              |  |  |  |

| 003D0Eн                  | TIER                     | Send completion interrupt permission register | R/W            | CAN controller | 0000000в                     |  |  |  |

| 003D0Fн                  |                          | (Reserv                                       | ed area) *     | ·              |                              |  |  |  |

| 003D10н,<br>003D11н      | AMSR                     | Acceptance mask selection register            | R/W            | CAN controller | XXXXXXXXB,<br>XXXXXXXB       |  |  |  |

| 003D12н,<br>003D13н      | (Reserved area) *        |                                               |                |                |                              |  |  |  |

| 003D14н<br>to<br>003D17н | AMR0                     | Acceptance mask register 0                    | R/W            | CAN controller | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |

| 003D18н<br>to<br>003D1Bн | AMR1                     | Acceptance mask register 1                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |

| 003D1Cн<br>to<br>003DFFн | (Reserved area) *        |                                               |                |                |                              |  |  |  |

| 003E00н<br>to<br>003EFFн |                          | (Reserved area) *                             |                |                |                              |  |  |  |

| 003FF0н<br>to<br>003FFFн |                          | (Reserved area) *                             |                |                |                              |  |  |  |

Initial values:

0: Initial value of this bit is "0."

1: Initial value of this bit is "1."

X: Initial value of this bit is undefined.

\*: "Reserved area" should not be written anything. Result of reading from "Reserved area" is undefined.

| Interrupt Source                  | El <sup>2</sup> OS | Interrupt Vector |     |         | Interrupt C | Priority*3             |              |

|-----------------------------------|--------------------|------------------|-----|---------|-------------|------------------------|--------------|

| interrupt Source                  | Readiness          | Number           |     | Address | ICR         | Address                | FIOTILY      |

| UART1 reception completed         | O                  | #37              | 25н | FFFF68H | ICR13       | 0000BDH*1              | High         |

| UART1 transmission completed      | Δ                  | #38              | 26н | FFFF64⊦ |             |                        | $\uparrow$   |

| Reserved                          | ×                  | #39              | 27н | FFFF60H | ICR14       | 0000BEH*1              |              |

| Reserved                          | ×                  | #40              | 28н | FFFF5CH |             |                        |              |

| Flash memory                      | ×                  | #41              | 29н | FFFF58H | ICR15       | 0000BF <sub>H</sub> *1 | $\downarrow$ |

| Delay interrupt generation module | ×                  | #42              | 2Ан | FFFF54⊦ | <u> </u>    |                        | Low          |

○ : Available

× : Unavailable

© : Available El<sup>2</sup>OS function is provided.

$\Delta$ : Available when a cause of interrupt sharing a same ICR is not used.

\*1:

□ Peripheral functions sharing an ICR register have the same interrupt level.

□ If peripheral functions share an ICR register, only one function is available when using expanded intelligent I/O service.

If peripheral functions share an ICR register, a function using expanded intelligent I/O service does not allow interrupt by another function.

\*2: Input capture 1 corresponds to EI2OS, however, PPG does not. When using EI2OS by input capture 1, interrupt should be disabled for PPG.

\*3:Priority when two or more interrupts of a same level occur simultaneously.

## 12. Peripheral Resources

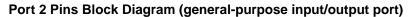

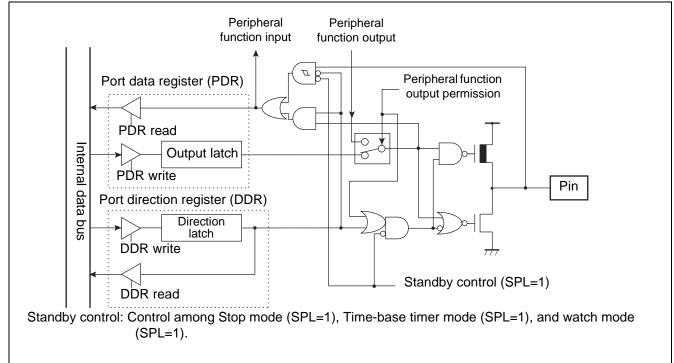

## 12.1 I/O Ports

The I/O ports are used as general-purpose input/output ports (parallel I/O ports). The MB60385 series model is provided with 5 ports (34 inputs). The ports function as input/output pins for peripheral functions also.

## I/O Port Functions

An I/O port, using port data resister (PDR), outputs the output data to I/O pin and input a signal input to I/O port. The port direction register (DDR) specifies direction of input/output of I/O pins on a bit-by-bit basis.

The following summarizes functions of the ports and sharing peripheral functions:

- Port 1: General-purpose input/output port, used also for PPG timer output and input capture inputs.

- Port 2: General-purpose input/output port, used also for reload timer input/output and external interrupt input.

- Port 3: General-purpose input/output port, used also for A/D converter activation trigger pin.

- Port 4: General-purpose input/output port, used also for UART input/output and CAN controller send/receive pin.

- Port 5: General-purpose input/output port, used also analog input pin.

## **Port 2 Registers**

- Port 2 registers include port 2 data register (PDR2) and port 2 direction register (DDR2).

- The bits configuring the register correspond to port 2 pins on a one-to-one basis.

## **Relation between Port 2 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 2    | PDR2,DDR2                               | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P27  | P26  | P25  | P24  | P23  | P22  | P21  | P20  |

## Port 4 Pins Block Diagram

## **Port 4 Registers**

- Port 4 registers include port 4 data register (PDR4) and port 4 direction register (DDR4).

- The bits configuring the register correspond to port 4 pins on a one-to-one basis.

## **Relation between Port 4 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |   |   |   |      |      |      |      |      |

|-----------|-----------------------------------------|---|---|---|------|------|------|------|------|

| Port 4    | PDR4, DDR4                              | - | - | - | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | - | - | - | P44  | P43  | P42  | P41  | P40  |

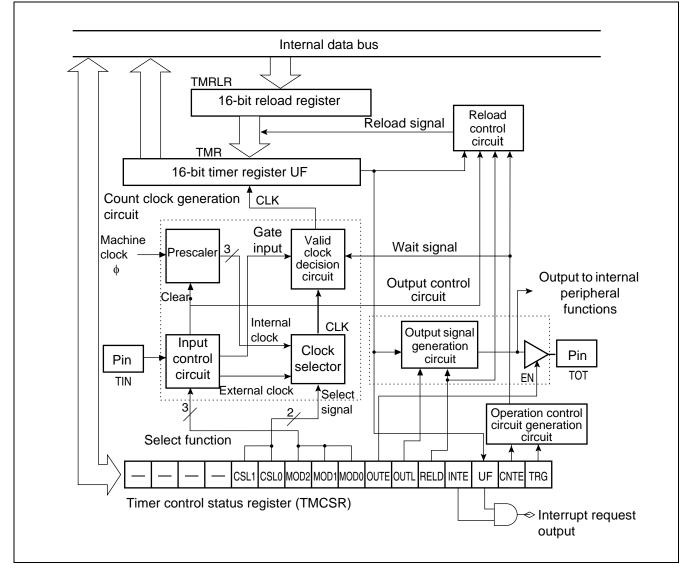

## 12.5 16-bit Reload Timer

The 16-bit reload timer has the following functions:

- Count clock is selectable among 3 internal clocks and external event clock.

- Activation trigger is selectable between software trigger and external trigger.

- Generation of CPU interrupt is allowed upon occurrence of underflow on 16-bit timer register. Available as an interval timer using the interrupt function.

- When underflow of 16-bit timer register (TMR) occurs, one of two reload modes is selectable between one-shot mode that halts counting operation of TMR, and reload mode that reloads 16-bit reload register value to TMR, continuing TMR counting operation.

- The 16-bit reload timer is ready for expanded intelligent I/O service (El<sup>2</sup>OS).

- MB90385 series device has 2 channels of built-in 16-bit reload timer.

## **Operation Mode of 16-bit Reload Timer**

| Count Clock         | Activation Trigger                 | Operation upon Underflow   |

|---------------------|------------------------------------|----------------------------|

| Internal clock mode | Software trigger, external trigger | One-shot mode, reload mode |

| Event count mode    | Software trigger                   | One-shot mode, reload mode |

## Internal Clock Mode

- The 16-bit reload timer is set to internal clock mode, by setting count clock selection bit (TMCSR: CSL1, CSL0) to "00<sub>B</sub>", "01<sub>B</sub>", "10<sub>B</sub>".

- In the internal clock mode, the counter decrements in synchronization with the internal clock.

- Three types of count clock cycles are selectable by count clock selection bit (TMCSR: CSL1, CSL0) in timer control status register.

- Edge detection of software trigger or external trigger is specified as an activation trigger.

## 16-bit Reload Timer Block Diagram

# MB90387/387S/F387/F387S MB90V495G

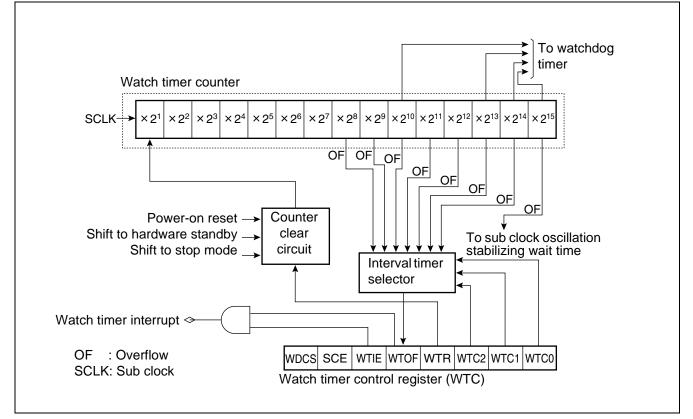

## Watch Timer Block Diagram

Actual interrupt request number of watch timer is as follows: Interrupt request number: #28 (1C<sub>H</sub>)

## Watch Timer Counter

A 15-bit up counter that uses sub clock (SCLK) as a count clock.

## **Counter Clear Circuit**

A circuit that clears the watch timer counter.

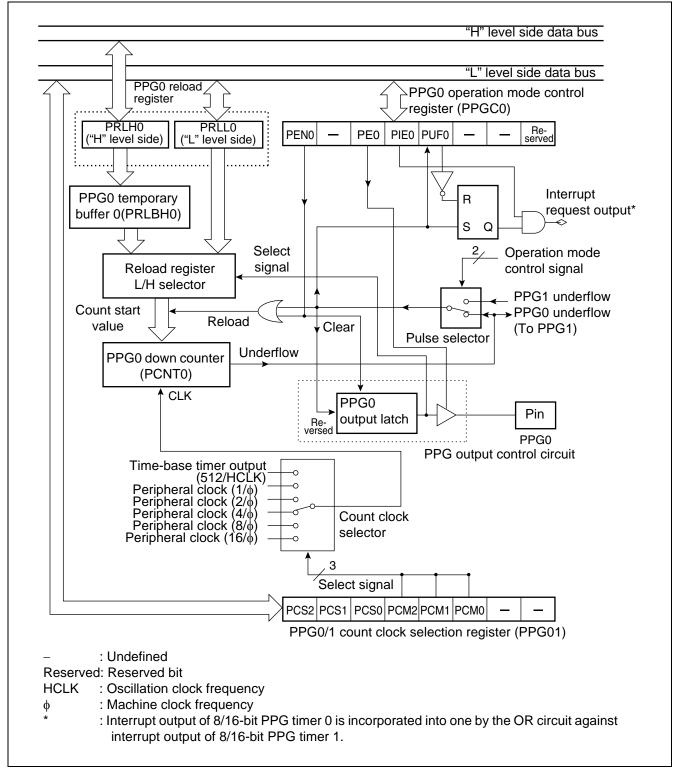

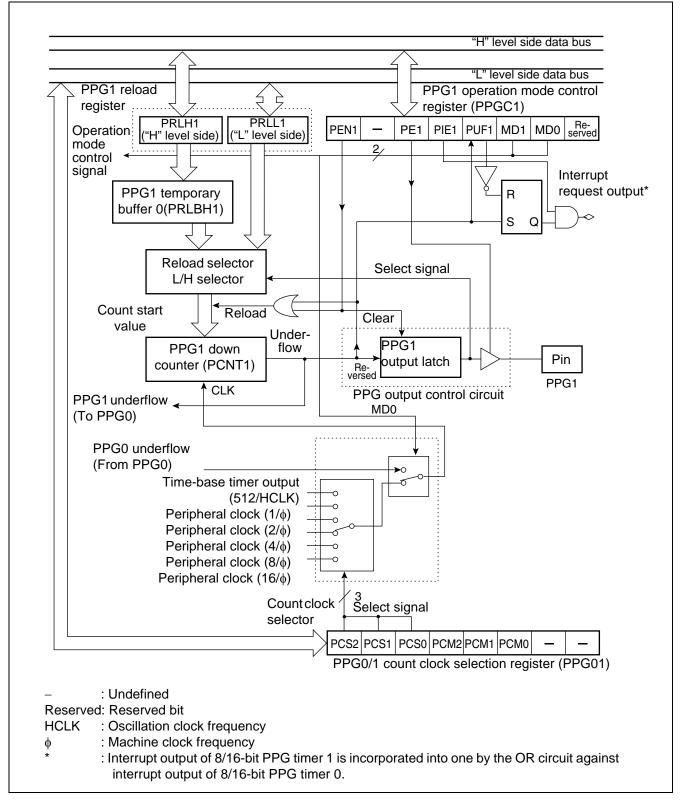

## 12.7 8/16-bit PPG Timer Outline

The 8/16-bit PPG timer is a 2-channel reload timer module (PPG0 and PPG1) that allows outputting pulses of arbitrary cycle and duty cycle. Combination of the two channels allows selection among the following operations:

- 8-bit PPG output 2-channel independent operation mode

- 16-bit PPG output operation mode

- 8-bit and 8-bit PPG output operation mode

MB90385 series device has two 8/16-bit built-in PPG timers. This section describes functions of PPG0/1. PPG2/3 have the same functions as those of PPG0/1.

## Functions of 8/16-bit PPG Timer

The 8/16-bit PPG timer is composed of four 8-bit reload register (PRLH0/PRLL0, PRLH1/PRLL1) and two PPG down counters (PCNT0, PCNT1).

- Widths of "H" and "L" in output pulse are specifiable independently. Cycle and duty factor of output pulse is specifiable arbitrarily.

- Count clock is selectable among 6 internal clocks.

- The timer is usable as an interval timer, by generating interrupt requests for each interval.

- The time is usable as a D/A converter, with an external circuit.

## 8/16-bit PPG Timer 0 Block Diagram

## MB90387/387S/F387/F387S MB90V495G

8/16-bit PPG Timer 1 Block Diagram

## 12.9 DTP/External Interrupt and CAN Wakeup Outline

DTP/external interrupt transfers an interrupt request generated by an external peripheral device or a data transmission request to CPU, generating external interrupt request and activating expanded intelligent I/O service. Input RX of CAN controller is used as external interrupt input.

#### **DTP/External Interrupt and CAN Wakeup Function**

An interrupt request input from external peripheral device to external input pins (INT7 to INT4) and RX pin, just as interrupt request of peripheral device, generates an interrupt request. The interrupt request generates an external interrupt and activates expanded intelligent I/O service (EI<sup>2</sup>OS).

If the expanded intelligent I/O service (EI<sup>2</sup>OS) has been disabled by interrupt control register (ICR: ISE=0), external interrupt function is enabled and branches to interrupt processing.

If the EI<sup>2</sup>OS has been enabled, (ICR: ISE=1), DTP function is enabled and automatic data transmission is performed by EI<sup>2</sup>OS. After performing specified number of data transmission processes, the process branches to interrupt processing.

|                   | External Interrupt                                         | DTP Function                                                                                                        |

|-------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Input pin         | 5 pins (RX, and INT4 to INT7)                              |                                                                                                                     |

| Interrupt cause   | Specify for each pin with detection level setting r        | egister (ELVR).                                                                                                     |

|                   | Input of "H" level/"L" level/rising edge/falling edge.     | Input of "H" level/ "L" level                                                                                       |

| Interrupt number  | #15 (0Fн), #24 (18н), #27 (1Вн)                            |                                                                                                                     |

| Interrupt control | Enabling or disabling output of interrupt request, (ENIR). | using DTP/external interrupt permission register                                                                    |

| Interrupt flag    | Retaining interrupt cause with DTP/external inter          | rrupt cause register (EIRR).                                                                                        |

| Process selection | Disable El <sup>2</sup> OS (ICR: ISE=0)                    | Enable El <sup>2</sup> OS (ICR: ISE=1)                                                                              |

| Process           | Branch to external interrupt process                       | After automatic data transmission by El <sup>2</sup> OS for specified number of times, branch to interrupt process. |

| Table 12-2. | DTP/External In | terrupt and CAN | Wakeup Outline |

|-------------|-----------------|-----------------|----------------|

|-------------|-----------------|-----------------|----------------|

## 12.11 UART Outline

UART is a general-purpose serial data communication interface for synchronous and asynchronous communication using external devices.

- Provided with bi-directional communication function for both clock-synchronous and clock-asynchronous modes.

- Provided with master/slave communication function (multi-processor mode). (Only master side is available.)

- Interrupt request is generated upon completion of reception, completion of transmission and detection of reception error.

- Ready for expanded intelligent service, El<sup>2</sup>OS.

#### Table 12-3. UART Functions

|                                                                             | Description                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data buffer                                                                 | Full-duplex double buffer                                                                                                                                                                                                     |

| Transmission mode                                                           | Clock synchronous (No start/stop bit, no parity bit)<br>Clock asynchronous (start-stop synchronous)                                                                                                                           |

| Baud rate                                                                   | Built-in special-purpose baud-rate generator. Setting is selectable among 8<br>values.<br>Input of external values is allowed.<br>Use of clock from external timer (16-bit reload timer 0) is allowed.                        |

| Data length                                                                 | 7 bits (only asynchronous normal mode)<br>8 bits                                                                                                                                                                              |

| Signaling system                                                            | Non Return to Zero (NRZ) system                                                                                                                                                                                               |

| Reception error detection                                                   | Framing error<br>Overrun error<br>Parity error (not detectable in operation mode 1 (multi-processor mode))                                                                                                                    |

| Interrupt request                                                           | Receive interrupt (reception completed, reception error detected)<br>Transmission interrupt (transmission completed)<br>Ready for expanded intelligent I/O service (El <sup>2</sup> OS) in both transmission and<br>reception |

| Master/slave communication function<br>(asynchronous, multi-processor mode) | Communication between 1 (master) and n (slaves) are available (usable as master only).                                                                                                                                        |

Note: Start/stop bit is not added upon clock-synchronous transmission. Data only is transmitted.

#### Table 12-4. UART Operation Modes

|   | Operation Mode                     | Data L         | ength          | Synchronization | Stop Bit Length    |  |

|---|------------------------------------|----------------|----------------|-----------------|--------------------|--|

|   | Operation mode                     | With Parity    | Without Parity | Synchronization |                    |  |

| 0 | Asynchronous mode<br>(normal mode) | 7-bit or 8-bit |                | Asynchronous    | 1- bit or 2-bit *2 |  |

| 1 | Multi processor mode               | 8+1*1          | -              | Asynchronous    |                    |  |

| 2 | Synchronous mode                   | 8              | -              | Synchronous     | No                 |  |

#### -: Disallowed

1: "+1" is an address/data selection bit used for communication control (bit 11 of SCR1 register: A/D).

2: Only 1 bit is detected as a stop bit on data reception.

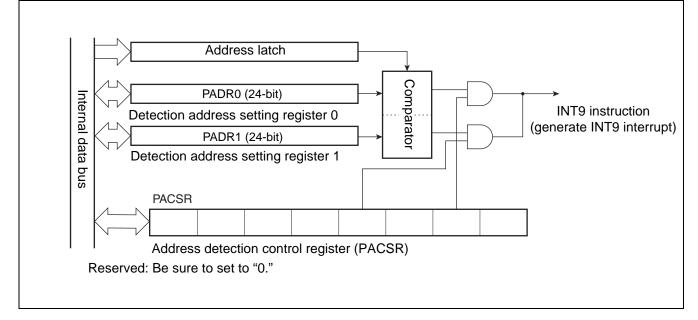

## 12.13 Address Matching Detection Function Outline

The address matching detection function checks if an address of an instruction to be processed next to a currently-processed instruction is identical with an address specified in the detection address register. If the addresses match with each other, an instruction to be processed next in program is forcibly replaced with INT9 instruction, and process branches to the interrupt process program. Using INT9 interrupt, this function is available for correcting program by batch processing.

#### Address Matching Detection Function Outline

- An address of an instruction to be processed next to a currently-processed instruction of the program is always retained in an address latch via internal data bus. By the address matching detection function, the address value retained in the address latch is always compared with an address specified in detection address setting register. If the compared address values match with each other, an instruction to be processed next by CPU is forcibly replaced with INT9 instruction, and an interrupt process program is executed.

- Two detection address setting registers are provided (PADR0 and PADR1), and each register is provided with interrupt permission bit. Generation of interrupt, which is caused by address matching between the address retained in address latch and the address specified in address setting register, is permitted and prohibited on a register-by-register basis.

#### Address Matching Detection Function Block Diagram

Address latch

Retains address value output to internal data bus.

- Address detection control register (PACSR) Specifies if interrupt is permitted or prohibited when addresses match with each other.

- Detection address setting (PADR0, PADR1) Specifies addresses to be compared with values in address latch.

## **13. Electrical Characteristics**

## 13.1 Absolute Maximum Rating

| Parameter                              | Cumhal          | Rating    |           | Unit | Remarks               |  |

|----------------------------------------|-----------------|-----------|-----------|------|-----------------------|--|

| Parameter                              | Symbol          | Min       | Max       | Unit | Remarks               |  |

| Power supply voltage*1                 | Vcc             | Vss - 0.3 | Vss + 6.0 | V    |                       |  |

|                                        | AVcc            | Vss - 0.3 | Vss + 6.0 | V    | Vcc = AVcc*2          |  |

|                                        | AVR             | Vss - 0.3 | Vss + 6.0 | V    | $AVcc \ge AVR^{*2}$   |  |

| Input voltage*1                        | Vi              | Vss - 0.3 | Vss + 6.0 | V    | *3                    |  |

| Output voltage*1                       | Vo              | Vss - 0.3 | Vss + 6.0 | V    | *3                    |  |

| Maximum clamp current                  |                 | - 2.0     | + 2.0     | mA   | *7                    |  |

| Total maximum clamp current            | Σ   Iclamp      | -         | 20        | mA   | *7                    |  |

| "L" level maximum output current       | IOL1            | -         | 15        | mA   | Normal output*4       |  |

|                                        | IOL2            | -         | 40        | mA   | High-current output*4 |  |

| "L" level average output current       | IOLAV1          | -         | 4         | mA   | Normal output*5       |  |

|                                        | IOLAV2          | -         | 30        | mA   | High-current output*5 |  |

| "L" level maximum total output current | Σlol1           | -         | 125       | mA   | Normal output         |  |

|                                        | ΣΙοι2           | -         | 160       | mA   | High-current output   |  |

| "L" level average total output current | $\Sigma$ lolav1 | -         | 40        | mA   | Normal output*6       |  |

|                                        | $\Sigma$ Iolav2 | -         | 40        | mA   | High-current output*6 |  |

| "H" level maximum output current       | Іон1            | -         | -15       | mA   | Normal output*4       |  |

|                                        | Іон2            | -         | -40       | mA   | High-current output*4 |  |

| "H" level average output current       | IOHAV1          | -         | -4        | mA   | Normal output*5       |  |

|                                        | IOHAV2          | -         | -30       | mA   | High-current output*5 |  |

| "H" level maximum total output current | ΣІон1           | -         | -125      | mA   | Normal output         |  |

|                                        | ΣІон2           | -         | -160      | mA   | High-current output   |  |

| "H" level average total output current | ΣΙομαν1         | -         | -40       | mA   | Normal output*6       |  |

|                                        | ΣΙομαν2         | -         | -40       | mA   | High-current output*6 |  |

| Power consumption                      | PD              | -         | 245       | mW   |                       |  |

| Operating temperature                  | TA              | -40       | +105      | °C   |                       |  |

| Storage temperature                    | Tstg            | -55       | +150      | °C   |                       |  |

\*1: The parameter is based on  $V_{SS} = AV_{SS} = 0.0 V$ .

\*2: AVcc and AVR should not exceed Vcc.

\*3: VI and Vo should not exceed Vcc + 0.3 V. However if the maximum current to/from an input is limited by some means with external components, the IcLAMP rating supersedes the VI rating.

\*4: A peak value of an applicable one pin is specified as a maximum output current.

- \*5: An average current value of an applicable one pin within 100 ms is specified as an average output current. (Average value is found by multiplying operating current by operating rate.)

- \*6: An average current value of all pins within 100 ms is specified as an average total output current. (Average value is found by multiplying operating current by operating rate.)

\*7:

Applicable to pins: P10 to P17, P20 to P27, P30 to P33, P35\*, P36\*, P37, P40 to P44, P50 to P57

\*: P35 and P36 are MB90387S and MB90F387S only.

## 13.2 Recommended Operating Conditions

(Vss = AVss = 0.0V)

| Parameter             | Symbol | Value |     |      | Unit | Remarks                            |  |

|-----------------------|--------|-------|-----|------|------|------------------------------------|--|

| Falameter             |        | Min   | Тур | Max  | Unit | Rellidiks                          |  |

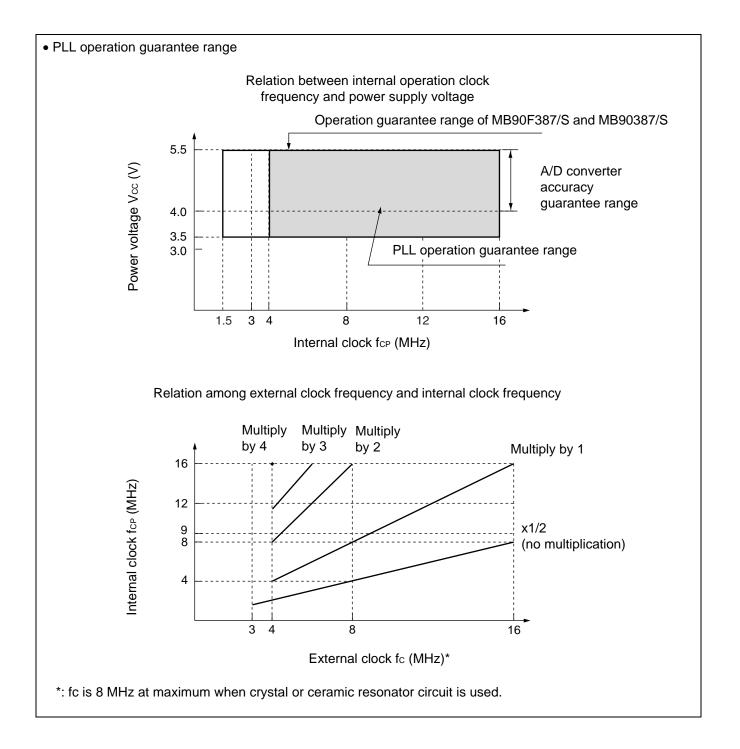

| Power supply voltage  | Vcc    | 3.5   | 5.0 | 5.5  | V    | Under normal operation             |  |

|                       |        | 3.0   | _   | 5.5  |      | Retain status of stop<br>operation |  |

|                       | AVcc   | 4.0   | -   | 5.5  | V    | *2                                 |  |

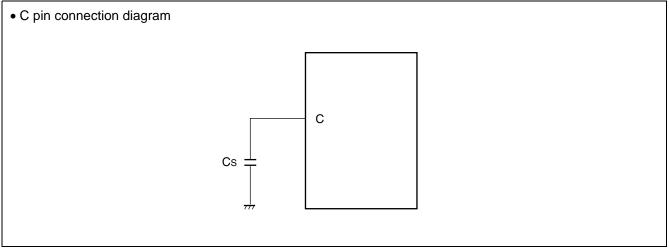

| Smoothing capacitor   | Cs     | 0.1   | -   | 1.0  | μF   | *1                                 |  |

| Operating temperature | TA     | -40   | -   | +105 | °C   |                                    |  |

\*1: Use a ceramic capacitor, or a capacitor of similar frequency characteristics. On the Vcc pin, use a bypass capacitor that has a larger capacity than that of Cs.

Refer to the following figure for connection of smoothing capacitor Cs.

\*2: AVcc is a voltage at which accuracy is guaranteed. AVcc should not exceed Vcc.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

| Parameter                   | Symbol | Pin Name                                      | Conditions                                                                                                  |     | Value | l Init | Remarks |                                                                 |

|-----------------------------|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|--------|---------|-----------------------------------------------------------------|

|                             |        |                                               |                                                                                                             | Min | Тур   | Max    | Unit    | Remarks                                                         |

| Power<br>supply<br>current* | lcc∟   | Vcc                                           | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>subclock operation,                                       |     | 0.3   | 1.2    | mA      | MB90F387/S                                                      |

|                             |        |                                               | $T_A = +25^{\circ}C$                                                                                        |     | 40    | 100    | μΑ      | MB90387/S                                                       |

| ICCLS                       |        |                                               | $V_{CC} = 5.0 V$ ,<br>Internally operating at 8 kHz,<br>subclock,<br>sleep mode,<br>$T_{A} = + 25^{\circ}C$ | _   | 10    | 30     | μA      |                                                                 |

|                             | Ісст   |                                               | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>watch mode,<br>$T_A = + 25^{\circ}C$                      |     | 8     | 25     | μΑ      |                                                                 |

|                             | Іссн   |                                               | Stopping,<br>T <sub>A</sub> = + 25°C                                                                        | _   | 5     | 20     | μΑ      |                                                                 |

| Input<br>capacity           | CIN    | Other than AVcc,<br>AVss, AVR, C, Vcc,<br>Vss | -                                                                                                           | _   | 5     | 15     | pF      |                                                                 |

| Pull-up<br>resistor         | Rup    | RST                                           | -                                                                                                           | 25  | 50    | 100    | kΩ      |                                                                 |

| Pull-down<br>resistor       | Rdown  | MD2                                           | -                                                                                                           | 25  | 50    | 100    | kΩ      | Flash product is<br>not provided<br>with pull-down<br>resistor. |

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 \circ C to +105 \circ C)$

\*: Test conditions of power supply current are based on a device using external clock.

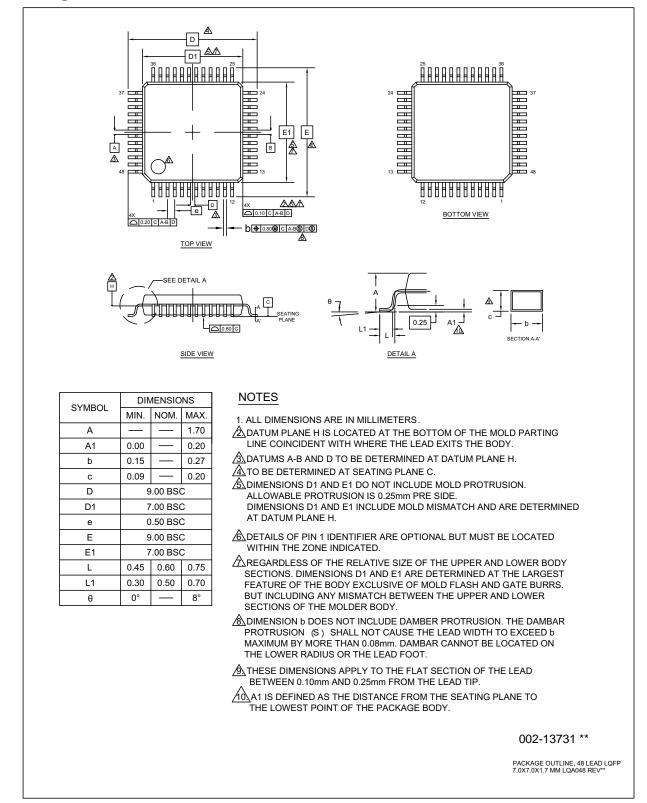

## 16. Package Dimension