Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-gs-249e1 |

|----------------------------|---------------------------------------------------------------------------------|

| Supplier Device Package    | 48-LQFP (7x7)                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Nounting Type              | Surface Mount                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Oscillator Type            | External                                                                        |

| Data Converters            | A/D 8x8/10b                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                     |

| RAM Size                   | 2K x 8                                                                          |

| EPROM Size                 | -                                                                               |

| rogram Memory Type         | Mask ROM                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| umber of I/O               | 36                                                                              |

| eripherals                 | POR, WDT                                                                        |

| Connectivity               | CANbus, SCI, UART/USART                                                         |

| peed                       | 16MHz                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Product Status             | Obsolete                                                                        |

| Details                    |                                                                                 |

# DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

■ Module for activation of expanded intelligent I/O service (El²OS), and generation of external interrupt.

#### **Delay Interrupt Generator Module**

■ Generates interrupt request for task switching.

#### 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 µs (at 16 MHz machine clock, including sampling time)

## **Program Patch Function**

■ Address matching detection for 2 address pointers.

Document Number: 002-07765 Rev. \*A Page 2 of 81

# 1. Product Lineup

| Part Number Parameter            |                          | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                          | MB90387<br>MB90387S                                                                           | MB90V495G                             |  |  |  |

|----------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

| Classification                   |                          | Flash ROM                                                                                                                                                                                                                                                                      | Mask ROM                                                                                      | Evaluation product                    |  |  |  |

| ROM capacity                     |                          | 64 Kby                                                                                                                                                                                                                                                                         | _                                                                                             |                                       |  |  |  |

| RAM capacity                     |                          | 2 Kbyt                                                                                                                                                                                                                                                                         | es                                                                                            | 6 Kbytes                              |  |  |  |

| Process                          |                          |                                                                                                                                                                                                                                                                                | CMOS                                                                                          | <u> </u>                              |  |  |  |

| Package                          |                          | LQFP-48 (pin pit                                                                                                                                                                                                                                                               | ch 0.50 mm)                                                                                   | PGA-256                               |  |  |  |

| Operating powe                   | r supply voltage         | 3.5 V to 5                                                                                                                                                                                                                                                                     | 5.5 V                                                                                         | 4.5 V to 5.5 V                        |  |  |  |

| Special power s<br>emulator*1    | upply for                | -                                                                                                                                                                                                                                                                              |                                                                                               | None                                  |  |  |  |

| CPU functions                    |                          | Number of basic instructions<br>Instruction bit length<br>Instruction length<br>Data bit length                                                                                                                                                                                | : 351 instructions<br>: 8 bits and 16 bits<br>: 1 byte to 7 bytes<br>: 1 bit, 8 bits, 16 bits |                                       |  |  |  |

|                                  |                          | Minimum instruction execution til                                                                                                                                                                                                                                              |                                                                                               | <u> </u>                              |  |  |  |

|                                  |                          | Interrupt processing time: 1.5 μs                                                                                                                                                                                                                                              | •                                                                                             | · · · · · · · · · · · · · · · · · · · |  |  |  |

| Low power cons<br>(standby) mode |                          | Sleep mode / Watch mode / Time                                                                                                                                                                                                                                                 | Sleep mode / Watch mode / Time-base timer mode / Stop mode / CPU intermittent                 |                                       |  |  |  |

| I/O port                         |                          | General-purpose input/output ports (CMOS output): 34 ports (36 ports*2) including 4 high-current output ports (P14 to P17)                                                                                                                                                     |                                                                                               |                                       |  |  |  |

| Time-base timer                  |                          | 18-bit free-run counter<br>Interrupt cycle: 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms<br>(with oscillation clock frequency at 4 MHz)                                                                                                                                           |                                                                                               |                                       |  |  |  |

| Watchdog timer                   |                          | Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (with oscillation clock frequency at 4 MHz)                                                                                                                                                                     |                                                                                               |                                       |  |  |  |

| 16-bit input/<br>output timer    | 16-bit free-run<br>timer | Number of channels: 1 Interrupt upon occurrence of overflow                                                                                                                                                                                                                    |                                                                                               |                                       |  |  |  |

|                                  | Input capture            | Number of channels: 4 Retaining free-run timer value set by pin input (rising edge, falling edge, and both edges)                                                                                                                                                              |                                                                                               |                                       |  |  |  |

| 16-bit reload timer              |                          | Number of channels: 2 16-bit reload timer operation Count clock cycle: 0.25 μs, 0.5 μs, 2.0 μs (at 16-MHz machine clock frequency) External event count is allowed.                                                                                                            |                                                                                               |                                       |  |  |  |

| Watch timer                      |                          | 15-bit free-run counter<br>Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s<br>(with 8.192 kHz sub clock)                                                                                                                                               |                                                                                               |                                       |  |  |  |

| 8/16-bit PPG timer               |                          | Number of channels: 2 (four 8-bit channels are available also.) PPG operation is allowed with four 8-bit channels or two 16-bit channels. Outputting pulse wave of arbitrary cycle or arbitrary duty is allowed. Count clock: 62.5 ns to 1 $\mu$ s (with 16 MHz machine clock) |                                                                                               |                                       |  |  |  |

| Delay interrupt of               | generator module         | Interrupt generator module for ta                                                                                                                                                                                                                                              | sk switching. Used for realtir                                                                | me OS.                                |  |  |  |

| DTP/External in                  | terrupt                  | Number of inputs: 4 Activated by rising edge, falling edge, "H" level or "L" level input. External interrupt or expanded intelligent I/O service (El <sup>2</sup> OS) is available.                                                                                            |                                                                                               |                                       |  |  |  |

Document Number: 002-07765 Rev. \*A Page 4 of 81

## 6. I/O Circuit Type

| Туре | Circuit                                                                                                           | Remarks                                                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | X1<br>X1A<br>X0<br>X0A  Standby control signal                                                                    | <ul> <li>High-rate oscillation feedback resistor, approx.1 MΩ</li> <li>Low-rate oscillation feedback resistor, approx.10 MΩ</li> </ul>              |

| В    | R ≷ R → W → Hysteresis input                                                                                      | <ul> <li>■ Hysteresis input with pull-up resistor.</li> <li>■ Pull-up resistor, approx.50 kΩ</li> </ul>                                             |

| С    | R                                                                                                                 | ■ Hysteresis input                                                                                                                                  |

| D    | P-ch Digital output  N-ch Digital output  R  CMOS  hysteresis input  Standby control                              | <ul> <li>■ CMOS hysteresis input</li> <li>■ CMOS level output</li> <li>■ Standby control provided</li> </ul>                                        |

| E    | P-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  Standby control  Analog input | <ul> <li>■ CMOS hysteresis input</li> <li>■ CMOS level output</li> <li>■ Shared for analog input pin</li> <li>■ Standby control provided</li> </ul> |

| Address                  | Register<br>Abbreviation | Register                                                | Read/<br>Write | Resource                            | Initial Value         |

|--------------------------|--------------------------|---------------------------------------------------------|----------------|-------------------------------------|-----------------------|

| 000083н                  |                          | (Reserve                                                | ed area) *     | 1                                   |                       |

| 000084н                  | TCANR                    | Send cancel register                                    | W              | CAN controller                      | 0000000В              |

| 000085н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000086н                  | TCR                      | Send completion register                                | R/W            | CAN controller                      | 0000000В              |

| 000087н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000088н                  | RCR                      | Receive completion register                             | R/W            | CAN controller                      | 0000000В              |

| 000089н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Ан                  | RRTRR                    | Receive RTR register                                    | R/W            | CAN controller                      | 0000000В              |

| 00008Вн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Сн                  | ROVRR                    | Receive overrun register                                | R/W            | CAN controller                      | 0000000В              |

| 00008Dн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Ен                  | RIER                     | Receive completion interrupt permission register        | R/W            | CAN controller                      | 0000000В              |

| 00008Fн<br>to<br>00009Dн |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00009Ен                  | PACSR                    | Address detection control register                      | R/W            | Address matching detection function | 0000000В              |

| 00009Fн                  | DIRR                     | Delay interrupt request generation/<br>release register | R/W            | Delay interrupt generation module   | XXXXXXX0 <sub>B</sub> |

| 0000А0н                  | LPMCR                    | Lower power consumption mode control register           | W,R/W          | Lower power consumption mode        | 00011000в             |

| 0000А1н                  | CKSCR                    | Clock selection register                                | R,R/W          | Clock                               | 11111100в             |

| 0000A2н<br>to<br>0000A7н |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 0000А8н                  | WDTC                     | Watchdog timer control register                         | R,W            | Watchdog timer                      | XXXXX111 <sub>B</sub> |

| 0000А9н                  | TBTC                     | Time-base timer control register                        | R/W,W          | Time-base timer                     | 1ХХ00100в             |

| 0000ААн                  | WTC                      | Watch timer control register                            | R,R/W          | Watch timer                         | 1Х001000в             |

| 0000ABн<br>to<br>0000ADн |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 0000АЕн                  | FMCS                     | Flash memory control status register                    | R,W,R/W        | 512k-bit Flash<br>memory            | 000Х0000в             |

| 0000АГн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| Address                  | Register<br>Abbreviation                               | Register                                            | Read/<br>Write | Resource                            | Initial Value |

|--------------------------|--------------------------------------------------------|-----------------------------------------------------|----------------|-------------------------------------|---------------|

| 0000В0н                  | ICR00                                                  | Interrupt control register 00                       | R/W            | Interrupt controller                | 00000111в     |

| 0000В1н                  | ICR01                                                  | Interrupt control register 01                       |                |                                     | 00000111в     |

| 0000В2н                  | ICR02                                                  | Interrupt control register 02                       |                |                                     |               |

| 0000ВЗн                  | ICR03                                                  | Interrupt control register 03                       |                |                                     | 00000111в     |

| 0000В4н                  | ICR04                                                  | Interrupt control register 04                       |                |                                     | 00000111в     |

| 0000В5н                  | ICR05                                                  | Interrupt control register 05                       |                |                                     | 00000111в     |

| 0000В6н                  | ICR06                                                  | Interrupt control register 06                       |                |                                     | 00000111в     |

| 0000В7н                  | ICR07                                                  | Interrupt control register 07                       |                |                                     | 00000111в     |

| 0000В8н                  | ICR08                                                  | Interrupt control register 08                       |                |                                     | 00000111в     |

| 0000В9н                  | ICR09                                                  | Interrupt control register 09                       |                |                                     | 00000111в     |

| 0000ВАн                  | ICR10                                                  | Interrupt control register 10                       |                |                                     | 00000111в     |

| 0000ВВн                  | ICR11                                                  | Interrupt control register 11                       |                |                                     | 00000111в     |

| 0000ВСн                  | ICR12                                                  | Interrupt control register 12                       |                |                                     | 00000111в     |

| 0000ВDн                  | ICR13                                                  | Interrupt control register 13                       |                |                                     | 00000111в     |

| 0000ВЕн                  | ICR14                                                  | Interrupt control register 14                       |                |                                     | 00000111в     |

| 0000ВГн                  | ICR15                                                  | Interrupt control register 15                       |                |                                     | 00000111в     |

| 0000FFн<br>001FF0н       | PADR0 Detection address setting register 0 (low-order) |                                                     | R/W            | Address matching detection function | XXXXXXXX      |

| 001FF1н                  | -                                                      | Detection address setting register 0 (middle-order) |                |                                     | XXXXXXXX      |

| 001FF2н                  |                                                        | Detection address setting register 0 (high-order)   |                |                                     | XXXXXXXX      |

| 001FF3н                  | PADR1                                                  | Detection address setting register 1 (low-order)    | R/W            |                                     | XXXXXXXXB     |

| 001FF4н                  |                                                        | Detection address setting register 1 (middle-order) |                |                                     | XXXXXXXXB     |

| 001FF5н                  |                                                        | Detection address setting register 1 (high-order)   |                |                                     | XXXXXXXXB     |

| 003900н                  | TMR0/                                                  | 16-bit timer register 0/16-bit reload               | R,W            | 16-bit reload timer 0               | XXXXXXXX      |

| 003901н                  | TMRLR0                                                 | register                                            |                |                                     | XXXXXXXX      |

| 003902н                  | TMR1/                                                  | 16-bit timer register 1/16-bit reload               | R,W            | 16-bit reload timer 1               | XXXXXXXX      |

| 003903н                  | TMRLR1                                                 | register                                            |                |                                     | XXXXXXXX      |

| 003904н<br>to<br>00390Fн |                                                        | (Reser                                              | ved area) *    |                                     |               |

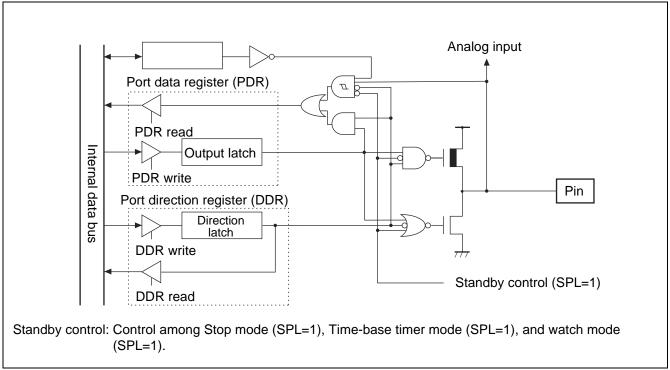

## Port 5 Pins Block Diagram

## **Port 5 Registers**

- Port 5 registers include port 5 data register (PDR5), port 5 direction register (DDR5), and analog input permission register (ADER).

- Analog input permission register (ADER) allows or disallows input of analog signal to the analog input pin.

- The bits configuring the register correspond to port 5 pins on a one-to-one basis.

## Relation between Port 5 Registers and Pins

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 5    | PDR5, DDR5                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | ADER                                    | ADE7 | ADE6 | ADE5 | ADE4 | ADE3 | ADE2 | ADE1 | ADE0 |

|           | Corresponding pins                      | P57  | P56  | P55  | P54  | P53  | P52  | P51  | P50  |

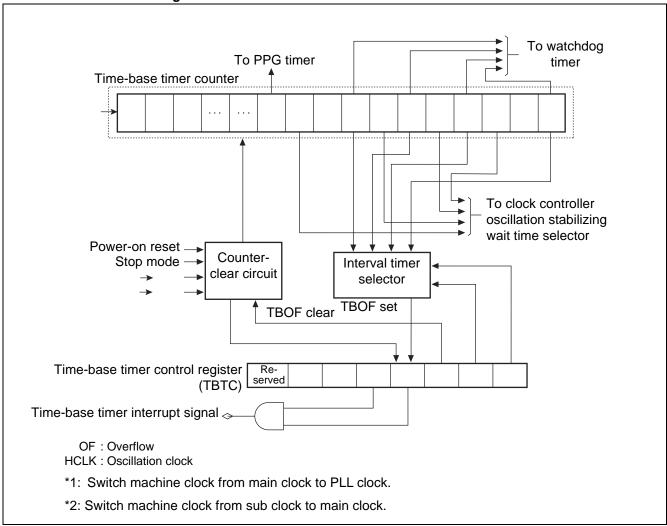

### 12.2 Time-Base Timer

The time-base time is an 18-bit free-run counter (time-base timer counter) that counts up in synchronization with the main clock (dividing main oscillation clock by 2).

- Four choices of interval time are selectable, and generation of interrupt request is allowed for each interval time.

- Provides operation clock signal to oscillation stabilizing wait timer and peripheral functions.

#### **Interval Timer Function**

- When the counter of time-base timer reaches an interval time specified by interval time selection bit (TBTC:TBC1, TBC0), an overflow (carrying-over) occurs (TBTC: TBOF=1) and interrupt request is generated.

- If an interrupt by overflow is permitted (TBTC: TBIE=1), an interrupt is generated when overflow occurs (TBTC: TBOF=1).

- The following four interval time settings are selectable:

#### **Interval Time of Time-base Timer**

| Count Clock     | Interval Time                            |

|-----------------|------------------------------------------|

| 2/HCLK (0.5 μs) | 212/HCLK (Approx. 1.0 ms)                |

|                 | 2 <sup>14</sup> /HCLK (Approx. 4.1 ms)   |

|                 | 216/HCLK (Approx. 16.4 ms)               |

|                 | 2 <sup>19</sup> /HCLK (Approx. 131.1 ms) |

HCLK: Oscillation clock

Values in parentheses "()" are those under operation of 4-MHz oscillation clock.

Document Number: 002-07765 Rev. \*A Page 28 of 81

## **Time-base Timer Block Diagram**

Actual interrupt request number of time-base timer is as follows:

Interrupt request number: #16 (10H)

## 12.3 Watchdog Timer

The watchdog timer is a 2-bit counter that uses time-base timer or watch timer as count clock. If the counter is not cleared within an interval time, CPU is reset.

## **Watchdog Timer Functions**

- The watchdog timer is a timer counter that prevents runaway of a program. Once a watchdog timer is activated, the counter of watchdog timer must always be cleared within a specified time of interval. If specified interval time elapses without clearing the counter of a watchdog timer, CPU resetting occurs. This is the function of a watchdog timer.

- The interval time of a watchdog timer is determined by a clock cycle, which is input as a count clock. Watchdog resetting occurs between a minimum time and a maximum time specified.

- The output target of a clock source is specified by the watchdog clock selection bit (WTC: WDCS) in the watch timer control register.

- Interval time of a watchdog timer is specified by the time-base timer output selection bit / watch timer output selection bit (WDTC: WT1, WT0) in the watchdog timer control register.

#### **Interval Timer of Watchdog Timer**

| Min                  | Max                  | Clock Cycle                                  | Min                 | Max                 | Clock Cycle                                  |

|----------------------|----------------------|----------------------------------------------|---------------------|---------------------|----------------------------------------------|

| Approx. 3.58 ms      | Approx. 4.61 ms      | (2 <sup>14</sup> ±2 <sup>11</sup> )<br>/HCLK | Approx. 0.457 s     | Approx. 0.576 s     | (2 <sup>12</sup> ±2 <sup>9</sup> )<br>/SCLK  |

| Approx. 14.33 ms     | Approx. 18.3 ms      | (2 <sup>16</sup> ±2 <sup>13</sup> )<br>/HCLK | Approx. 3.584 s     | Approx. 4.608 s     | (2 <sup>15</sup> ±2 <sup>12</sup> )<br>/SCLK |

| Approx. 57.23 ms     | Approx. 73.73 ms     | (2 <sup>18</sup> ±2 <sup>15</sup> )<br>/HCLK | Approx. 7.168 s     | Approx. 9.216 s     | (2 <sup>16</sup> ±2 <sup>13</sup> )<br>/SCLK |

| Approx.<br>458.75 ms | Approx.<br>589.82 ms | (2 <sup>21</sup> ±2 <sup>18</sup> )<br>/HCLK | Approx.<br>14.336 s | Approx.<br>18.432 s | (2 <sup>17</sup> ±2 <sup>14</sup> )<br>/SCLK |

HCLK: Oscillation clock (4 MHz), CSCLK: Sub clock (8.192 kHz)

### Notes:

- If the time-base timer is cleared when watchdog timer count clock is used as time base timer output (carry-over signal), watchdog reset time may become longer.

- When using the sub clock as machine clock, be sure to specify watchdog timer clock source selection bit (WDCS) in watch timer control register (WTC) at "0," selecting output of watch timer.

Document Number: 002-07765 Rev. \*A Page 30 of 81

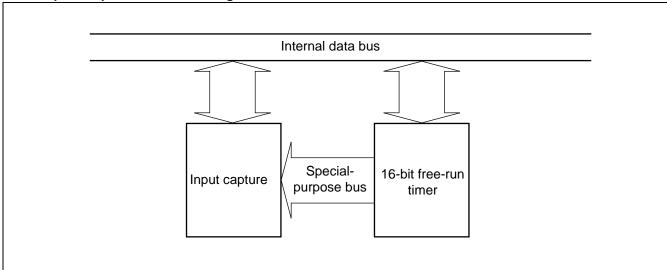

## 12.4 16-bit Input/Output Timer

The 16-bit input/output timer is a compound module composed of 16-bit free-run timer, (1 unit) and input capture (2 units, 4 input pins). The timer, using the 16-bit free-run timer as a basis, enables measurement of clock cycle of an input signal and its pulse width.

#### Configuration of 16-bit Input/Output Timer

The 16-bit input/output timer is composed of the following modules:

- 16-bit free-run timer (1 unit)

- Input capture (2 units, 2 input pins per unit)

### Functions of 16-bit Input/Output Timer

#### Functions of 16-bit Free-run Timer

The 16-bit free-run timer is composed of 16-bit up counter, timer counter control status register, and prescaler. The 16-bit up counter increments in synchronization with dividing ratio of machine clock.

- Count clock is set among four types of machine clock dividing rates.

- Generation of interrupt is allowed by counter value overflow.

- Activation of expanded intelligent I/O service (El²OS) is allowed by interrupt generation.

- Counter value of 16-bit free-run timer is cleared to "0000H" by either resetting or software-clearing with timer count clear bit (TCCS: CLR).

- Counter value of 16-bit free-run timer is output to input capture, which is available as base time for capture operation.

#### Functions of Input Capture

The input capture, upon detecting an edge of a signal input to the input pin from external device, stores a counter value of 16-bit freerun timer at the time of detection into the input capture data register. The function includes the input capture data registers corresponding to four input pins, input capture control status register, and edge detection circuit.

- Rising edge, falling edge, and both edges are selectable for detection.

- Generating interrupt on CPU is allowed by detecting an edge of input signal.

- Expanded intelligent I/O service (El<sup>2</sup>OS) is activated by interrupt generation.

- The four input capture input pins and input capture data registers allows monitoring of a maximum of four events.

## 16-bit Input/Output Timer Block Diagram

Document Number: 002-07765 Rev. \*A Page 32 of 81

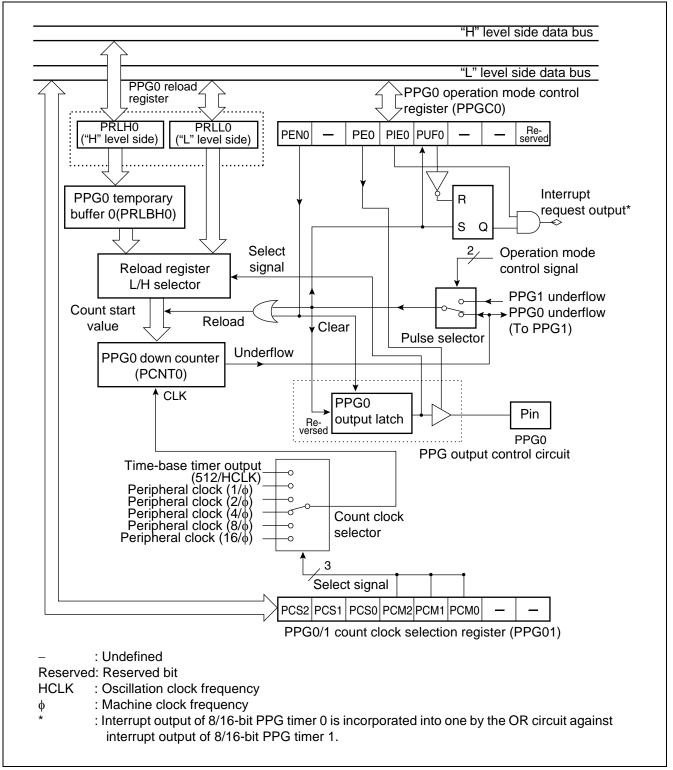

### 12.7 8/16-bit PPG Timer Outline

The 8/16-bit PPG timer is a 2-channel reload timer module (PPG0 and PPG1) that allows outputting pulses of arbitrary cycle and duty cycle. Combination of the two channels allows selection among the following operations:

- 8-bit PPG output 2-channel independent operation mode

- 16-bit PPG output operation mode

- 8-bit and 8-bit PPG output operation mode

MB90385 series device has two 8/16-bit built-in PPG timers. This section describes functions of PPG0/1. PPG2/3 have the same functions as those of PPG0/1.

#### **Functions of 8/16-bit PPG Timer**

The 8/16-bit PPG timer is composed of four 8-bit reload register (PRLH0/PRLL0, PRLH1/PRLL1) and two PPG down counters (PCNT0, PCNT1).

- Widths of "H" and "L" in output pulse are specifiable independently. Cycle and duty factor of output pulse is specifiable arbitrarily.

- Count clock is selectable among 6 internal clocks.

- The timer is usable as an interval timer, by generating interrupt requests for each interval.

- The time is usable as a D/A converter, with an external circuit.

Document Number: 002-07765 Rev. \*A Page 39 of 81

## 8/16-bit PPG Timer 0 Block Diagram

## 13.2 Recommended Operating Conditions

(Vss = AVss = 0.0V)

| Parameter             | Symbol | Value |     |      |      | Remarks                         |

|-----------------------|--------|-------|-----|------|------|---------------------------------|

| raiailletei           | Symbol | Min   | Тур | Max  | Unit | Remarks                         |

| Power supply voltage  | Vcc    | 3.5   | 5.0 | 5.5  | V    | Under normal operation          |

|                       |        | 3.0   | _   | 5.5  |      | Retain status of stop operation |

|                       | AVcc   | 4.0   | _   | 5.5  | V    | *2                              |

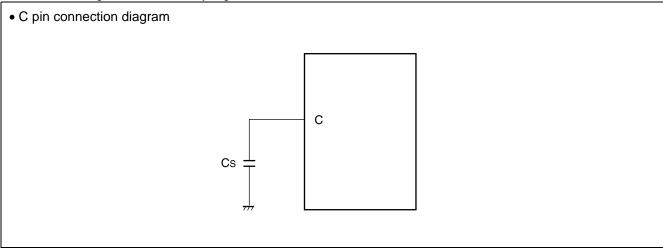

| Smoothing capacitor   | Cs     | 0.1   | _   | 1.0  | μF   | *1                              |

| Operating temperature | Та     | -40   | -   | +105 | °C   |                                 |

<sup>\*1:</sup> Use a ceramic capacitor, or a capacitor of similar frequency characteristics. On the Vcc pin, use a bypass capacitor that has a larger capacity than that of Cs.

Refer to the following figure for connection of smoothing capacitor Cs.

\*2: AVcc is a voltage at which accuracy is guaranteed. AVcc should not exceed Vcc.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

Document Number: 002-07765 Rev. \*A Page 57 of 81

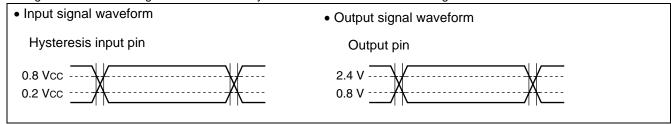

Rating values of alternating current is defined by the measurement reference voltage values shown below:

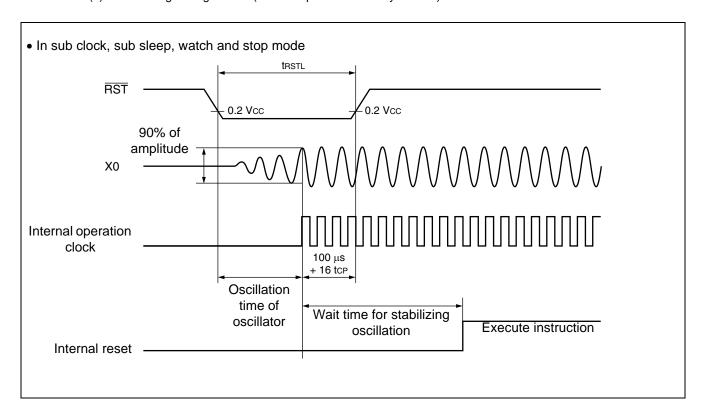

13.4.2 Reset Input Timing

| Parameter        | Symbol   | Pin Name  | Value Value                                          |     |      | Remarks                                                  |

|------------------|----------|-----------|------------------------------------------------------|-----|------|----------------------------------------------------------|

| Parameter        | Syllibol | FIII Name | Min                                                  | Max | Unit | Remarks                                                  |

| Reset input time | trstl    | RST       | 16 tcp*3                                             | -   | ns   | Normal operation                                         |

|                  |          |           | Oscillation time of oscillator*1 + 100 μs + 16 tcp*3 | -   |      | In sub clock*2, sub<br>sleep*2, watch*2 and<br>stop mode |

|                  |          |           | 100                                                  | _   | μS   | In timebase timer                                        |

<sup>\*1:</sup> Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

<sup>\*3:</sup> Refer to "(1) Clock timing" ratings for tcp (internal operation clock cycle time).

<sup>\*2:</sup> Except for MB90F387S and MB90387S.

(Continued)

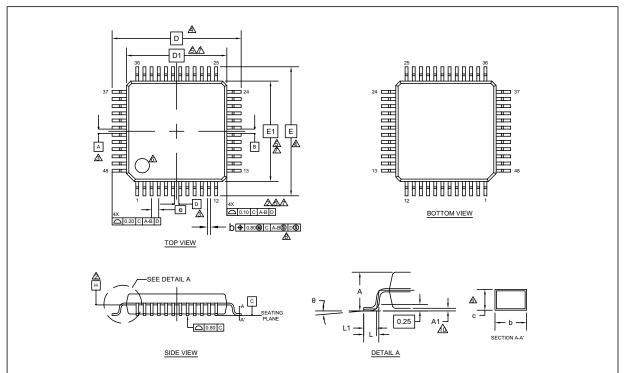

## 16. Package Dimension

| SYMBOL | DIN      | /ENSIO  | NS   |  |

|--------|----------|---------|------|--|

| STMBOL | MIN.     | NOM.    | MAX. |  |

| Α      | _        |         | 1.70 |  |

| A1     | 0.00     | _       | 0.20 |  |

| b      | 0.15     |         | 0.27 |  |

| С      | 0.09     | 0.20    |      |  |

| D      | 9.00 BSC |         |      |  |

| D1     | 7        | .00 BS0 | 0    |  |

| е      | 0        | .50 BS  | 0    |  |

| E      | 9        | .00 BS  | 2    |  |

| E1     | 7.00 BSC |         |      |  |

| L      | 0.45     | 0.60    | 0.75 |  |

| L1     | 0.30     | 0.50    | 0.70 |  |

| θ      | 0°       | _       | 8°   |  |

#### **NOTES**

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- △ DATUM PLANE H IS LOCATED AT THE BOTTOM OF THE MOLD PARTING LINE COINCIDENT WITH WHERE THE LEAD EXITS THE BODY.

- ⚠DATUMS A-B AND D TO BE DETERMINED AT DATUM PLANE H.

- ⚠ TO BE DETERMINED AT SEATING PLANE C.

- ⚠DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION.

ALLOWABLE PROTRUSION IS 0.25mm PRE SIDE.

DIMENSIONS D1 AND E1 INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

- ⚠ DETAILS OF PIN 1 IDENTIFIER ARE OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

- AREGARDLESS OF THE RELATIVE SIZE OF THE UPPER AND LOWER BODY SECTIONS. DIMENSIONS D1 AND E1 ARE DETERMINED AT THE LARGEST FEATURE OF THE BODY EXCLUSIVE OF MOLD FLASH AND GATE BURRS. BUT INCLUDING ANY MISMATCH BETWEEN THE UPPER AND LOWER SECTIONS OF THE MOLDER BODY.

- ⚠ DIMENSION b DOES NOT INCLUDE DAMBER PROTRUSION. THE DAMBAR PROTRUSION (S) SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED b MAXIMUM BY MORE THAN 0.08mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE LEAD FOOT.

- ⚠ THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP.

- A1 IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

002-13731 \*\*

PACKAGE OUTLINE, 48 LEAD LQFP 7.0X7.0X1.7 MM LQA048 REV\*\*

## 17. Major Changes

Spansion Publication Number: DS07-13717-5E

| Page | Section               | Change Results                                                                                                         |

|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| 4    |                       | Changed the number of channel of 8/16 bit PPG timer. or one 16-bit channel → or two 16-bit channels                    |

| 13   |                       | Changed the direction of arrow of TIN0, TIN1 signals of 16-bit reload timer. right arrow (output) → left arrow (input) |

| 67   | 4. AC Characteristics | Changed the value of Serial clock. Serial clock "H" pulse width: 4tcp→2tcp Serial clock "L" pulse width: 4tcp→2tcp     |

NOTE: Please see "Document History" about later revised information.

Document Number: 002-07765 Rev. \*A Page 79 of 81

## **Document History**

| Document Title: MB90387/387S/F387/F387S, MB90V495G, 16-bit Microcontrollers F <sup>2</sup> MC-16LX MB90385 Series Document Number:002-07765 |         |                    |                    |                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|

| Revision                                                                                                                                    | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |

| **                                                                                                                                          | _       | AKIH               | 12/19/2008         | Migrated to Cypress and assigned document number 002-07765.<br>No change to document contents or format. |

| *A                                                                                                                                          | 6059071 | SSAS               | 02/05/2018         | Updated to Cypress template Package: FPT-48P-M26> LQA048                                                 |

Document Number: 002-07765 Rev. \*A Page 80 of 81