Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | CANbus, SCI, UART/USART                                                         |

| Peripherals                | POR, WDT                                                                        |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | Mask ROM                                                                        |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | 48-LQFP (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-gs-384e1 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number<br>Parameter | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MB90387<br>MB90387S | MB90V495G                 |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|--|

| 8/10-bit A/D converter   | Number of channels: 8<br>Resolution: Selectable 10-bit or 8-bit.<br>Conversion time: $6.125 \ \mu s$ (at 16 MHz machine clock, including sampling time)<br>Sequential conversion of two or more successive channels is allowed. (Setting a<br>maximum of 8 channels is allowed.)<br>Single conversion mode: Selected channel is converted only once.<br>Sequential conversion mode: Selected channel is converted repetitively.<br>Halt conversion mode: Conversion of selected channel is stopped and activated alter-<br>nately. |                     |                           |  |

| UART(SCI)                | Number of channels: 1<br>Clock-synchronous transfer: 62.9<br>Clock-asynchronous transfer: 9,0<br>Communication is allowed by bi-<br>slave type connection.                                                                                                                                                                                                                                                                                                                                                                         | 615 bps to 500 kbps | tion function and master/ |  |

| CAN                      | Compliant with Ver 2.0A and Ver<br>8 built-in message buffers.<br>Transmission rate of 10 kbps to<br>CAN wake-up                                                                                                                                                                                                                                                                                                                                                                                                                   | ·                   | clock)                    |  |

\*1: Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

\*2: MB90387S, MB90F387S

## 2. Packages And Product Models

| Package | MB90F387, MB90F387S | MB90387, MB90387S |

|---------|---------------------|-------------------|

| LQA048  | $\bigcirc$          | $\bigcirc$        |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to Package Dimension for details of the package.

## 3. Product Comparison

### Memory Space

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

- On MB90V495G, an image from FF4000<sup>H</sup> to FFFFFF<sup>H</sup> is viewed on 00 bank and an image of FE0000<sup>H</sup> to FF3FFF<sup>H</sup> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387/387S, an image from FF4000H to FFFFFFH is viewed on 00 bank and an image of FE0000H to FF3FFFH is viewed only on FF bank.

| Pin No.  | Pin Name   | Circuit<br>Type | Function                                                                                               |

|----------|------------|-----------------|--------------------------------------------------------------------------------------------------------|

| 39       | P42        | D               | General-purpose input/output port.                                                                     |

|          | SOT1       |                 | Serial data input pin for UART. Valid only when serial data input/output setting on UART is "enabled." |

| 40       | P43        | D               | General-purpose input/output port.                                                                     |

|          | ТХ         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |

| 41       | P44        | D               | General-purpose input/output port.                                                                     |

|          | RX         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |

| 42 to 45 | P30 to P33 | D               | General-purpose input/output ports.                                                                    |

| 46       | X0A*       | А               | Pin for low-rate oscillation.                                                                          |

|          | P35*       |                 | General-purpose input/output port.                                                                     |

| 47       | X1A*       | A               | Pin for low-rate oscillation.                                                                          |

|          | P36*       | 1               | General-purpose input/output port.                                                                     |

| 48       | AVss       | -               | Vss power source input pin for A/D converter.                                                          |

\*: MB90387, MB90F387: X1A, X0A MB90387S, MB90F387S: P36, P35

| Address                  | Register<br>Abbreviation | Register                                                | Read/<br>Write | Resource                            | Initial Value         |

|--------------------------|--------------------------|---------------------------------------------------------|----------------|-------------------------------------|-----------------------|

| 000083н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000084н                  | TCANR                    | Send cancel register                                    | W              | CAN controller                      | 0000000в              |

| 000085н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000086н                  | TCR                      | Send completion register                                | R/W            | CAN controller                      | 0000000в              |

| 000087н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000088н                  | RCR                      | Receive completion register                             | R/W            | CAN controller                      | 0000000в              |

| 000089н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Ан                  | RRTRR                    | Receive RTR register                                    | R/W            | CAN controller                      | 0000000в              |

| 00008Вн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Сн                  | ROVRR                    | Receive overrun register                                | R/W            | CAN controller                      | 0000000в              |

| 00008Dн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Eн                  | RIER                     | Receive completion interrupt<br>permission register     | R/W            | CAN controller                      | 0000000в              |

| 00008Fн<br>to<br>00009Dн |                          | (Reserv                                                 | ed area) *     |                                     |                       |

| 00009Eн                  | PACSR                    | Address detection control register                      | R/W            | Address matching detection function | 0000000в              |

| 00009Fн                  | DIRR                     | Delay interrupt request generation/<br>release register | R/W            | Delay interrupt generation module   | XXXXXXX0B             |

| 0000А0н                  | LPMCR                    | Lower power consumption mode control register           | W,R/W          | Lower power consumption mode        | 00011000в             |

| 0000A1н                  | CKSCR                    | Clock selection register                                | R,R/W          | Clock                               | 11111100в             |

| 0000А2н<br>to<br>0000А7н |                          | (Reserv                                                 | ed area) *     |                                     |                       |

| 0000A8н                  | WDTC                     | Watchdog timer control register                         | R,W            | Watchdog timer                      | XXXXX111 <sub>B</sub> |

| 0000A9н                  | TBTC                     | Time-base timer control register                        | R/W,W          | Time-base timer                     | 1XX00100в             |

| 0000ААн                  | WTC                      | Watch timer control register                            | R,R/W          | Watch timer                         | 1Х001000в             |

| 0000ABн<br>to<br>0000ADн |                          | (Reserv                                                 | ed area) *     | ·                                   |                       |

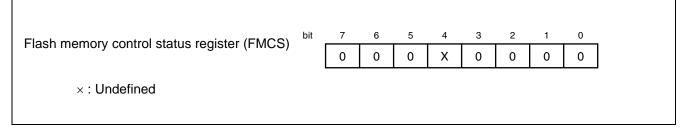

| 0000AEн                  | FMCS                     | Flash memory control status register                    | R,W,R/W        | 512k-bit Flash<br>memory            | 000X0000 <sub>B</sub> |

| 0000AFн                  |                          | (Reserv                                                 | ed area) *     | . 1                                 |                       |

| Address                  | Register<br>Abbreviation | Register                                               | Read/<br>Write           | Resource                            | Initial Value |

|--------------------------|--------------------------|--------------------------------------------------------|--------------------------|-------------------------------------|---------------|

| 0000В0н                  | ICR00                    | Interrupt control register 00                          | R/W                      | Interrupt controller                | 00000111в     |

| 0000B1н                  | ICR01                    | Interrupt control register 01                          |                          |                                     | 00000111в     |

| 0000В2н                  | ICR02                    | Interrupt control register 02                          | rupt control register 02 |                                     |               |

| 0000ВЗн                  | ICR03                    | Interrupt control register 03                          |                          |                                     | 00000111в     |

| 0000В4н                  | ICR04                    | Interrupt control register 04                          |                          |                                     | 00000111в     |

| 0000B5н                  | ICR05                    | Interrupt control register 05                          |                          |                                     | 00000111в     |

| 0000В6н                  | ICR06                    | Interrupt control register 06                          |                          |                                     | 00000111в     |

| <b>0000B7</b> н          | ICR07                    | Interrupt control register 07                          |                          |                                     | 00000111в     |

| 0000B8н                  | ICR08                    | Interrupt control register 08                          |                          |                                     | 00000111в     |

| 0000B9н                  | ICR09                    | Interrupt control register 09                          |                          |                                     | 00000111в     |

| 0000ВАн                  | ICR10                    | Interrupt control register 10                          |                          |                                     | 00000111в     |

| 0000ВВн                  | ICR11                    | Interrupt control register 11                          |                          |                                     | 00000111в     |

| 0000ВСн                  | ICR12                    | Interrupt control register 12                          |                          |                                     | 00000111в     |

| 0000BDн                  | ICR13                    | Interrupt control register 13                          |                          |                                     | 00000111в     |

| 0000ВЕн                  | ICR14                    | Interrupt control register 14                          |                          | 1   F                               |               |

| 0000BFн                  | ICR15                    | Interrupt control register 15                          |                          |                                     | 00000111в     |

| 0000C0н<br>to<br>0000FFн |                          | (Reser                                                 | ved area) *              |                                     |               |

| 001FF0⊦                  | PADR0                    | Detection address setting register 0 (low-order)       | R/W                      | Address matching detection function | XXXXXXXXB     |

| 001FF1⊦                  |                          | Detection address setting register 0 (middle-order)    |                          |                                     | XXXXXXXXB     |

| 001FF2⊦                  |                          | Detection address setting register 0 (high-order)      |                          |                                     | XXXXXXXXB     |

| 001FF3⊦                  | PADR1                    | Detection address setting register 1 (low-order)       | R/W                      | ] [                                 | XXXXXXXXB     |

| 001FF4⊦                  |                          | Detection address setting register 1<br>(middle-order) |                          |                                     | XXXXXXXXB     |

| 001FF5н                  | 1                        | Detection address setting register 1 (high-order)      | 1                        |                                     | XXXXXXXXB     |

| 003900н                  | TMR0/                    | 16-bit timer register 0/16-bit reload                  | R,W                      | 16-bit reload timer 0               | XXXXXXXXB     |

| 003901н                  | TMRLR0                   | register                                               |                          | F F                                 | XXXXXXXXB     |

| 003902н                  | TMR1/                    | 16-bit timer register 1/16-bit reload                  | R,W                      | 16-bit reload timer 1               | XXXXXXXXB     |

| 003903н                  | TMRLR1                   | register                                               |                          |                                     | XXXXXXXXB     |

| 003904н<br>to<br>00390Fн |                          | (Reser                                                 | ved area) *              |                                     |               |

## 11. Interrupt Sources, Interrupt Vectors, And Interrupt Control Registers

| Interrupt Source                                                               | El <sup>2</sup> OS | I   | nterrup     | t Vector            | Interrupt C | ontrol Register        | Priority*3   |

|--------------------------------------------------------------------------------|--------------------|-----|-------------|---------------------|-------------|------------------------|--------------|

|                                                                                | Readiness          | Nur | nber        | Address             | ICR         | Address                | Priority**   |

| Reset                                                                          | ×                  | #08 | 08н         | <b>FFFFDC</b> H     | -           | -                      | High         |

| INT 9 instruction                                                              | ×                  | #09 | 09н         | FFFFD8H             | -           | -                      | ↑            |

| Exceptional treatment                                                          | ×                  | #10 | 0Ан         | FFFFD4H             | -           | -                      |              |

| CAN controller reception completed (RX)                                        | ,                  | #11 | 0Вн         | FFFFD0H             | ICR00       | 0000B0н*1              |              |

| CAN controller transmission<br>completed (TX) / Node status<br>transition (NS) | ,                  | #12 | 0Сн         | FFFFCCH             |             |                        |              |

| Reserved                                                                       | ×                  | #13 | 0Dн         | FFFFC8H             | ICR01       | 0000B1н                |              |

| Reserved                                                                       | ×                  | #14 | 0Ен         | FFFFC4H             | 1           |                        |              |

| CAN wakeup                                                                     | Δ                  | #15 | 0Fн         | FFFFC0H             | ICR02       | 0000B2н*1              |              |

| Time-base timer                                                                | ×                  | #16 | 10н         | <b>FFFFBC</b> H     | 1           |                        |              |

| 16-bit reload timer 0                                                          | Δ                  | #17 | 11н         | FFFFB8 <sub>H</sub> | ICR03       | 0000B3н*1              |              |

| 8/10-bit A/D converter                                                         | Δ                  | #18 | 12н         | FFFFB4H             |             |                        |              |

| 16-bit free-run timer overflow                                                 | Δ                  | #19 | 13н         | FFFFB0H             | ICR04       | 0000B4н*1              |              |

| Reserved                                                                       | ×                  | #20 | 14н         | <b>FFFFAC</b> H     |             |                        |              |

| Reserved                                                                       | ×                  | #21 | <b>15</b> н | FFFFA8H             | ICR05       | 0000B5н*1              |              |

| PPG timer ch0, ch1 underflow                                                   | ,                  | #22 | <b>16</b> н | FFFFA4H             |             |                        |              |

| Input capture 0-input                                                          | Δ                  | #23 | <b>17</b> н | FFFFA0н             | ICR06       | 0000В6н*1              |              |

| External interrupt (INT4/INT5)                                                 | Δ                  | #24 | <b>18</b> н | FFFF9CH             |             |                        |              |

| Input capture 1-input                                                          | Δ                  | #25 | <b>19</b> н | FFFF98н             | ICR07       | 0000 <b>B7</b> н*2     |              |

| PPG timer ch2, ch3 underflow                                                   | ,                  | #26 | 1Ан         | FFFF94⊦             | -           |                        |              |

| External interrupt (INT6/INT7)                                                 | Δ                  | #27 | 1Bн         | FFFF90H             | ICR08       | 0000B8н*1              |              |

| Watch timer                                                                    | Δ                  | #28 | 1Сн         | FFFF8CH             |             |                        |              |

| Reserved                                                                       | ×                  | #29 | 1Dн         | FFFF88H             | ICR09       | 0000B9н*1              |              |

| Input capture 2-input<br>Input capture 3-input                                 | ,                  | #30 | 1Ен         | FFFF84⊦             | -           |                        |              |

| Reserved                                                                       | ×                  | #31 | 1Fн         | FFFF80H             | ICR10       | 0000BAн*1              |              |

| Reserved                                                                       | ×                  | #32 | 20н         | FFFF7CH             |             |                        |              |

| Reserved                                                                       | ×                  | #33 | 21н         | FFFF78⊦             | ICR11       | 0000BB <sub>H</sub> *1 |              |

| Reserved                                                                       | ×                  | #34 | 22н         | FFFF74 <sub>H</sub> |             |                        |              |

| Reserved                                                                       | ×                  | #35 | 23н         | FFFF70н             | ICR12       | 0000BC <sub>H</sub> *1 | $\downarrow$ |

| 16-bit reload timer 1                                                          | 0                  | #36 | 24н         | FFFF6CH             |             |                        | Low          |

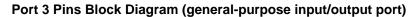

### **Port 3 Registers**

- Port 3 registers include port 3 data register (PDR3) and port 3 direction register (DDR3).

- The bits configuring the register correspond to port 3 pins on a one-to-one basis.

#### **Relation between Port 3 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 3    | PDR3, DDR3                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P37  | P36* | P35* | _    | P33  | P32  | P31  | P30  |

\*: P35 and P36 do not exist on MB90387and MB90F387.

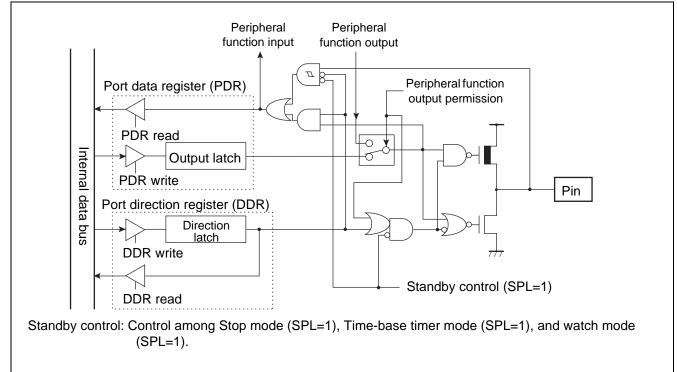

#### 12.2 Time-Base Timer

The time-base time is an 18-bit free-run counter (time-base timer counter) that counts up in synchronization with the main clock (dividing main oscillation clock by 2).

- Four choices of interval time are selectable, and generation of interrupt request is allowed for each interval time.

- Provides operation clock signal to oscillation stabilizing wait timer and peripheral functions.

#### **Interval Timer Function**

- When the counter of time-base timer reaches an interval time specified by interval time selection bit (TBTC:TBC1, TBC0), an overflow (carrying-over) occurs (TBTC: TBOF=1) and interrupt request is generated.

- If an interrupt by overflow is permitted (TBTC: TBIE=1), an interrupt is generated when overflow occurs (TBTC: TBOF=1).

- The following four interval time settings are selectable:

#### Interval Time of Time-base Timer

| Count Clock     | Interval Time                            |

|-----------------|------------------------------------------|

| 2/HCLK (0.5 μs) | 2 <sup>12</sup> /HCLK (Approx. 1.0 ms)   |

|                 | 2 <sup>14</sup> /HCLK (Approx. 4.1 ms)   |

|                 | 216/HCLK (Approx. 16.4 ms)               |

|                 | 2 <sup>19</sup> /HCLK (Approx. 131.1 ms) |

#### HCLK: Oscillation clock

Values in parentheses "()" are those under operation of 4-MHz oscillation clock.

#### Time-base Timer Block Diagram

Actual interrupt request number of time-base timer is as follows: Interrupt request number: #16 (10<sub>H</sub>)

#### Watchdog timer control register(WDTC) Watch timer control register (WTC) WRST ERST SRST WTE WT1 WT0 PONR \_\_\_\_ WDCS Watchdog timer 2, Activate Reset occurs \_ Counter Watchdog Shift to sleep mode -----2-bit Internal reset Count clock reset clear control Shift to time-base counter - 6 generation generation selector circuit timer mode circuit circuit Shift to watch mode Clear Shift to stop mode 4 4 Time-base timer counter Main clock $\times 2^2$ × 28 × 29 × 210 × 211 × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> $\times 2^1$ × 215 × 216 × 2<sup>17</sup> $\times 2^{18}$ (dividing HCLK by 2) Watch counter Sub clock $\times 2^2$ × 2<sup>5</sup> $\times 2^{6}$ × 2<sup>8</sup> × 2<sup>9</sup> × 2<sup>10</sup> × 2<sup>11</sup> × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> × 2<sup>15</sup> $\times 2^{1}$ $\times 2^7$ . SCLK HCLK: Oscillation clock SCLK: Sub clock

#### Watchdog Timer Block Diagram

#### 12.9 DTP/External Interrupt and CAN Wakeup Outline

DTP/external interrupt transfers an interrupt request generated by an external peripheral device or a data transmission request to CPU, generating external interrupt request and activating expanded intelligent I/O service. Input RX of CAN controller is used as external interrupt input.

#### **DTP/External Interrupt and CAN Wakeup Function**

An interrupt request input from external peripheral device to external input pins (INT7 to INT4) and RX pin, just as interrupt request of peripheral device, generates an interrupt request. The interrupt request generates an external interrupt and activates expanded intelligent I/O service (EI<sup>2</sup>OS).

If the expanded intelligent I/O service (EI<sup>2</sup>OS) has been disabled by interrupt control register (ICR: ISE=0), external interrupt function is enabled and branches to interrupt processing.

If the EI<sup>2</sup>OS has been enabled, (ICR: ISE=1), DTP function is enabled and automatic data transmission is performed by EI<sup>2</sup>OS. After performing specified number of data transmission processes, the process branches to interrupt processing.

|                   | External Interrupt                                                                                          | DTP Function                                                                                                        |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Input pin         | 5 pins (RX, and INT4 to INT7)                                                                               |                                                                                                                     |  |  |  |

| Interrupt cause   | Specify for each pin with detection level setting register (ELVR).                                          |                                                                                                                     |  |  |  |

|                   | Input of "H" level/"L" level/rising edge/falling edge.                                                      | Input of "H" level/ "L" level                                                                                       |  |  |  |

| Interrupt number  | #15 (0Fн), #24 (18н), #27 (1Вн)                                                                             |                                                                                                                     |  |  |  |

| Interrupt control | Enabling or disabling output of interrupt request, using DTP/external interrupt permission register (ENIR). |                                                                                                                     |  |  |  |

| Interrupt flag    | Retaining interrupt cause with DTP/external inter                                                           | rrupt cause register (EIRR).                                                                                        |  |  |  |

| Process selection | Disable El <sup>2</sup> OS (ICR: ISE=0)                                                                     | Enable El <sup>2</sup> OS (ICR: ISE=1)                                                                              |  |  |  |

| Process           | Branch to external interrupt process                                                                        | After automatic data transmission by El <sup>2</sup> OS for specified number of times, branch to interrupt process. |  |  |  |

| Table 12-2. | DTP/External In | terrupt and CAN | Wakeup Outline |

|-------------|-----------------|-----------------|----------------|

|-------------|-----------------|-----------------|----------------|

### 12.11 UART Outline

UART is a general-purpose serial data communication interface for synchronous and asynchronous communication using external devices.

- Provided with bi-directional communication function for both clock-synchronous and clock-asynchronous modes.

- Provided with master/slave communication function (multi-processor mode). (Only master side is available.)

- Interrupt request is generated upon completion of reception, completion of transmission and detection of reception error.

- Ready for expanded intelligent service, El<sup>2</sup>OS.

#### Table 12-3. UART Functions

|                                                                          | Description                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data buffer                                                              | Full-duplex double buffer                                                                                                                                                                                                     |

| Transmission mode                                                        | Clock synchronous (No start/stop bit, no parity bit)<br>Clock asynchronous (start-stop synchronous)                                                                                                                           |

| Baud rate                                                                | Built-in special-purpose baud-rate generator. Setting is selectable among 8<br>values.<br>Input of external values is allowed.<br>Use of clock from external timer (16-bit reload timer 0) is allowed.                        |

| Data length                                                              | 7 bits (only asynchronous normal mode)<br>8 bits                                                                                                                                                                              |

| Signaling system                                                         | Non Return to Zero (NRZ) system                                                                                                                                                                                               |

| Reception error detection                                                | Framing error<br>Overrun error<br>Parity error (not detectable in operation mode 1 (multi-processor mode))                                                                                                                    |

| Interrupt request                                                        | Receive interrupt (reception completed, reception error detected)<br>Transmission interrupt (transmission completed)<br>Ready for expanded intelligent I/O service (EI <sup>2</sup> OS) in both transmission and<br>reception |

| Master/slave communication function (asynchronous, multi-processor mode) | Communication between 1 (master) and n (slaves) are available (usable as master only).                                                                                                                                        |

Note: Start/stop bit is not added upon clock-synchronous transmission. Data only is transmitted.

#### Table 12-4. UART Operation Modes

| Operation Mode |                                    | Data L         | ength          | Synchronization | Stop Bit Length    |  |

|----------------|------------------------------------|----------------|----------------|-----------------|--------------------|--|

|                | Operation mode                     | With Parity    | Without Parity | Synchronization | Stop Bit Length    |  |

| 0              | Asynchronous mode<br>(normal mode) | 7-bit or 8-bit |                | Asynchronous    | 1- bit or 2-bit *2 |  |

| 1              | Multi processor mode               | 8+1*1 –        |                | Asynchronous    |                    |  |

| 2              | Synchronous mode                   | 8              | _              | Synchronous     | No                 |  |

#### -: Disallowed

1: "+1" is an address/data selection bit used for communication control (bit 11 of SCR1 register: A/D).

2: Only 1 bit is detected as a stop bit on data reception.

#### 12.15 512 Kbit Flash Memory Outline

The following three methods are provided for data writing and deleting on Flash memory:

- 1. Parallel writer

- 2. Serial special-purpose writer

- 3. Writing/deleting by program execution

This section describes "3. Writing/deleting by program execution."

#### 512 Kbit Flash Memory Outline

The 512 Kbit Flash memory is allocated on FF<sub>H</sub> bank of CPU memory map. Using the function of Flash memory interface circuit, the memory allows read access and program access from CPU.

Writing/deleting on Flash memory is performed by instruction from CPU via Flash memory interface. Because rewriting is allowed on mounted memory, modifying program and data is performed efficiently.

#### Features of 512 Kbit Flash Memory

- 128 K words x 8 bits/64 K words x 16 bits (16 K + 8 K + 8 K + 32 K) sector configuration

- Automatic program algorithm (Embedded Algorithm: Similar to MBM29LV200.)

- Built-in deletion pause/deletion resume function

- Detection of completed writing/deleting by data polling and toggle bits.

- Detection of completed writing/deleting by CPU interrupt.

- Deletion is allowed on a sector-by-sector basis (sectors are combined freely).

- Number of writing/deleting operations (minimum): 10,000 times

- Sector protection

- Expanded sector protection

- Temporaly sector unprotection

Note: A function of reading manufacture code and device code is not provided. These codes are not accessible by command either.

#### Flash Memory Writing/Deleting

- Writing and reading data is not allowed simultaneously on the Flash memory.

- Data writing and deleting on the Flash memory is performed by the processes as follows: Make a copy of program on Flash memory onto RAM. Then, execute the program copied on the RAM.

#### List of Registers and Reset Values in Flash Memory

#### Sector Configuration

For access from CPU, SA0 to SA3 are allocated in FF bank register.

### Sector Configuration of 512 Kbit Flash Memory

| Flash memory    | CPU address | Writer address* |

|-----------------|-------------|-----------------|

|                 | FF0000H     | 70000н          |

| SA0 (32 Kbytes) |             |                 |

|                 | FF7FFFH     | 77FFFн          |

|                 | FF8000H     | 78000н          |

| SA1 (8 Kbytes)  |             |                 |

|                 | FF9FFFH     | 79FFFH          |

|                 | FFA000H     | 7А000н          |

| SA2 (8 Kbytes)  |             |                 |

|                 | FFBFFFH     | 7BFFFн          |

|                 | FFC000H     | 7С000н          |

| SA3 (16 Kbytes) |             |                 |

|                 | FFFFFH      | 7FFFFH          |

\*: "Writer address" is an address equivalent to CPU address, which is used when data is written on Flash memory, using parallel writer. When writing/ deleting data with general-purpose writer, the writer address is used for writing and deleting.

### 13.2 Recommended Operating Conditions

(Vss = AVss = 0.0V)

| Parameter                                                            | Symbol | Value |                        |      |      | Remarks                            |  |

|----------------------------------------------------------------------|--------|-------|------------------------|------|------|------------------------------------|--|

| Falameter                                                            |        | Min   | Тур                    | Max  | Unit | Relliarks                          |  |

| Power supply voltage         Vcc         3.5         5.0         5.5 |        | V     | Under normal operation |      |      |                                    |  |

|                                                                      |        | 3.0   | _                      | 5.5  |      | Retain status of stop<br>operation |  |

|                                                                      | AVcc   | 4.0   | -                      | 5.5  | V    | *2                                 |  |

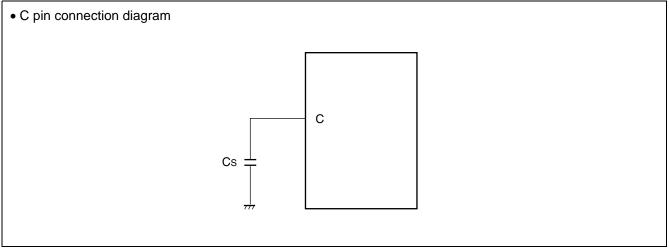

| Smoothing capacitor                                                  | Cs     | 0.1   | -                      | 1.0  | μF   | *1                                 |  |

| Operating temperature                                                | TA     | -40   | -                      | +105 | °C   |                                    |  |

\*1: Use a ceramic capacitor, or a capacitor of similar frequency characteristics. On the Vcc pin, use a bypass capacitor that has a larger capacity than that of Cs.

Refer to the following figure for connection of smoothing capacitor Cs.

\*2: AVcc is a voltage at which accuracy is guaranteed. AVcc should not exceed Vcc.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

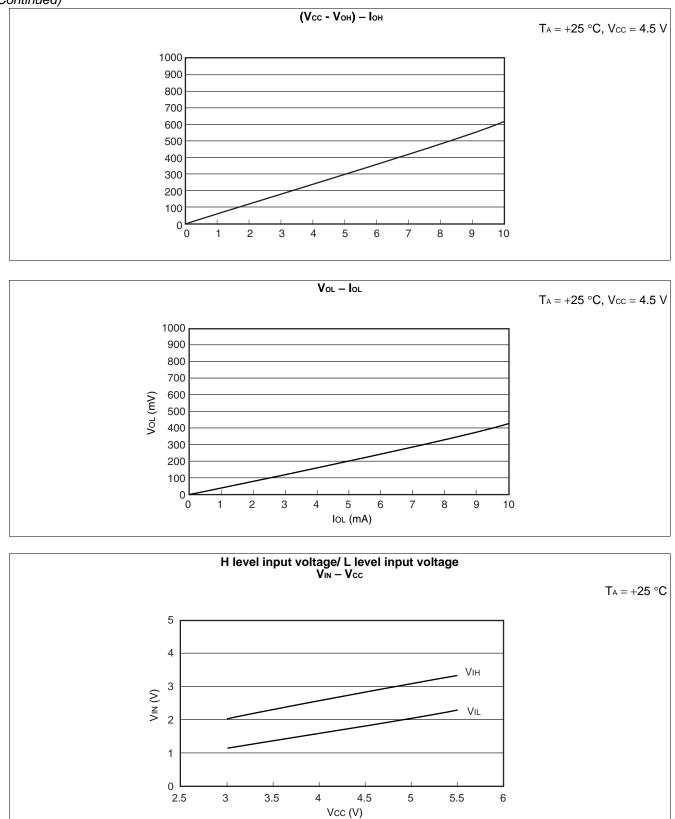

### **13.3 DC Characteristics**

|                             |        |                               | (****                                                                           | - 5.0 V±107 | Value | 1V35 – 0.0 V | , 14 –  | –40 °C to +105 |

|-----------------------------|--------|-------------------------------|---------------------------------------------------------------------------------|-------------|-------|--------------|---------|----------------|

| Parameter                   | Symbol | Pin Name                      | Conditions                                                                      | Min Typ Max |       | Unit         | Remarks |                |

| "H" level<br>input          | Vins   | CMOS hysteresis<br>input pin  | _                                                                               | 0.8 Vcc     |       | Vcc + 0.3    | V       |                |

| voltage                     | Vінм   | MD input pin                  | _                                                                               | Vcc - 0.3   | _     | Vcc + 0.3    | V       |                |

| "L" level<br>input          | Vils   | CMOS hysteresis<br>input pin  | _                                                                               | Vss - 0.3   | _     | 0.2 Vcc      | V       |                |

| voltage                     | Vilm   | MD input pin                  | —                                                                               | Vss - 0.3   | —     | Vss + 0.3    | V       |                |

| "H" level<br>output         | Vон1   | Pins other than<br>P14 to P17 | Vcc = 4.5 V,<br>Іон = -4.0 mA                                                   | Vcc - 0.5   | _     | —            | V       |                |

| voltage                     | Vон2   | P14 to P17                    | Vcc = 4.5 V,<br>Іон = -14.0 mA                                                  | Vcc - 0.5   | _     | —            | V       |                |

| "L" level<br>output         | Vol1   | Pins other than<br>P14 to P17 | Vcc = 4.5 V,<br>IoL = 4.0 mA                                                    | —           | _     | 0.4          | V       |                |

| voltage                     | Vol2   | P14 to P17                    | Vcc = 4.5 V,<br>Io∟ = 20.0 mA                                                   | —           | —     | 0.4          | V       |                |

| Input leak<br>current       | lι∟    | All input pins                | Vcc = 5.5 V,<br>Vss < Vi < Vcc                                                  | -5          | _     | +5           | μA      |                |

| Power<br>supply<br>current* | Icc    | Vcc                           | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, normal operation.            | —           | 25    | 30           | mA      |                |

|                             |        |                               | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, writing on<br>Flash memory.  | _           | 45    | 50           | mA      | MB90F387/S     |

|                             |        |                               | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, deleting on<br>Flash memory. | _           | 45    | 50           | mA      | MB90F387/S     |

|                             | lccs   |                               | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, sleeping.                    | _           | 8     | 12           | mA      |                |

|                             | Icts   |                               | Vcc = 5.0 V,<br>Internally operating at<br>2 MHz, transition from main          | —           | 0.75  | 1.0          | mA      | MB90F387/S     |

|                             |        |                               | clock mode, in time-base timer<br>mode.                                         |             | 0.2   | 0.35         |         | MB90387/S      |

#### (Vcc = 5.0 V±10%, Vss = AVss = 0.0 V, T<sub>A</sub> = -40 °C to +105 °C)

### 13.5 A/D Converter

| Demonstration                 | 0 miles | Pin Name      | Value          |                   |                   |      | <b>_</b>                                                                    |  |

|-------------------------------|---------|---------------|----------------|-------------------|-------------------|------|-----------------------------------------------------------------------------|--|

| Parameter                     | Symbol  |               | Min            | Тур               | Max               | Unit | Remarks                                                                     |  |

| Resolution                    | -       | -             | _              | _                 | 10                | bit  |                                                                             |  |

| Total error                   | _       | _             | _              | _                 | ± 3.0             | LSB  |                                                                             |  |

| Nonlinear error               | -       | -             | _              | _                 | ± 2.5             | LSB  |                                                                             |  |

| Differential linear error     | -       | -             | -              | _                 | ± 1.9             | LSB  |                                                                             |  |

| Zero transition voltage       | Vот     | AN0 to<br>AN7 | AVss – 1.5 LSB | AVss + 0.5<br>LSB | AVss + 2.5<br>LSB | V    | 1 LSB = (AVR – AVss) /<br>1024                                              |  |

| Full-scale transition voltage | Vfst    | AN0 to<br>AN7 | AVR – 3.5 LSB  | AVR – 1.5<br>LSB  | AVR + 0.5<br>LSB  | V    | -                                                                           |  |

| Compare time                  | -       | -             | 66 tcp *1      | _                 | _                 | ns   | With 16 MHz machine clock $5.5 \text{ V} \ge AV_{CC} \ge 4.5 \text{ V}$     |  |

|                               |         |               | 88 tcp *1      | _                 | _                 | ns   | With 16 MHz<br>machine clock<br>$4.5 \text{ V} > AV_{CC} \ge 4.0 \text{ V}$ |  |

| Sampling time                 | -       | -             | 32 tcp *1      | _                 | _                 | ns   | With 16 MHz machine clock $5.5 \text{ V} \ge AV_{CC} \ge 4.5 \text{ V}$     |  |

|                               |         |               | 128 tcp *1     | _                 | _                 | ns   | With 16 MHz machine clock 4.5 V > AVcc $\ge$ 4.0 V                          |  |

| Analog port input current     | Iain    | AN0 to<br>AN7 | -              | -                 | 10                | μA   |                                                                             |  |

| Analog input voltage          | Vain    | AN0 to<br>AN7 | AVss           | -                 | AVR               | V    |                                                                             |  |

| Reference voltage             | _       | AVR           | AVss + 2.7     | _                 | AVcc              | V    |                                                                             |  |

| Power supply current          | la      | AVcc          | —              | 3.5               | 7.5               | mA   |                                                                             |  |

|                               | Іан     | AVcc          | —              | -                 | 5                 | μA   | *2                                                                          |  |

| Reference voltage             | IR      | AVR           | _              | 165               | 250               | μA   |                                                                             |  |

| supplying current             | IRH     | AVR           | _              | _                 | 5                 | μA   | *2                                                                          |  |

| Variation among channels      | -       | AN0 to<br>AN7 | _              | _                 | 4                 | LSB  |                                                                             |  |

$(Vcc = AVcc = 4.0 \text{ V to } 5.5 \text{ V}, \text{ Vss} = AVss = 0.0 \text{ V}, 3.0 \text{ V} \le AVR - AVss, \text{ T}_{\text{A}} = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C})$

\*1: Refer to Clock Timing on AC Characteristics.

\*2: If A/D converter is not operating, a current when CPU is stopped is applicable (Vcc=AVcc=AVR=5.0 V).

(Continued)

#### (Continued)

## 17. Major Changes

Spansion Publication Number: DS07-13717-5E

| Page | Section                                                                                              | Change Results                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 4    | ■ PRODUCT LINEUP                                                                                     | Changed the number of channel of 8/16 bit PPG timer. or one 16-bit channel $\rightarrow$ or two 16-bit channels                       |

| 13   | ■ BLOCK DIAGRAM                                                                                      | Changed the direction of arrow of TIN0, TIN1 signals of 16-bit reload timer.<br>right arrow (output) $\rightarrow$ left arrow (input) |

| 67   | <ul> <li>ELECTRIC CHARACTERISTICS</li> <li>4. AC Characteristics</li> <li>(4) UART timing</li> </ul> | Changed the value of Serial clock.<br>Serial clock "H" pulse width: 4tcp→2tcp<br>Serial clock "L" pulse width: 4tcp→2tcp              |

NOTE: Please see "Document History" about later revised information.

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

**PSoC®** Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

## Cypress Developer Community

Community | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

<sup>©</sup> Cypress Semiconductor Corporation, 2004-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or system could cause personal injury, death, or properly damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify a