Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                      |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 16MHz                                                                       |

| Connectivity               | CANbus, SCI, UART/USART                                                     |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x8/10b                                                                 |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-LQFP                                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f387pmc-gte1 |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

Module for activation of expanded intelligent I/O service (EI<sup>2</sup>OS), and generation of external interrupt.

#### **Delay Interrupt Generator Module**

Generates interrupt request for task switching.

#### 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 μs (at 16 MHz machine clock, including sampling time)

## **Program Patch Function**

■ Address matching detection for 2 address pointers.

## 5. Pin Description

| Pin No.  | Pin Name     | Circuit<br>Type | Function                                                                                                    |  |  |  |  |  |  |

|----------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1        | AVcc         | -               | Vcc power input pin for A/D converter.                                                                      |  |  |  |  |  |  |

| 2        | AVR          | -               | Power (Vref+) input pin for A/D converter. Use as input for Vcc or lower.                                   |  |  |  |  |  |  |

| 3 to 10  | P50 to P57   | Е               | General-purpose input/output ports.                                                                         |  |  |  |  |  |  |

|          | AN0 to AN7   |                 | Functions as analog input pins for A/D converter. Valid when analog input setti "enabled."                  |  |  |  |  |  |  |

| 11       | P37          | D               | General-purpose input/output port.                                                                          |  |  |  |  |  |  |

|          | ADTG         |                 | Function as an external trigger input pin for A/D converter. Use the pin by setting as input port.          |  |  |  |  |  |  |

| 12       | P20          | D               | General-purpose input/output port.                                                                          |  |  |  |  |  |  |

|          | TIN0         |                 | Function as an event input pin for reload timer 0. Use the pin by setting as input port.                    |  |  |  |  |  |  |

| 13       | P21          | D               | General-purpose input/output port.                                                                          |  |  |  |  |  |  |

|          | TOT0         |                 | Function as an event output pin for reload timer 0. Valid only when output setting is "enabled."            |  |  |  |  |  |  |

| 14       | P22          | D               | General-purpose input/output port.                                                                          |  |  |  |  |  |  |

|          | TIN1         |                 | Function as an event input pin for reload timer 1. Use the pin by setting as input port.                    |  |  |  |  |  |  |

| 15       | P23          | D               | General-purpose input/output port.                                                                          |  |  |  |  |  |  |

|          | TOT1         |                 | Function as an event output pin for reload timer 1. Valid only when output setting is "enabled."            |  |  |  |  |  |  |

| 16 to 19 | P24 to P27   | D               | General-purpose input/output ports.                                                                         |  |  |  |  |  |  |

|          | INT4 to INT7 |                 | Functions as external interrupt input pins. Use the pins by setting as input port.                          |  |  |  |  |  |  |

| 20       | MD2          | F               | Input pin for specifying operation mode. Connect directly to Vss.                                           |  |  |  |  |  |  |

| 21       | MD1          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |  |  |  |  |

| 22       | MD0          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |  |  |  |  |

| 23       | RST          | В               | External reset input pin.                                                                                   |  |  |  |  |  |  |

| 24       | Vcc          | -               | Power source (5 V) input pin.                                                                               |  |  |  |  |  |  |

| 25       | Vss          | -               | Power source (0 V) input pin.                                                                               |  |  |  |  |  |  |

| 26       | С            | -               | Capacitor pin for stabilizing power source. Connect a ceramic capacitor of approximately 0.1 $\mu\text{F}.$ |  |  |  |  |  |  |

| 27       | X0           | А               | Pin for high-rate oscillation.                                                                              |  |  |  |  |  |  |

| 28       | X1           | А               | Pin for high-rate oscillation.                                                                              |  |  |  |  |  |  |

| 29 to 32 | P10 to P13   | D               | General-purpose input/output ports.                                                                         |  |  |  |  |  |  |

|          | IN0 to IN3   |                 | Functions as trigger input pins of input capture ch.0 to ch.3. Use the pins by setting as input ports.      |  |  |  |  |  |  |

| 33 to 36 | P14 to P17   | G               | General-purpose input/output ports. High-current output ports.                                              |  |  |  |  |  |  |

|          | PPG0 to PPG3 |                 | Functions as output pins of PPG timers 01 and 23. Valid when output setting is "enabled."                   |  |  |  |  |  |  |

| 37       | P40          | D               | General-purpose input/output port.                                                                          |  |  |  |  |  |  |

|          | SIN1         |                 | Serial data input pin for UART. Use the pin by setting as input port.                                       |  |  |  |  |  |  |

| 38       | P41          | D               | General-purpose input/output port.                                                                          |  |  |  |  |  |  |

|          | SCK1         |                 | Serial clock input pin for UART. Valid only when serial clock input/output setting on UART is "enabled."    |  |  |  |  |  |  |

#### Notes When Using No Sub Clock

■ If an oscillator is not connected to X0A and X1A pin, apply pull-down resistor to X0A pin and leave X1A pin open.

#### About Power Supply Pins

- If two or more Vcc and Vss pins exist, the pins that should be at the same potential are connected to each other inside the device. For reducing unwanted emissions and preventing malfunction of strobe signals caused by increase of ground level, however, be sure to connect the Vcc and Vss pins to the power source and the ground externally.

- Pay attention to connect a power supply to Vcc and Vss of MB90385 series device in a lowest-possible impedance.

- Near pins of MB90385 series device, connecting a bypass capacitor is recommended at 0.1 µF across Vcc pin and Vss pin.

#### **Crystal Oscillator Circuit**

- Noises around X0 and X1 pins cause malfunctions on a MB90385 series device. Design a print circuit so that X0 and X1 pins, an crystal oscillator (or a ceramic oscillator), and bypass capacitor to the ground become as close as possible to each other. Furthermore, avoid wires to X0 and X1 pins crossing each other as much as possible.

- Print circuit designing that surrounds X0 and X1 pins with grounding wires, which ensures stable operation, is strongly recommended.

#### Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

#### Sequence of Turning on Power of A/D Converter and Applying Analog Input

- Be sure to turn on digital power (Vcc) before applying signals to the A/D converter and applying analog input signals (AN0 to AN7 pins).

- Be sure to turn off the power of A/D converter and analog input before turning off the digital power source.

- Be sure not to apply AVR exceeding AVcc when turning on and off. (No problems occur if analog and digital power is turned on and off simultaneously.)

#### Handling Pins When A/D Converter is Not Used

■ If the A/D converter is not used, connect the pins under the following conditions: "AVcc=AVR=Vcc," and "AVss=Vss"

#### Note on Turning on Power

For preventing malfunctions on built-in step-down circuit, maintain a minimum of 50 μs of voltage rising time (between 0.2 V and 2.7V) when turning on the power.

#### Stabilization of Supply Voltage

■ A sudden change in the supply voltage may cause the device to malfunction even within the specified Vcc supply voltage operating range. Therefore, the Vcc supply voltage should be stabilized.

For reference, the supply voltage should be controlled so that Vcc ripple variations (peak-to-peak values) at commercial frequencies (50 Hz / 60 Hz) fall below 10% of the standard Vcc supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instantaneous power switching.

| Address                  | Register<br>Abbreviation | Register               | Read/<br>Write    | Resource           | Initial Value                 |

|--------------------------|--------------------------|------------------------|-------------------|--------------------|-------------------------------|

| 003910н                  | PRLL0                    | PPG0 reload register L | R/W               | 8/16-bit PPG timer | XXXXXXXXB                     |

| <b>003911</b> н          | PRLH0                    | PPG0 reload register H | R/W               |                    | XXXXXXXXB                     |

| 003912н                  | PRLL1                    | PPG1 reload register L | R/W               | XXXXXXXXB          |                               |

| 003913н                  | PRLH1                    | PPG1 reload register H | R/W               |                    | XXXXXXXXB                     |

| 003914н                  | PRLL2                    | PPG2 reload register L | R/W               |                    | XXXXXXXXB                     |

| <b>003915</b> н          | PRLH2                    | PPG2 reload register H | R/W               |                    | XXXXXXXXB                     |

| <b>003916</b> н          | PRLL3                    | PPG3 reload register L | R/W               |                    | XXXXXXXX <sub>B</sub>         |

| <b>003917</b> н          | PRLH3                    | PPG3 reload register H | R/W               |                    | XXXXXXXXB                     |

| 003918н<br>to<br>00392Fн |                          |                        | (Reserved area) * |                    |                               |

| 003930н<br>to<br>003BFFн |                          |                        | (Reserved area) * |                    |                               |

| 003C00н<br>to<br>003C0Fн |                          | RAM (                  | General-purpose R | AM)                |                               |

| 003C10н<br>to<br>003C13н | IDR0                     | ID register 0          | R/W               | CAN controller     | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C14н<br>to<br>003C17н | IDR1                     | ID register 1          | R/W               | -                  | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C18н<br>to<br>003C1Bн | IDR2                     | ID register 2          | R/W               | _                  | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C1Cн<br>to<br>003C1Fн | IDR3                     | ID register 3          | R/W               | -                  | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C20н<br>to<br>003C23н | IDR4                     | ID register 4          | R/W               | _                  | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C24н<br>to<br>003C27н | IDR5                     | ID register 5          | R/W               | _                  | XXXXXXXXAB<br>to<br>XXXXXXXXB |

| 003C28н<br>to<br>003C2Bн | IDR6                     | ID register 6          | R/W               | -                  | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C2Cн<br>to<br>003C2Fн | IDR7                     | ID register 7          | R/W               |                    | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C30н,<br>003C31н      | DLCR0                    | DLC register 0         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXB        |

| 003C32н,<br>003C33н      | DLCR1                    | DLC register 1         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXB        |

| 003C34н,<br>003C35н      | DLCR2                    | DLC register 2         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXXB       |

| 003C36н,<br>003C37н      | DLCR3                    | DLC register 3         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXXB       |

| Address                  | Register<br>Abbreviation | Register                           | Read/<br>Write         | Resource               | Initial Value                                    |

|--------------------------|--------------------------|------------------------------------|------------------------|------------------------|--------------------------------------------------|

| 003С38н,<br>003С39н      | DLCR4                    | DLC register 4                     | R/W                    | CAN controller         | XXXXXXXXB,<br>XXXXXXXB                           |

| 003С3Ан,<br>003С3Вн      | DLCR5                    | DLC register 5                     | XXXXXXXXB,<br>XXXXXXXB |                        |                                                  |

| 003C3Cн,<br>003C3Dн      | DLCR6                    | DLC register 6                     |                        | XXXXXXXXB,<br>XXXXXXXB |                                                  |

| 003C3Eн,<br>003C3Fн      | DLCR7                    | DLC register 7                     | R/W                    |                        | XXXXXXXXB,<br>XXXXXXXB                           |

| 003C40н<br>to<br>003C47н | DTR0                     | Data register 0                    | R/W                    |                        | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C48н<br>to<br>003C4Fн | DTR1                     | Data register 1                    | R/W                    |                        | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C50н<br>to<br>003C57н | DTR2                     | Data register 2                    | R/W                    | -                      | XXXXXXXXB<br>to<br>XXXXXXXB                      |

| 003C58н<br>to<br>003C5Fн | DTR3                     | Data register 3                    | R/W                    | _                      | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C60н<br>to<br>003C67н | DTR4                     | Data register 4                    | R/W                    |                        | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C68н<br>to<br>003C6Fн | DTR5                     | Data register 5                    | R/W                    |                        | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C70н<br>to<br>003C77н | DTR6                     | Data register 6                    | R/W                    |                        | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C78н<br>to<br>003C7Fн | DTR7                     | Data register 7                    | R/W                    |                        | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C80н<br>to<br>003CFFн |                          | (Rese                              | rved area) *           |                        |                                                  |

| 003D00н,<br>003D01н      | CSR                      | Control status register            | R/W, R                 | CAN controller         | 0XXXX001в,<br>00XXX000в                          |

| 003D02н                  | LEIR                     | Last event display register        | R/W                    |                        | 000XX000 <sub>B</sub>                            |

| 003D03н                  |                          | (Rese                              | rved area) *           |                        |                                                  |

| 003D04н,<br>003D05н      | RTEC                     | Send/receive error counter         | R                      | CAN controller         | 0000000в,<br>0000000в                            |

| 003D06н,<br>003D07н      | BTR                      | Bit timing register                | R/W                    |                        | 11111111 <sub>в</sub> ,<br>Х1111111 <sub>в</sub> |

| 003D08н                  | IDER                     | IDE register                       | R/W                    |                        | XXXXXXXXB                                        |

| 003D09н                  |                          | (Rese                              | rved area) *           |                        |                                                  |

| 003D0Aн                  | TRTRR                    | Send RTR register                  | R/W                    | CAN controller         | 0000000в                                         |

| 003D0Bн                  |                          | (Rese                              | rved area) *           |                        |                                                  |

| 003D0CH                  | RFWTR                    | Remote frame receive wait register | R/W                    | CAN controller         | XXXXXXXXB                                        |

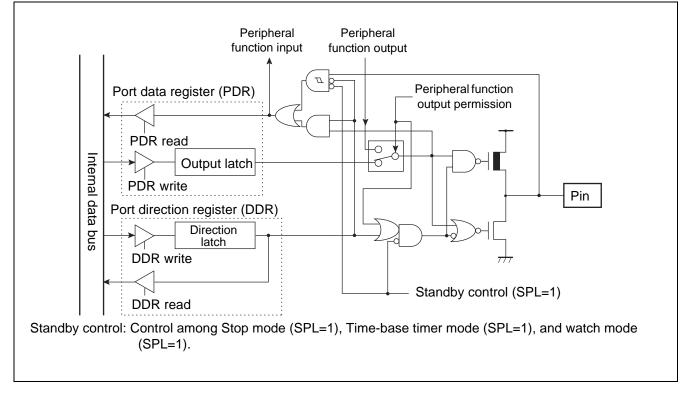

### Port 4 Pins Block Diagram

### **Port 4 Registers**

- Port 4 registers include port 4 data register (PDR4) and port 4 direction register (DDR4).

- The bits configuring the register correspond to port 4 pins on a one-to-one basis.

#### **Relation between Port 4 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |                                           |   |   |     |     |     |      |     |

|-----------|-----------------------------------------|-------------------------------------------|---|---|-----|-----|-----|------|-----|

| Port 4    | PDR4, DDR4                              | PDR4, DDR4 – – – bit4 bit3 bit2 bit1 bit0 |   |   |     |     |     | bit0 |     |

|           | Corresponding pins                      | -                                         | - | - | P44 | P43 | P42 | P41  | P40 |

## MB90387/387S/F387/F387S MB90V495G

#### Watchdog timer control register(WDTC) Watch timer control register (WTC) WRST ERST SRST WTE WT1 WT0 PONR \_\_\_\_ WDCS Watchdog timer 2, Activate Reset occurs \_ Counter Watchdog Shift to sleep mode -----2-bit Internal reset Count clock reset clear control Shift to time-base counter - 6 generation generation selector circuit timer mode circuit circuit Shift to watch mode Clear Shift to stop mode 4 4 Time-base timer counter Main clock $\times 2^2$ × 28 × 29 × 210 × 211 × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> $\times 2^1$ × 215 × 216 × 2<sup>17</sup> $\times 2^{18}$ (dividing HCLK by 2) Watch counter Sub clock $\times 2^2$ × 2<sup>5</sup> $\times 2^{6}$ × 2<sup>8</sup> × 2<sup>9</sup> × 2<sup>10</sup> × 2<sup>11</sup> × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> × 2<sup>15</sup> $\times 2^{1}$ $\times 2^7$ . SCLK HCLK: Oscillation clock SCLK: Sub clock

#### Watchdog Timer Block Diagram

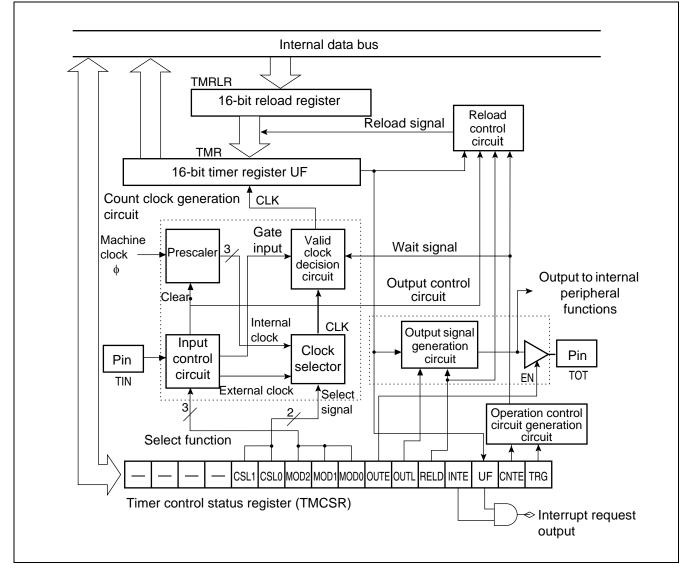

## 16-bit Reload Timer Block Diagram

## 12.7 8/16-bit PPG Timer Outline

The 8/16-bit PPG timer is a 2-channel reload timer module (PPG0 and PPG1) that allows outputting pulses of arbitrary cycle and duty cycle. Combination of the two channels allows selection among the following operations:

- 8-bit PPG output 2-channel independent operation mode

- 16-bit PPG output operation mode

- 8-bit and 8-bit PPG output operation mode

MB90385 series device has two 8/16-bit built-in PPG timers. This section describes functions of PPG0/1. PPG2/3 have the same functions as those of PPG0/1.

#### Functions of 8/16-bit PPG Timer

The 8/16-bit PPG timer is composed of four 8-bit reload register (PRLH0/PRLL0, PRLH1/PRLL1) and two PPG down counters (PCNT0, PCNT1).

- Widths of "H" and "L" in output pulse are specifiable independently. Cycle and duty factor of output pulse is specifiable arbitrarily.

- Count clock is selectable among 6 internal clocks.

- The timer is usable as an interval timer, by generating interrupt requests for each interval.

- The time is usable as a D/A converter, with an external circuit.

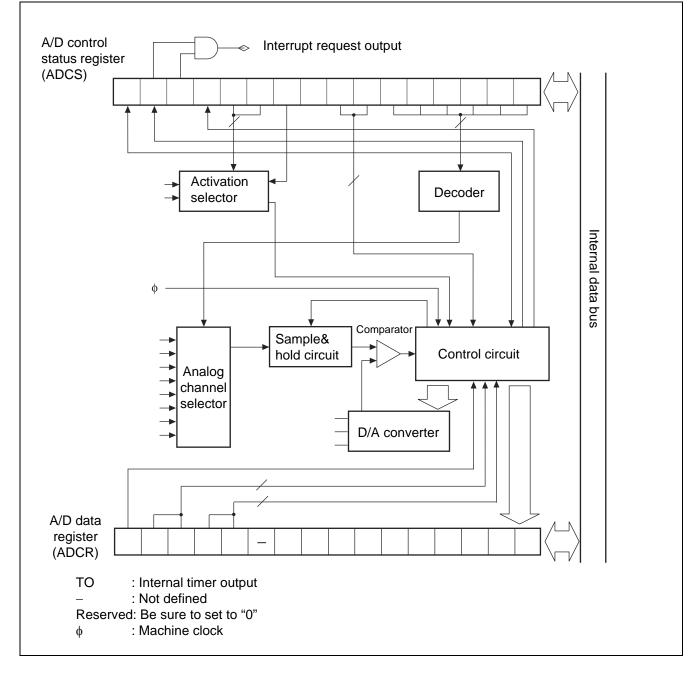

#### 12.10 8/10-bit A/D Converter

The 8/10-bit A/D converter converts an analog input voltage into 8-bit or 10/bit digital value, using the RC-type successive approximation conversion method.

- Input signal is selected among 8 channels of analog input pins.

- Activation trigger is selected among software trigger, internal timer output, and external trigger.

#### Functions of 8/10-bit A/D Converter

The 8/10-bit A/D converter converts an analog voltage (input voltage) input to analog input pin into an 8-bit or 10-bit digital value (A/D conversion).

The 8/10-bit A/D converter has the following functions:

- A/D conversion takes a minimum of 6.12 µs\* for 1 channel, including sampling time. (A/D conversion)

- Sampling of one channel takes a minimum of 2.0 µs\*.

- RC-type successive approximation conversion method, with sample & hold circuit is used for conversion.

- Resolution of either 8 bits or 10 bits is specifiable.

- A maximum of 8 channels of analog input pins are allowed for use.

- Generation of interrupt request is allowed, by storing A/D conversion result in A/D data register.

- Activation of EI<sup>2</sup>OS is allowed upon occurrence of an interrupt request. With use of EI<sup>2</sup>OS, data loss is avoided even if A/D conversion is performed successively.

- An activation trigger is selectable among software trigger, internal timer output, and external trigger (fall edge).

- : When operating with 16 MHz machine clock

#### 8/10-bit A/D Converter Conversion Mode

| Conversion Mode            | Description                                                                                                                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Singular conversion mode   | The A/D conversion is performed form a start channel to an end channel sequentially. Upon completion of A/D conversion on an end channel, A/D conversion function stops.                          |

| Sequential conversion mode | The A/D conversion is performed form a start channel to an end channel sequentially. Upon completion of A/D conversion on an end channel, A/D conversion function resumes from the start channel. |

| Pausing conversion mode    | The A/D conversion is performed by pausing at each channel. Upon completion of A/D conversion on an end channel, A/D conversion and pause functions resume from the start channel.                |

## MB90387/387S/F387/F387S MB90V495G

### 8/10-bit A/D Converter Block Diagram

## Sector Configuration of 512 Kbit Flash Memory

| Flash memory    | CPU address | Writer address* |

|-----------------|-------------|-----------------|

|                 | FF0000H     | 70000н          |

| SA0 (32 Kbytes) |             |                 |

|                 | FF7FFFH     | 77FFFH          |

|                 | FF8000H     | 78000н          |

| SA1 (8 Kbytes)  |             |                 |

|                 | FF9FFFH     | 79FFFH          |

|                 | FFA000H     | 7А000н          |

| SA2 (8 Kbytes)  |             |                 |

|                 | FFBFFFH     | 7BFFFH          |

|                 | FFC000H     | 7С000н          |

| SA3 (16 Kbytes) |             |                 |

|                 | FFFFFH      | 7FFFFH          |

\*: "Writer address" is an address equivalent to CPU address, which is used when data is written on Flash memory, using parallel writer. When writing/ deleting data with general-purpose writer, the writer address is used for writing and deleting.

| Deremeter                   | Symbol | Pin Name                                      | Conditions                                                                                                  |     | Value |     | Unit | Remarks                                                         |

|-----------------------------|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|-----------------------------------------------------------------|

| Parameter                   | Symbol | Pin Name                                      | Conditions                                                                                                  | Min | Тур   | Max | Unit | Remarks                                                         |

| Power<br>supply<br>current* | lcc∟   | Vcc                                           | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>subclock operation,                                       | _   | 0.3   | 1.2 | mA   | MB90F387/S                                                      |

| 000                         |        |                                               | $T_A = +25^{\circ}C$                                                                                        |     | 40    | 100 | μΑ   | MB90387/S                                                       |

|                             | ICCLS  |                                               | $V_{CC} = 5.0 V$ ,<br>Internally operating at 8 kHz,<br>subclock,<br>sleep mode,<br>$T_{A} = + 25^{\circ}C$ | _   | 10    | 30  | μA   |                                                                 |

|                             | Ісст   |                                               | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>watch mode,<br>$T_A = + 25^{\circ}C$                      |     | 8     | 25  | μΑ   |                                                                 |

|                             | Іссн   |                                               | Stopping,<br>T <sub>A</sub> = + 25°C                                                                        | _   | 5     | 20  | μΑ   |                                                                 |

| Input<br>capacity           | CIN    | Other than AVcc,<br>AVss, AVR, C, Vcc,<br>Vss | -                                                                                                           | _   | 5     | 15  | pF   |                                                                 |

| Pull-up<br>resistor         | Rup    | RST                                           | -                                                                                                           | 25  | 50    | 100 | kΩ   |                                                                 |

| Pull-down<br>resistor       | Rdown  | MD2                                           | -                                                                                                           | 25  | 50    | 100 | kΩ   | Flash product is<br>not provided<br>with pull-down<br>resistor. |

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 \circ C to +105 \circ C)$

\*: Test conditions of power supply current are based on a device using external clock.

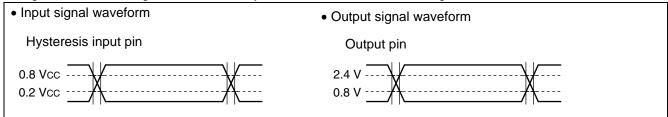

Rating values of alternating current is defined by the measurement reference voltage values shown below:

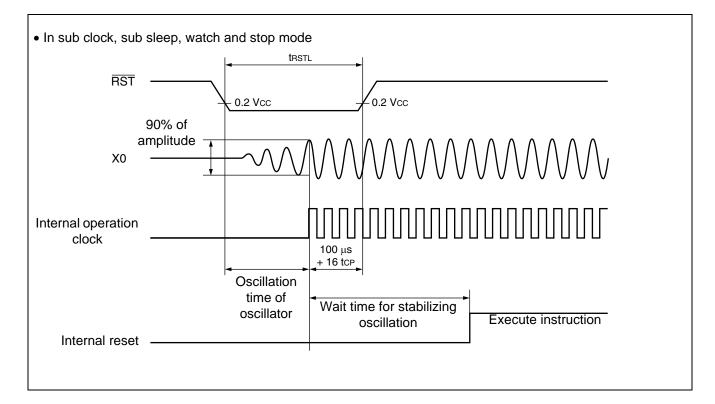

#### 13.4.2 Reset Input Timing

| Parameter        | eter Symbol Pin Name Value |     |                                                                                | Unit    | Remarks |                                                                                                |

|------------------|----------------------------|-----|--------------------------------------------------------------------------------|---------|---------|------------------------------------------------------------------------------------------------|

| Falameter        | Symbol                     |     | Min                                                                            | lin Max |         | Reillarks                                                                                      |

| Reset input time | <b>t</b> RSTL              | RST | 16 tce*3                                                                       | -       | ns      | Normal operation                                                                               |

|                  |                            |     | Oscillation time of oscillator <sup>*1</sup> + $100 \ \mu s$ + $16 \ tcP^{*3}$ | -       |         | In sub clock <sup>*2</sup> , sub<br>sleep <sup>*2</sup> , watch <sup>*2</sup> and<br>stop mode |

|                  |                            |     | 100                                                                            | _       | μS      | In timebase timer                                                                              |

\*1: Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

\*2: Except for MB90F387S and MB90387S.

\*3: Refer to "(1) Clock timing" ratings for tcp (internal operation clock cycle time).

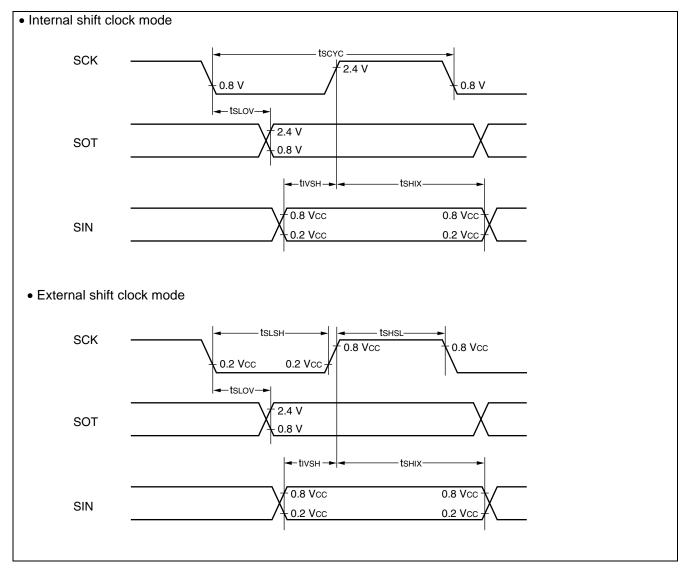

### 13.4.4 UART Timing

| Parameter                                      | Symbol Pin Name |               | Conditions                              | Va      | lue | Unit | Remarks |

|------------------------------------------------|-----------------|---------------|-----------------------------------------|---------|-----|------|---------|

| Falameter                                      | Symbol          |               | Conditions                              | Min     | Max | Unit | Remarks |

| Serial clock cycle time                        | tscyc           | SCK1          | Internal shift clock                    | 4 tcp * | -   | ns   |         |

| $SCK \downarrow \to SOT$ delay time            | <b>t</b> slov   | SCK1,<br>SOT1 | mode output pin is: CL<br>= 80 pF+1TTL. | -80     | +80 | ns   |         |

| Valid SIN $\rightarrow$ SCK $\uparrow$         | <b>t</b> ivsh   | SCK1, SIN1    |                                         | 100     | -   | ns   |         |

| SCK $\uparrow \rightarrow$ valid SIN hold time | tsнix           | SCK1, SIN1    |                                         | 60      | -   | ns   |         |

| Serial clock "H" pulse width                   | <b>t</b> shsl   | SCK1          | External shift clock                    | 2 tcp * | -   | ns   |         |

| Serial clock "L" pulse width                   | tslsh           | SCK1          | mode output pin is: CL<br>= 80 pF+1TTL. | 2 tcp * | -   | ns   |         |

| $SCK \downarrow \to SOT$ delay time            | tslov           | SCK1,<br>SOT1 |                                         | -       | 150 | ns   |         |

| Valid SIN $\rightarrow$ SCK $\uparrow$         | <b>t</b> ivsh   | SCK1, SIN1    |                                         | 60      | -   | ns   |         |

| SCK $\uparrow \rightarrow$ valid SIN hold time | tsнix           | SCK1, SIN1    |                                         | 60      | _   | ns   |         |

### (Vcc = 4.5 V to 5.5 V, Vss = 0.0 V, T\_A = -40 °C to +105 °C)

\*: Refer to Clock Timing ratings for  $t_{\mbox{\tiny CP}}$  (internal operation clock cycle time).

Notes:

■ AC Characteristics in CLK synchronous mode.

$\blacksquare$  C<sub>L</sub> is a load capacitance value on pins for testing.

13.4.5 Timer Input Timing

$(V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}, \text{ Vss} = 0.0 \text{ V}, \text{ T}_{A} = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C})$

| Parameter         | Symbol | Pin Name   | Conditions | Value  |     | Unit | Remarks |

|-------------------|--------|------------|------------|--------|-----|------|---------|

| Falameter         | Symbol | Finite     | Conditions | Min    | Max | Onit | Remains |

| Input pulse width | tтіwн  | TIN0, TIN1 | -          | 4 tcp* | -   | ns   |         |

|                   | t⊤ıw∟  | IN0 to IN3 |            |        |     |      |         |

\*: Refer to Clock Timing ratings for tcp (internal operation clock cycle time).

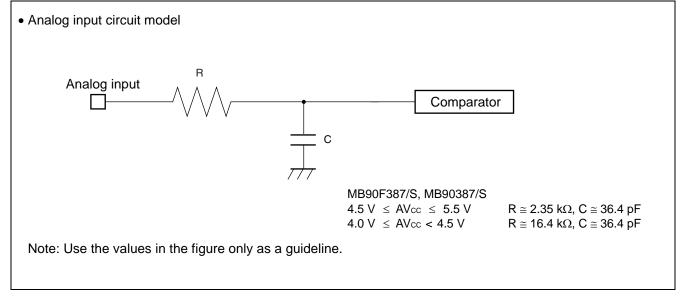

## 13.7 Notes on A/D Converter Section

Use the device with external circuits of the following output impedance for analog inputs:

Recommended output impedance of external circuits are: Approx. 3.9 k $\Omega$  or lower (4.5 V  $\leq$  AVcc  $\leq$  5.5 V) (sampling period=2.00  $\mu$ s at 16 MHz machine clock), Approx. 11 k $\Omega$  or lower (4.0 V  $\leq$  AVcc < 4.5 V) (sampling period=8.0  $\mu$ s at 16 MHz machine clock).

If an external capacitor is used, in consideration of the effect by tap capacitance caused by external capacitors and on-chip capacitors, capacitance of the external one is recommended to be several thousand times as high as internal capacitor.

If output impedance of an external circuit is too high, a sampling period for an analog voltage may be insufficient.

#### About errors

As [AVR-AVss] become smaller, values of relative errors grow larger.

### 13.8 Flash Memory Program/Erase Characteristics

| Parameter                               | Conditions                                                                       |        | Value |       | Unit  | Remarks                                      |

|-----------------------------------------|----------------------------------------------------------------------------------|--------|-------|-------|-------|----------------------------------------------|

| Falameter                               | Conditions                                                                       | Min    | Тур   | Max   | Onit  | Remarks                                      |

| Sector erase time                       | $\begin{array}{l} T_{\text{A}}=+~25~^{\circ}C\\ V_{\text{CC}}=5.0~V \end{array}$ | -      | 1     | 15    | S     | Excludes 00H programming<br>prior to erasure |

| Chip erase time                         |                                                                                  | -      | 4     | -     | S     | Excludes 00H programming<br>prior to erasure |

| Word (16-bit width)<br>programming time |                                                                                  | -      | 16    | 3,600 | μS    | Except for the over head time of the system  |

| Program/Erase cycle                     | _                                                                                | 10,000 | -     | -     | cycle |                                              |

| Flash Data Retention Time               | Average<br>T <sub>A</sub> = + 85 °C                                              | 20     | -     | -     | Year  | *                                            |

\*: This value comes from the technology qualification (using Arrhenius equation to translate high temperature measurements into normalized value at + 85 °C).

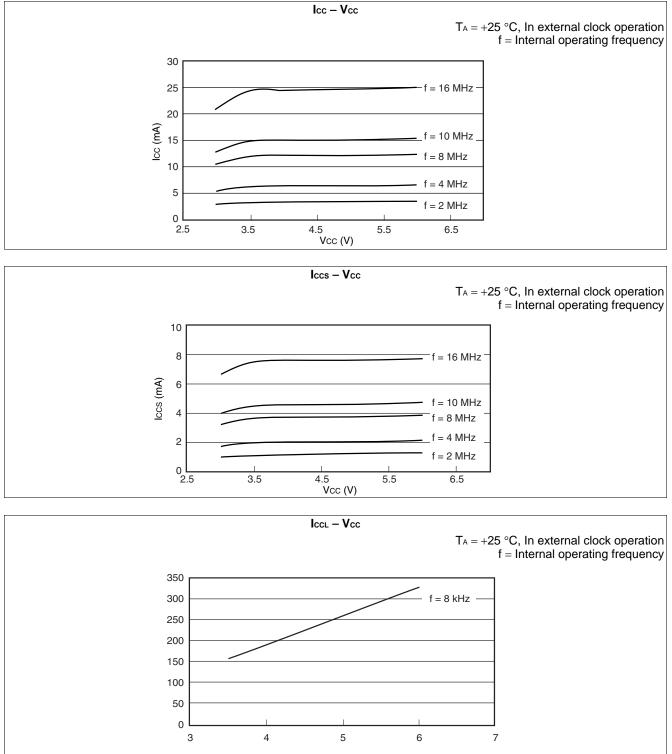

## 14. Example Characteristics

## MB90F387

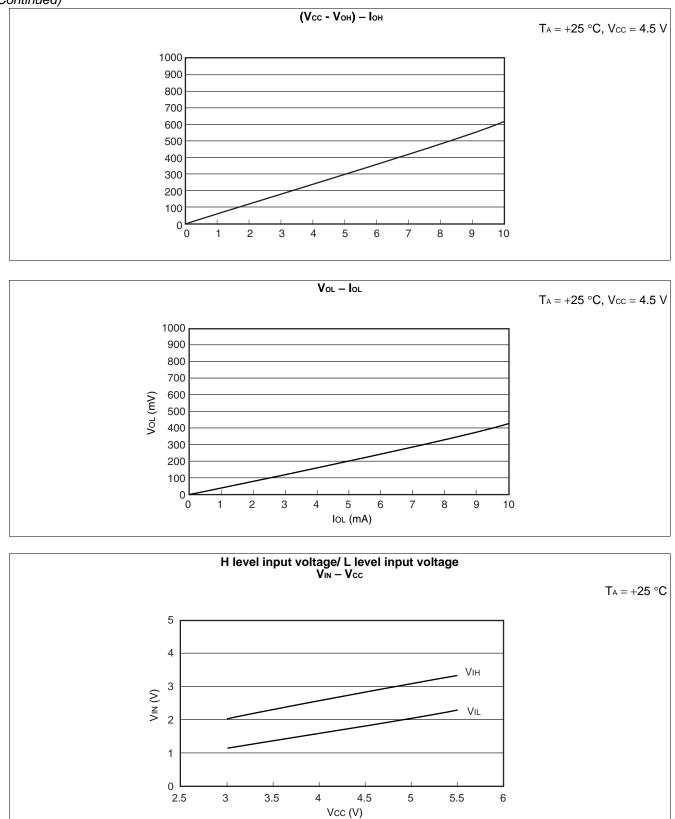

(Continued)

## MB90387/387S/F387/F387S MB90V495G

#### (Continued)

## **Document History**

| Document Title: MB90387/387S/F387/F387S, MB90V495G, 16-bit Microcontrollers F <sup>2</sup> MC-16LX MB90385 Series<br>Document Number:002-07765 |         |                    |                    |                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|

| Revision                                                                                                                                       | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |

| **                                                                                                                                             | _       | AKIH               | 12/19/2008         | Migrated to Cypress and assigned document number 002-07765.<br>No change to document contents or format. |

| *A                                                                                                                                             | 6059071 | SSAS               | 02/05/2018         | Updated to Cypress template<br>Package: FPT-48P-M26> LQA048                                              |