Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| urchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f387pmt-gs-n2e1 |

|---------------------------|--------------------------------------------------------------------------------|

| upplier Device Package    | 48-LQFP (7x7)                                                                  |

| ackage / Case             | 48-LQFP                                                                        |

| ounting Type              | Surface Mount                                                                  |

| perating Temperature      | -40°C ~ 105°C (TA)                                                             |

| scillator Type            | External                                                                       |

| ata Converters            | A/D 8x8/10b                                                                    |

| oltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                    |

| AM Size                   | 2K x 8                                                                         |

| PROM Size                 | -                                                                              |

| ogram Memory Type         | FLASH                                                                          |

| ogram Memory Size         | 64KB (64K x 8)                                                                 |

| mber of I/O               | 34                                                                             |

| ipherals                  | POR, WDT                                                                       |

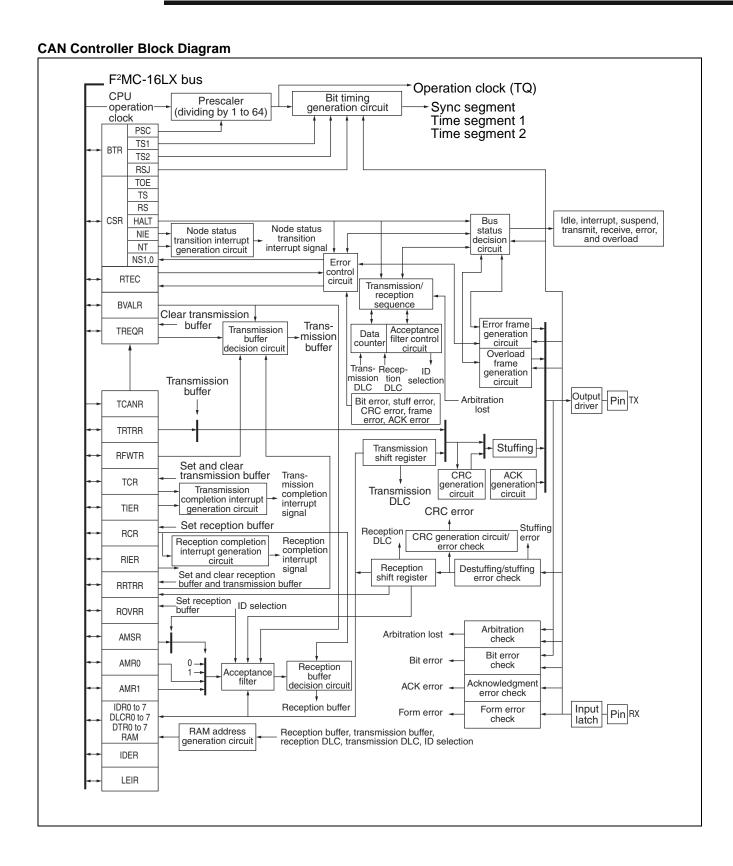

| nnectivity                | CANbus, SCI, UART/USART                                                        |

| eed                       | 16MHz                                                                          |

| re Size                   | 16-Bit                                                                         |

| ore Processor             | F <sup>2</sup> MC-16LX                                                         |

| oduct Status              | Obsolete                                                                       |

| etails                    |                                                                                |

# DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

■ Module for activation of expanded intelligent I/O service (El²OS), and generation of external interrupt.

#### **Delay Interrupt Generator Module**

■ Generates interrupt request for task switching.

#### 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 µs (at 16 MHz machine clock, including sampling time)

# **Program Patch Function**

■ Address matching detection for 2 address pointers.

Document Number: 002-07765 Rev. \*A Page 2 of 81

# 1. Product Lineup

| Parameter                        | Part Number           | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                          | MB90387<br>MB90387S                                                                           | MB90V495G                             |  |  |

|----------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|--|--|

| Classification                   |                       | Flash ROM                                                                                                                                                                                                                                                                      | Mask ROM                                                                                      | Evaluation product                    |  |  |

| ROM capacity                     |                       | 64 Kby                                                                                                                                                                                                                                                                         | _                                                                                             |                                       |  |  |

| RAM capacity                     |                       | 2 Kbytes 6 Kbytes                                                                                                                                                                                                                                                              |                                                                                               |                                       |  |  |

| Process                          |                       |                                                                                                                                                                                                                                                                                | CMOS                                                                                          | <u> </u>                              |  |  |

| Package                          |                       | LQFP-48 (pin pit                                                                                                                                                                                                                                                               | ch 0.50 mm)                                                                                   | PGA-256                               |  |  |

| Operating powe                   | r supply voltage      | 3.5 V to 5                                                                                                                                                                                                                                                                     | 5.5 V                                                                                         | 4.5 V to 5.5 V                        |  |  |

| Special power s<br>emulator*1    | upply for             | -                                                                                                                                                                                                                                                                              |                                                                                               | None                                  |  |  |

| CPU functions                    |                       | Number of basic instructions<br>Instruction bit length<br>Instruction length<br>Data bit length                                                                                                                                                                                | : 351 instructions<br>: 8 bits and 16 bits<br>: 1 byte to 7 bytes<br>: 1 bit, 8 bits, 16 bits |                                       |  |  |

|                                  |                       | Minimum instruction execution til                                                                                                                                                                                                                                              |                                                                                               |                                       |  |  |

|                                  |                       | Interrupt processing time: 1.5 μs                                                                                                                                                                                                                                              | •                                                                                             | · · · · · · · · · · · · · · · · · · · |  |  |

| Low power cons<br>(standby) mode |                       | Sleep mode / Watch mode / Time                                                                                                                                                                                                                                                 | e-base timer mode / Stop mo                                                                   | ode / CPU intermittent                |  |  |

| I/O port                         |                       | General-purpose input/output ports (CMOS output): 34 ports (36 ports*2) including 4 high-current output ports (P14 to P17)                                                                                                                                                     |                                                                                               |                                       |  |  |

| Time-base timer                  |                       | 18-bit free-run counter<br>Interrupt cycle: 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms<br>(with oscillation clock frequency at 4 MHz)                                                                                                                                           |                                                                                               |                                       |  |  |

| Watchdog timer                   |                       | Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (with oscillation clock frequency at 4 MHz)                                                                                                                                                                     |                                                                                               |                                       |  |  |

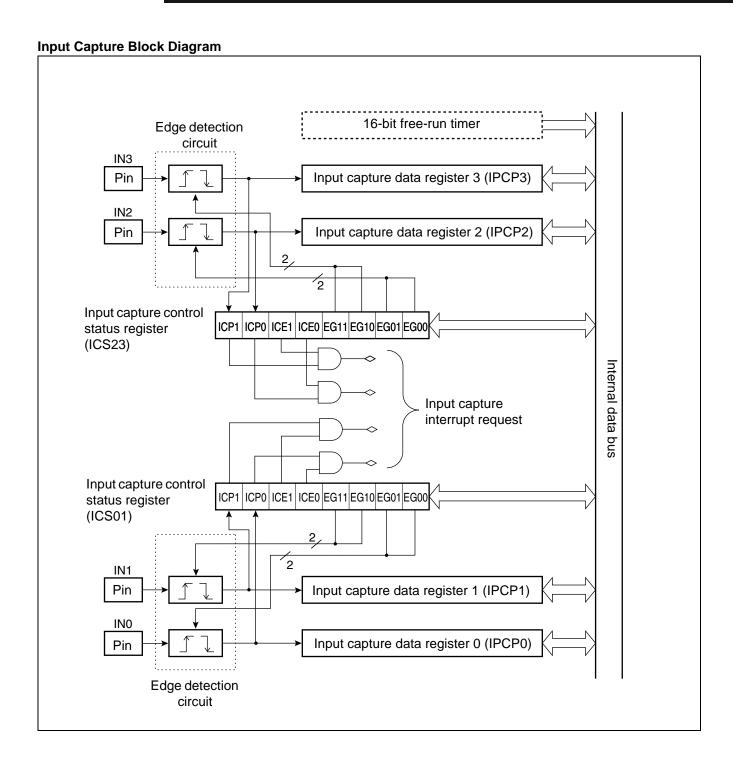

| 16-bit input/<br>output timer    | 16-bit free-run timer | Number of channels: 1<br>Interrupt upon occurrence of overflow                                                                                                                                                                                                                 |                                                                                               |                                       |  |  |

|                                  | Input capture         | Number of channels: 4<br>Retaining free-run timer value set                                                                                                                                                                                                                    | t by pin input (rising edge, fall                                                             | ing edge, and both edges)             |  |  |

| 16-bit reload timer              |                       | Number of channels: 2<br>16-bit reload timer operation<br>Count clock cycle: 0.25 μs, 0.5 μs, 2.0 μs<br>(at 16-MHz machine clock frequency)<br>External event count is allowed.                                                                                                |                                                                                               |                                       |  |  |

| Watch timer                      |                       | 15-bit free-run counter<br>Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s<br>(with 8.192 kHz sub clock)                                                                                                                                               |                                                                                               |                                       |  |  |

| 8/16-bit PPG tim                 | ner                   | Number of channels: 2 (four 8-bit channels are available also.) PPG operation is allowed with four 8-bit channels or two 16-bit channels. Outputting pulse wave of arbitrary cycle or arbitrary duty is allowed. Count clock: 62.5 ns to 1 $\mu s$ (with 16 MHz machine clock) |                                                                                               |                                       |  |  |

| Delay interrupt of               | generator module      | Interrupt generator module for task switching. Used for realtime OS.                                                                                                                                                                                                           |                                                                                               |                                       |  |  |

| DTP/External in                  | terrupt               | Number of inputs: 4 Activated by rising edge, falling edge, "H" level or "L" level input. External interrupt or expanded intelligent I/O service (EI <sup>2</sup> OS) is available.                                                                                            |                                                                                               |                                       |  |  |

Document Number: 002-07765 Rev. \*A Page 4 of 81

# 5. Pin Description

| Pin No.  | Pin Name     | Circuit<br>Type | Function                                                                                                    |  |  |

|----------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------|--|--|

| 1        | AVcc         | _               | Vcc power input pin for A/D converter.                                                                      |  |  |

| 2        | AVR          | _               | Power (Vref+) input pin for A/D converter. Use as input for Vcc or lower.                                   |  |  |

| 3 to 10  | P50 to P57   | Е               | General-purpose input/output ports.                                                                         |  |  |

|          | AN0 to AN7   |                 | Functions as analog input pins for A/D converter. Valid when analog input setting is "enabled."             |  |  |

| 11       | P37          | D               | General-purpose input/output port.                                                                          |  |  |

|          | ADTG         |                 | Function as an external trigger input pin for A/D converter. Use the pin by setting as input port.          |  |  |

| 12       | P20          | D               | General-purpose input/output port.                                                                          |  |  |

|          | TIN0         |                 | Function as an event input pin for reload timer 0. Use the pin by setting as input port.                    |  |  |

| 13       | P21          | D               | General-purpose input/output port.                                                                          |  |  |

|          | ТОТ0         |                 | Function as an event output pin for reload timer 0. Valid only when output setting is "enabled."            |  |  |

| 14       | P22          | D               | General-purpose input/output port.                                                                          |  |  |

|          | TIN1         |                 | Function as an event input pin for reload timer 1. Use the pin by setting as input port.                    |  |  |

| 15       | P23          | D               | General-purpose input/output port.                                                                          |  |  |

|          | TOT1         |                 | Function as an event output pin for reload timer 1. Valid only when output setting is "enabled."            |  |  |

| 16 to 19 | P24 to P27   | D               | General-purpose input/output ports.                                                                         |  |  |

|          | INT4 to INT7 |                 | Functions as external interrupt input pins. Use the pins by setting as input port.                          |  |  |

| 20       | MD2          | F               | Input pin for specifying operation mode. Connect directly to Vss.                                           |  |  |

| 21       | MD1          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |

| 22       | MD0          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |

| 23       | RST          | В               | External reset input pin.                                                                                   |  |  |

| 24       | Vcc          | _               | Power source (5 V) input pin.                                                                               |  |  |

| 25       | Vss          | _               | Power source (0 V) input pin.                                                                               |  |  |

| 26       | С            | _               | Capacitor pin for stabilizing power source. Connect a ceramic capacitor of approximately 0.1 $\mu\text{F}.$ |  |  |

| 27       | X0           | Α               | Pin for high-rate oscillation.                                                                              |  |  |

| 28       | X1           | Α               | Pin for high-rate oscillation.                                                                              |  |  |

| 29 to 32 | P10 to P13   | D               | General-purpose input/output ports.                                                                         |  |  |

|          | IN0 to IN3   |                 | Functions as trigger input pins of input capture ch.0 to ch.3. Use the pins by setting as input ports.      |  |  |

| 33 to 36 | P14 to P17   | G               | General-purpose input/output ports. High-current output ports.                                              |  |  |

|          | PPG0 to PPG3 |                 | Functions as output pins of PPG timers 01 and 23. Valid when output setting is "enabled."                   |  |  |

| 37       | P40          | D               | General-purpose input/output port.                                                                          |  |  |

|          | SIN1         |                 | Serial data input pin for UART. Use the pin by setting as input port.                                       |  |  |

| 38       | P41          | D               | General-purpose input/output port.                                                                          |  |  |

|          | SCK1         |                 | Serial clock input pin for UART. Valid only when serial clock input/output setting on UART is "enabled."    |  |  |

Document Number: 002-07765 Rev. \*A Page 7 of 81

# 6. I/O Circuit Type

| Туре | Circuit                                                                                                                  | Remarks                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| A    | X1<br>X1A<br>X0<br>X0A  Standby control signal                                                                           | <ul> <li>High-rate oscillation feedback resistor, approx.1 MΩ</li> <li>Low-rate oscillation feedback resistor, approx.10 MΩ</li> </ul> |

| В    | R R Hysteresis input                                                                                                     | <ul> <li>■ Hysteresis input with pull-up resistor.</li> <li>■ Pull-up resistor, approx.50 kΩ</li> </ul>                                |

| С    | R                                                                                                                        | ■ Hysteresis input                                                                                                                     |

| D    | P-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  Standby control | <ul> <li>■ CMOS hysteresis input</li> <li>■ CMOS level output</li> <li>■ Standby control provided</li> </ul>                           |

| E    | P-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  Standby control  Analog input        | ■ CMOS hysteresis input ■ CMOS level output ■ Shared for analog input pin ■ Standby control provided                                   |

| Туре | Circuit                                                                                                 | Remarks                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | R                                                                                                       | <ul> <li>Hysteresis input with pull-down resistor</li> <li>Pull-down resistor, approx. 50 kΩ</li> <li>Flash product is not provided with pull-down resistor.</li> </ul> |

|      | R                                                                                                       | Tedition.                                                                                                                                                               |

| G    | P-ch High-current output  High-current output  N-ch  N-ch  Vss  CMOS  hysteresis input  Standby control | <ul> <li>■ CMOS hysteresis input</li> <li>■ CMOS level output (high-current output)</li> <li>■ Standby control provided</li> </ul>                                      |

# 7. Handling Devices

## Do Not Exceed Maximum Rating (preventing "latch up")

- On a CMOS IC, latch-up may occur when applying a voltage higher than Vcc or a voltage lower than Vss to input or output pin, which has no middle or high withstand voltage. Latch-up may also occur when a voltage exceeding maximum rating is applied across Vcc pin and Vss pin.

- Latch-up causes drastic increase of power current, which may lead to destruction of elements by heat. Extreme caution must be taken not to exceed maximum rating.

- When turning on and off analog power source, take extra care not to apply an analog power voltages (AVcc and AVR) and analog input voltage that are higher than digital power voltage (Vcc).

#### **Handling Unused Pins**

Leaving unused input pins open may cause permanent destruction by malfunction or latch-up. Apply pull-up or pull-down process to the unused pins using resistors of 2 kΩ or higher. Leave unused input/output pins open under output status, or process as input pins if they are under input status.

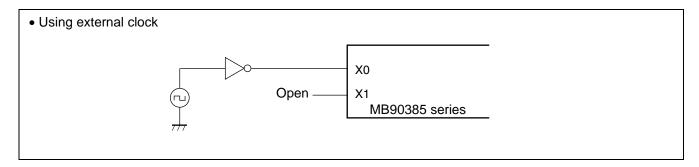

#### **Using External Clock**

■ When using an external clock, drive only X0 pin and leave X1 pin open. An example of using an external clock is shown below.

Document Number: 002-07765 Rev. \*A

## **Notes When Using No Sub Clock**

■ If an oscillator is not connected to X0A and X1A pin, apply pull-down resistor to X0A pin and leave X1A pin open.

#### **About Power Supply Pins**

- If two or more Vcc and Vss pins exist, the pins that should be at the same potential are connected to each other inside the device. For reducing unwanted emissions and preventing malfunction of strobe signals caused by increase of ground level, however, be sure to connect the Vcc and Vss pins to the power source and the ground externally.

- Pay attention to connect a power supply to Vcc and Vss of MB90385 series device in a lowest-possible impedance.

- Near pins of MB90385 series device, connecting a bypass capacitor is recommended at 0.1 μF across Vcc pin and Vss pin.

## **Crystal Oscillator Circuit**

- Noises around X0 and X1 pins cause malfunctions on a MB90385 series device. Design a print circuit so that X0 and X1 pins, an crystal oscillator (or a ceramic oscillator), and bypass capacitor to the ground become as close as possible to each other. Furthermore, avoid wires to X0 and X1 pins crossing each other as much as possible.

- Print circuit designing that surrounds X0 and X1 pins with grounding wires, which ensures stable operation, is strongly recommended.

#### Caution on Operations during PLL Clock Mode

■ If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

#### Sequence of Turning on Power of A/D Converter and Applying Analog Input

- Be sure to turn on digital power (Vcc) before applying signals to the A/D converter and applying analog input signals (AN0 to AN7 pins).

- Be sure to turn off the power of A/D converter and analog input before turning off the digital power source.

- Be sure not to apply AVR exceeding AVcc when turning on and off. (No problems occur if analog and digital power is turned on and off simultaneously.)

#### Handling Pins When A/D Converter is Not Used

■ If the A/D converter is not used, connect the pins under the following conditions: "AVcc=AVR=Vcc," and "AVss=Vss"

#### Note on Turning on Power

■ For preventing malfunctions on built-in step-down circuit, maintain a minimum of 50 μs of voltage rising time (between 0.2 V and 2.7V) when turning on the power.

#### Stabilization of Supply Voltage

■ A sudden change in the supply voltage may cause the device to malfunction even within the specified Vcc supply voltage operating range. Therefore, the Vcc supply voltage should be stabilized.

For reference, the supply voltage should be controlled so that  $V_{cc}$  ripple variations (peak-to-peak values) at commercial frequencies (50 Hz / 60 Hz) fall below 10% of the standard  $V_{cc}$  supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instantaneous power switching.

Document Number: 002-07765 Rev. \*A Page 11 of 81

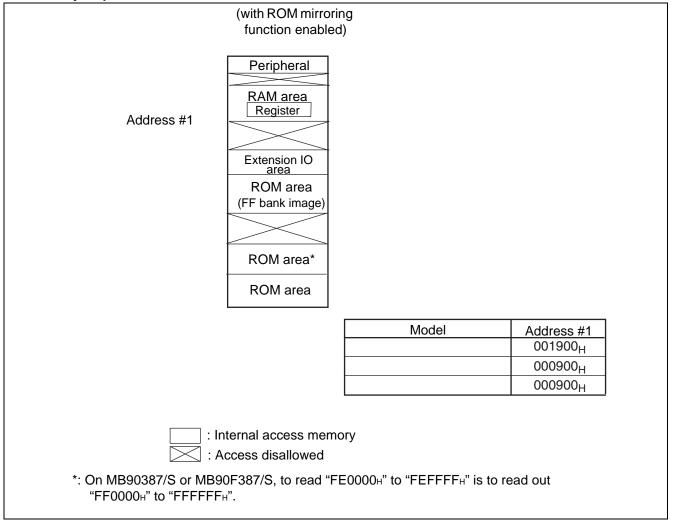

## 9.2 Memory Map

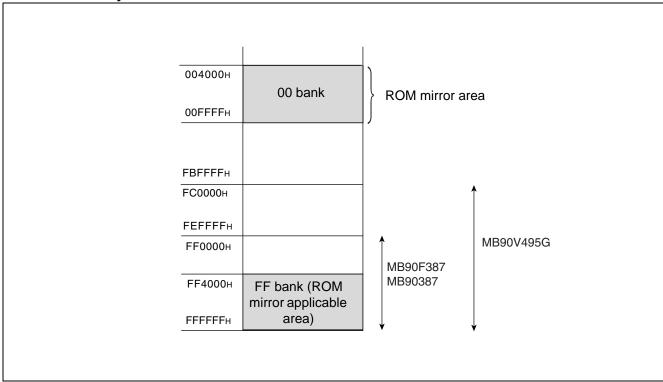

Note: When internal ROM is operating, F<sup>2</sup>MC-16LX allows viewing ROM data image on FF bank at upper-level of 00 bank. This function is called "mirroring ROM," which allows effective use of C compiler small model.

F<sup>2</sup>MC-16LX assigns the same low order 16-bit address to FF bank and 00 bank, which allows referencing table in ROM without specifying "far" using pointer.

For example, when accessing to "00C000H", ROM data at "FFC000H" is accessed actually. However, because ROM area of FF bank exceeds 48 Kbytes, viewing all areas is not possible on 00 bank image. Because ROM data of "FF4000H" to "FFFFFH" is viewed on "004000H" to "00FFFFH" image, store a ROM data table in area "FF4000H" to "FFFFFFH."

| Address                  | Register<br>Abbreviation | Register                           | Read/<br>Write | Resource       | Initial Value                                    |

|--------------------------|--------------------------|------------------------------------|----------------|----------------|--------------------------------------------------|

| 003С38н,<br>003С39н      | DLCR4                    | DLC register 4                     | R/W            | CAN controller | XXXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub> |

| 003С3Ан,<br>003С3Вн      | DLCR5                    | DLC register 5                     | R/W            |                | XXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub>  |

| 003С3Сн,<br>003С3Dн      | DLCR6                    | DLC register 6                     | R/W            |                | XXXXXXX <sub>B</sub> ,<br>XXXXXXX <sub>B</sub>   |

| 003С3Ен,<br>003С3Fн      | DLCR7                    | DLC register 7                     | R/W            |                | XXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub>  |

| 003С40н<br>to<br>003С47н | DTR0                     | Data register 0                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С48н<br>to<br>003С4Fн | DTR1                     | Data register 1                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С50н<br>to<br>003С57н | DTR2                     | Data register 2                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С58н<br>to<br>003С5Fн | DTR3                     | Data register 3                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С60н<br>to<br>003С67н | DTR4                     | Data register 4                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С68н<br>to<br>003С6Fн | DTR5                     | Data register 5                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXB                       |

| 003С70н<br>to<br>003С77н | DTR6                     | Data register 6                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С78н<br>to<br>003С7Fн | DTR7                     | Data register 7                    | R/W            |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С80н<br>to<br>003СFFн |                          | (Reser                             | rved area) *   |                |                                                  |

| 003D00н,<br>003D01н      | CSR                      | Control status register            | R/W, R         | CAN controller | 0XXXX001в,<br>00XXX000в                          |

| 003D02н                  | LEIR                     | Last event display register        | R/W            | 1              | 000ХХ000в                                        |

| 003D03н                  |                          | (Reser                             | rved area) *   | •              | •                                                |

| 003D04н,<br>003D05н      | RTEC                     | Send/receive error counter         | R              | CAN controller | 0000000в,<br>0000000в                            |

| 003D06н,<br>003D07н      | BTR                      | Bit timing register                | R/W            |                | 11111111в,<br>X1111111в                          |

| 003D08н                  | IDER                     | IDE register                       | R/W            |                | XXXXXXXXB                                        |

| 003D09н                  |                          | (Reser                             | rved area) *   | •              | •                                                |

| 003D0Ан                  | TRTRR                    | Send RTR register                  | R/W            | CAN controller | 0000000В                                         |

| 003D0Вн                  |                          | (Reser                             | rved area) *   |                |                                                  |

| 003D0Сн                  | RFWTR                    | Remote frame receive wait register | R/W            | CAN controller | XXXXXXXX                                         |

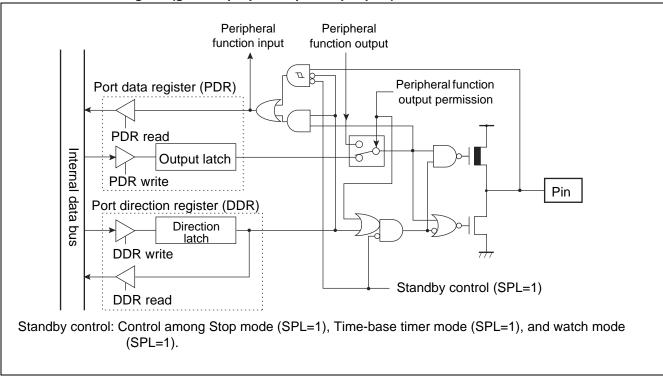

# Port 3 Pins Block Diagram (general-purpose input/output port)

## **Port 3 Registers**

- Port 3 registers include port 3 data register (PDR3) and port 3 direction register (DDR3).

- The bits configuring the register correspond to port 3 pins on a one-to-one basis.

# **Relation between Port 3 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 3    | PDR3, DDR3                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P37  | P36* | P35* | -    | P33  | P32  | P31  | P30  |

<sup>\*:</sup> P35 and P36 do not exist on MB90387and MB90F387.

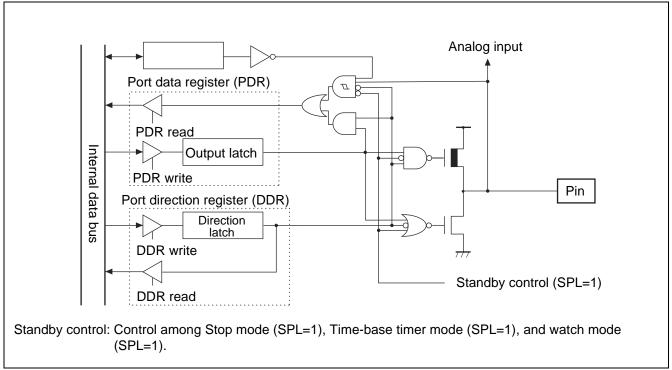

# Port 5 Pins Block Diagram

# **Port 5 Registers**

- Port 5 registers include port 5 data register (PDR5), port 5 direction register (DDR5), and analog input permission register (ADER).

- Analog input permission register (ADER) allows or disallows input of analog signal to the analog input pin.

- The bits configuring the register correspond to port 5 pins on a one-to-one basis.

## Relation between Port 5 Registers and Pins

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 5    | PDR5, DDR5                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | ADER                                    | ADE7 | ADE6 | ADE5 | ADE4 | ADE3 | ADE2 | ADE1 | ADE0 |

|           | Corresponding pins                      | P57  | P56  | P55  | P54  | P53  | P52  | P51  | P50  |

## 12.6 Watch Timer Outline

The watch timer is a 15-bit free-run counter that increments in synchronization with sub clock.

- Interval time is selectable among 7 choices, and generation of interrupt request is allowed for each interval.

- Provides operation clock to the subclock oscillation stabilizing wait timer and watchdog timer.

- Always uses subclock as a count clock regardless of settings of clock selection register (CKSCR).

#### **Interval Timer Function**

- In the watch timer, a bit corresponding to the interval time overflows (carry-over) when an interval time, which is specified by interval time selection bit, is reached. Then overflow flag bit is set (WTC: WTOF=1).

- If an interrupt by overflow is permitted (WTC: WTIE=1), an interrupt request is generated upon setting an overflow flag bit.

- Interval time of watch timer is selectable among the following seven choices:

#### **Interval Time of Watch Timer**

| Sub Clock Cycle | Interval Time                 |

|-----------------|-------------------------------|

| 1/SCLK (122 μs) | 28/SCLK (31.25 ms)            |

|                 | 2º/SCLK (62.5 ms)             |

|                 | 210/SCLK (125 ms)             |

|                 | 211/SCLK (250 ms)             |

|                 | 212/SCLK (500 ms)             |

|                 | 213/SCLK (1.0 s)              |

|                 | 2 <sup>14</sup> /SCLK (2.0 s) |

SCLK: Sub clock frequency

Values in parentheses "()" are calculation when operating with 8.192 kHz clock.

Document Number: 002-07765 Rev. \*A Page 37 of 81

## 12.11 UART Outline

UART is a general-purpose serial data communication interface for synchronous and asynchronous communication using external devices.

- Provided with bi-directional communication function for both clock-synchronous and clock-asynchronous modes.

- Provided with master/slave communication function (multi-processor mode). (Only master side is available.)

- Interrupt request is generated upon completion of reception, completion of transmission and detection of reception error.

- Ready for expanded intelligent service, El<sup>2</sup>OS.

Table 12-3. UART Functions

|                                                                          | Description                                                                                                                                                                                             |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data buffer                                                              | Full-duplex double buffer                                                                                                                                                                               |

| Transmission mode                                                        | Clock synchronous (No start/stop bit, no parity bit) Clock asynchronous (start-stop synchronous)                                                                                                        |

| Baud rate                                                                | Built-in special-purpose baud-rate generator. Setting is selectable among 8 values. Input of external values is allowed. Use of clock from external timer (16-bit reload timer 0) is allowed.           |

| Data length                                                              | 7 bits (only asynchronous normal mode)<br>8 bits                                                                                                                                                        |

| Signaling system                                                         | Non Return to Zero (NRZ) system                                                                                                                                                                         |

| Reception error detection                                                | Framing error Overrun error Parity error (not detectable in operation mode 1 (multi-processor mode))                                                                                                    |

| Interrupt request                                                        | Receive interrupt (reception completed, reception error detected) Transmission interrupt (transmission completed) Ready for expanded intelligent I/O service (El²OS) in both transmission and reception |

| Master/slave communication function (asynchronous, multi-processor mode) | Communication between 1 (master) and n (slaves) are available (usable as master only).                                                                                                                  |

Note: Start/stop bit is not added upon clock-synchronous transmission. Data only is transmitted.

Table 12-4. UART Operation Modes

|   | Operation Mode                  | Data L         | -ength         | Synchronization | Stop Bit Length    |  |

|---|---------------------------------|----------------|----------------|-----------------|--------------------|--|

|   | Operation mode                  | With Parity    | Without Parity | Synchronization | Stop Bit Length    |  |

| 0 | Asynchronous mode (normal mode) | 7-bit or 8-bit |                | Asynchronous    | 1- bit or 2-bit *2 |  |

| 1 | Multi processor mode            | 8+1*1 –        |                | Asynchronous    |                    |  |

| 2 | Synchronous mode                | 8              | _              | Synchronous     | No                 |  |

<sup>-:</sup> Disallowed

Document Number: 002-07765 Rev. \*A Page 47 of 81

<sup>1: &</sup>quot;+1" is an address/data selection bit used for communication control (bit 11 of SCR1 register: A/D).

<sup>2:</sup> Only 1 bit is detected as a stop bit on data reception.

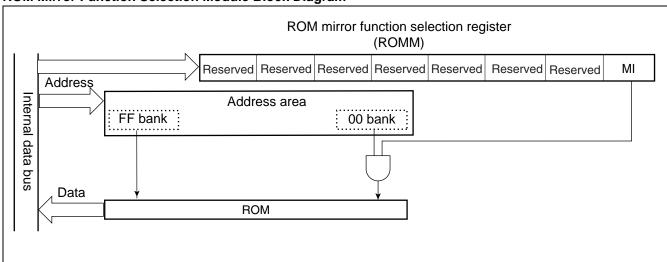

# 12.14 ROM Mirror Function Selection Module Outline

The ROM mirror function selection module sets the data in ROM assigned to FF bank so that the data is read by access to 00 bank.

# **ROM Mirror Function Selection Module Block Diagram**

# FF Bank Access by ROM Mirror Function

- Use within recommended operating conditions.

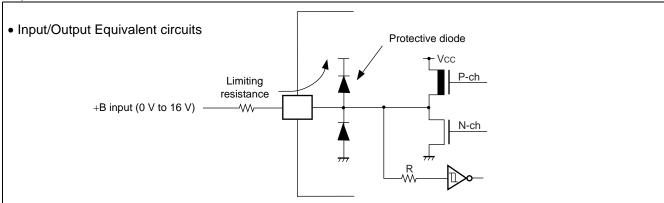

- Use at DC voltage (current).

- The +B signal should always be applied a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits:

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

Document Number: 002-07765 Rev. \*A Page 56 of 81

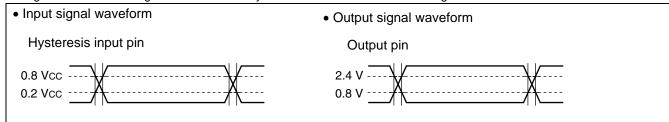

Rating values of alternating current is defined by the measurement reference voltage values shown below:

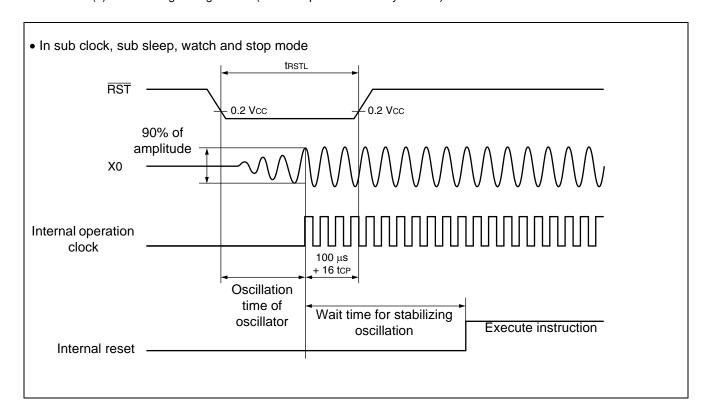

13.4.2 Reset Input Timing

| Parameter        | Symbol        | Pin Name     | Value                                                |     | Unit  | Remarks                                                  |

|------------------|---------------|--------------|------------------------------------------------------|-----|-------|----------------------------------------------------------|

| Parameter        | Symbol        | riii ivaille | Min                                                  | Max | Offic | Remarks                                                  |

| Reset input time | <b>t</b> RSTL | RST          | 16 tcp*3                                             | -   | ns    | Normal operation                                         |

|                  |               |              | Oscillation time of oscillator*1 + 100 μs + 16 tcp*3 | _   |       | In sub clock*2, sub<br>sleep*2, watch*2 and<br>stop mode |

|                  |               |              | 100                                                  | _   | μS    | In timebase timer                                        |

<sup>\*1:</sup> Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

<sup>\*3:</sup> Refer to "(1) Clock timing" ratings for tcp (internal operation clock cycle time).

<sup>\*2:</sup> Except for MB90F387S and MB90387S.

# 13.4.4 UART Timing

(Vcc = 4.5 V to 5.5 V, Vss = 0.0 V, TA =  $-40~^{\circ}C$  to  $+105~^{\circ}C$ )

| Parameter                                      | Symbol        | Pin Name      | Conditions                                                      | Value  |     | Unit  | Remarks |

|------------------------------------------------|---------------|---------------|-----------------------------------------------------------------|--------|-----|-------|---------|

|                                                |               |               | Conditions                                                      | Min    | Max | Oilit | Remarks |

| Serial clock cycle time                        | tscyc         | SCK1          | Internal shift clock                                            | 4 tcp* | -   | ns    |         |

| $SCK \downarrow \to SOT$ delay time            | <b>t</b> slov | SCK1,<br>SOT1 | mode output pin is: CL<br>= 80 pF+1TTL.                         | -80    | +80 | ns    |         |

| Valid SIN → SCK ↑                              | tıvsн         | SCK1, SIN1    |                                                                 | 100    | -   | ns    |         |

| $SCK \uparrow \rightarrow valid SIN hold time$ | <b>t</b> sнıx | SCK1, SIN1    |                                                                 | 60     | -   | ns    |         |

| Serial clock "H" pulse width                   | <b>t</b> shsl | SCK1          | External shift clock<br>mode output pin is: CL<br>= 80 pF+1TTL. | 2 tcp* | -   | ns    |         |

| Serial clock "L" pulse width                   | <b>t</b> slsh | SCK1          |                                                                 | 2 tcp* | -   | ns    |         |

| $SCK \downarrow \to SOT$ delay time            | tsLov         | SCK1,<br>SOT1 | 00 pt 7 1 1 2                                                   | -      | 150 | ns    |         |

| Valid SIN → SCK ↑                              | tıvsн         | SCK1, SIN1    |                                                                 | 60     | _   | ns    |         |

| SCK $\uparrow \rightarrow$ valid SIN hold time | <b>t</b> shix | SCK1, SIN1    |                                                                 | 60     | _   | ns    |         |

<sup>\*:</sup> Refer to Clock Timing ratings for top (internal operation clock cycle time).

## Notes:

- AC Characteristics in CLK synchronous mode.

- C<sub>L</sub> is a load capacitance value on pins for testing.

Document Number: 002-07765 Rev. \*A Page 64 of 81

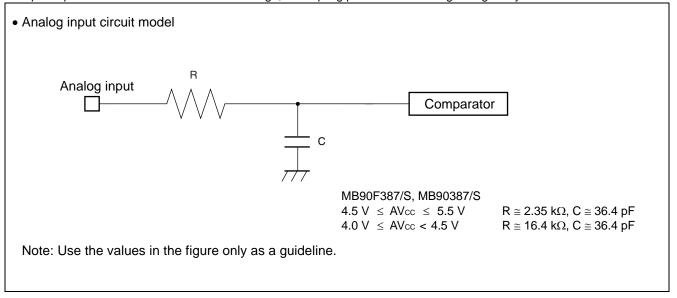

## 13.7 Notes on A/D Converter Section

Use the device with external circuits of the following output impedance for analog inputs:

Recommended output impedance of external circuits are: Approx. 3.9 k $\Omega$  or lower (4.5 V  $\leq$  AVcc  $\leq$  5.5 V) (sampling period=2.00  $\mu$ s at 16 MHz machine clock), Approx. 11 k $\Omega$  or lower (4.0 V  $\leq$  AVcc < 4.5 V) (sampling period=8.0  $\mu$ s at 16 MHz machine clock).

If an external capacitor is used, in consideration of the effect by tap capacitance caused by external capacitors and on-chip capacitors, capacitance of the external one is recommended to be several thousand times as high as internal capacitor.

If output impedance of an external circuit is too high, a sampling period for an analog voltage may be insufficient.

#### **About errors**

As [AVR-AVss] become smaller, values of relative errors grow larger.

## 13.8 Flash Memory Program/Erase Characteristics

| Parameter                            | Conditions                             | Value  |     |       | Unit  | Remarks                                     |  |

|--------------------------------------|----------------------------------------|--------|-----|-------|-------|---------------------------------------------|--|

|                                      |                                        | Min    | Тур | Max   | Offic | Remarks                                     |  |

| Sector erase time                    | $T_A = +25  ^{\circ}C$<br>Vcc = 5.0  V | -      | 1   | 15    | s     | Excludes 00H programming prior to erasure   |  |

| Chip erase time                      |                                        | -      | 4   | _     | s     | Excludes 00H programming prior to erasure   |  |

| Word (16-bit width) programming time |                                        | -      | 16  | 3,600 | μS    | Except for the over head time of the system |  |

| Program/Erase cycle                  | _                                      | 10,000 | -   | -     | cycle |                                             |  |

| Flash Data Retention Time            | Average<br>T <sub>A</sub> = + 85 °C    | 20     | -   | -     | Year  | *                                           |  |

<sup>\*:</sup> This value comes from the technology qualification (using Arrhenius equation to translate high temperature measurements into normalized value at + 85 °C).

Document Number: 002-07765 Rev. \*A Page 70 of 81

# MB90387

(Continued)