Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Core Size                  | 16-Bit                                                                          |

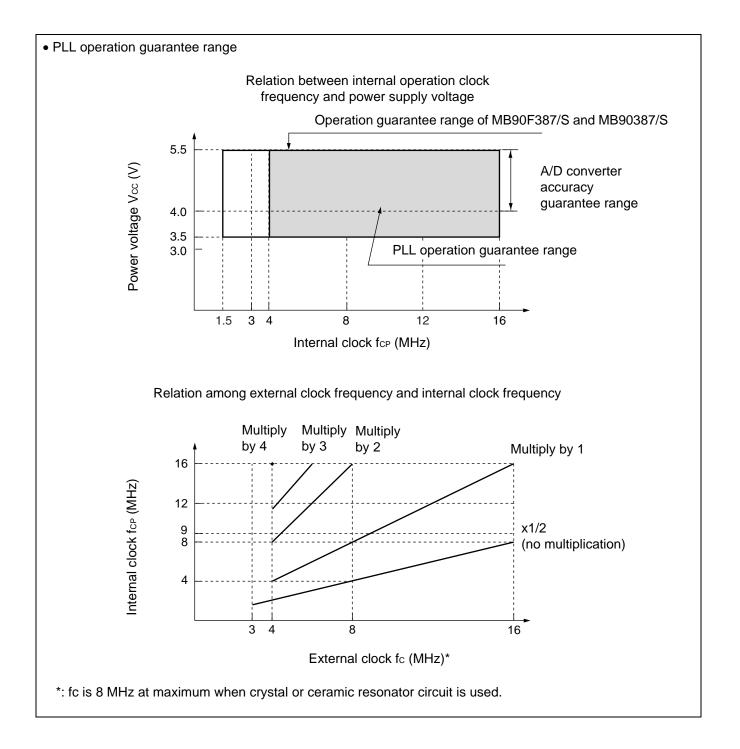

| Speed                      | 16MHz                                                                           |

| Connectivity               | CANbus, SCI, UART/USART                                                         |

| Peripherals                | POR, WDT                                                                        |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | 48-LQFP (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f387spmt-gs-9002 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number<br>Parameter | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MB90387<br>MB90387S | MB90V495G |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|--|--|--|

| 8/10-bit A/D converter   | Number of channels: 8<br>Resolution: Selectable 10-bit or 8-bit.<br>Conversion time: 6.125 µs (at 16 MHz machine clock, including sampling time)<br>Sequential conversion of two or more successive channels is allowed. (Setting a<br>maximum of 8 channels is allowed.)<br>Single conversion mode: Selected channel is converted only once.<br>Sequential conversion mode: Selected channel is converted repetitively.<br>Halt conversion mode: Conversion of selected channel is stopped and activated alter-<br>nately. |                     |           |  |  |  |

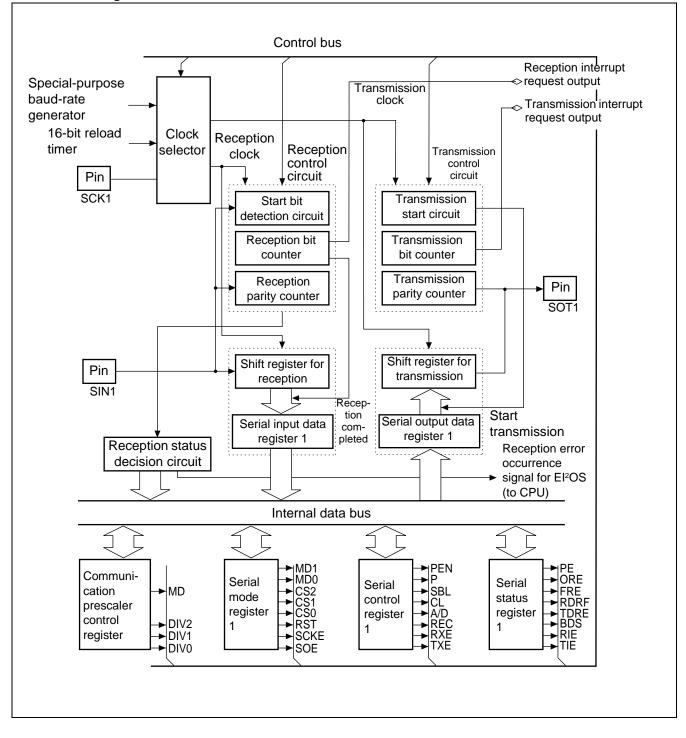

| UART(SCI)                | Number of channels: 1<br>Clock-synchronous transfer: 62.5 kbps to 2 Mbps<br>Clock-asynchronous transfer: 9,615 bps to 500 kbps<br>Communication is allowed by bi-directional serial communication function and master<br>slave type connection.                                                                                                                                                                                                                                                                             |                     |           |  |  |  |

| CAN                      | Compliant with Ver 2.0A and Ver 2.0B CAN specifications.<br>8 built-in message buffers.<br>Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)<br>CAN wake-up                                                                                                                                                                                                                                                                                                                                                  |                     |           |  |  |  |

\*1: Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

\*2: MB90387S, MB90F387S

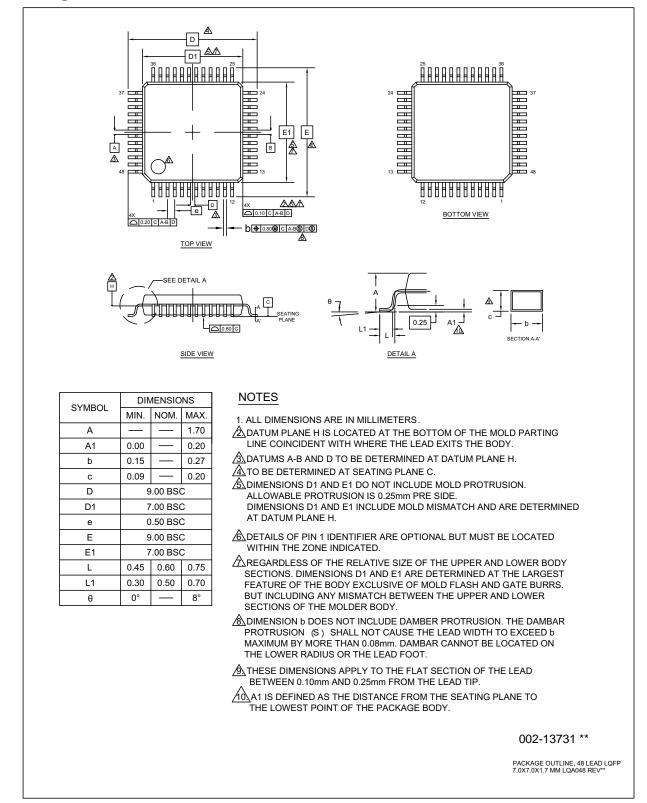

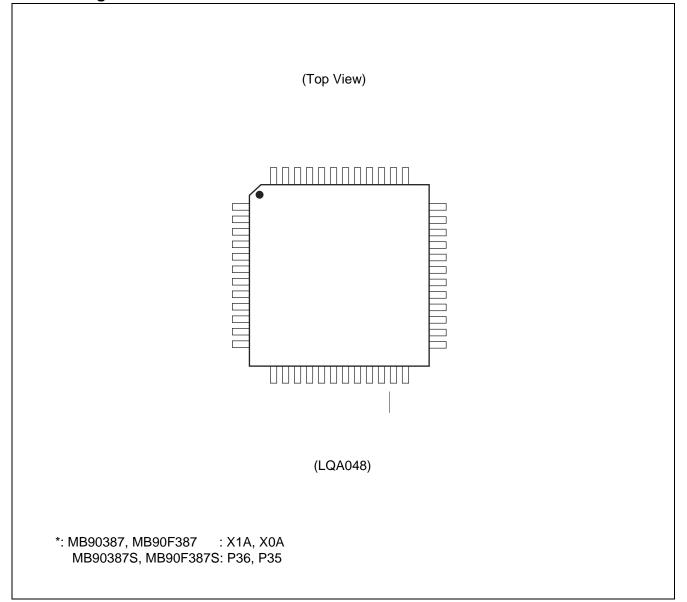

### 2. Packages And Product Models

| Package | MB90F387, MB90F387S | MB90387, MB90387S |

|---------|---------------------|-------------------|

| LQA048  | $\bigcirc$          | $\bigcirc$        |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to Package Dimension for details of the package.

### 3. Product Comparison

### Memory Space

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

- On MB90V495G, an image from FF4000<sup>H</sup> to FFFFFF<sup>H</sup> is viewed on 00 bank and an image of FE0000<sup>H</sup> to FF3FFF<sup>H</sup> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387/387S, an image from FF4000H to FFFFFFH is viewed on 00 bank and an image of FE0000H to FF3FFFH is viewed only on FF bank.

### 4. Pin Assignment

| Address                  | Register<br>Abbreviation | Register                                                | Read/<br>Write | Resource                            | Initial Value         |

|--------------------------|--------------------------|---------------------------------------------------------|----------------|-------------------------------------|-----------------------|

| 000083н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000084н                  | TCANR                    | Send cancel register                                    | W              | CAN controller                      | 0000000в              |

| 000085н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000086н                  | TCR                      | Send completion register                                | R/W            | CAN controller                      | 0000000в              |

| 000087н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000088н                  | RCR                      | Receive completion register                             | R/W            | CAN controller                      | 0000000в              |

| 000089н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Ан                  | RRTRR                    | Receive RTR register                                    | R/W            | CAN controller                      | 0000000в              |

| 00008Вн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Сн                  | ROVRR                    | Receive overrun register                                | R/W            | CAN controller                      | 0000000в              |

| 00008Dн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Eн                  | RIER                     | Receive completion interrupt<br>permission register     | R/W            | CAN controller                      | 0000000в              |

| 00008Fн<br>to<br>00009Dн |                          | (Reserv                                                 | ed area) *     |                                     |                       |

| 00009Eн                  | PACSR                    | Address detection control register                      | R/W            | Address matching detection function | 0000000в              |

| 00009Fн                  | DIRR                     | Delay interrupt request generation/<br>release register | R/W            | Delay interrupt generation module   | XXXXXXX0B             |

| 0000А0н                  | LPMCR                    | Lower power consumption mode control register           | W,R/W          | Lower power consumption mode        | 00011000в             |

| 0000A1н                  | CKSCR                    | Clock selection register                                | R,R/W          | Clock                               | 11111100в             |

| 0000A2н<br>to<br>0000A7н |                          | (Reserv                                                 | ed area) *     |                                     |                       |

| 0000A8н                  | WDTC                     | Watchdog timer control register                         | R,W            | Watchdog timer                      | XXXXX111 <sub>B</sub> |

| 0000A9н                  | TBTC                     | Time-base timer control register                        | R/W,W          | Time-base timer                     | 1XX00100в             |

| 0000ААн                  | WTC                      | Watch timer control register                            | R,R/W          | Watch timer                         | 1Х001000в             |

| 0000ABн<br>to<br>0000ADн |                          | (Reserv                                                 | ed area) *     | ·                                   |                       |

| 0000AEн                  | FMCS                     | Flash memory control status register                    | R,W,R/W        | 512k-bit Flash<br>memory            | 000X0000 <sub>B</sub> |

| 0000AFн                  |                          | (Reserv                                                 | ed area) *     | . 1                                 |                       |

| Address                  | Register<br>Abbreviation | Register                                               | Read/<br>Write | Resource                            | Initial Value |

|--------------------------|--------------------------|--------------------------------------------------------|----------------|-------------------------------------|---------------|

| 0000В0н                  | ICR00                    | Interrupt control register 00                          | R/W            | Interrupt controller                | 00000111в     |

| 0000B1н                  | ICR01                    | Interrupt control register 01                          |                |                                     | 00000111в     |

| 0000В2н                  | ICR02                    | Interrupt control register 02                          |                |                                     | 00000111в     |

| 0000ВЗн                  | ICR03                    | Interrupt control register 03                          |                |                                     | 00000111в     |

| 0000В4н                  | ICR04                    | Interrupt control register 04                          |                |                                     | 00000111в     |

| 0000B5н                  | ICR05                    | Interrupt control register 05                          |                |                                     | 00000111в     |

| 0000В6н                  | ICR06                    | Interrupt control register 06                          |                |                                     | 00000111в     |

| <b>0000B7</b> н          | ICR07                    | Interrupt control register 07                          |                |                                     | 00000111в     |

| 0000B8н                  | ICR08                    | Interrupt control register 08                          |                |                                     | 00000111в     |

| 0000B9н                  | ICR09                    | Interrupt control register 09                          |                |                                     | 00000111в     |

| 0000ВАн                  | ICR10                    | Interrupt control register 10                          |                |                                     | 00000111в     |

| 0000ВВн                  | ICR11                    | Interrupt control register 11                          |                |                                     | 00000111в     |

| 0000ВСн                  | ICR12                    | Interrupt control register 12                          |                |                                     | 00000111в     |

| 0000BDн                  | ICR13                    | Interrupt control register 13                          |                |                                     | 00000111в     |

| 0000ВЕн                  | ICR14                    | Interrupt control register 14                          |                |                                     | 00000111в     |

| 0000BFн                  | ICR15                    | Interrupt control register 15                          |                |                                     | 00000111в     |

| 0000C0н<br>to<br>0000FFн |                          | (Reser                                                 | ved area) *    |                                     |               |

| 001FF0⊦                  | PADR0                    | Detection address setting register 0 (low-order)       | R/W            | Address matching detection function | XXXXXXXXB     |

| 001FF1⊦                  |                          | Detection address setting register 0 (middle-order)    |                |                                     | XXXXXXXXB     |

| 001FF2⊦                  |                          | Detection address setting register 0 (high-order)      |                |                                     | XXXXXXXXB     |

| 001FF3⊦                  | PADR1                    | Detection address setting register 1 (low-order)       | R/W            | ] [                                 | XXXXXXXXB     |

| 001FF4⊦                  |                          | Detection address setting register 1<br>(middle-order) |                |                                     | XXXXXXXXB     |

| 001FF5н                  | 1                        | Detection address setting register 1 (high-order)      | 1              |                                     | XXXXXXXXB     |

| 003900н                  | TMR0/                    | 16-bit timer register 0/16-bit reload                  | R,W            | 16-bit reload timer 0               | XXXXXXXXB     |

| 003901н                  | TMRLR0                   | register                                               |                | F F                                 | XXXXXXXXB     |

| 003902н                  | TMR1/                    | 16-bit timer register 1/16-bit reload                  | R,W            | 16-bit reload timer 1               | XXXXXXXXB     |

| 003903н                  | TMRLR1                   | register                                               |                |                                     | XXXXXXXXB     |

| 003904н<br>to<br>00390Fн |                          | (Reser                                                 | ved area) *    |                                     |               |

| Address                  | Register<br>Abbreviation | Register                           | Read/<br>Write | Resource       | Initial Value                                    |

|--------------------------|--------------------------|------------------------------------|----------------|----------------|--------------------------------------------------|

| 003С38н,<br>003С39н      | DLCR4                    | DLC register 4                     | R/W            | CAN controller | XXXXXXXXB,<br>XXXXXXXB                           |

| 003С3Ан,<br>003С3Вн      | DLCR5                    |                                    |                |                | XXXXXXXXB,<br>XXXXXXXB                           |

| 003C3Cн,<br>003C3Dн      | DLCR6                    | DLC register 6                     | R/W            |                | XXXXXXXXB,<br>XXXXXXXB                           |

| 003C3Eн,<br>003C3Fн      | DLCR7                    | DLC register 7                     | R/W            |                | XXXXXXXXB,<br>XXXXXXXB                           |

| 003C40н<br>to<br>003C47н | DTR0                     | Data register 0                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C48н<br>to<br>003C4Fн | DTR1                     | Data register 1                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C50н<br>to<br>003C57н | DTR2                     | Data register 2                    | R/W            | -              | XXXXXXXXB<br>to<br>XXXXXXXB                      |

| 003C58н<br>to<br>003C5Fн | DTR3                     | Data register 3                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C60н<br>to<br>003C67н | DTR4                     | Data register 4                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C68н<br>to<br>003C6Fн | DTR5                     | Data register 5                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C70н<br>to<br>003C77н | DTR6                     | Data register 6                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C78н<br>to<br>003C7Fн | DTR7                     | Data register 7                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB                     |

| 003C80н<br>to<br>003CFFн |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D00н,<br>003D01н      | CSR                      | Control status register            | R/W, R         | CAN controller | 0XXXX001в,<br>00XXX000в                          |

| 003D02н                  | LEIR                     | Last event display register        | R/W            |                | 000XX000 <sub>B</sub>                            |

| 003D03н                  |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D04н,<br>003D05н      | RTEC                     | Send/receive error counter         | R              | CAN controller | 0000000в,<br>0000000в                            |

| 003D06н,<br>003D07н      | BTR                      | Bit timing register                | R/W            |                | 11111111 <sub>в</sub> ,<br>Х1111111 <sub>в</sub> |

| 003D08н                  | IDER                     | IDE register                       | R/W            |                | XXXXXXXXB                                        |

| 003D09н                  |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D0Aн                  | TRTRR                    | Send RTR register                  | R/W            | CAN controller | 0000000в                                         |

| 003D0Bн                  |                          | (Rese                              | rved area) *   |                |                                                  |

| 003D0CH                  | RFWTR                    | Remote frame receive wait register | R/W            | CAN controller | XXXXXXXXB                                        |

| Address                  | Register<br>Abbreviation | Register                                      | Read/<br>Write | Resource               | Initial Value                |  |  |

|--------------------------|--------------------------|-----------------------------------------------|----------------|------------------------|------------------------------|--|--|

| 003D0Dн                  |                          | (Reserv                                       | ed area) *     |                        |                              |  |  |

| 003D0Eн                  | TIER                     | Send completion interrupt permission register | CAN controller | 0000000в               |                              |  |  |

| 003D0Fн                  |                          | (Reserv                                       | ed area) *     | ·                      |                              |  |  |

| 003D10н,<br>003D11н      | AMSR                     | Acceptance mask selection register            | CAN controller | XXXXXXXXB,<br>XXXXXXXB |                              |  |  |

| 003D12н,<br>003D13н      | (Reserved area) *        |                                               |                |                        |                              |  |  |

| 003D14н<br>to<br>003D17н | AMR0                     | Acceptance mask register 0                    | R/W            | CAN controller         | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |

| 003D18н<br>to<br>003D1Bн | AMR1                     | Acceptance mask register 1                    | R/W            |                        | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |

| 003D1Cн<br>to<br>003DFFн |                          | (Reserv                                       | ed area) *     |                        |                              |  |  |

| 003E00н<br>to<br>003EFFн | (Reserved area) *        |                                               |                |                        |                              |  |  |

| 003FF0н<br>to<br>003FFFн |                          | (Reserved area) *                             |                |                        |                              |  |  |

Initial values:

0: Initial value of this bit is "0."

1: Initial value of this bit is "1."

X: Initial value of this bit is undefined.

\*: "Reserved area" should not be written anything. Result of reading from "Reserved area" is undefined.

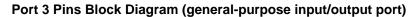

### **Port 3 Registers**

- Port 3 registers include port 3 data register (PDR3) and port 3 direction register (DDR3).

- The bits configuring the register correspond to port 3 pins on a one-to-one basis.

#### **Relation between Port 3 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 3    | PDR3, DDR3                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P37  | P36* | P35* | _    | P33  | P32  | P31  | P30  |

\*: P35 and P36 do not exist on MB90387and MB90F387.

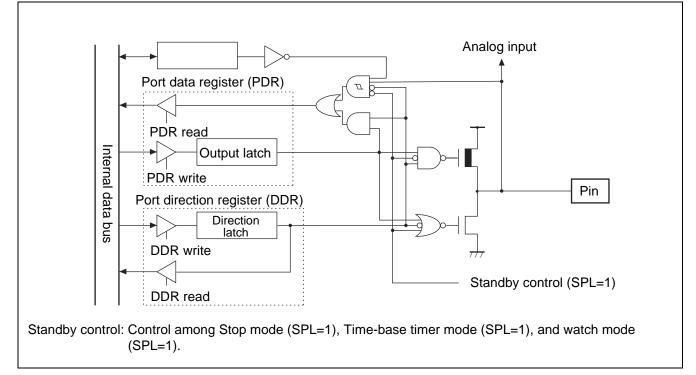

#### Port 5 Pins Block Diagram

#### **Port 5 Registers**

- Port 5 registers include port 5 data register (PDR5), port 5 direction register (DDR5), and analog input permission register (ADER).

- Analog input permission register (ADER) allows or disallows input of analog signal to the analog input pin.

- The bits configuring the register correspond to port 5 pins on a one-to-one basis.

#### **Relation between Port 5 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 5    | PDR5, DDR5                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | ADER                                    | ADE7 | ADE6 | ADE5 | ADE4 | ADE3 | ADE2 | ADE1 | ADE0 |

|           | Corresponding pins                      | P57  | P56  | P55  | P54  | P53  | P52  | P51  | P50  |

#### Watchdog timer control register(WDTC) Watch timer control register (WTC) WRST ERST SRST WTE WT1 WT0 PONR \_\_\_\_ WDCS Watchdog timer 2, Activate Reset occurs \_ Counter Watchdog Shift to sleep mode \_\_\_ 2-bit Internal reset Count clock reset clear control Shift to time-base counter - 6 generation generation selector circuit timer mode circuit circuit Shift to watch mode Clear Shift to stop mode 4 4 Time-base timer counter Main clock $\times 2^2$ × 28 × 29 × 210 × 211 × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> $\times 2^1$ × 215 × 216 × 2<sup>17</sup> $\times 2^{18}$ (dividing HCLK by 2) Watch counter Sub clock $\times 2^2$ × 2<sup>5</sup> $\times 2^{6}$ × 2<sup>8</sup> × 2<sup>9</sup> × 2<sup>10</sup> × 2<sup>11</sup> × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> × 2<sup>15</sup> $\times 2^{1}$ $\times 2^7$ . SCLK HCLK: Oscillation clock SCLK: Sub clock

#### Watchdog Timer Block Diagram

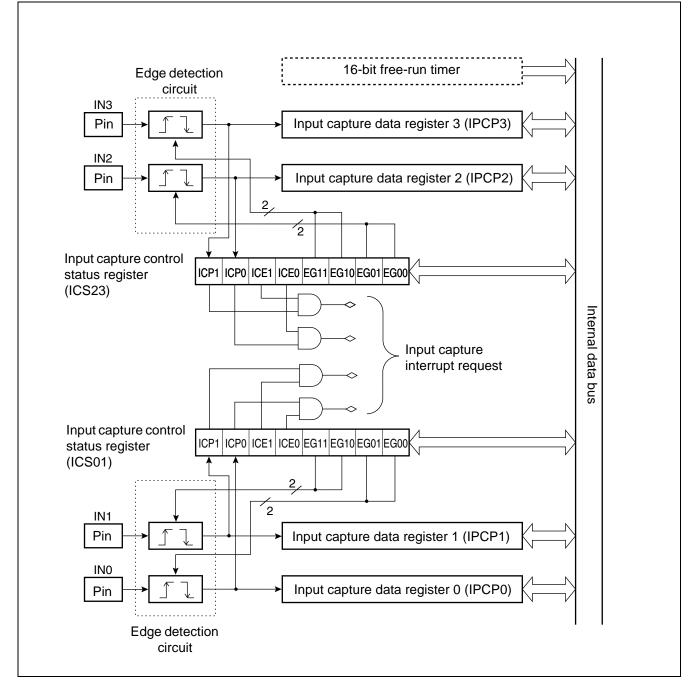

#### Input Capture Block Diagram

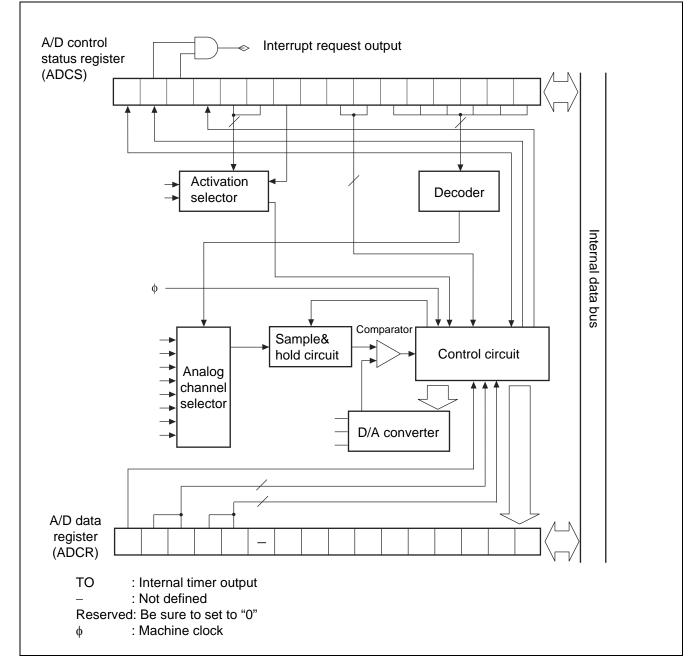

#### 12.10 8/10-bit A/D Converter

The 8/10-bit A/D converter converts an analog input voltage into 8-bit or 10/bit digital value, using the RC-type successive approximation conversion method.

- Input signal is selected among 8 channels of analog input pins.

- Activation trigger is selected among software trigger, internal timer output, and external trigger.

#### Functions of 8/10-bit A/D Converter

The 8/10-bit A/D converter converts an analog voltage (input voltage) input to analog input pin into an 8-bit or 10-bit digital value (A/D conversion).

The 8/10-bit A/D converter has the following functions:

- A/D conversion takes a minimum of 6.12 µs\* for 1 channel, including sampling time. (A/D conversion)

- Sampling of one channel takes a minimum of 2.0 µs\*.

- RC-type successive approximation conversion method, with sample & hold circuit is used for conversion.

- Resolution of either 8 bits or 10 bits is specifiable.

- A maximum of 8 channels of analog input pins are allowed for use.

- Generation of interrupt request is allowed, by storing A/D conversion result in A/D data register.

- Activation of EI<sup>2</sup>OS is allowed upon occurrence of an interrupt request. With use of EI<sup>2</sup>OS, data loss is avoided even if A/D conversion is performed successively.

- An activation trigger is selectable among software trigger, internal timer output, and external trigger (fall edge).

- : When operating with 16 MHz machine clock

#### 8/10-bit A/D Converter Conversion Mode

| Conversion Mode            | Description                                                                                                                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Singular conversion mode   | The A/D conversion is performed form a start channel to an end channel sequentially. Upon completion of A/D conversion on an end channel, A/D conversion function stops.                          |

| Sequential conversion mode | The A/D conversion is performed form a start channel to an end channel sequentially. Upon completion of A/D conversion on an end channel, A/D conversion function resumes from the start channel. |

| Pausing conversion mode    | The A/D conversion is performed by pausing at each channel. Upon completion of A/D conversion on an end channel, A/D conversion and pause functions resume from the start channel.                |

#### 8/10-bit A/D Converter Block Diagram

#### **UART Block Diagram**

### 12.12 CAN Controller

The Controller Area Network (CAN) is a serial communication protocol compliant with CANVer2.0A and Ver2.0B. The protocol allows data transmission and reception in both standard frame format and expanded frame format.

#### Features of CAN Controller

- CAN controller format is compliant with CANVer2.0A and Ver2.0B.

- The protocol allows data transmission and reception in standard frame format and expanded frame format.

- Automatic transmission of data frame by remote frame reception is allowed.

- Baud rate ranges from 10 kbps to 1 Mbps (with 16-MHz machine clock).

#### Table 12-5. Data Transmission Baud Rate

| Machine Clock | Baud Rate (Max) |

|---------------|-----------------|

| 16 MHz        | 1 Mbps          |

| 12 MHz        | 1 Mbps          |

| 8 MHz         | 1 Mbps          |

| 4 MHz         | 500 kbps        |

| 2 MHz         | 250 kbps        |

- Provided with 8 transmission/reception message buffers.

- Transmission/reception is allowed at ID 11 bit in standard format, and at ID 29 bit in expanded frame format.

- Specifying 0 byte to 8 bytes is allowed in message data.

- Multi-level message buffer configuration is allowed.

- CAN controller has two built-in acceptance masks. Mask settings are independently allowed for the two acceptance masks on reception IDs.

- The two acceptance masks allow reception in standard frame format and expanded frame format.

- For types of masking, all-bit comparison, all-bit masking, and partial masking with acceptance mask register 0/1, are specifiable.

### **13. Electrical Characteristics**

#### 13.1 Absolute Maximum Rating

| Parameter                              | Symbol          | Rat       | ting      | Unit | Remarks               |

|----------------------------------------|-----------------|-----------|-----------|------|-----------------------|

| Parameter                              | Symbol          | Min       | Max       | Unit | Remarks               |

| Power supply voltage*1                 | Vcc             | Vss - 0.3 | Vss + 6.0 | V    |                       |

|                                        | AVcc            | Vss - 0.3 | Vss + 6.0 | V    | Vcc = AVcc*2          |

|                                        | AVR             | Vss - 0.3 | Vss + 6.0 | V    | $AVcc \ge AVR^{*2}$   |

| Input voltage*1                        | Vi              | Vss - 0.3 | Vss + 6.0 | V    | *3                    |

| Output voltage*1                       | Vo              | Vss - 0.3 | Vss + 6.0 | V    | *3                    |

| Maximum clamp current                  |                 | - 2.0     | + 2.0     | mA   | *7                    |

| Total maximum clamp current            | Σ   Iclamp      | -         | 20        | mA   | *7                    |

| "L" level maximum output current       | IOL1            | -         | 15        | mA   | Normal output*4       |

|                                        | IOL2            | -         | 40        | mA   | High-current output*4 |

| "L" level average output current       | IOLAV1          | -         | 4         | mA   | Normal output*5       |

|                                        | IOLAV2          | -         | 30        | mA   | High-current output*5 |

| "L" level maximum total output current | Σlol1           | -         | 125       | mA   | Normal output         |

|                                        | ΣΙοι2           | -         | 160       | mA   | High-current output   |

| "L" level average total output current | $\Sigma$ lolav1 | -         | 40        | mA   | Normal output*6       |

|                                        | $\Sigma$ Iolav2 | -         | 40        | mA   | High-current output*6 |

| "H" level maximum output current       | Іон1            | -         | -15       | mA   | Normal output*4       |

|                                        | Іон2            | -         | -40       | mA   | High-current output*4 |

| "H" level average output current       | IOHAV1          | -         | -4        | mA   | Normal output*5       |

|                                        | IOHAV2          | -         | -30       | mA   | High-current output*5 |

| "H" level maximum total output current | ΣІон1           | -         | -125      | mA   | Normal output         |

|                                        | ΣІон2           | -         | -160      | mA   | High-current output   |

| "H" level average total output current | ΣΙομαν1         | -         | -40       | mA   | Normal output*6       |

|                                        | ΣΙομαν2         | -         | -40       | mA   | High-current output*6 |

| Power consumption                      | PD              | -         | 245       | mW   |                       |

| Operating temperature                  | TA              | -40       | +105      | °C   |                       |

| Storage temperature                    | Tstg            | -55       | +150      | °C   |                       |

\*1: The parameter is based on  $V_{SS} = AV_{SS} = 0.0 V$ .

\*2: AVcc and AVR should not exceed Vcc.

\*3: VI and Vo should not exceed Vcc + 0.3 V. However if the maximum current to/from an input is limited by some means with external components, the IcLAMP rating supersedes the VI rating.

\*4: A peak value of an applicable one pin is specified as a maximum output current.

- \*5: An average current value of an applicable one pin within 100 ms is specified as an average output current. (Average value is found by multiplying operating current by operating rate.)

- \*6: An average current value of all pins within 100 ms is specified as an average total output current. (Average value is found by multiplying operating current by operating rate.)

\*7:

Applicable to pins: P10 to P17, P20 to P27, P30 to P33, P35\*, P36\*, P37, P40 to P44, P50 to P57

\*: P35 and P36 are MB90387S and MB90F387S only.

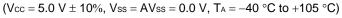

13.4.3 Power-on Reset

| Parameter                  | Symbol     | Pin Name | Conditions | Value |     | Unit | Remarks                        |

|----------------------------|------------|----------|------------|-------|-----|------|--------------------------------|

| Farameter                  |            |          |            | Min   | Max | Onit | Remarks                        |

| Power supply rise time     | <b>t</b> ℝ | Vcc      | -          | 0.05  | 30  | ms   |                                |

| Power supply shutdown time | toff       | Vcc      |            | 1     | -   | ms   | Waiting time until<br>power-on |

### 15. Ordering Information

| Part Number                                              | Package                         | Remarks |

|----------------------------------------------------------|---------------------------------|---------|

| MB90F387PMT<br>MB90387PMT<br>MB90F387SPMT<br>MB90387SPMT | 48-pin plastic LQFP<br>(LQA048) |         |

### 16. Package Dimension