Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                     |

| Core Size                  | 16-Bit                                                                     |

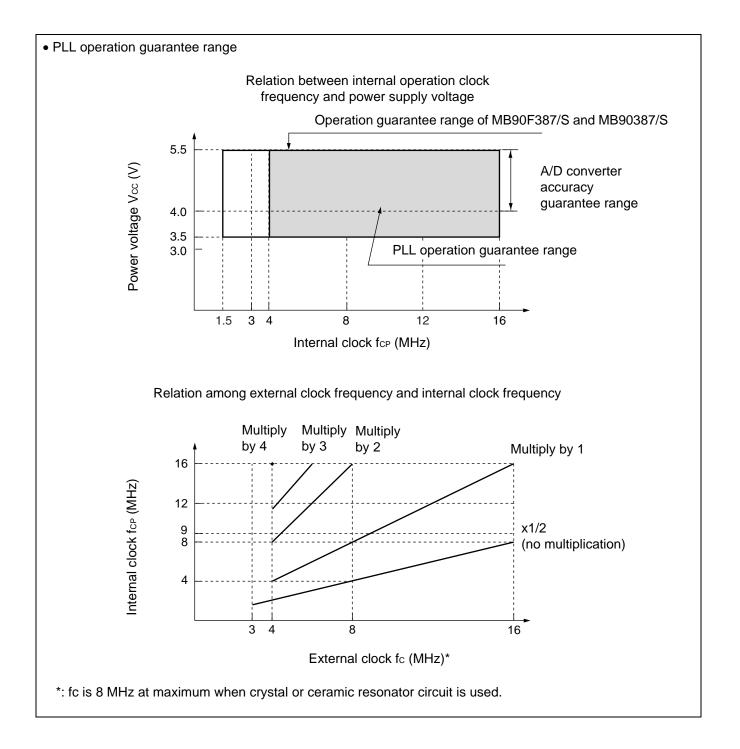

| Speed                      | 16MHz                                                                      |

| Connectivity               | CANbus, SCI, UART/USART                                                    |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | ·                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8/10b                                                                |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-LQFP                                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f387spmt-gs |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin No.  | Pin Name   | Circuit<br>Type | Function                                                                                               |  |

|----------|------------|-----------------|--------------------------------------------------------------------------------------------------------|--|

| 39       | P42        | D               | General-purpose input/output port.                                                                     |  |

|          | SOT1       |                 | Serial data input pin for UART. Valid only when serial data input/output setting on UART is "enabled." |  |

| 40       | P43        | D               | General-purpose input/output port.                                                                     |  |

|          | ТХ         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |  |

| 41       | P44        | D               | General-purpose input/output port.                                                                     |  |

|          | RX         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |  |

| 42 to 45 | P30 to P33 | D               | General-purpose input/output ports.                                                                    |  |

| 46       | X0A*       | A               | Pin for low-rate oscillation.                                                                          |  |

|          | P35*       |                 | General-purpose input/output port.                                                                     |  |

| 47       | X1A*       | А               | Pin for low-rate oscillation.                                                                          |  |

|          | P36*       | 1               | General-purpose input/output port.                                                                     |  |

| 48       | AVss       | -               | Vss power source input pin for A/D converter.                                                          |  |

\*: MB90387, MB90F387: X1A, X0A MB90387S, MB90F387S: P36, P35

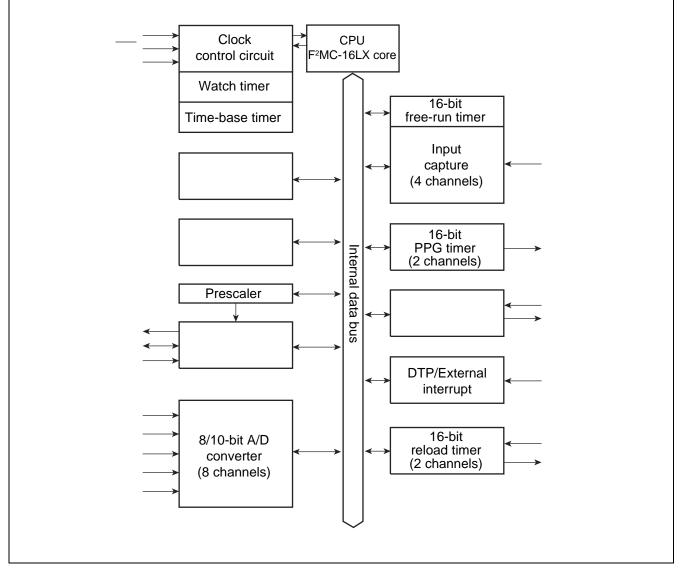

### 8. Block Diagram

### 9. Memory Map

MB90385 series allows specifying a memory access mode "single chip mode."

#### 9.1 Memory Allocation of MB90385

MB90385 series model has 24-bit wide internal address bus and up to 24-bit bus of external address bus. A maximum of 16-Mbyte memory space of external access memory is accessible.

# 10. I/O Map

| Address                  | Register<br>Abbreviation | Register                                                    | Read/<br>Write | Resource                  | Initial Value |

|--------------------------|--------------------------|-------------------------------------------------------------|----------------|---------------------------|---------------|

| 00000н                   |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000001н                  | PDR1                     | Port 1 data register                                        | R/W            | Port 1                    | XXXXXXXXB     |

| 000002н                  | PDR2                     | Port 2 data register                                        | R/W            | Port 2                    | XXXXXXXXB     |

| 00003н                   | PDR3                     | Port 3 data register                                        | R/W            | Port 3                    | XXXXXXXXB     |

| 000004н                  | PDR4                     | Port 4 data register                                        | R/W            | Port 4                    | XXXXXXXXAB    |

| 000005н                  | PDR5                     | Port 5 data register                                        | R/W            | Port 5                    | XXXXXXXXB     |

| 000006н<br>to<br>000010н |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000011н                  | DDR1                     | Port 1 direction data register                              | R/W            | Port 1                    | 0000000в      |

| 000012н                  | DDR2                     | Port 2 direction data register                              | R/W            | Port 2                    | 0000000в      |

| 000013н                  | DDR3                     | Port 3 direction data register                              | R/W            | Port 3                    | 000Х0000в     |

| 000014н                  | DDR4                     | Port 4 direction data register                              | R/W            | Port 4                    | ХХХ00000в     |

| 000015н                  | DDR5                     | Port 5 direction data register                              | R/W            | Port 5                    | 0000000в      |

| 000016н<br>to<br>00001Ан |                          | (Reserve                                                    | ed area) *     |                           |               |

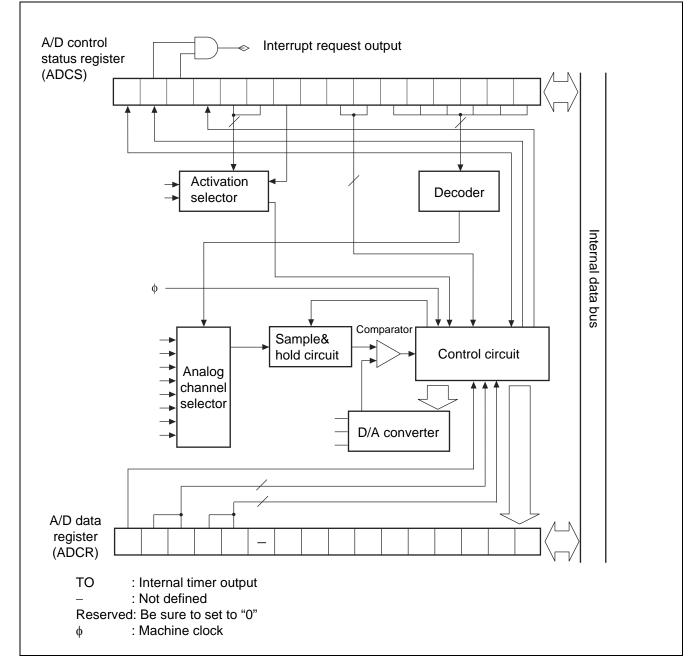

| 00001Bн                  | ADER                     | Analog input permission register                            | R/W            | 8/10-bit A/D<br>converter | 11111111в     |

| 00001Cнto<br>000025н     |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000026н                  | SMR1                     | Serial mode register 1                                      | R/W            | UART1                     | 0000000в      |

| 000027н                  | SCR1                     | Serial control register 1                                   | R/W, W         |                           | 00000100в     |

| 000028н                  | SIDR1/<br>SODR1          | Serial input data register 1/ Serial output data register 1 | R, W           |                           | XXXXXXXXB     |

| 000029н                  | SSR1                     | Serial status data register 1                               | R, R/W         |                           | 00001000в     |

| 00002Ан                  |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00002Вн                  | CDCR1                    | Communication prescaler control register 1                  | R/W            | UART1                     | 0ХХХ0000в     |

| 00002Cнto<br>00002Fн     |                          | (Reserve                                                    | ed area) *     |                           | ·             |

| 000030н                  | ENIR                     | DTP/External interrupt permission register                  | R/W            | DTP/External<br>interrupt | 0000000в      |

| 000031н                  | EIRR                     |                                                             |                |                           | XXXXXXXXB     |

| 000032н                  | ELVR                     | Detection level setting register                            | R/W            | 1                         | 0000000в      |

| 000033н                  |                          |                                                             | R/W            | 1                         | 0000000в      |

| 000034н                  | ADCS                     | A/D control status register                                 | R/W            | 8/10-bit A/D              | 0000000в      |

| 000035н                  |                          |                                                             | R/W, W         | converter                 | 0000000в      |

| 000036н                  | ADCR                     | A/D data register                                           | W, R           | 1                         | XXXXXXXXB     |

| 000037н                  |                          |                                                             | R              | 1                         | 00101XXXв     |

| Address                  | Register<br>Abbreviation                      | Register                              | Read/<br>Write | Resource                                      | Initial Value         |  |

|--------------------------|-----------------------------------------------|---------------------------------------|----------------|-----------------------------------------------|-----------------------|--|

| 000038н                  |                                               | (Reserve                              | ed area) *     |                                               |                       |  |

| to<br>00003Fн            |                                               |                                       |                |                                               |                       |  |

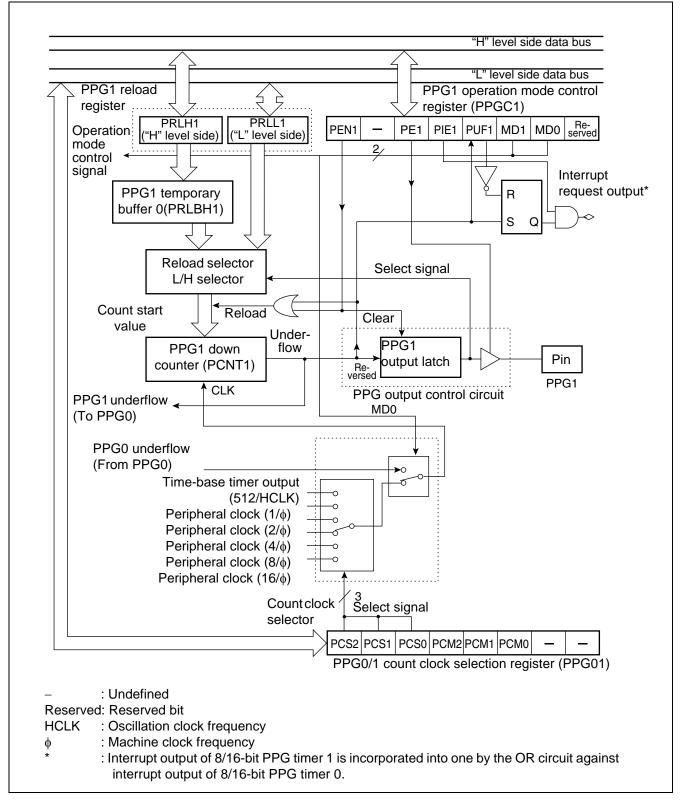

| 000040н                  | PPGC0                                         | PPG0 operation mode control register  | R/W, W         | 8/16-bit PPG timer 0/                         | 0Х000ХХ1в             |  |

| 000041н                  | PPGC1                                         | PPG1 operation mode control register  | R/W, W         |                                               | 0Х00001в              |  |

| 000042н                  | PPG01                                         | PPG0/1 count clock selection register | R/W            |                                               | 000000XXB             |  |

| 000043н                  |                                               | (Reserve                              | ed area) *     |                                               |                       |  |

| 000044н                  | PPGC2                                         | PPG2 operation mode control register  | R/W, W         | 8/16-bit PPG timer 2/                         | 0X000XX1в             |  |

| 000045н                  | PPGC3                                         | PPG3 operation mode control register  | R/W, W         | 3                                             | 0Х00001в              |  |

| 000046н                  | PPG23                                         | PPG2/3 count clock selection register | R/W            | 1 [                                           | 000000XXв             |  |

| 000047н to<br>00004Fн    |                                               | (Reserve                              | ed area) *     | · ·                                           |                       |  |

| 000050н                  | IPCP0                                         | Input capture data register 0         | R              | 16-bit input/output                           | XXXXXXXXB             |  |

| 000051н                  |                                               |                                       |                | timer                                         | XXXXXXXXB             |  |

| 000052н                  | IPCP1                                         | Input capture data register 1         | R              | 1 [                                           | XXXXXXXXB             |  |

| 000053н                  |                                               |                                       |                |                                               | XXXXXXXXB             |  |

| 000054н                  | ICS01                                         | Input capture control status register | R/W            |                                               | 0000000в              |  |

| 000055н                  | ICS23                                         |                                       | R/W            |                                               | 0000000в              |  |

| 000056н                  | TCDT                                          | Timer counter data register           |                |                                               | 0000000в              |  |

| 000057н                  |                                               |                                       |                | 0000000в                                      |                       |  |

| 000058н                  | TCCS                                          | Timer counter control status register | R/W            | 1 [                                           | 0000000в              |  |

| 000059н                  |                                               | (Reserve                              | ed area) *     | · · ·                                         |                       |  |

| 00005Ан                  | IPCP2                                         | 2 Input capture data register 2       | R              | 16-bit input/output<br>timer                  | XXXXXXXXB             |  |

| 00005Вн                  |                                               |                                       |                |                                               | XXXXXXXXB             |  |

| 00005Сн                  | IPCP3                                         | Input capture data register 3         | R              |                                               | XXXXXXXXB             |  |

| 00005Dн                  |                                               |                                       |                |                                               | XXXXXXXXB             |  |

| 00005Eнto<br>000065н     |                                               | (Reserve                              | ed area) *     |                                               |                       |  |

| 000066н                  | TMCSR0                                        | Timer control status register         | R/W            | 16-bit reload timer 0                         | 0000000в              |  |

| 000067н                  |                                               |                                       | R/W            |                                               | XXXX0000 <sub>B</sub> |  |

| 000068н                  | TMCSR1                                        |                                       | R/W            | 16-bit reload timer 1                         | 0000000в              |  |

| 000069н                  |                                               |                                       | R/W            |                                               | XXXX0000b             |  |

| 00006Анto<br>00006Ен     |                                               | (Reserve                              | ed area) *     |                                               |                       |  |

| 00006Fн                  | ROMM ROM mirroring function selection registe |                                       | W              | ROM mirroring<br>function selection<br>module | XXXXXXX1B             |  |

| 000070н<br>to<br>00007Fн |                                               | (Reserve                              | ed area) *     |                                               |                       |  |

| 000080н                  | BVALR                                         | Message buffer enabling register      | R/W            | CAN controller                                | 0000000в              |  |

| 000081н                  |                                               |                                       | ed area) *     |                                               |                       |  |

| 000082н                  | TREQR                                         | Send request register                 | R/W            | CAN controller                                | 0000000в              |  |

| Address                  | Register<br>Abbreviation | egister<br>reviation Register                          |             | Resource                            | Initial Value |

|--------------------------|--------------------------|--------------------------------------------------------|-------------|-------------------------------------|---------------|

| 0000В0н                  | ICR00                    | Interrupt control register 00                          | R/W         | Interrupt controller                | 00000111в     |

| 0000B1н                  | ICR01                    | Interrupt control register 01                          |             |                                     | 00000111в     |

| 0000В2н                  | ICR02                    | Interrupt control register 02                          |             |                                     | 00000111в     |

| 0000ВЗн                  | ICR03                    | Interrupt control register 03                          |             |                                     | 00000111в     |

| 0000В4н                  | ICR04                    | Interrupt control register 04                          |             | 00000111в                           |               |

| 0000B5н                  | ICR05                    | Interrupt control register 05                          |             |                                     | 00000111в     |

| 0000В6н                  | ICR06                    | Interrupt control register 06                          |             |                                     | 00000111в     |

| <b>0000B7</b> н          | ICR07                    | Interrupt control register 07                          |             |                                     | 00000111в     |

| 0000B8н                  | ICR08                    | Interrupt control register 08                          |             |                                     | 00000111в     |

| 0000B9н                  | ICR09                    | Interrupt control register 09                          |             |                                     | 00000111в     |

| 0000ВАн                  | ICR10                    | Interrupt control register 10                          |             |                                     | 00000111в     |

| 0000ВВн                  | ICR11                    | Interrupt control register 11                          |             |                                     | 00000111в     |

| 0000ВСн                  | ICR12                    | Interrupt control register 12                          |             |                                     | 00000111в     |

| 0000BDн                  | ICR13                    | Interrupt control register 13                          |             |                                     | 00000111в     |

| 0000ВЕн                  | ICR14                    | Interrupt control register 14                          |             | 00000111в                           |               |

| 0000BFн                  | ICR15                    | Interrupt control register 15                          |             |                                     | 00000111в     |

| 0000C0н<br>to<br>0000FFн |                          | (Reser                                                 | ved area) * |                                     |               |

| 001FF0⊦                  | PADR0                    | Detection address setting register 0 (low-order)       | R/W         | Address matching detection function | XXXXXXXXB     |

| 001FF1⊦                  |                          | Detection address setting register 0 (middle-order)    |             |                                     | XXXXXXXXB     |

| 001FF2⊦                  |                          | Detection address setting register 0 (high-order)      |             |                                     | XXXXXXXXB     |

| 001FF3⊦                  | PADR1                    | Detection address setting register 1 (low-order)       | R/W         | ] [                                 | XXXXXXXXB     |

| 001FF4⊦                  |                          | Detection address setting register 1<br>(middle-order) |             |                                     | XXXXXXXXB     |

| 001FF5н                  | -                        | Detection address setting register 1 (high-order)      |             |                                     | XXXXXXXXB     |

| 003900н                  | TMR0/                    | 16-bit timer register 0/16-bit reload                  | R,W         | 16-bit reload timer 0               | XXXXXXXXB     |

| 003901н                  | TMRLR0                   | register                                               |             | F                                   | XXXXXXXXB     |

| 003902н                  | TMR1/                    | 16-bit timer register 1/16-bit reload                  | R,W         | 16-bit reload timer 1               | XXXXXXXXB     |

| 003903н                  | TMRLR1                   | register                                               |             | F                                   | XXXXXXXXB     |

| 003904н<br>to<br>00390Fн |                          | (Reser                                                 | ved area) * |                                     |               |

| Address                  | Register<br>Abbreviation | Register                                      | Read/<br>Write | Resource       | Initial Value                |  |  |  |  |  |

|--------------------------|--------------------------|-----------------------------------------------|----------------|----------------|------------------------------|--|--|--|--|--|

| 003D0Dн                  | (Reserved area) *        |                                               |                |                |                              |  |  |  |  |  |

| 003D0Eн                  | TIER                     | Send completion interrupt permission register | R/W            | CAN controller | 0000000в                     |  |  |  |  |  |

| 003D0Fн                  |                          | (Reserv                                       | ed area) *     | ·              | -                            |  |  |  |  |  |

| 003D10н,<br>003D11н      | AMSR                     | Acceptance mask selection register            | R/W            | CAN controller | XXXXXXXXB,<br>XXXXXXXB       |  |  |  |  |  |

| 003D12н,<br>003D13н      |                          | (Reserved area) *                             |                |                |                              |  |  |  |  |  |

| 003D14н<br>to<br>003D17н | AMR0                     | Acceptance mask register 0                    | R/W            | CAN controller | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003D18н<br>to<br>003D1Bн | AMR1                     | Acceptance mask register 1                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003D1Cн<br>to<br>003DFFн |                          | (Reserv                                       | ed area) *     |                |                              |  |  |  |  |  |

| 003E00н<br>to<br>003EFFн |                          | (Reserved area) *                             |                |                |                              |  |  |  |  |  |

| 003FF0н<br>to<br>003FFFн |                          | (Reserv                                       | ed area) *     |                |                              |  |  |  |  |  |

Initial values:

0: Initial value of this bit is "0."

1: Initial value of this bit is "1."

X: Initial value of this bit is undefined.

\*: "Reserved area" should not be written anything. Result of reading from "Reserved area" is undefined.

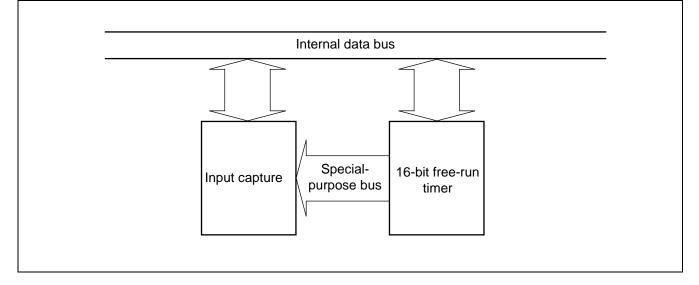

#### 12.4 16-bit Input/Output Timer

The 16-bit input/output timer is a compound module composed of 16-bit free-run timer, (1 unit) and input capture (2 units, 4 input pins). The timer, using the 16-bit free-run timer as a basis, enables measurement of clock cycle of an input signal and its pulse width.

#### Configuration of 16-bit Input/Output Timer

The 16-bit input/output timer is composed of the following modules:

- 16-bit free-run timer (1 unit)

- Input capture (2 units, 2 input pins per unit)

#### Functions of 16-bit Input/Output Timer

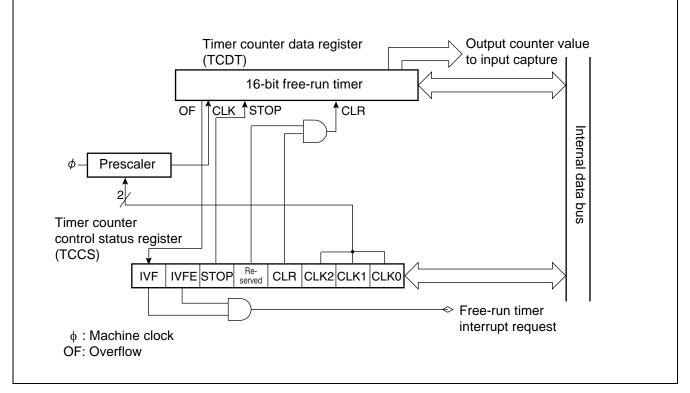

#### Functions of 16-bit Free-run Timer

The 16-bit free-run timer is composed of 16-bit up counter, timer counter control status register, and prescaler. The 16-bit up counter increments in synchronization with dividing ratio of machine clock.

- Count clock is set among four types of machine clock dividing rates.

- Generation of interrupt is allowed by counter value overflow.

- Activation of expanded intelligent I/O service (EI<sup>2</sup>OS) is allowed by interrupt generation.

- Counter value of 16-bit free-run timer is cleared to "0000<sup>H</sup>" by either resetting or software-clearing with timer count clear bit (TCCS: CLR).

- Counter value of 16-bit free-run timer is output to input capture, which is available as base time for capture operation.

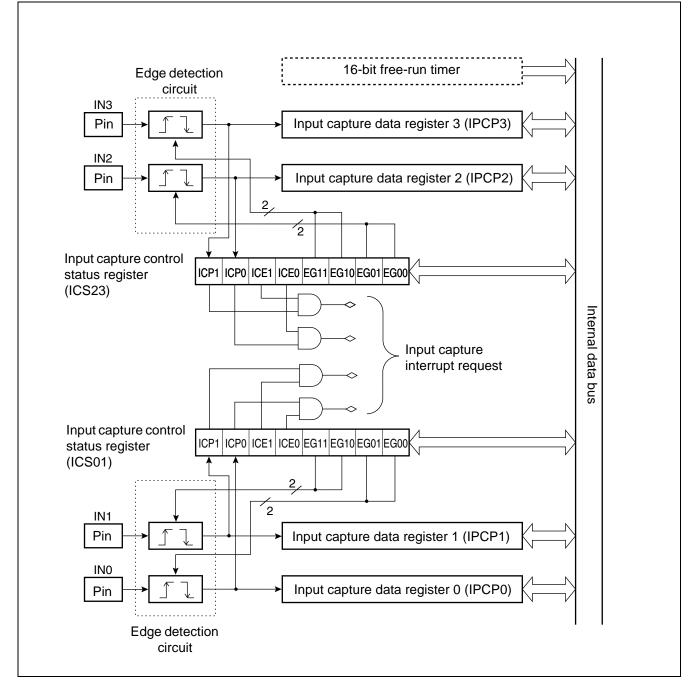

#### Functions of Input Capture

The input capture, upon detecting an edge of a signal input to the input pin from external device, stores a counter value of 16-bit freerun timer at the time of detection into the input capture data register. The function includes the input capture data registers corresponding to four input pins, input capture control status register, and edge detection circuit.

- Rising edge, falling edge, and both edges are selectable for detection.

- Generating interrupt on CPU is allowed by detecting an edge of input signal.

- Expanded intelligent I/O service (EI<sup>2</sup>OS) is activated by interrupt generation.

- The four input capture input pins and input capture data registers allows monitoring of a maximum of four events.

#### 16-bit Input/Output Timer Block Diagram

#### 16-bit Free-run Timer

Counter value of 16-bit free-run timer is used as reference time (base time) of input capture.

#### Input Capture

Input capture detects rising edge, falling edge or both edges and retains a counter value of 16-bit free-run timer. Detection of edge on input signal is allowed to generate interrupt.

#### 16-bit Free-run Timer Block Diagram

#### **Detailed Pin Assignment on Block Diagram**

The 16-bit input/output timer includes a 16-bit free-run timer. Interrupt request number of the 16-bit free-run timer is as follows: Interrupt request number: 19 (13<sub>H</sub>)

#### Prescaler

The prescaler divides a machine clock and provides a counter clock to the 16-bit up counter. Dividing ratio of the machine clock is specified by timer counter control status register (TCCS) among four values.

#### Timer Counter Data Register (TCDT)

The timer counter data register is a 16-bit up counter. A current counter value of the 16-bit free-run timer is read. Writing a value during halt of the counter allows setting an arbitrary counter value.

#### Input Capture Block Diagram

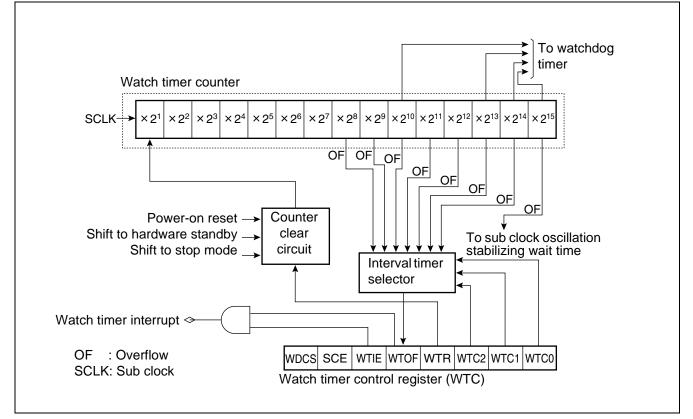

#### Watch Timer Block Diagram

Actual interrupt request number of watch timer is as follows: Interrupt request number: #28 (1C<sub>H</sub>)

#### Watch Timer Counter

A 15-bit up counter that uses sub clock (SCLK) as a count clock.

### **Counter Clear Circuit**

A circuit that clears the watch timer counter.

8/16-bit PPG Timer 1 Block Diagram

#### 8/10-bit A/D Converter Block Diagram

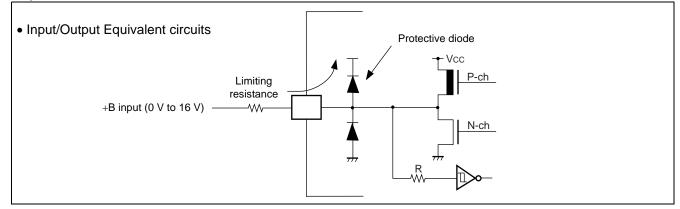

- Use within recommended operating conditions.

- Use at DC voltage (current).

- The +B signal should always be applied a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits:

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### 13.2 Recommended Operating Conditions

(Vss = AVss = 0.0V)

| Parameter             | Symbol | Value |     |      |      | Remarks                            |

|-----------------------|--------|-------|-----|------|------|------------------------------------|

| Falameter             | Symbol | Min   | Тур | Max  | Unit | Reindi K5                          |

| Power supply voltage  | Vcc    | 3.5   | 5.0 | 5.5  | V    | Under normal operation             |

|                       |        | 3.0   | _   | 5.5  |      | Retain status of stop<br>operation |

|                       | AVcc   | 4.0   | -   | 5.5  | V    | *2                                 |

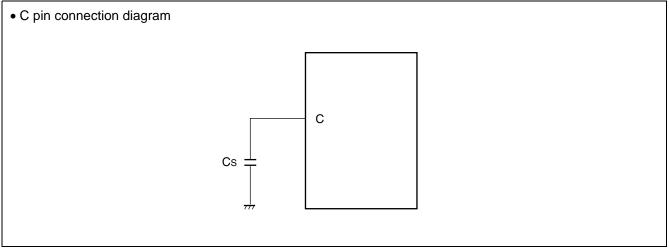

| Smoothing capacitor   | Cs     | 0.1   | -   | 1.0  | μF   | *1                                 |

| Operating temperature | TA     | -40   | -   | +105 | °C   |                                    |

\*1: Use a ceramic capacitor, or a capacitor of similar frequency characteristics. On the Vcc pin, use a bypass capacitor that has a larger capacity than that of Cs.

Refer to the following figure for connection of smoothing capacitor Cs.

\*2: AVcc is a voltage at which accuracy is guaranteed. AVcc should not exceed Vcc.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

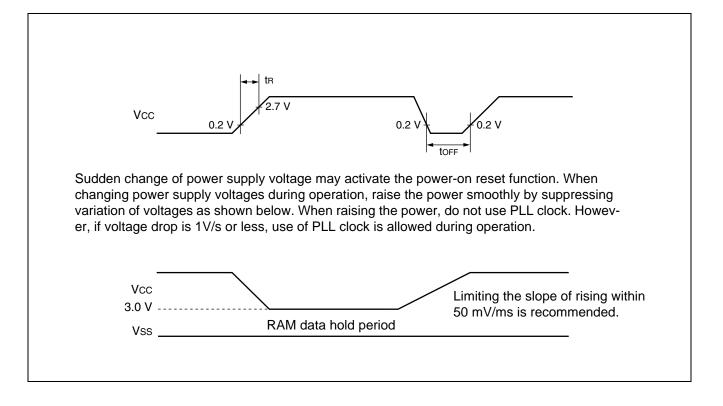

13.4.3 Power-on Reset

| Parameter                  | Symbol | nbol Pin Name Conc |            | Conditions |     | Unit | Remarks                        |

|----------------------------|--------|--------------------|------------|------------|-----|------|--------------------------------|

| Falameter                  | Symbol |                    | Conditions | Min        | Max | Unit | Relliaiks                      |

| Power supply rise time     | tR     | Vcc                | -          | 0.05       | 30  | ms   |                                |

| Power supply shutdown time | toff   | Vcc                |            | 1          | -   | ms   | Waiting time until<br>power-on |

(Continued)

#### (Continued)

### 17. Major Changes

Spansion Publication Number: DS07-13717-5E

| Page | Section                                                                                              | Change Results                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 4    | ■ PRODUCT LINEUP                                                                                     | Changed the number of channel of 8/16 bit PPG timer. or one 16-bit channel $\rightarrow$ or two 16-bit channels                       |

| 13   | ■ BLOCK DIAGRAM                                                                                      | Changed the direction of arrow of TIN0, TIN1 signals of 16-bit reload timer.<br>right arrow (output) $\rightarrow$ left arrow (input) |

| 67   | <ul> <li>ELECTRIC CHARACTERISTICS</li> <li>4. AC Characteristics</li> <li>(4) UART timing</li> </ul> | Changed the value of Serial clock.<br>Serial clock "H" pulse width: 4tcp→2tcp<br>Serial clock "L" pulse width: 4tcp→2tcp              |

NOTE: Please see "Document History" about later revised information.

### **Document History**

|                                                                                                          | Document Title: MB90387/387S/F387/F387S, MB90V495G, 16-bit Microcontrollers F <sup>2</sup> MC-16LX MB90385 Series<br>Document Number:002-07765 |      |            |                                                                                                          |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Revision         ECN         Orig. of<br>Change         Submission<br>Date         Description of Change |                                                                                                                                                |      |            |                                                                                                          |  |  |  |  |  |

| **                                                                                                       | _                                                                                                                                              | AKIH | 12/19/2008 | Migrated to Cypress and assigned document number 002-07765.<br>No change to document contents or format. |  |  |  |  |  |

| *A                                                                                                       | 6059071                                                                                                                                        | SSAS | 02/05/2018 | Updated to Cypress template<br>Package: FPT-48P-M26> LQA048                                              |  |  |  |  |  |