Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                    |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART, USB                              |

| Peripherals                | POR, PWM, Voltage Detect, WDT                                                    |

| Number of I/O              | 30                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 10x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 40-WFQFN Exposed Pad                                                             |

| Supplier Device Package    | 40-HWQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f213m8knnp-u0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 4.12 SFR Information (12) (1)

| Address | Register                               | Symbol   | After Reset |

|---------|----------------------------------------|----------|-------------|

| 2CF0h   | DTC Control Data 22                    | DTCD22   | XXh         |

| 2CF1h   |                                        |          | XXh         |

| 2CF2h   |                                        |          | XXh         |

| 2CF3h   |                                        |          | XXh         |

| 2CF4h   | 1                                      |          | XXh         |

| 2CF5h   | -                                      |          | XXh         |

| 2CF6h   |                                        |          | XXh         |

| 2CF7h   |                                        |          | XXh         |

| 2CF8h   | DTC Control Data 23                    | DTCD23   | XXh         |

| 2CF9h   | B TO CONTION Balla 25                  | B10B20   | XXh         |

| 2CFAh   | -                                      |          | XXh         |

| 2CFBh   |                                        |          | XXh         |

| 2CFCh   |                                        |          | XXh         |

|         |                                        |          |             |

| 2CFDh   | 4                                      |          | XXh         |

| 2CFEh   |                                        |          | XXh         |

| 2CFFh   |                                        |          | XXh         |

| 2D00h   |                                        |          |             |

| :       |                                        |          |             |

| 2DFFh   |                                        |          |             |

| 2E00h   | System Configuration Control Register  | SYSCFG   | 00h         |

| 2E01h   |                                        |          | 00h         |

| 2E02h   |                                        |          |             |

| 2E03h   |                                        |          |             |

| 2E04h   | System Configuration Status Register 0 | SYSSTS0  | 00000X00b   |

| 2E05h   |                                        |          | XX000000b   |

| 2E06h   |                                        |          | 70.000000   |

| 2E07h   |                                        |          |             |

| 2E08h   | Device State Control Register 0        | DVSTCTR0 | 00h         |

|         | Device State Control Register 0        | DVSTCTRU |             |

| 2E09h   |                                        |          | 00h         |

| 2E0Ah   |                                        |          |             |

| 2E0Bh   |                                        |          |             |

| 2E0Ch   |                                        |          |             |

| 2E0Dh   |                                        |          |             |

| 2E0Eh   |                                        |          |             |

| 2E0Fh   |                                        |          |             |

| 2E10h   |                                        |          |             |

| 2E11h   |                                        |          |             |

| 2E12h   |                                        |          |             |

| 2E13h   |                                        |          |             |

| 2E14h   | CFIFO Port Register                    | CFIFO    | 00h         |

| 2E15h   | Of it of the register                  | 0.110    | 00h         |

| 2E16h   |                                        |          | 0011        |

| 2E16h   |                                        |          |             |

|         |                                        |          |             |

| 2E18h   |                                        |          |             |

| 2E19h   |                                        |          |             |

| 2E1Ah   |                                        |          |             |

| 2E1Bh   |                                        |          |             |

| 2E1Ch   |                                        |          |             |

| 2E1Dh   |                                        |          |             |

| 2E1Eh   |                                        |          |             |

| 2E1Fh   |                                        |          |             |

| 2E20h   | CFIFO Port Select Register             | CFIFOSEL | 00h         |

| 2E21h   | 1                                      |          | 00h         |

| 2E22h   | CFIFO Port Control Register            | CFIFOCTR | 00h         |

|         | Of it O Fort Control Register          | CHIOCIK  |             |

| 2E23h   |                                        |          | 00h         |

| 2E24h   |                                        |          |             |

| 2E25h   |                                        |          |             |

| 2E26h   |                                        |          |             |

| 2E27h   |                                        |          |             |

| 2E28h   |                                        |          |             |

| 2E29h   |                                        |          |             |

|         |                                        | +        | 1           |

| 2E2Ah   |                                        |          |             |

2E2Eh 2E2Fh X: Undefined

2E2Bh 2E2Ch 2E2Dh

Note:

<sup>1.</sup> The blank areas are reserved and cannot be accessed by users.

## 5.1 Registers

# 5.1.1 Processor Mode Register 0 (PM0)

Address 0004h

| Bit         | b7 | b6 | b5 | b4 | b3   | b2 | b1 | b0 |

|-------------|----|----|----|----|------|----|----|----|

| Symbol      | _  | _  | _  | _  | PM03 | _  | _  | _  |

| After Reset | 0  | 0  | 0  | 0  | 0    | 0  | 0  | 0  |

| Bit | Symbol | Bit Name                                 | Function                                                                 | R/W |

|-----|--------|------------------------------------------|--------------------------------------------------------------------------|-----|

| b0  | _      | Reserved bits                            | Set to 0.                                                                | R/W |

| b1  | _      |                                          |                                                                          |     |

| b2  | _      |                                          |                                                                          |     |

| b3  | PM03   | Software reset bit                       | The MCU is reset when this bit is set to 1. When read, the content is 0. | R/W |

| b4  | _      | Nothing is assigned. If necessary, set t | to 0. When read, the content is 0.                                       | _   |

| b5  | _      |                                          |                                                                          |     |

| b6  | _      |                                          |                                                                          |     |

| b7  | _      |                                          |                                                                          |     |

Set the PRC1 bit in the PRCR register to 1 (write enabled) before rewriting the PM0 register.

## 5.1.2 Reset Source Determination Register (RSTFR)

Address 000Bh

| Bit         | b7 | b6 | b5 | b4 | b3  | b2  | b1  | b0  |          |

|-------------|----|----|----|----|-----|-----|-----|-----|----------|

| Symbol      | _  | _  | _  | _  | WDR | SWR | HWR | CWR |          |

| After Reset | 0  | Х  | Х  | Х  | Х   | Χ   | Χ   | Х   | (Note 1) |

| Bit | Symbol | Bit Name                         | Function                             | R/W |

|-----|--------|----------------------------------|--------------------------------------|-----|

| b0  | CWR    | Cold start-up/warm start-up      | 0: Cold start-up                     | R/W |

|     |        | determine flag (2, 3)            | 1: Warm start-up                     |     |

| b1  | HWR    | Hardware reset detect flag       | 0: Not detected                      | R   |

|     |        |                                  | 1: Detected                          |     |

| b2  | SWR    | Software reset detect flag       | 0: Not detected                      | R   |

|     |        |                                  | 1: Detected                          |     |

| b3  | WDR    | Watchdog timer reset detect flag | 0: Not detected                      | R   |

|     |        |                                  | 1: Detected                          |     |

| b4  | _      | Reserved bits                    | When read, the content is undefined. | R   |

| b5  | _      |                                  |                                      |     |

| b6  | _      |                                  |                                      |     |

| b7  | _      | Reserved bit                     | Set to 0.                            | R/W |

#### Notes:

- 1. The CWR bit is set to 0 (cold start-up) after power-on or voltage monitor 0 reset. This bit remains unchanged at a hardware reset, software reset, or watchdog timer reset.

- 2. If 1 is written to the CWR bit by a program, it is set to 1. (Writing 0 does not affect this bit.)

- 3. When the VW0C0 bit in the VW0C register is set to 0 (voltage monitor 0 reset disabled), the CWR bit value is undefined.

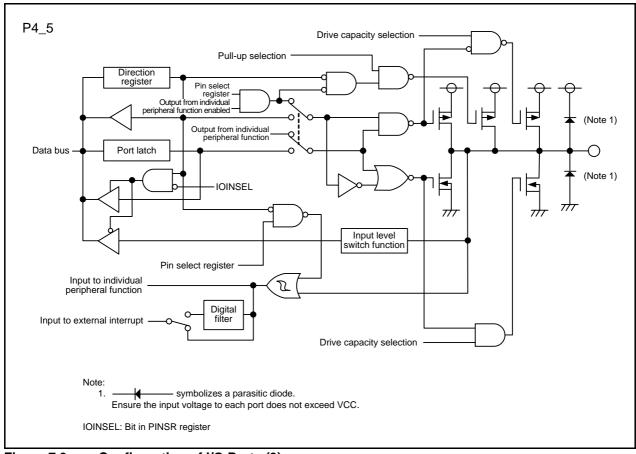

Figure 7.9 Configuration of I/O Ports (9)

b0

b1

# 7.4.25 USB Pin Select Register 0 (USBSR0)

Address 2F10h

Bit b7 b6 b5 b4 b3 b2

| Symbol      | USBVSENSEL | USBOVASEL | USBVBUSSEL | USBDMSEL | USBDPSEL | USBUPESEL | _ | _ |

|-------------|------------|-----------|------------|----------|----------|-----------|---|---|

| After Reset | 0          | 0         | 0          | 0        | 0        | 0         | 0 | 0 |

| Bit | Symbol     | Bit Name                       | Function                                        | R/W |

|-----|------------|--------------------------------|-------------------------------------------------|-----|

| b0  | _          | Reserved bits                  | Set to 0.                                       | R/W |

| b1  | _          |                                |                                                 |     |

| b2  | USBUPESEL  | USB_DPUPE pin select bit       | 0: USB_DPUPE pin not used 1: USB_DPUPE pin used | R/W |

| b3  | USBDPSEL   | USB_DP pin select bit          | 0: USB_DP pin not used 1: USB_DP pin used       | R/W |

| b4  | USBDMSEL   | USB_DM pin select bit          | 0: USB_DM pin not used 1: USB_DM pin used       | R/W |

| b5  | USBVBUSSEL | USB_VBUS pin select bit        | 0: USB_VBUS pin not used 1: USB_VBUS pin used   | R/W |

| b6  |            | USB_OVRCURA pin select bit (1) | 0: USB_OVRCURA pin not used 1: P7_6 assigned    | R/W |

| b7  | USBVSENSEL | USB_VBUSEN pin select bit (1)  | 0: USB_VBUSEN pin not used 1: P7_7 assigned     | R/W |

#### Note:

1. This bit is reserved and must be set to 0 in the R8C/3MU Group.

The USBSR0 register is used to select the pins for the USB.

Table 7.35 TRBO Pin Setting

| Register | TRBIOC | TRE   | BMR   | Function                                                    |

|----------|--------|-------|-------|-------------------------------------------------------------|

| Bit      | TOCNT  | TMOD1 | TMOD0 | T unction                                                   |

|          | 0      | 0     | 1     | Programmable waveform generation mode (pulse output)        |

| Setting  | 1      | 0     | 1     | Programmable waveform generation mode (programmable output) |

| Value    | 0      | 1     | 0     | Programmable one-shot generation mode                       |

|          | 0      | 1     | 1     | Programmable wait one-shot generation mode                  |

## Table 7.36 TRCIOA Pin Setting

| Register | TRCOER | TRCMR |      | TRCIOR0 |      | TRC   | CR2   | Function                              |

|----------|--------|-------|------|---------|------|-------|-------|---------------------------------------|

| Bit      | EA     | PWM2  | IOA2 | IOA1    | IOA0 | TCEG1 | TCEG0 | Function                              |

|          | 0      | 1     | 0    | 0       | 1    | Х     | Х     | Timer waveform output (output compare |

|          | U      | '     | U    | 1       | Χ    | ^     | ^     | function)                             |

| Setting  | 0      | 1     | 1    | Х       | Х    | Х     | Х     | Timer mode (input capture function)   |

| Value    | 1      | '     | ı    | ^       | ^    | ^     | ^     |                                       |

|          | 4      | 0     | Х    | Х       | Х    | 0     | 1     | PWM2 mode TRCTRG input                |

|          |        | U     | ^    | ^       | ^    | 1     | Х     |                                       |

X: 0 or 1

Table 7.37 TRCIOB Pin Setting

| Register | TRCOER | TRCMR |      | TRCIOR0 |      |      | Function                                        |

|----------|--------|-------|------|---------|------|------|-------------------------------------------------|

| Bit      | EB     | PWM2  | PWMB | IOB2    | IOB1 | IOB0 | Function                                        |

|          | 0      | 0     | Х    | Х       | Х    | Х    | PWM2 mode waveform output                       |

|          | 0      | 1     | 1    | Х       | Х    | Х    | PWM mode waveform output                        |

| Setting  | 0      | 1     | 0    | 0       | 0    | 1    | Timer waveform output (output compare function) |

| Value    | U      | '     | 0    | U       | 1    | Х    |                                                 |

|          | 0      | 1     | 0    | 1       | V    | V    | Timer mode (input capture function)             |

|          | 1      | '     | U    |         | ^    | ^    |                                                 |

X: 0 or 1

Table 7.38 TRCIOC Pin Setting

| Register         | TRCOER | TRO  | CMR  |      | TRCIOR1 |      | Function                                        |

|------------------|--------|------|------|------|---------|------|-------------------------------------------------|

| Bit              | EC     | PWM2 | PWMC | IOC2 | IOC1    | IOC0 | Function                                        |

|                  | 0      | 1    | 1    | Х    | Х       | Х    | PWM mode waveform output                        |

| C = 445 = ==     | 0      | 1    | 0    | 0    | 0       | 1    | Timer waveform output (output compare function) |

| Setting<br>Value | U      | '    | 0    | U    | 1       | Х    |                                                 |

| Value            | 0      | 1    | 0    | 1    | V       | v    | Timer mode (input capture function)             |

|                  | 1      | '    |      | '    | ^       | ^    |                                                 |

X: 0 or 1

Table 7.39 TRCIOD Pin Setting

| Register         | TRCOER | TRO  | CMR  | TRCIOR1 |      |      | Function                                        |

|------------------|--------|------|------|---------|------|------|-------------------------------------------------|

| Bit              | ED     | PWM2 | PWMD | IOD2    | IOD1 | IOD0 | Function                                        |

|                  | 0      | 1    | 1    | Х       | Х    | Х    | PWM mode waveform output                        |

| 0 - 11'          | 0      | 1    | 0    | 0       | 0    | 1    | Timer waveform output (output compare function) |

| Setting<br>Value | U      | '    | 0    | U       | 1    | Х    |                                                 |

| Value            | 0      | 1    | 0    | 1       | V    | V    | Timer mode (input capture function)             |

|                  | 1      | ı    | U    | I       | ^    | Х    |                                                 |

X: 0 or 1

As with other maskable interrupts, the timer RC interrupt, synchronous serial communication unit interrupt, I<sup>2</sup>C bus interface interrupt, and flash memory interrupt are controlled by the combination of the I flag, IR bit, bits ILVL0 to ILVL2, and IPL. However, since each interrupt source is generated by a combination of multiple interrupt request sources, the following differences from other maskable interrupts apply:

- When bits in the enable register are set to 1 and the corresponding bits in the status register are set to 1 (interrupt enabled), the IR bit in the interrupt control register is set to 1 (interrupt requested).

- When either bits in the status register or the corresponding bits in the enable register, or both are set to 0, the IR bit is set to 0 (no interrupt requested).

- That is, even if the interrupt is not acknowledged after the IR bit is set to 1, the interrupt request will not be retained.

- Also, the IR bit is not set to 0 even if 0 is written to this bit.

- Individual bits in the status register are not automatically set to 0 even if the interrupt is acknowledged. The IR bit is also not automatically set to 0 when the interrupt is acknowledged. Set individual bits in the status register to 0 in the interrupt routine. Refer to the status register figure for how to set individual bits in the status register to 0.

- When multiple bits in the enable register are set to 1 and other request sources are generated after the IR bit is set to 1, the IR bit remains 1.

- When multiple bits in the enable register are set to 1, use the status register to determine which request source causes an interrupt.

Refer to chapters of the individual peripheral functions (19. Timer RC, 23. Synchronous Serial Communication Unit (SSU), 24. I<sup>2</sup>C bus Interface, and 29. Flash Memory) for the status register and enable register. For the interrupt control register, refer to 11.3 Interrupt Control.

# 19.2.2 Timer RC Mode Register (TRCMR)

Address 0120h

| Bit         | b7     | b6 | b5  | b4  | b3   | b2   | b1   | b0   |

|-------------|--------|----|-----|-----|------|------|------|------|

| Symbol      | TSTART | _  | BFD | BFC | PWM2 | PWMD | PWMC | PWMB |

| After Reset | 0      | 1  | 0   | 0   | 1    | 0    | 0    | 0    |

| Bit | Symbol | Bit Name                                  | Function                                                | R/W |

|-----|--------|-------------------------------------------|---------------------------------------------------------|-----|

| b0  | PWMB   | PWM mode of TRCIOB select bit (1)         | 0: Timer mode<br>1: PWM mode                            | R/W |

| b1  | PWMC   | PWM mode of TRCIOC select bit (1)         | 0: Timer mode<br>1: PWM mode                            | R/W |

| b2  | PWMD   | PWM mode of TRCIOD select bit (1)         | 0: Timer mode<br>1: PWM mode                            | R/W |

| b3  | PWM2   | PWM2 mode select bit                      | 0: PWM 2 mode<br>1: Timer mode or PWM mode              | R/W |

| b4  | BFC    | TRCGRC register function select bit (2)   | General register     Buffer register of TRCGRA register | R/W |

| b5  | BFD    | TRCGRD register function select bit       | General register     Buffer register of TRCGRB register | R/W |

| b6  | _      | Nothing is assigned. If necessary, set to | 0. When read, the content is 1.                         | _   |

| b7  | TSTART | TRC count start bit                       | Count stops     Count starts                            | R/W |

#### Notes:

- 1. These bits are enabled when the PWM2 bit is set to 1 (timer mode or PWM mode).

- 2. Set the BFC bit to 0 (general register) in PWM2 mode.

For notes on PWM2 mode, refer to 19.9.6 TRCMR Register in PWM2 Mode.

## 19.2.14 Timer RC Pin Select Register (TRBRCSR)

| Address (   | 0181h |    |            |            |    |    |    |    |

|-------------|-------|----|------------|------------|----|----|----|----|

| Bit         | b7    | b6 | b5         | b4         | b3 | b2 | b1 | b0 |

| Symbol      | _     | _  | TRCCLKSEL1 | TRCCLKSEL0 | _  | 1  | 1  | _  |

| After Reset | 0     | 0  | 0          | 0          | 0  | 0  | 0  | 0  |

| Bit | Symbol     | Bit Name                                 | Function                            | R/W |

|-----|------------|------------------------------------------|-------------------------------------|-----|

| b0  | _          | Reserved bits                            | Set to 0.                           | R/W |

| b1  | _          |                                          |                                     | R/W |

| b2  | _          | Nothing is assigned. If necessary, set t | o 0. When read, the content is 0.   | _   |

| b3  | _          |                                          |                                     |     |

| b4  | TRCCLKSEL0 | TRCCLK pin select bit                    | b5 b4<br>  0 0: TRCCLK pin not used | R/W |

| b5  | TRCCLKSEL1 |                                          | 0 1: P1_4 assigned                  | R/W |

|     |            |                                          | 1 0: P3_3 assigned                  |     |

|     |            |                                          | 1 1: Do not set.                    |     |

| b6  | _          | Reserved bit                             | Set to 0.                           | R/W |

| b7  | _          | Nothing is assigned. If necessary, set t | o 0. When read, the content is 0.   | _   |

The TRBRCSR register selects which pin is assigned to the timer RC I/O. To use the I/O pin for timer RC, set this register.

Set bits TRCCLKSEL0 to TRCCLKSEL1 before setting the timer RC associated registers. Also, do not change the setting values. Do not change the setting values of bits TRCCLKSEL0 to TRCCLKSEL1 during timer RC operation.

## 19.2.15 Timer RC Pin Select Register 0 (TRCPSR0)

Address 0182h

| Bit         | b7 | b6 | b5         | b4         | b3 | b2         | b1         | b0         |

|-------------|----|----|------------|------------|----|------------|------------|------------|

| Symbol      | _  | _  | TRCIOBSEL1 | TRCIOBSEL0 | _  | TRCIOASEL2 | TRCIOASEL1 | TRCIOASEL0 |

| After Reset | 0  | 0  | 0          | 0          | 0  | 0          | 0          | 0          |

| Bit            | Symbol                | Bit Name                                  | Function                                                                                                              | R/W               |

|----------------|-----------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|

| b0<br>b1<br>b2 | TRCIOASEL1 TRCIOASEL2 | TRCIOA/TRCTRG pin select bit              | b2 b1 b0<br>0 0 0: TRCIOA/TRCTRG pin not used<br>0 0 1: P1_1 assigned<br>0 1 0: P0_0 assigned<br>0 1 1: P0_1 assigned | R/W<br>R/W<br>R/W |

| b3             | _                     | Nothing is assigned. If necessary, set to | 1 0 0: P0_2 assigned Other than above: Do not set. to 0. When read, the content is 0.                                 | _                 |

| b4<br>b5       | TRCIOBSEL0 TRCIOBSEL1 | TRCIOB pin select bit                     | 0 0: TRCIOB pin not used<br>0 1: P1_2 assigned<br>1 0: P0_3 assigned<br>1 1: P0_4 assigned                            | R/W<br>R/W        |

| b6             | _                     | Reserved bit                              | Set to 0.                                                                                                             | R/W               |

| b7             | _                     | Nothing is assigned. If necessary, set t  | o 0. When read, the content is 0.                                                                                     | _                 |

The TRCPSR0 register selects which pin is assigned to the timer RC I/O. To use the I/O pin for timer RC, set this register.

Set the TRCPSR0 register before setting the timer RC associated registers. Also, do not change the setting value in this register during timer RC operation.

# 19.4.1 Timer RC I/O Control Register 0 (TRCIOR0) for Input Capture Function

| Address     | 0124h |      |      |      |      |      |      |      |

|-------------|-------|------|------|------|------|------|------|------|

| Bit         | b7    | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

| Symbol      | _     | IOB2 | IOB1 | IOB0 | IOA3 | IOA2 | IOA1 | IOA0 |

| After Reset | 1     | 0    | 0    | 0    | 1    | 0    | 0    | 0    |

| Bit      | Symbol       | Bit Name                                  | Function                                                                                                                                                                                                                                                          | R/W        |

|----------|--------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| b0<br>b1 | IOA0<br>IOA1 | TRCGRA control bit                        | 0 0: Input capture to the TRCGRA register at the rising edge     1: Input capture to the TRCGRA register at the falling edge     1 0: Input capture to the TRCGRA register at both edges     1 1: Do not set.                                                     | R/W<br>R/W |

| b2       | IOA2         | TRCGRA mode select bit (1)                | Set to 1 (input capture) in the input capture function.                                                                                                                                                                                                           | R/W        |

| b3       | IOA3         | TRCGRA input capture input switch bit (3) | 0: fOCO128 signal<br>1: TRCIOA pin input                                                                                                                                                                                                                          | R/W        |

| b4<br>b5 | IOB0<br>IOB1 | TRCGRB control bit                        | <ul> <li>b5 b4</li> <li>0 0: Input capture to the TRCGRB register at the rising edge</li> <li>0 1: Input capture to the TRCGRB register at the falling edge</li> <li>1 0: Input capture to the TRCGRB register at both edges</li> <li>1 1: Do not set.</li> </ul> | R/W<br>R/W |

| b6       | IOB2         | TRCGRB mode select bit (2)                | Set to 1 (input capture) in the input capture function.                                                                                                                                                                                                           | R/W        |

| b7       | _            | Nothing is assigned. If necessary, se     | t to 0. When read, the content is 1.                                                                                                                                                                                                                              | _          |

### Notes:

- 1. When the BFC bit in the TRCMR register is set to 1 (buffer register of TRCGRA register), set the IOC2 bit in the TRCIOR1 register to the same value as the IOA2 bit in the TRCIOR0 register.

- 2. When the BFD bit in the TRCMR register is set to 1 (buffer register of TRCGRB register), set the IOD2 bit in the TRCIOR1 register to the same value as the IOB2 bit in the TRCIOR0 register.

- 3. The IOA3 bit is enabled when the IOA2 bit is set to 1 (input capture function).

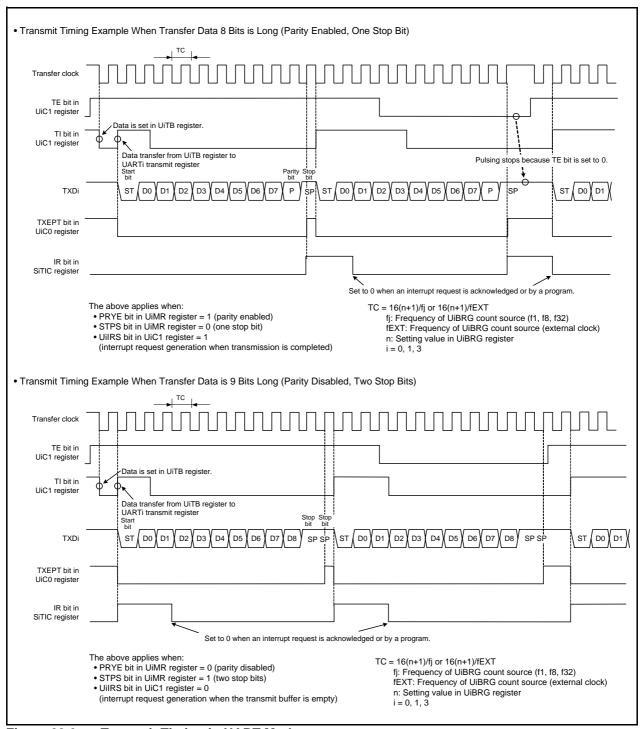

Figure 20.6 Transmit Timing in UART Mode

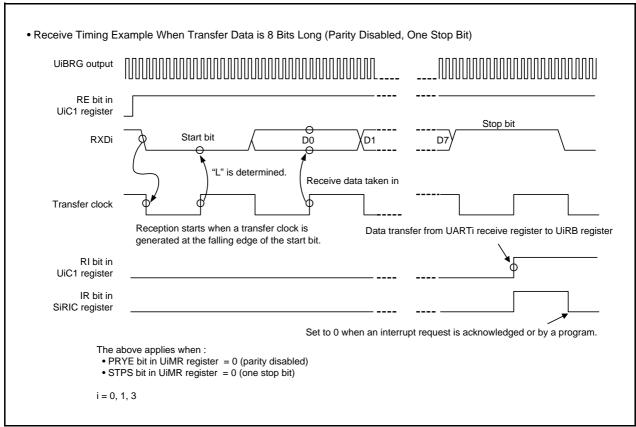

Figure 20.7 Receive Timing in UART Mode

## 24.2.6 IIC bus Control Register 1 (ICCR1)

| Address (   | )198h |      |     |     |      |      |      |      |   |

|-------------|-------|------|-----|-----|------|------|------|------|---|

| Bit         | b7    | b6   | b5  | b4  | b3   | b2   | b1   | b0   |   |

| Symbol      | ICE   | RCVD | MST | TRS | CKS3 | CKS2 | CKS1 | CKS0 | ì |

| After Reset | 0     | 0    | 0   | 0   | 0    | 0    | 0    | 0    |   |

| Bit | Symbol | Bit Name                                                 | Function                                              | R/W     |

|-----|--------|----------------------------------------------------------|-------------------------------------------------------|---------|

| b0  | CKS0   | Transmit clock select bits 3 to 0 (1)                    | b3 b2 b1 b0<br>0 0 0 0; f1/28                         | R/W     |

| b1  | CKS1   |                                                          | 0 0 0 1: f1/40                                        | R/W     |

| b2  | CKS2   |                                                          | 0 0 1 0: f1/48                                        | R/W     |

| b3  | CKS3   |                                                          | 0 0 1 1: f1/64                                        | R/W     |

|     |        |                                                          | 0 1 0 0: f1/80                                        |         |

|     |        |                                                          | 0 1 0 1: f1/100                                       |         |

|     |        |                                                          | 0 1 1 0: f1/112                                       |         |

|     |        |                                                          | 0 1 1 1: f1/128                                       |         |

|     |        |                                                          | 1 0 0 0: f1/56                                        |         |

|     |        |                                                          | 1 0 0 1: f1/80                                        |         |

|     |        |                                                          | 1 0 1 0: f1/96                                        |         |

|     |        |                                                          | 1 0 1 1: f1/128                                       |         |

|     |        |                                                          | 1 1 0 0: f1/160                                       |         |

|     |        |                                                          | 1 1 0 1: f1/200                                       |         |

|     |        |                                                          | 1 1 1 0: f1/224                                       |         |

|     |        |                                                          | 1 1 1 1: f1/256                                       |         |

| b4  | TRS    | Transfer/receive select bit (2, 3, 6)                    | b5 b4                                                 | R/W     |

| b5  | MST    | Master/slave select bit (5, 6)                           | 0 0: Slave Receive Mode (4)                           | R/W     |

|     |        |                                                          | 0 1: Slave Transmit Mode                              |         |

|     |        |                                                          | 1 0: Master Receive Mode<br>1 1: Master Transmit Mode |         |

| b6  | RCVD   | Receive disable bit                                      | After reading the ICDRR register while the TRS bit is | R/W     |

| 00  | RCVD   | Receive disable bit                                      | Iset to 0                                             | K/VV    |

|     |        |                                                          | 0: Next receive operation continues                   |         |

|     |        |                                                          | 1: Next receive operation disabled                    |         |

| b7  | ICE    | I <sup>2</sup> C bus interface enable bit <sup>(7)</sup> | 0: This module is halted                              | R/W     |

| D7  | ICE    | Lec bus interface enable bit (*)                         | (Pins SCL and SDA are set to a port function)         | 17/ / / |

|     |        |                                                          | 1: This module is enabled for transfer operations     |         |

|     |        |                                                          | (Pins SCL and SDA are in a bus drive state)           |         |

|     |        |                                                          | (1 mo ool and oblit are in a bas arive state)         |         |

#### Notes

- 1. Set according to the necessary transfer rate in master mode. Refer to **Tables 24.4 and 24.5 Transfer Rate Examples** for the transfer rate. This bit is used for maintaining the setup time in transmit mode of slave mode.

The time is 10Tcyc when the CKS3 bit is set to 0 and 20Tcyc when the CKS3 bit is set to 1. (1Tcyc = 1/f1(s))

- 2. Rewrite the TRS bit between transfer frames.

- 3. When the first 7 bits after the start condition in slave receive mode match the slave address set in the SAR register and the 8th bit is set to 1, the TRS bit is set to 1.

- 4. In master mode with the I<sup>2</sup>C bus format, if arbitration is lost, bits MST and TRS are set to 0 and the IIC enters slave receive mode.

- 5. When an overrun error occurs in master receive mode with the clock synchronous serial format, the MST bit is set to 0 and the I<sup>2</sup>C bus enters slave receive mode.

- 6. In multimaster operation, use the MOV instruction to set bits TRS and MST.

- 7. When writing 0 to the ICE bit or 1 to the IICRST bit in the ICCR2 register during an I<sup>2</sup>C bus interface operation, the BBSY bit in the ICCR2 register and the STOP bit in the ICSR register may become undefined. Refer to **24.9**Notes on I<sup>2</sup>C bus Interface.

# 26. USB 2.0 Host/Function Module (USB)

#### Note

The description offered in this chapter is based on the R8C/3MK Group. For R8C/3MU Group, refer to **1.1.2 Differences between Groups**.

### 26.1 Overview

R8C/3MK Group provides one port of USB2.0 host/function module (USB).

The USB is a USB controller which provides capabilities as a USB host controller and a USB function controller. The USB supports full-speed transfer defined by the USB (universal serial bus) Specifications 2.0 when used as the host controller, and supports control transfer, bulk transfer, and interrupt transfer when used as the function controller. Also, the USB has a USB transceiver and supports all of the transfer types defined by the USB Specifications.

The USB has buffer memory for data transfer, providing a maximum of five pipes. Any endpoint numbers can be assigned to PIPE4 to PIPE7, based on the peripheral devices or user system for communication. Table 26.1 shows the USB Specifications.

Table 26.1 USB Specifications

| Item                             | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features                         | <ul> <li>USB Device Controller (UDC) and transceiver for USB2.0 are incorporated.</li> <li>The USB host controller and USB function controller are incorporated (can be switched by software).</li> <li>Self-power mode or bus-power mode can be selected.</li> <li>(1) Features of the USB host controller</li> <li>Full-speed transfer (12 Mbps) is supported</li> <li>Automatic scheduling for SOF and packet transmissions</li> <li>Programmable intervals for interrupt transfers</li> <li>(2) Features of the USB function controller</li> <li>Full-speed transfer (12 Mbps) is supported</li> <li>Control transfer stage control function</li> <li>Device state control function</li> <li>Auto response function for SET_ADDRESS request</li> <li>SOF interpolation function</li> </ul> |

| Communication data transfer type | Control transfer     Bulk transfer     Interrupt transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pipe configuration               | <ul> <li>Buffer memory for USB communications is provided.</li> <li>Up to five pipes can be selected (including the default control pipe).</li> <li>Usable pipe numbers are 0, 4, 5, 6, and 7.</li> <li>Endpoint numbers can be assigned flexibly to PIPE4 to PIPE7.</li> <li>Transfer conditions that can be set for each pipe: PIPE0: Control transfer only (default control pipe: DCP), 64 bytes (single buffer)</li> <li>PIPE4 and PIPE5: Bulk transfer only Buffer size: 64 bytes (double buffer can be specified)</li> <li>PIPE6 and PIPE7: Interrupt transfer only Buffer size: 64 bytes (single buffer)</li> </ul>                                                                                                                                                                     |

| Others                           | <ul> <li>Reception ending function using transaction count</li> <li>Function that changes the BRDY interrupt event notification timing (BFRE)</li> <li>NAK setting function for response PID generated by end of transfer (SHTNAK)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

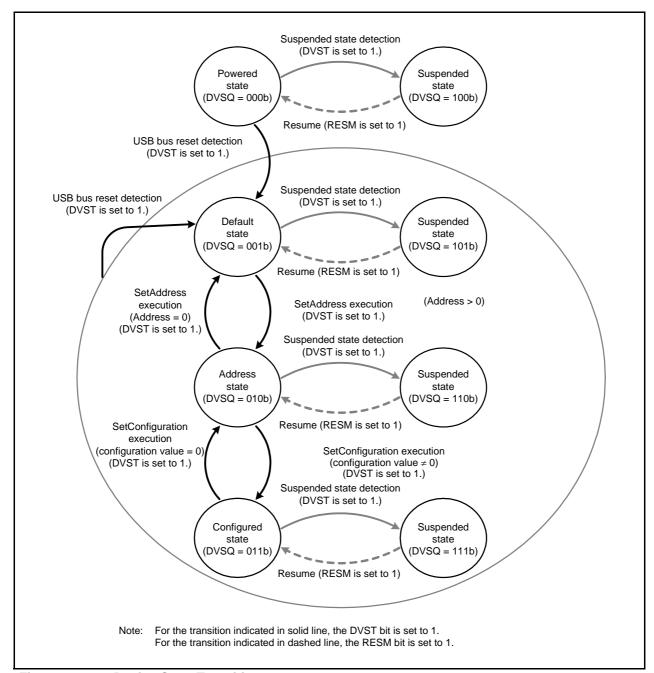

### 26.3.3.4 Device State Transition Interrupt

Figure 26.9 is a diagram of Device State Transitions in the USB module. The USB module controls device state and generates device state transition interrupts. However, recovery from the suspended state (resume signal detection) is detected by means of the resume interrupt. The device state transition interrupts can be enabled or disabled individually using INTENB0. The device state to which a transition was made can be confirmed using the DVSQ bits in INTSTS0.

When a transition is made to the default state, a device state transition interrupt is generated after a USB bus reset is detected.

Device state can be controlled only when the function controller function is selected. The device state transition interrupts can also be generated only when the function controller function is selected.

Figure 26.9 Device State Transitions

### 26.3.6.2 Control Transfers when Function Controller Function is Selected

#### (1) Setup Stage

The USB module always sends an ACK response for a correct setup packet targeted to the USB module. The operation of the USB module in the setup stage is described below.

When receiving a new setup packet, the USB module sets the following bits.

- Set the VALID bit in INTSTS0 to 1.

- Set the PID bits in DCPCTR to NAK.

- Set the CCPL bit in DCPCTR to 0.

When receiving a data packet right after the setup packet, the USB module stores the USB request parameters in USBREQ, USBVAL, USBINDX, and USBLENG.

Response processing with respect to the control transfer should always be carried out after setting VALID = 0. In the VALID = 1 state, PID = BUF cannot be set, and the data stage cannot be terminated.

Using the function of the VALID bit, the USB module can suspend the current request processing when receiving a new USB request during a control transfer, and can send a response to the newest request.

In addition, the USB module automatically detects the direction bit (bit 8 of bmRequestType) and the request data length (wLength) of the received USB request, distinguishes between control read transfer, control write transfer, and no-data control transfer, and controls stage transitions. For a wrong sequence, the sequence error of the control transfer stage transition interrupt is generated, and the software is notified of occurrence of the error. For the stage control of the USB module, refer to **Figure 26.10**.

#### (2) Data Stage

Data transfers corresponding to received USB requests should be done using the DCP. Before accessing the DCP buffer memory, the access direction should be specified using the ISEL bit in CFIFOSEL.

If the transfer data is larger than the size of the DCP buffer memory, the data transfer should be carried out using the BRDY interrupt for control write transfers and the BEMP interrupt for control read transfers.

#### (3) Status Stage

Control transfers are terminated by setting the CCPL bit to 1 while the PID bits in DCPCTR are set to BUF. After the above settings have been made, the USB module automatically executes the status stage in accordance with the data transfer direction determined at the setup stage. The specific procedure is as follows.

• For control read transfers

The USB module transmits a zero-length packet and receives an ACK response from the USB host.

• For control write transfers and no-data control transfers

The USB module receives a zero-length packet from the USB host and sends an ACK response.

### (4) Control Transfer Auto Response Function

The USB module automatically responds to a correct SET\_ADDRESS request. If any of the following errors occurs in the SET\_ADDRESS request, a response from the software is necessary.

- Any transfer other than a control read transfer: bmRequestType ≠ 00h

- Request error: wIndex  $\neq$  00h

- Any transfer other than a no-data control transfer: wLength ≠ 00h

- Request error: wValue > 7Fh

- Control transfer of a device state error: DVSQ = 011b (Configured)

For all requests other than the SET\_ADDRESS request, a response is required from the corresponding software.

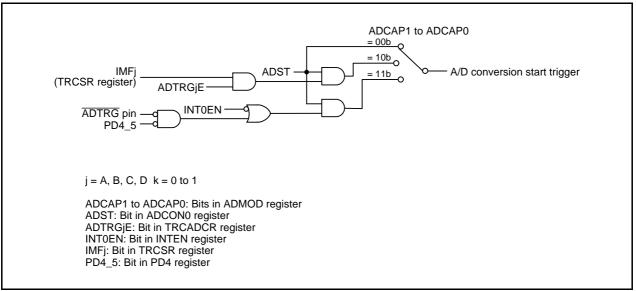

### 27.3.3 A/D Conversion Start Condition

A software trigger, trigger from timer RC, and external trigger are used as A/D conversion start triggers. Figure 27.4 shows the Block Diagram of A/D Conversion Start Control Unit.

Figure 27.4 Block Diagram of A/D Conversion Start Control Unit

### 27.3.3.1 Software Trigger

A software trigger is selected when bits ADCAP1 to ADCAP0 in the ADMOD register are set to 00b (software trigger).

The A/D conversion starts when the ADST bit in the ADCON0 register is set to 1 (A/D conversion starts).

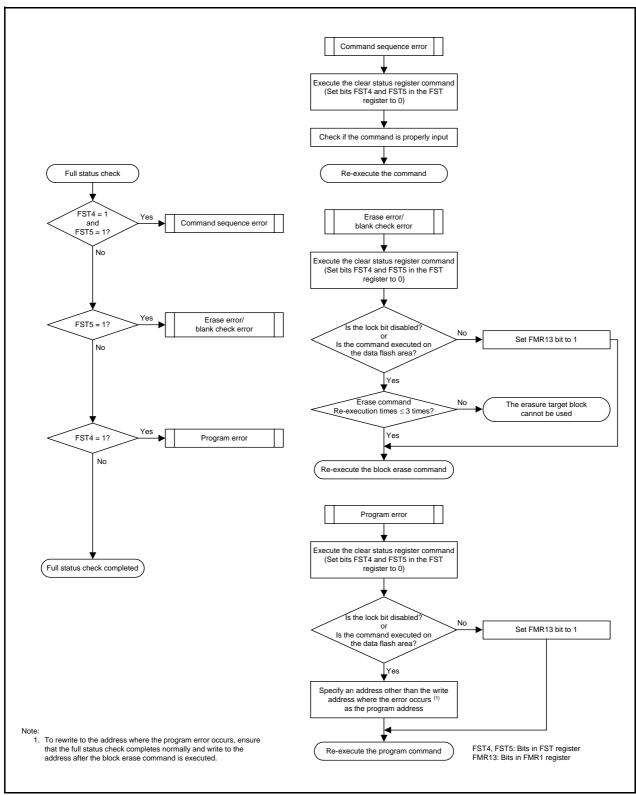

Figure 29.17 Full Status Check and Handling Procedure for Individual Errors

### 29.6 Parallel I/O Mode

Parallel I/O mode is used to input and output software commands, addresses and data necessary to control (read, program, and erase) the on-chip flash memory.

Use a parallel programmer which supports the MCU. Contact the parallel programmer manufacturer for more information. Refer to the user's manual included with your parallel programmer for instructions.

In parallel I/O mode, the user ROM areas shown in Figures 29.1 and 29.2 can be rewritten.

### 29.6.1 ROM Code Protect Function

The ROM code protect function prevents the flash memory from being read and rewritten (refer to **29.3.2 ROM Code Protect Function**).

Table 31.35 Recommended Operating Conditions (1)

| Symbol                      | Parameter                                      |                               |                                              |                        | Conditions                                       | Standard |           |          | Unit  |

|-----------------------------|------------------------------------------------|-------------------------------|----------------------------------------------|------------------------|--------------------------------------------------|----------|-----------|----------|-------|

| Syllibol                    |                                                |                               |                                              |                        | Conditions                                       | Min.     | Тур.      | Max.     | Offic |

| Vcc/AVcc                    | Supply voltage                                 | When USB function is used     |                                              |                        |                                                  | 3.0      | 5.0       | 5.5      | V     |

|                             |                                                | When USB function is not used |                                              |                        |                                                  | 1.8      | 5.0       | 5.5      | V     |

| UVcc                        | USB Supply                                     | When USB function is used     |                                              |                        | Vcc/AVcc = 3.0 to                                | _        | Vcc/      | _        | V     |

|                             | Voltage (When                                  |                               |                                              |                        | 3.6 V                                            |          | AVcc      |          |       |

|                             | UVCC pin is                                    |                               |                                              |                        |                                                  |          | (4)       |          |       |

|                             | input)                                         | When USB function is not used |                                              |                        | Vcc/AVcc = 1.8 to                                | _        | Vcc/      | _        | V     |

|                             |                                                |                               |                                              |                        | 5.5 V                                            |          | AVcc      |          |       |

|                             |                                                |                               |                                              |                        |                                                  |          | (4)       |          |       |

| Vss/AVss                    | Supply voltage                                 |                               |                                              |                        |                                                  | _        | 0         | _        | V     |

| VIH                         | Input "H" voltage                              | Other th                      | han CMOS input                               |                        |                                                  | 0.8 Vcc  |           | Vcc      | V     |

|                             | , ,                                            |                               | Inputlevel                                   | Input level selection: | 4.0 V ≤ Vcc ≤ 5.5 V                              | 0.5 Vcc  | _         | Vcc      | V     |

|                             |                                                | input                         | switching                                    | 0.35 Vcc               | 2.7 V ≤ Vcc < 4.0 V                              | 0.55 Vcc | _         | Vcc      | V     |

|                             |                                                |                               | function                                     |                        | 1.8 V ≤ Vcc < 2.7 V                              | 0.65 Vcc |           | Vcc      | V     |

|                             |                                                |                               | (I/O port)                                   | Input level selection: | 4.0 V ≤ Vcc ≤ 5.5 V                              | 0.65 Vcc | _         | Vcc      | V     |

|                             |                                                |                               | (                                            | 0.5 Vcc                | 2.7 V ≤ Vcc < 4.0 V                              | 0.7 Vcc  |           | Vcc      | V     |

|                             |                                                |                               |                                              |                        | 1.8 V ≤ Vcc < 2.7 V                              | 0.8 Vcc  | _         | Vcc      | V     |

|                             |                                                |                               |                                              | Input level selection: | 4.0 V ≤ Vcc ≤ 5.5 V                              | 0.85 Vcc | _         | Vcc      | V     |

|                             |                                                |                               |                                              | 0.7 Vcc                | 2.7 V ≤ Vcc < 4.0 V                              | 0.85 Vcc |           | Vcc      | V     |

|                             |                                                |                               |                                              | 0.7 VCC                | $1.8 \text{ V} \le \text{VCC} < 4.0 \text{ V}$   | 0.85 VCC |           | Vcc      | V     |

|                             |                                                | Evtorno                       | l<br>Il clock input                          | (YOUT)                 | 1.0 V \( \text{V} \)                             | 1.2      |           | Vcc      | V     |

| Mu                          | Input "L" voltage                              |                               | nan CMOS i                                   |                        |                                                  |          |           |          | V     |

| VIL                         | input L voltage                                | CMOS                          |                                              |                        | 4.0 V ≤ Vcc ≤ 5.5 V                              | 0        |           | 0.2 Vcc  | V     |

|                             |                                                |                               | Input level                                  |                        |                                                  | 0        | _         | 0.2 Vcc  |       |

|                             |                                                | input                         | switching                                    | 0.35 Vcc               | 2.7 V ≤ Vcc < 4.0 V                              | 0        | _         | 0.2 Vcc  | V     |

|                             |                                                |                               | function                                     |                        | 1.8 V ≤ Vcc < 2.7 V                              | 0        | _         | 0.2 Vcc  | V     |

|                             |                                                |                               | (I/O port)                                   | Input level selection: | 4.0 V ≤ Vcc ≤ 5.5 V                              | 0        |           | 0.4 Vcc  | V     |

|                             |                                                |                               |                                              | 0.5 Vcc                | 2.7 V ≤ Vcc < 4.0 V                              | 0        | _         | 0.3 Vcc  | V     |

|                             |                                                |                               |                                              |                        | 1.8 V ≤ Vcc < 2.7 V                              | 0        | _         | 0.2 Vcc  | V     |

|                             |                                                |                               |                                              | Input level selection: | 4.0 V ≤ Vcc ≤ 5.5 V                              | 0        | _         | 0.55 Vcc | V     |

|                             |                                                |                               |                                              | 0.7 Vcc                | $2.7 \text{ V} \le \text{Vcc} < 4.0 \text{ V}$   | 0        | _         | 0.45 Vcc | V     |

|                             |                                                |                               |                                              |                        | $1.8 \text{ V} \le \text{Vcc} < 2.7 \text{ V}$   | 0        | _         | 0.35 Vcc | V     |

|                             |                                                |                               | I clock input                                | (XOUT)                 |                                                  | 0        | _         | 0.4      | V     |

| IOH(sum)                    | Peak sum output                                | "H"                           | Sum of all                                   | pins IOH(peak)         |                                                  | _        | _         | -160     | mΑ    |

| •                           | current                                        |                               |                                              |                        |                                                  |          |           |          |       |

| IOH(sum)                    | Average sum output "H"                         |                               | Sum of all pins IOH(avg)                     |                        |                                                  | _        | _         | -80      | mΑ    |

|                             | current                                        |                               |                                              |                        |                                                  |          |           |          |       |

| IOH(peak)                   | Peak output "H" current                        |                               | Drive capacity Low                           |                        |                                                  | _        | _         | -10      | mΑ    |

|                             |                                                |                               | Drive capacity High                          |                        |                                                  | _        | _         | -40      | mA    |

| IOH(avg)                    | Average output "H" current Peak sum output "L" |                               | Drive capacity Low                           |                        |                                                  | _        | _         | -5       | mA    |

|                             |                                                |                               | Drive capacity High                          |                        |                                                  | _        | _         | -20      | mA    |

|                             |                                                |                               | Sum of all pins IOL(peak)                    |                        |                                                  | _        | _         | 160      | mA    |

|                             | current                                        |                               |                                              | F                      |                                                  |          |           |          |       |

| IOL(sum) IOL(peak) IOL(avg) |                                                |                               | Sum of all pins IoL(avg)  Drive capacity Low |                        |                                                  |          | _         | 80       | mA    |

|                             |                                                |                               |                                              |                        |                                                  |          |           |          | , \   |

|                             |                                                |                               |                                              |                        |                                                  | _        | _         | 10       | mA    |

|                             | . Jan Japan E 0                                |                               | Drive capacity High                          |                        |                                                  | _        | _         | 40       | mA    |

|                             | Average output "L"                             |                               | Drive capacity Low                           |                        |                                                  |          | <b></b> _ | 5        | mA    |

|                             | current                                        |                               | Drive capacity Low  Drive capacity High      |                        |                                                  |          |           | 20       | mA    |

|                             | XIN clock input oscillation frequency          |                               |                                              | 2.7 V ≤ Vcc ≤ 5.5 V    |                                                  |          | 20        | MHz      |       |

|                             | Any Gook input oscillation nequency            |                               |                                              |                        | $1.8 \text{ V} \le \text{VCC} \le 3.3 \text{ V}$ | _        |           | 5        | MHz   |

| fOCO40M                     | When used as the count source for timer RC (3) |                               |                                              |                        |                                                  | 22       |           | 40       | MHz   |

|                             |                                                |                               |                                              |                        | 2.7 V ≤ Vcc ≤ 5.5 V                              | 32       |           |          |       |

| fOCO-F                      | fOCO-F frequency                               |                               |                                              |                        | 2.7 V ≤ Vcc ≤ 5.5 V                              | _        | _         | 20       | MHz   |

|                             | Out and of frame                               |                               |                                              |                        | 1.8 V ≤ Vcc < 2.7 V                              | _        | _         | 5        | MHz   |

| _                           | System clock frequency                         |                               |                                              |                        | 2.7 V ≤ Vcc ≤ 5.5 V                              | _        |           | 20       | MHz   |

| _                           |                                                |                               |                                              |                        | 1.8 V ≤ Vcc < 2.7 V                              |          |           | 5        | MHz   |

| f(BCLK)                     | CPU clock frequency                            |                               |                                              |                        | 2.7 V ≤ Vcc ≤ 5.5 V                              | _        | _         | 20       | MHz   |

|                             |                                                |                               |                                              |                        | 1.8 V ≤ Vcc < 2.7 V                              |          |           | 5        | MHz   |

|                             | PLL frequency sy                               | mthesize                      | er stabilization                             | n wait time            | 4.0 V ≤ Vcc ≤ 5.5 V                              | _        |           | 2        | ms    |

|                             |                                                |                               |                                              |                        | 2.7 V ≤ Vcc < 4.0 V                              | _        | _         | 3        | ms    |

#### Notes:

- 1. Vcc = 1.8 to 5.5 V and  $T_{opr} = -20$  to 85 °C (N version), unless otherwise specified.

- 2. The average output current indicates the average value of current measured during 100 ms.

- 3. fOCO40M can be used as the count source for timer RC in the range of Vcc = 2.7 to 5.5 V.

- 4. Connect Vcc/AVcc for the UVcc pin input.

#### 32.15.1.3 How to Access

To set one of the following bits to 1, first write 0 and then 1 immediately. Disable interrupts and DTC activation between writing 0 and writing 1.

- The FMR01 bit or FMR02 bit in the FMR0 register

- The FMR13 bit in the FMR1 register

- The FMR20 bit, FMR22 bit, or FMR 27 bit in the FMR2 register

To set one of the following bits to 0, first write 1 and then 0 immediately. Disable interrupts and DTC activation between writing 1 and writing 0.

• The FMR14 bit, FMR15 bit, FMR16 bit, or FMR17 bit in the FMR1 register

## 32.15.1.4 Rewriting User ROM Area

In EW0 mode, if the supply voltage drops while rewriting any block in which a rewrite control program is stored, it may not be possible to rewrite the flash memory because the rewrite control program cannot be rewritten correctly. In this case, use standard serial I/O mode.

## **32.15.1.5 Programming**

Do not write additions to the already programmed address.

## 32.15.1.6 Entering Stop Mode or Wait Mode

Do not enter stop mode or wait mode during erase-suspend.

If the FST7 bit in the FST register is set to 0 (busy (during programming or erasure execution), do not enter to stop mode or wait mode.

Do not enter stop mode or wait mode while the FMR27 bit is 1 (low-current-consumption read mode enabled).

## 32.15.1.7 Programming and Erasure Voltage for Flash Memory

To perform programming and erasure, use VCC = 2.7 to 5.5 V as the supply voltage. Do not perform programming and erasure at less than 2.7 V.

#### 32.15.1.8 Block Blank Check

Do not execute the block blank check command during erase-suspend.

### 32.15.1.9 Low-Current-Consumption Read Mode

In low-speed on-chip oscillator mode, the current consumption when reading the flash memory can be reduced by setting the FMR27 bit in the FMR2 register to 1 (low-current-consumption read mode enabled).

Low-current-consumption read mode can be used when the CPU clock is set to either of the following:

• The CPU clock is set to the low-speed on-chip oscillator clock divided by 4, 8, or 16.

However, do not use low-current-consumption read mode when the frequency of the selected CPU clock is 3 kHz or below. After setting the divide ratio of the CPU clock, set the FMR27 bit to 1 (low-current-consumption read mode enabled).

To reduce the power consumption, refer to **30. Reducing Power Consumption**.

Enter wait mode or stop mode after setting the FMR27 bit to 0 (low-current-consumption read mode disabled). Do not enter wait mode or stop mode while the FMR27 bit is 1 (low-current-consumption read mode enabled).