Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 2x14b; D/A 2x9b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24633-24pvxi |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

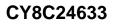

# **Block Diagram**

#### Additional System Resources

System resources, some of which have been previously listed, provide additional capability useful to complete systems. Additional resources include a multiplier, decimator, low voltage detection, and power on reset. Brief statements describing the merits of each system resource are presented below.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks can be generated using digital PSoC blocks as clock dividers.

- A multiply accumulate (MAC) provides a fast 8-bit multiplier with 32-bit accumulate, to assist in both general math as well as digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of Delta Sigma ADCs.

- The I<sup>2</sup>C module provides 100 and 400 kHz communication over two wires. Slave, master, and multi-master modes are all supported.

- Low-voltage detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced power-on reset (POR) circuit eliminates the need for a system supervisor.

- An internal 1.3 V reference provides an absolute reference for the analog system, including ADCs and DACs.

#### **PSoC Device Characteristics**

Depending on your PSoC device characteristics, the digital and analog systems can have 16, 8, or 4 digital blocks and 12, 6, or 3 analog blocks. The following table lists the resources available for specific PSoC device groups.

| PSoC Part<br>Number | Digital<br>I/O | Digital<br>Rows | Digital<br>Blocks | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Columns | Analog<br>Blocks               | SRAM<br>Size | Flash<br>Size | SAR<br>ADC |

|---------------------|----------------|-----------------|-------------------|------------------|-------------------|-------------------|--------------------------------|--------------|---------------|------------|

| CY8C29x66           | up to 64       | 4               | 16                | up to 12         | 4                 | 4                 | 12                             | 2 K          | 32 K          | No         |

| CY8C28xxx           | up to 44       | up to 3         | up to 12          | up to 44         | up to 4           | up to 6           | up to<br>12 + 4 <sup>[1]</sup> | 1 K          | 16 K          | Yes        |

| CY8C27x43           | up to 44       | 2               | 8                 | up to 12         | 4                 | 4                 | 12                             | 256          | 16 K          | No         |

| CY8C24x94           | up to 56       | 1               | 4                 | up to 48         | 2                 | 2                 | 6                              | 1 K          | 16 K          | No         |

| CY8C24x23A          | up to 24       | 1               | 4                 | up to 12         | 2                 | 2                 | 6                              | 256          | 4 K           | No         |

| CY8C23x33           | up to 26       | 1               | 4                 | up to 12         | 2                 | 2                 | 4                              | 256          | 8 K           | Yes        |

| CY8C22x45           | up to 38       | 2               | 8                 | up to 38         | 0                 | 4                 | 6 <sup>[1]</sup>               | 1 K          | 16 K          | No         |

| CY8C21x45           | up to 24       | 1               | 4                 | up to 24         | 0                 | 4                 | 6 <sup>[1]</sup>               | 512          | 8 K           | Yes        |

| CY8C21x34           | up to 28       | 1               | 4                 | up to 28         | 0                 | 2                 | 4 <sup>[1]</sup>               | 512          | 8 K           | No         |

| CY8C21x23           | up to 16       | 1               | 4                 | up to 8          | 0                 | 2                 | 4 <sup>[1]</sup>               | 256          | 4 K           | No         |

| CY8C20x34           | up to 28       | 0               | 0                 | up to 28         | 0                 | 0                 | 3 <sup>[1,2]</sup>             | 512          | 8 K           | No         |

| CY8C20xx6           | up to 36       | 0               | 0                 | up to 36         | 0                 | 0                 | 3 <sup>[1,2]</sup>             | up to<br>2 K | up to<br>32 K | No         |

#### Table 1. PSoC Device Characteristics

Notes

Limited analog functionality.

Two analog blocks and one CapSense<sup>®</sup>.

# **Development Tools**

PSoC Designer<sup>™</sup> is the revolutionary integrated design environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- Hardware and software I<sup>2</sup>C slaves and masters

- □ Full-speed USB 2.0

- Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

## **PSoC Designer Software Subsystems**

#### Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use the PSoC blocks, which are called user modules. Examples of user modules are analog-to-digital converters (ADCs), digital-to-analog converters (DACs), amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this lets you to use more than 100 percent of PSoC's resources for an application.

#### Code Generation Tools

The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. You can develop your design in C, assembly, or a combination of the two.

**Assemblers**. The assemblers allow you to merge assembly code seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compilers.** C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all of the features of C, tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### Debugger

PSoC Designer has a debug environment that provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow you to read and program and read and write data memory, and read and write I/O registers. You can read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also lets you to create a trace buffer of registers and memory locations of interest.

#### Online Help System

The online help system displays online, context-sensitive help. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer.

#### In-Circuit Emulator

A low-cost, high-functionality in-circuit emulator (ICE) is available for development support. This hardware can program single devices.

The emulator consists of a base unit that connects to the PC using a USB port. The base unit is universal and operates with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full-speed (24 MHz) operation.

### Table 4. Register Map Bank 0 Table: User Space

|          |              |    | Table: User |              |        |            |              |        |                                              |              |          |

|----------|--------------|----|-------------|--------------|--------|------------|--------------|--------|----------------------------------------------|--------------|----------|

| Name     | Addr (0,Hex) |    | Name        | Addr (0,Hex) | Access | Name       | Addr (0,Hex) | Access | Name                                         | Addr (0,Hex) | Access   |

| PRTODR   | 00           | RW |             | 40           |        |            | 80           |        |                                              | C0           | <b></b>  |

| PRTOIE   | 01           | RW |             | 41           |        |            | 81           |        | l                                            | C1           |          |

| PRT0GS   | 02           | RW |             | 42           |        |            | 82           |        | <b></b>                                      | C2           |          |

| PRT0DM2  | 03           | RW |             | 43           |        |            | 83           |        |                                              | C3           |          |

| PRT1DR   | 04           | RW |             | 44           |        | ASD11CR0   | 84           | RW     | <b></b>                                      | C4           |          |

| PRT1IE   | 05           | RW |             | 45           |        | ASD11CR1   | 85           | RW     | L                                            | C5           |          |

| PRT1GS   | 06           | RW |             | 46           |        | ASD11CR2   | 86           | RW     |                                              | C6           |          |

| PRT1DM2  | 07           | RW |             | 47           |        | ASD11CR3   | 87           | RW     |                                              | C7           |          |

| PRT2DR   | 08           | RW |             | 48           |        |            | 88           |        |                                              | C8           |          |

| PRT2IE   | 09           | RW |             | 49           |        |            | 89           |        |                                              | C9           |          |

| PRT2GS   | 0A           | RW |             | 4A           |        |            | 8A           |        |                                              | CA           |          |

| PRT2DM2  | 0B           | RW |             | 4B           |        |            | 8B           |        |                                              | CB           |          |

| PRT3DR   | 0C           | RW |             | 4C           |        |            | 8C           |        |                                              | CC           |          |

| PRT3IE   | 0D           | RW |             | 4D           |        |            | 8D           |        |                                              | CD           |          |

| PRT3GS   | 0E           | RW |             | 4E           |        |            | 8E           |        |                                              | CE           |          |

| PRT3DM2  | 0F           | RW |             | 4F           |        |            | 8F           |        |                                              | CF           |          |

|          | 10           |    |             | 50           |        |            | 90           |        |                                              | D0           |          |

|          | 11           |    |             | 51           |        |            | 91           |        |                                              | D1           |          |

|          | 12           |    |             | 52           |        |            | 92           |        | 1                                            | D2           | <u> </u> |

|          | 13           |    |             | 53           |        |            | 93           |        | 1                                            | D3           | <u> </u> |

|          | 14           |    |             | 54           |        | ASC21CR0   | 94           | RW     | ł                                            | D4           | <u> </u> |

|          | 15           |    |             | 55           |        | ASC21CR1   | 95           | RW     | 1                                            | D5           | <u> </u> |

|          | 16           |    |             | 56           |        | ASC21CR2   | 96           | RW     | I <sup>2</sup> C_CFG                         | D6           | RW       |

|          | 17           |    |             | 57           |        | ASC21CR3   | 97           | RW     | I <sup>2</sup> C_SCR                         | D7           | #        |

|          | 18           |    | -           | 58           |        | /1002/0110 | 98           |        | I <sup>2</sup> C_DR                          | D8           | RW       |

|          | 19           |    |             | 59           |        |            | 99           |        | I <sup>2</sup> C_MSCR                        | D9           | #        |

|          | 19<br>1A     |    |             | 59<br>5A     |        |            | 99<br>9A     |        | INT_CLR0                                     | D9           | #<br>RW  |

|          | 1A<br>1B     |    |             | 5A<br>5B     |        |            | 9A<br>9B     |        | INT_CLR0                                     | DA           | RW       |

|          |              |    |             |              |        |            |              |        | INI_CLRI                                     |              | RW       |

|          | 1C           |    | -           | 5C           |        |            | 9C           |        |                                              | DC           | DW       |

|          | 1D           |    |             | 5D           |        |            | 9D           |        | INT_CLR3                                     | DD           | RW       |

|          | 1E           |    |             | 5E           |        |            | 9E           |        | INT_MSK3                                     | DE           | RW       |

|          | 1F           |    |             | 5F           | 514    |            | 9F           |        |                                              | DF           |          |

| DBB00DR0 | 20           | #  | AMX_IN      | 60           | RW     |            | A0           |        | INT_MSK0                                     | E0           | RW       |

| DBB00DR1 | 21           | W  |             | 61           |        |            | A1           |        | INT_MSK1                                     | E1           | RW       |

| DBB00DR2 | 22           | RW |             | 62           |        |            | A2           |        | INT_VC                                       | E2           | RC       |

| DBB00CR0 | 23           | #  | ARF_CR      | 63           | RW     |            | A3           |        | RES_WDT                                      | E3           | W        |

| DBB01DR0 | 24           | #  | CMP_CR0     | 64           | #      |            | A4           |        | DEC_DH                                       | E4           | RC       |

| DBB01DR1 | 25           | W  | ASY_CR      | 65           | #      |            | A5           |        | DEC_DL                                       | E5           | RC       |

| DBB01DR2 | 26           | RW | CMP_CR1     | 66           | RW     |            | A6           |        | DEC_CR0                                      | E6           | RW       |

| DBB01CR0 | 27           | #  | SARADC_DL   | 67           | RW     |            | A7           |        | DEC_CR1                                      | E7           | RW       |

| DCB02DR0 | 28           | #  |             | 68           |        |            | A8           |        | MUL0_X                                       | E8           | W        |

| DCB02DR1 | 29           | W  | SARADC_C0   | 69           | #      |            | A9           |        | MUL0_Y                                       | E9           | W        |

| DCB02DR2 | 2A           | RW | SARADC_C1   | 6A           | RW     |            | AA           |        | MUL0_DH                                      | EA           | R        |

| DCB02CR0 | 2B           | #  |             | 6B           |        |            | AB           |        | MUL0_DL                                      | EB           | R        |

| DCB03DR0 | 2C           | #  | TMP_DR0     | 6C           | RW     |            | AC           |        | ACC0_DR1                                     | EC           | RW       |

| DCB03DR1 | 2D           | W  | TMP_DR1     | 6D           | RW     |            | AD           |        | ACC0_DR0                                     | ED           | RW       |

| DCB03DR2 | 2E           | RW | TMP_DR2     | 6E           | RW     |            | AE           |        | ACC0_DR3                                     | EE           | RW       |

| DCB03CR0 | 2F           | #  | TMP_DR3     | 6F           | RW     |            | AF           |        | ACC0_DR2                                     | EF           | RW       |

|          | 30           |    | ACB00CR3    | 70           | RW     | RDIORI     | B0           | RW     | i i                                          | F0           |          |

|          | 31           |    | ACB00CR0    | 71           | RW     | RDI0SYN    | B1           | RW     | 1                                            | F1           | <b></b>  |

|          | 32           |    | ACB00CR1    | 72           | RW     | RDI0IS     | B2           | RW     | 1                                            | F2           |          |

|          | 33           |    | ACB00CR2    | 73           | RW     | RDI0LT0    | B3           | RW     | 1                                            | F3           | <u> </u> |

|          | 34           |    | ACB01CR3    | 74           | RW     | RDI0LT1    | B4           | RW     | 1                                            | F4           | <u> </u> |

|          | 35           |    | ACB01CR0    | 75           | RW     | RDI0RO0    | B5           | RW     | 1                                            | F5           | <u> </u> |

|          | 36           |    | ACB01CR1 *  | 76           | RW     | RDI0RO1    | B6           | RW     | l                                            | F6           | <u> </u> |

|          | 37           |    | ACB01CR2 *  | 77           | RW     |            | B7           |        | CPU_F                                        | F7           | RL       |

|          | 38           |    |             | 78           |        |            | B8           |        | <u>                                     </u> | F8           |          |

|          | 39           |    |             | 79           |        |            | B9           |        | <b> </b>                                     | F9           | <u> </u> |

|          | 39<br>3A     |    |             | 79<br>7A     |        | ł          | BA           |        | <b> </b>                                     | FA           | <u> </u> |

|          | 3B           |    |             | 7B           |        | 1          | BB           |        | <b> </b>                                     | FB           | <u> </u> |

|          | 3D<br>3C     |    |             | 7B<br>7C     |        | ł          | BC           |        | <b> </b>                                     | FD           | <u> </u> |

|          | 3C<br>3D     |    |             | 7C<br>7D     |        |            | BD           |        | <b> </b>                                     | FC           |          |

|          | 3D<br>3E     |    |             | 7D<br>7E     |        |            |              |        |                                              | FD           | #        |

|          | 0E           |    |             | / 🗆          |        |            | BE           | 1 1    | CPU_SCR1                                     |              | #        |

|          | 3F           |    |             | 7F           |        |            | BF           | i      | CPU SCR0                                     | FF           | #        |

# **Electrical Specifications**

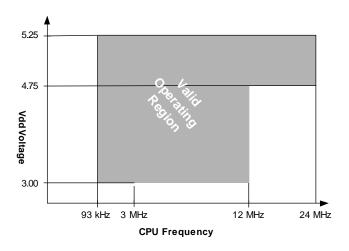

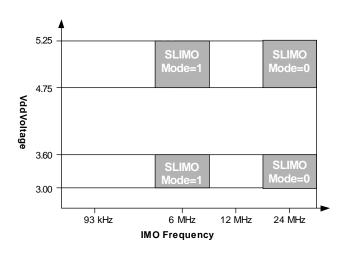

This section presents the DC and AC electrical specifications of the CY8C24633 PSoC device. For the most up to date electrical specifications, confirm that you have the most recent data sheet by going to the web at <a href="http://www.cypress.com/psoc">http://www.cypress.com/psoc</a>.

Specifications are valid for –40 °C  $\leq$   $T_A$   $\leq$  85 °C and  $T_J$   $\leq$  100 °C, except where noted.

Refer to Table 22 for the electrical specifications on the IMO using SLIMO mode.

## Figure 6. Voltage versus CPU Frequency

## Figure 5a. IMO Frequency Trim Options

## **Absolute Maximum Ratings**

## Table 6. Absolute Maximum Ratings

| Symbol                | Description                                                   | Min                     | Тур | Max                     | Units | Notes                                                                                                                                                                                                |

|-----------------------|---------------------------------------------------------------|-------------------------|-----|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Τ <sub>STG</sub>      | Storage temperature                                           | -55                     | 25  | +100                    | °C    | Higher storage temperatures<br>reduce data retention time.<br>Recommended storage<br>temperature is +25 °C ± 25 °C.<br>Extended duration storage<br>temperatures above 65 °C<br>degrade reliability. |

| T <sub>BAKETEMP</sub> | Bake temperature                                              | -                       | 125 | See<br>package<br>label | °C    |                                                                                                                                                                                                      |

| T <sub>BAKETIME</sub> | Bake time                                                     | See<br>package<br>label | -   | 72                      | hours |                                                                                                                                                                                                      |

| T <sub>A</sub>        | Ambient temperature with power applied                        | -40                     | -   | +85                     | °C    |                                                                                                                                                                                                      |

| Vdd                   | Supply voltage on V <sub>dd</sub> Relative to V <sub>ss</sub> | -0.5                    | _   | +6.0                    | V     |                                                                                                                                                                                                      |

| V <sub>IO</sub>       | DC input voltage                                              | V <sub>ss</sub> - 0.5   | -   | V <sub>dd</sub> + 0.5   | V     |                                                                                                                                                                                                      |

| V <sub>IOZ</sub>      | DC voltage applied to Tri-state                               | V <sub>ss</sub> - 0.5   | -   | V <sub>dd</sub> + 0.5   | V     |                                                                                                                                                                                                      |

| I <sub>MIO</sub>      | Maximum current into any port pin                             | -25                     | -   | +50                     | mA    |                                                                                                                                                                                                      |

| ESD                   | Electro static discharge voltage                              | 2000                    | -   | -                       | V     | Human Body Model ESD.                                                                                                                                                                                |

| LU                    | Latch up current                                              | -                       | -   | 200                     | mA    |                                                                                                                                                                                                      |

# **Operating Temperature**

# Table 7. Operating Temperature

| Symbol         | Description          | Min | Тур | Мах  | Units | Notes                                                                                                                                                                                                           |

|----------------|----------------------|-----|-----|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub> | Ambient temperature  | -40 | 1   | +85  | °C    |                                                                                                                                                                                                                 |

| Tj             | Junction temperature | -40 | _   | +100 | ℃     | The temperature rise from<br>ambient to junction is package<br>specific. See Thermal Imped-<br>ances by Package on page 41.<br>The user must limit the power<br>consumption to comply with this<br>requirement. |

## Table 11. 3.3 V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                                                                           | Min                                                | Тур                                    | Max                                    | Units                      | Notes                                                                                                                                                                                                     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value)<br>Power = low, opamp bias = high<br>Power = medium, opamp bias = high<br>Power = high, opamp bias = high                                                                                                                       | _<br>_<br>_                                        | 1.65<br>1.32<br>-                      | 10<br>8<br>-                           | mV<br>mV<br>mV             | Power = high, opamp bias = high setting is not allowed for $3.3 \text{ V} \text{ V}_{\text{DD}}$ operation.                                                                                               |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                                                    | -                                                  | 7.0                                    | 35.0                                   | µV/°C                      |                                                                                                                                                                                                           |

| I <sub>EBOA</sub>    | Input leakage current (port 0 analog pins)                                                                                                                                                                                                                            | -                                                  | 20                                     | Ι                                      | pА                         | Gross tested to 1 µA                                                                                                                                                                                      |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                                                | -                                                  | 4.5                                    | 9.5                                    | pF                         | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                                                |

| V <sub>CMOA</sub>    | Common mode voltage range                                                                                                                                                                                                                                             | 0.2                                                | -                                      | V <sub>DD</sub> – 0.2                  | V                          | The common-mode input voltage<br>range is measured through an<br>analog output buffer. The<br>specification includes the<br>limitations imposed by the<br>characteristics of the analog<br>output buffer. |

| G <sub>OLOA</sub>    | Open loop gain<br>power = low, ppamp, Opamp bias = low<br>Power = medium, opamp bias = low<br>Power = high, opamp bias = low                                                                                                                                          | 60<br>60<br>80                                     |                                        |                                        | dB<br>dB<br>dB             | Specification is applicable at low<br>Opamp bias. For high opamp bias<br>mode (except high power, high<br>opamp bias), minimum is 60 dB.                                                                  |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals)<br>Power = low, opamp bias = low<br>Power = medium, opamp bias = low<br>Power = high, opamp bias = low                                                                                                                   | $V_{DD} - 0.2$<br>$V_{DD} - 0.2$<br>$V_{DD} - 0.2$ |                                        |                                        | V<br>V<br>V                | Power = high, opamp bias = high setting is not allowed for $3.3 \text{ V} \text{ V}_{\text{DD}}$ operation.                                                                                               |

| V <sub>OLOWOA</sub>  | Low output voltage swing (internal signals)<br>Power = low, opamp bias = low<br>Power = medium, opamp bias = low<br>Power = high, opamp bias = low                                                                                                                    | _<br>_<br>_                                        |                                        | 0.2<br>0.2<br>0.2                      | V<br>V<br>V                | Power = high, opamp bias = high setting is not allowed for $3.3 \text{ V} \text{ V}_{\text{DD}}$ operation.                                                                                               |

| I <sub>SOA</sub>     | Supply current (including associated AGND<br>buffer)<br>Power = low, opamp bias = low<br>Power = low, opamp bias = high<br>Power = medium, opamp bias = low<br>Power = medium, opamp bias = high<br>Power = high, opamp bias = low<br>Power = high, opamp bias = high | -<br>-<br>-<br>-<br>-                              | 150<br>300<br>600<br>1200<br>2400<br>- | 200<br>400<br>800<br>1600<br>3200<br>- | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | Power = high, opamp bias = high setting is not allowed for $3.3 \text{ V} \text{ V}_{\text{DD}}$ operation.                                                                                               |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                                        | 64                                                 | 80                                     | -                                      | dB                         | $V_{SS} \le V_{IN} \le (V_{DD} - 2.25) \text{ or } \\ (V_{DD} - 1.25 \text{ V}) \le V_{IN} \le V_{DD}$                                                                                                    |

### DC Low Power Comparator Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

| Symbol              | Description                                        | Min | Тур | Max                 | Units | Notes |

|---------------------|----------------------------------------------------|-----|-----|---------------------|-------|-------|

| V <sub>REFLPC</sub> | Low power comparator (LPC) reference voltage range | 0.2 | -   | V <sub>dd</sub> - 1 | V     |       |

| I <sub>SLPC</sub>   | LPC supply current                                 | -   | 10  | 40                  | μA    |       |

| VOSLPC              | LPC voltage offset                                 | -   | 2.5 | 30                  | mV    |       |

## DC Analog Reference Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \degree C \le T_A \le 85 \degree C$ , or 3.0 V to 3.6 V and  $-40 \degree C \le T_A \le 85 \degree C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

The guaranteed specifications are measured through the analog continuous time PSoC blocks. The power levels for AGND refer to the power of the analog continuous Time PSoC block. The power levels for RefHi and RefLo refer to the analog reference control register. The limits stated for AGND include the offset error of the AGND buffer local to the analog continuous time PSoC block. reference control power is high.

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                                | Min                        | Тур                        | Мах                        | Units |

|------------------------------|----------------------------------------|--------------------|-----------|------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b000                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.136 | V <sub>DD</sub> /2 + 1.288 | V <sub>DD</sub> /2 + 1.409 | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2-0.138   | $V_{DD}/2 + 0.003$         | $V_{DD}/2 + 0.132$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2-1.417   | V <sub>DD</sub> /2 - 1.289 | V <sub>DD</sub> /2 - 1.154 | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.202 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.358 | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.055$         | V <sub>DD</sub> /2 + 0.001 | $V_{DD}/2 + 0.055$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2-1.369   | V <sub>DD</sub> /2 - 1.295 | V <sub>DD</sub> /2 – 1.218 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.211 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.357 | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.055$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.052$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2-1.368   | V <sub>DD</sub> /2 - 1.298 | V <sub>DD</sub> /2 – 1.224 | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.215 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.353 | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | $V_{DD}/2 - 0.040$         | $V_{DD}/2 - 0.001$         | $V_{DD}/2 + 0.033$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2-1.368   | V <sub>DD</sub> /2 - 1.299 | V <sub>DD</sub> /2 – 1.225 | V     |

| 0b001                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6]<br>- 0.076   | P2[4]+P2[6]-<br>0.021      | P2[4]+P2[6]+<br>0.041      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6]<br>– 0.025   | P2[4]-P2[6]+<br>0.011      | P2[4]-P2[6]+<br>0.085      | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6]<br>- 0.069   | P2[4]+P2[6]-<br>0.014      | P2[4]+P2[6]+<br>0.043      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6]<br>– 0.029   | P2[4]-P2[6]+<br>0.005      | P2[4]-P2[6]+<br>0.052      | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6]<br>- 0.072   | P2[4]+P2[6]-<br>0.011      | P2[4]+P2[6]+<br>0.048      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6]<br>– 0.031   | P2[4]-P2[6]+<br>0.002      | P2[4]-P2[6]+<br>0.057      | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6]<br>- 0.070   | P2[4]+P2[6]-<br>0.009      | P2[4]+P2[6]+<br>0.047      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6]<br>– 0.033   | P2[4]-P2[6]+<br>0.001      | P2[4]-P2[6]+<br>0.039      | V     |

Table 15.

5-V DC Analog Reference Specifications

## Table 15. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                     | Min             | Тур                     | Мах                     | Units |

|------------------------------|----------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|-------|

| 0b101                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.228   | P2[4] + 1.284           | P2[4] + 1.332           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.358   | P2[4] – 1.293           | P2[4] – 1.226           | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.236   | P2[4] + 1.289           | P2[4] + 1.332           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.357   | P2[4] – 1.297           | P2[4] – 1.229           | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.237   | P2[4] + 1.291           | P2[4] + 1.337           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.356   | P2[4] – 1.299           | P2[4] – 1.232           | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.237   | P2[4] + 1.292           | P2[4] + 1.337           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.357   | P2[4] – 1.300           | P2[4] – 1.233           | V     |

| 0b110                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.512           | 2.594                   | 2.654                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.250           | 1.303                   | 1.346                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.011 | V <sub>SS</sub> + 0.027 | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.515           | 2.592                   | 2.654                   | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.253           | 1.301                   | 1.340                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.02  | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.518           | 2.593                   | 2.651                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.254           | 1.301                   | 1.338                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.517           | 2.594                   | 2.650                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.255           | 1.300                   | 1.337                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.015 | V     |

| 0b111                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.011           | 4.143                   | 4.203                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.020           | 2.075                   | 2.118                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.011 | V <sub>SS</sub> + 0.026 | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.022           | 4.138                   | 4.203                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.023           | 2.075                   | 2.114                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | $V_{SS} + 0.006$        | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.026           | 4.141                   | 4.207                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.024           | 2.075                   | 2.114                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.015 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.030           | 4.143                   | 4.206                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.024           | 2.076                   | 2.112                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.013 | V     |

## Table 16. 3.3-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                | Symbol             | Reference | Description                                                          | Min             | Тур                     | Max                     | Units |

|------------------------------|--------------------------------------------|--------------------|-----------|----------------------------------------------------------------------|-----------------|-------------------------|-------------------------|-------|

| 0b100                        | All power settings<br>Not allowed at 3.3 V | -                  | _         | -                                                                    | -               | -                       | _                       | -     |

| 0b101                        | RefPower = high<br>opamp bias = high       |                    | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2)                      | P2[4] + 1.211   | P2[4] + 1.285           | P2[4] + 1.348           | V     |

|                              | -                                          | V <sub>AGND</sub>  | AGND      | P2[4]                                                                | P2[4]           | P2[4]                   | P2[4]                   | -     |

| -                            |                                            | V <sub>REFLO</sub> | Ref Low   | $\begin{array}{l} P2[4]-Bandgap\\ (P2[4]=V_{DD}/2) \end{array}$      | P2[4] – 1.354   | P2[4] – 1.290           | P2[4] – 1.197           | V     |

|                              | RefPower = high<br>opamp bias = low        | V <sub>REFHI</sub> | Ref High  | $\begin{array}{l} P2[4] + Bandgap \\ (P2[4] = V_{DD}/2) \end{array}$ | P2[4] + 1.209   | P2[4] + 1.289           | P2[4] + 1.353           | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                                | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2)                      | P2[4] – 1.352   | P2[4] – 1.294           | P2[4] – 1.222           | V     |

|                              | RefPower = medium<br>opamp bias = high     | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2)                      | P2[4] + 1.218   | P2[4] + 1.291           | P2[4] + 1.351           | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                                | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2)                      | P2[4] – 1.351   | P2[4] – 1.296           | P2[4] – 1.224           | V     |

|                              | RefPower = medium<br>opamp bias = low      | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2)                      | P2[4] + 1.215   | P2[4] + 1.292           | P2[4] + 1.354           | V     |

|                              |                                            | V <sub>AGND</sub>  | AGND      | P2[4]                                                                | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2)                      | P2[4] – 1.352   | P2[4] – 1.297           | P2[4] – 1.227           | V     |

| 0b110                        | RefPower = high                            | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                                          | 2.460           | 2.594                   | 2.695                   | V     |

|                              | opamp bias = high                          | V <sub>AGND</sub>  | AGND      | Bandgap                                                              | 1.257           | 1.302                   | 1.335                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                                      | V <sub>SS</sub> | V <sub>SS</sub> + 0.01  | V <sub>SS</sub> + 0.029 | V     |

|                              | RefPower = high<br>opamp bias = low        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                                          | 2.462           | 2.592                   | 2.692                   | V     |

|                              | opattip bias = 10w                         | V <sub>AGND</sub>  | AGND      | Bandgap                                                              | 1.256           | 1.301                   | 1.332                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                                      | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                          | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                                          | 2.473           | 2.593                   | 2.682                   | V     |

|                              | opamp bias = high                          | V <sub>AGND</sub>  | AGND      | Bandgap                                                              | 1.257           | 1.301                   | 1.330                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                                      | V <sub>SS</sub> | $V_{SS} + 0.003$        | V <sub>SS</sub> + 0.014 | V     |

|                              | RefPower = medium                          | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                                          | 2.470           | 2.594                   | 2.685                   | V     |

|                              | opamp bias = low                           | V <sub>AGND</sub>  | AGND      | Bandgap                                                              | 1.256           | 1.300                   | 1.332                   | V     |

|                              |                                            | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                                      | V <sub>SS</sub> | V <sub>SS</sub> + 0.002 | V <sub>SS</sub> + 0.012 | V     |

| 0b111                        | All power settings<br>Not allowed at 3.3 V | _                  | _         | -                                                                    | -               | _                       | _                       | -     |

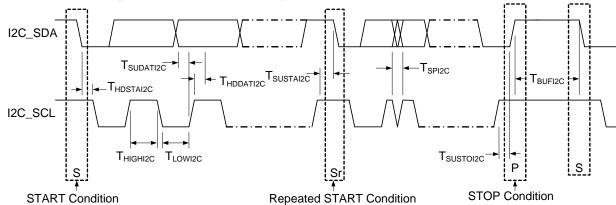

## DC I<sup>2</sup>C Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

## Table 20. DC I<sup>2</sup>C Specifications<sup>[11]</sup>

| Symbol             | Description      | Min                 | Тур | Max                  | Units | Notes                                                |

|--------------------|------------------|---------------------|-----|----------------------|-------|------------------------------------------------------|

| V <sub>ILI2C</sub> | Input low level  | -                   | 1   | $0.3 \times V_{DD}$  | V     | $3.0~V \leq V_{DD} \leq 3.6~V$                       |

|                    |                  | -                   | -   | $0.25 \times V_{DD}$ | V     | $4.75~V \leq V_{DD} \leq 5.25~V$                     |

| V <sub>IHI2C</sub> | Input high level | $0.7 \times V_{DD}$ | 1   | -                    | V     | $3.0~\text{V} \leq \text{V}_{DD} \leq 5.25~\text{V}$ |

#### SAR8 ADC DC Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 21. SAR8 ADC DC Specifications

| Symbol               | Description                                                                | Min  | Тур | Max  | Units | Notes                                                                                                                                                                                             |

|----------------------|----------------------------------------------------------------------------|------|-----|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>ADCVREF</sub> | Reference voltage at pin P3[0] when<br>configured as ADC reference voltage | 3.0  | _   | 5.25 | V     | The voltage level at P3[0] (when<br>configured as ADC reference voltage)<br>should always be maintained to be less<br>than chip supply voltage level on $V_{dd}$<br>pin. $V_{ADCVREF} < V_{dd}$ . |

| IADCVREF             | Current when P3[0] is configured as ADC $V_{REF}$                          | 3    | -   | -    | mA    |                                                                                                                                                                                                   |

| INL                  | R-2R integral non-linearity <sup>[12]</sup>                                | -1.2 | -   | +1.2 | LSB   | The maximum LSB is over a sub-range not exceeding 1/16 of the full-scale range.                                                                                                                   |

| DNL                  | R-2R differential non-linearity <sup>[13]</sup>                            | -1   | -   | +1   | LSB   | Output is monatonic.                                                                                                                                                                              |

Notes

11. All GPIOs meet the DC GPIO V<sub>IL</sub> and V<sub>IH</sub> specifications found in the DC GPIO Specifications sections. The  $I^2$ C GPIO pins also meet the above specs. 12. At the 7F and 80 points, the maximum INL is 1.5 LSB. 13. For the 7F to 80 transition, the DNL specification is waived.

## **AC Electrical Characteristics**

## AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 22. 5V and 3.3V AC Chip-Level Specifications

| Symbol                               | Description                                             | Min   | Тур    | Max                        | Units | Notes                                                                                                                                                                                                                                                                                             |

|--------------------------------------|---------------------------------------------------------|-------|--------|----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO24</sub>                   | Internal main oscillator frequency for 24 MHz           | 22.8  | 24     | 25.2 <sup>[14,15,16]</sup> | MHz   | Trimmed for 5 V or 3.3 V operation<br>using factory trim values. See Figure<br>5b on page 15. SLIMO mode = 0.                                                                                                                                                                                     |

| F <sub>IMO6</sub>                    | Internal main oscillator frequency for 6 MHz            | 5.5   | 6      | 6.5 <sup>[14,15,16]</sup>  | MHz   | Trimmed for 5 V or 3.3 V operation<br>using factory trim values. See Figure<br>5b on page 15. SLIMO mode = 1.                                                                                                                                                                                     |

| F <sub>CPU1</sub>                    | CPU frequency (5 V nominal)                             | 0.093 | 24     | 24.6 <sup>[14,15]</sup>    | MHz   | SLIMO mode = 0.                                                                                                                                                                                                                                                                                   |

| F <sub>CPU2</sub>                    | CPU frequency (3.3 V nominal)                           | 0.093 | 12     | 12.3 <sup>[15,16]</sup>    | MHz   | SLIMO mode = 0.                                                                                                                                                                                                                                                                                   |

| F <sub>48M</sub>                     | digital psoc block frequency                            | 0     | 48     | 49.2 <sup>[14,15,17]</sup> | MHz   | Refer to the Table 27 on page 36.                                                                                                                                                                                                                                                                 |

| F <sub>24M</sub>                     | Digital PSoC block frequency                            | 0     | 24     | 24.6 <sup>[15,17]</sup>    | MHz   |                                                                                                                                                                                                                                                                                                   |

| F <sub>32K1</sub>                    | Internal low speed oscillator frequency                 | 15    | 32     | 75                         | kHz   |                                                                                                                                                                                                                                                                                                   |

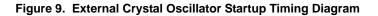

| F <sub>32K2</sub>                    | External crystal oscillator                             | -     | 32.768 | -                          | kHz   | Accuracy is capacitor and crystal dependent. 50% duty cycle.                                                                                                                                                                                                                                      |

| F <sub>32K_U</sub>                   | Internal low speed oscillator untrimmed<br>frequency    | 5     | -      | 100                        | kHz   |                                                                                                                                                                                                                                                                                                   |

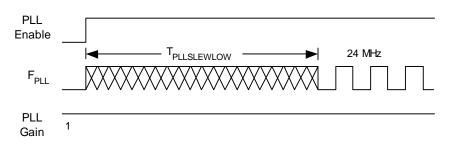

| F <sub>PLL</sub>                     | PLL frequency                                           | -     | 23.986 | -                          | MHz   | Is a multiple (x732) of crystal frequency.                                                                                                                                                                                                                                                        |

| DC <sub>ILO</sub>                    | Internal low speed oscillator duty cycle                | 20    | 50     | 80                         | %     |                                                                                                                                                                                                                                                                                                   |

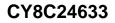

| T <sub>PLLSLEW</sub>                 | PLL Lock time                                           | 0.5   | -      | 10                         | ms    |                                                                                                                                                                                                                                                                                                   |

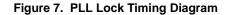

| T <sub>PLLSLEWSLOW</sub>             | PLL Lock time for low gain setting                      | 0.5   | -      | 50                         | ms    |                                                                                                                                                                                                                                                                                                   |

| T <sub>OS</sub>                      | External crystal oscillator startup to 1%               | -     | 1700   | 2620                       | ms    |                                                                                                                                                                                                                                                                                                   |

| T <sub>osacc</sub>                   | External crystal oscillator startup to 100 ppm          | -     | 2800   | 3800                       | ms    | The crystal oscillator frequency is within 100 ppm of its final value by the end of the T <sub>osacc</sub> period. Correct operation assumes a properly loaded 1 uW maximum drive level 32.768 kHz crystal. 3.0 V $\leq$ V <sub>dd</sub> $\leq$ 5.5 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C. |

| T <sub>XRST</sub>                    | External reset pulse width                              | 10    | -      | -                          | μS    |                                                                                                                                                                                                                                                                                                   |

| DC24M                                | 24 MHz duty cycle                                       | 40    | 50     | 60                         | %     |                                                                                                                                                                                                                                                                                                   |

| Step24M                              | 24 MHz trim step size                                   | -     | 50     | -                          | kHz   |                                                                                                                                                                                                                                                                                                   |

| Fout48M                              | 48 MHz output frequency                                 | 46.8  | 48.0   | 49.2 <sup>[14,16]</sup>    | MHz   | Trimmed. Utilizing factory trim values.                                                                                                                                                                                                                                                           |