Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18326-e-st |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                            |  |

|-------|----------------------------------------------------------------------------|--|

| 2.0   | Guidelines for Getting Started With PIC16(L)F183XX Microcontrollers        |  |

| 3.0   | Enhanced Mid-Range CPU                                                     |  |

| 4.0   | Memory Organization                                                        |  |

| 5.0   | Device Configuration                                                       |  |

| 6.0   | Resets                                                                     |  |

| 7.0   | Oscillator Module                                                          |  |

| 8.0   | Interrupts                                                                 |  |

| 9.0   | Power-Saving Operation Modes                                               |  |

| 10.0  | Watchdog Timer (WDT)                                                       |  |

| 11.0  | Nonvolatile Memory (NVM) Control                                           |  |

|       | I/O Ports                                                                  |  |

| 13.0  | Peripheral Pin Select (PPS) Module                                         |  |

|       | Peripheral Module Disable                                                  |  |

| 15.0  | Interrupt-on-Change                                                        |  |

| 16.0  | Fixed Voltage Reference (FVR)                                              |  |

| 17.0  | Temperature Indicator Module                                               |  |

|       | Comparator Module                                                          |  |

| 19.0  | Pulse-Width Modulation (PWM)                                               |  |

|       | Complementary Waveform Generator (CWG) Module                              |  |

|       | Configurable Logic Cell (CLC)                                              |  |

|       | Analog-to-Digital Converter (ADC) Module                                   |  |

|       | Numerically Controlled Oscillator (NCO1) Module                            |  |

|       | 5-bit Digital-to-Analog Converter (DAC1) Module                            |  |

|       | Data Signal Modulator (DSM) Module                                         |  |

|       | Timer0 Module                                                              |  |

|       | Timer1/3/5 Module with Gate Control                                        |  |

|       | Timer 2/4/6 Module                                                         |  |

|       | Capture/Compare/PWM Modules                                                |  |

|       | Master Synchronous Serial Port (MSSPx) Module                              |  |

|       | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART1) |  |

|       | Reference Clock Output Module                                              |  |

|       | In-Circuit Serial Programming™ (ICSP™)                                     |  |

|       | Instruction Set Summary                                                    |  |

|       | Electrical Specifications                                                  |  |

|       | DC and AC Characteristics Graphs and Charts                                |  |

|       | Development Support                                                        |  |

|       | Packaging Information                                                      |  |

|       | ndix A: Data Sheet Revision History                                        |  |

|       | Nicrochip Website                                                          |  |

|       | omer Change Notification Service                                           |  |

|       | omer Support                                                               |  |

| Produ | uct Identification System                                                  |  |

## TABLE 1-2: PIC16(L)F18326 PINOUT DESCRIPTION

| Name                                                                                                             | Function | Input<br>Type | Output Type | Description                                          |

|------------------------------------------------------------------------------------------------------------------|----------|---------------|-------------|------------------------------------------------------|

| RA0/ANA0/C1IN0+/DAC1OUT/                                                                                         | RA0      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| SS2 <sup>(1)</sup> / ICDDAT/ICSPDAT                                                                              | ANA0     | AN            | _           | ADC Channel A0 input.                                |

|                                                                                                                  | C1IN0+   | AN            | _           | Comparator C1 positive input.                        |

|                                                                                                                  | DAC1OUT  | _             | AN          | Digital-to-Analog Converter output.                  |

|                                                                                                                  | SS2      | TTL/ST        | —           | Slave Select 2 input.                                |

|                                                                                                                  | ICDDAT   | TTL/ST        | CMOS        | In-Circuit Debug Data I/O.                           |

|                                                                                                                  | ICSPDAT  | TTL/ST        | CMOS        | ICSP™ Data I/O.                                      |

| RA1/ANA1/VREF+/C1IN0-/                                                                                           | RA1      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| C2IN0-/DAC1REF+/ ICDCLK/                                                                                         | ANA1     | AN            | —           | ADC Channel A1 input.                                |

| ICSPCLK                                                                                                          | VREF+    | AN            | —           | ADC positive voltage reference input.                |

|                                                                                                                  | C1IN0-   | AN            | _           | Comparator C1 negative input.                        |

|                                                                                                                  | C2IN0-   | AN            | _           | Comparator C2 negative input.                        |

|                                                                                                                  | DAC1REF+ | _             | AN          | Digital-to-Analog Converter positive reference input |

|                                                                                                                  | ICDCLK   | TTL/ST        | CMOS        | In-Circuit Debug Clock I/O.                          |

|                                                                                                                  | ICSPCLK  | TTL/ST        | CMOS        | ICSP Clock I/O.                                      |

| RA2/ANA2/VREF-/ DAC1REF-/                                                                                        | RA2      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| T0CKI <sup>(1)</sup> / CCP3 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /<br>CWG2IN <sup>(1)</sup> /INT <sup>(1)</sup> | ANA2     | AN            | _           | ADC Channel A2 input.                                |

| CWG2IN <sup>(1</sup> /INI <sup>(1)</sup>                                                                         | VREF-    | AN            | —           | ADC negative voltage reference input.                |

|                                                                                                                  | DAC1REF- | —             | AN          | Digital-to-Analog Converter negative reference inpu  |

|                                                                                                                  | TOCKI    | TTL/ST        | _           | TMR0 Clock input.                                    |

|                                                                                                                  | CCP3     | TTL/ST        | CMOS        | Capture/Compare/PWM 3 input.                         |

|                                                                                                                  | CWG1IN   | TTL/ST        | —           | Complementary Waveform Generator 1 input.            |

|                                                                                                                  | CWG2IN   | TTL/ST        | —           | Complementary Waveform Generator 2 input.            |

|                                                                                                                  | INT      | TTL/ST        | —           | External interrupt input.                            |

| RA3/MCLR/Vpp                                                                                                     | RA3      | TTL/ST        | CMOS        | General purpose I/O.                                 |

|                                                                                                                  | MCLR     | TTL/ST        | —           | Master Clear with internal pull-up.                  |

|                                                                                                                  | Vpp      | HV            | _           | Programming voltage.                                 |

| RA4/ANA4/T1G <sup>(1)</sup> / SOSCO/                                                                             | RA4      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| CLKOUT/OSC2                                                                                                      | ANA4     | AN            | _           | ADC Channel A4 input.                                |

|                                                                                                                  | T1G      | ST            | _           | TMR1 gate input.                                     |

|                                                                                                                  | SOSCO    | _             | XTAL        | Secondary Oscillator connection.                     |

|                                                                                                                  | CLKOUT   | —             | CMOS        | Fosc/4 output.                                       |

|                                                                                                                  | OSC2     | _             | XTAL        | Crystal/Resonator (LP, XT, HS modes).                |

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD

= Open-Drain

TTL = TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL

= Crystal levels

I

I

I

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-1.

All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| TABLE   | 4-4: SPE | CIAL FU                          | NCTION RE |       | UMMARY B | ANKS 0-31 ( | CONTINUE | <b>)</b> |       |       |

|---------|----------|----------------------------------|-----------|-------|----------|-------------|----------|----------|-------|-------|

| Address | Name     | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7     | Bit 6 | Bit 5    | Bit 4       | Bit 3    | Bit 2    | Bit 1 | Bit 0 |

| Bank 1          | 0-11    |   |        |                                  |             |               |                  |         |           |           |      |      |

|-----------------|---------|---|--------|----------------------------------|-------------|---------------|------------------|---------|-----------|-----------|------|------|

|                 |         |   |        |                                  | CPU CORE RE | EGISTERS; see | Table 4-2 for sp | ecifics |           |           |      |      |

| 50Ch to<br>51Fh | -       | - |        |                                  |             | Unimple       | emented          |         |           |           | -    | _    |

| 58Ch to<br>59Fh | _       | — |        |                                  |             | Unimple       | emented          |         |           |           | -    | _    |

| Bank 1          | 2       |   |        |                                  |             |               |                  |         |           |           |      |      |

| 60Ch            | —       | — |        |                                  |             | Unimple       | emented          |         |           |           | —    | _    |

| 60Dh            | —       |   |        |                                  |             | Unimple       | emented          |         |           |           | _    |      |

| 60Eh            | —       | — |        |                                  |             | Unimple       | emented          |         |           |           | —    | _    |

| 60Fh            | —       |   |        |                                  |             | Unimple       | emented          |         |           |           | _    |      |

| 610h            | —       |   |        |                                  |             | Unimple       | emented          |         |           |           | _    |      |

| 611h            | —       | — |        |                                  |             | Unimple       | emented          |         |           |           | —    | _    |

| 612h            | —       | — |        |                                  |             | Unimple       | emented          |         |           |           | —    | _    |

| 613h            | —       | — |        | Unimplemented                    |             |               |                  |         |           | —         | —    |      |

| 614h            | —       | — |        | Unimplemented                    |             |               |                  |         |           | —         | _    |      |

| 615h            | —       | — |        | Unimplemented                    |             |               |                  |         |           | —         | _    |      |

| 616h            | —       | — |        | Unimplemented                    |             |               |                  |         |           | —         | _    |      |

| 617h            | PWM5DCL |   | PWM5DC | PWM5DC<1:0>                      |             |               |                  |         | xx        | uu        |      |      |

| 618h            | PWM5DCH |   |        | PWM5DC<9:2> xxxx xxxx uuuu u     |             |               |                  |         |           | uuuu uuuu |      |      |

| 619h            | PWM5CON |   | PWM5EN | PWM5EN — PWM5OUT PWM5POL — — — — |             |               |                  |         |           | 0-00      | 0-00 |      |

| 61Ah            | PWM6DCL |   | PWM6DC | PWM6DC<1:0>                      |             |               |                  |         | xx        | uu        |      |      |

| 61Bh            | PWM6DCH |   |        | PWM6DC<9:2>                      |             |               |                  |         | XXXX XXXX | uuuu uuuu |      |      |

| 61Ch            | PWM6CON |   | PWM6EN | _                                | PWM6OUT     | PWM6POL       | —                | —       | —         | —         | 0-00 | 0-00 |

| 61Dh to<br>61Eh | _       | - |        |                                  |             | Unimple       | emented          |         |           |           | -    | _    |

| 61Fh            | PWMTMRS |   | _      | _                                | _           | _             | P6TSE            | EL<1:0> | P5TSI     | EL<1:0>   | 0101 | 0101 |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Only on PIC16F18326/18346.

> 2: Register accessible from both User and ICD Debugger.

Value on

all other Resets

Value on: POR, BOR

| Address | Name   | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7 | Bit 6             | Bit 5         | Bit 4         | Bit 3             | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------------------|-------|-------------------|---------------|---------------|-------------------|-------------|-------|-------|-----------------------|---------------------------------|

| Bank 2  | 9      |                                  |       |                   |               |               |                   |             |       |       |                       |                                 |

|         |        |                                  |       |                   | CPU CORE RI   | EGISTERS; see | Table 4-2 for spe | ecifics     |       |       |                       |                                 |

| E8Dh    | —      | —                                |       |                   |               | Unimple       | mented            |             |       |       | _                     | -                               |

| E8Eh    | —      | —                                |       |                   |               | Unimple       | mented            |             |       |       | —                     | —                               |

| E8Fh    | —      |                                  |       |                   |               | Unimple       | mented            |             |       |       | _                     |                                 |

| E90h    | RA0PPS |                                  | _     |                   |               |               |                   | RA0PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E91h    | RA1PPS |                                  | —     | _                 | —             | RA1PPS<4:0>   |                   |             |       |       | 0 0000                | u uuuu                          |

| E92h    | RA2PPS |                                  | _     | _                 | —             |               |                   | RA2PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E93h    | —      | —                                |       |                   | Unimplemented |               |                   |             |       |       | -                     | —                               |

| E94h    | RA4PPS |                                  | —     | —                 | —             |               |                   | RA4PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E95h    | RA5PPS |                                  | —     | —                 | —             |               |                   | RA5PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E96h    | —      |                                  |       |                   |               | Unimple       | mented            |             |       |       | _                     |                                 |

| E97h    | _      |                                  |       |                   |               | Unimple       | mented            |             |       |       |                       |                                 |

| E98h    | —      |                                  |       |                   |               | Unimple       | mented            |             |       |       |                       |                                 |

| E99h    | _      |                                  |       |                   |               | Unimple       | mented            |             |       |       |                       |                                 |

| E9Ah    | —      |                                  |       | Unimplemented —   |               |               |                   |             |       |       |                       |                                 |

| E9Bh    | —      | _                                |       | Unimplemented — — |               |               |                   |             |       |       | —                     |                                 |

| E9Ch    | RB4PPS | X —                              |       | Unimplemented     |               |               |                   |             |       |       |                       |                                 |

|         |        | — X                              | _     | —                 |               |               |                   |             |       |       | 0 0000                | u uuuu                          |

| E9Dh    | RB5PPS | X —                              |       | Unimplemented — — |               |               |                   |             |       | —     |                       |                                 |

|         |        | — X                              | _     | _                 | _             |               |                   | RB5PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E9Eh    | RB6PPS | X —                              |       |                   |               | Unimple       | mented            |             |       |       | -                     | -                               |

|         |        | — X                              | _     | _                 | _             |               |                   | RB6PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E9Fh    | RB7PPS | X —                              |       |                   |               | Unimple       | mented            |             |       |       | -                     | -                               |

|         |        | — X                              | —     | —                 | —             |               |                   | RB7PPS<4:0> |       |       | 0 0000                | u uuuu                          |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Only on PIC16F18326/18346.

2: Register accessible from both User and ICD Debugger.

## 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep, but device wake-up will be delayed until the BOR can determine that VDD is higher than the BOR threshold. The device wake-up will be delayed until the BOR is ready.

## 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device wake from Sleep is not delayed by the BOR Ready condition or the VDD level only when the SBOREN bit is cleared in software and the device is starting up from a non POR/BOR Reset event.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register. BOR Protection is unchanged by Sleep

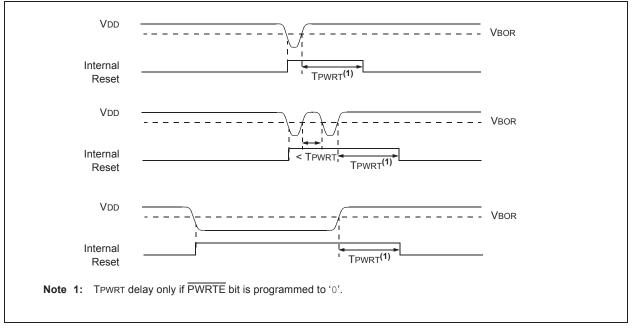

#### FIGURE 6-2: BROWN-OUT SITUATIONS

#### 6.2.4 BOR ALWAYS OFF

When the BOREN bits of Configuration Word 2 are programmed to '00', the BOR is always disable. In the configuration, setting the SWBOREN bit will have no affect on BOR operation.

| R/W-0/0          | R/W-0/0                             | R/W-0/0                                                       | R/W-0/0          | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0      |

|------------------|-------------------------------------|---------------------------------------------------------------|------------------|--------------|------------------|----------|--------------|

| OSFIE            | CSWIE                               | TMR3GIE                                                       | TMR3IE           | CLC4IE       | CLC3IE           | CLC2IE   | CLC1IE       |

| bit 7            | ·                                   |                                                               |                  | •            |                  |          | bit (        |

| Legend:          |                                     |                                                               |                  |              |                  |          |              |

| R = Readable     | bit                                 | W = Writable                                                  | bit              | U = Unimpler | mented bit, read | l as '0' |              |

| u = Bit is unch  |                                     | x = Bit is unkr                                               | nown             | •            | at POR and BO    |          | other Resets |

| '1' = Bit is set | 0                                   | '0' = Bit is clea                                             | ared             |              |                  |          |              |

| bit 7            | 1 = Enables                         | ator Fail Interru<br>the Oscillator F<br>the Oscillator I     | ail interrupt    |              |                  |          |              |

| bit 6            | 1 = The clock                       | k Switch Comp<br>switch module<br>switch module               | e interrupt is e | enabled      |                  |          |              |

| bit 5            | 1 = Timer3 Ga                       | mer3 Gate Inte<br>ate interrupt is<br>ate interrupt is        | enabled          | oit          |                  |          |              |

| bit 4            | 1 = TMR3 ove                        | R3 Overflow Interrupt<br>erflow interrupt<br>erflow interrupt | is enabled       |              |                  |          |              |

| bit 3            | 1 = CLC4 inte                       | 4 Interrupt Fla<br>errupt is enable<br>errupt is not ena      | d                |              |                  |          |              |

| bit 2            | CLC3IE: CLC<br>1 = CLC3 inte        | 3 Interrupt Fla<br>errupt is enable<br>errupt is not ena      | g bit<br>d       |              |                  |          |              |

| bit 1            | 1 = CLC2 inte                       | 2 Interrupt Ena<br>errupt enabled<br>errupt disabled          | able bit         |              |                  |          |              |

| bit 0            | <b>CLC1IE:</b> CLC<br>1 = CLC1 inte | 1 Interrupt Ena                                               | able bit         |              |                  |          |              |

#### REGISTER 8-5: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

# 12.7 Register Definitions: PORTC

'1' = Bit is set

#### **REGISTER 12-17: PORTC: PORTC REGISTER**

| R/W-x/u                           | R/W-x/u            | R/W-x/u         | R/W-x/u | R/W-x/u                            | R/W-x/u       | R/W-x/u          | R/W-x/u     |  |  |

|-----------------------------------|--------------------|-----------------|---------|------------------------------------|---------------|------------------|-------------|--|--|

| RC7 <sup>(1)</sup>                | RC6 <sup>(1)</sup> | RC5             | RC4     | RC3                                | RC2           | RC1              | RC0         |  |  |

| bit 7                             |                    |                 |         |                                    |               |                  | bit 0       |  |  |

|                                   |                    |                 |         |                                    |               |                  |             |  |  |

| Legend:                           |                    |                 |         |                                    |               |                  |             |  |  |

| R = Readable bit W = Writable bit |                    |                 |         | U = Unimplemented bit, read as '0' |               |                  |             |  |  |

| u = Bit is uncha                  | anged              | x = Bit is unkr | nown    | -n/n = Value a                     | at POR and BO | R/Value at all o | ther Resets |  |  |

| bit 7-6 | RC<7:6>: PORTC I/O Value bits <sup>(1,2)</sup>             |

|---------|------------------------------------------------------------|

|         | 1 = Port pin is ≥ Viн                                      |

|         | 0 = Port pin is <u>&lt;</u> VIL                            |

| bit 5-0 | RC<5:0>: PORTC General Purpose I/O Pin bits <sup>(2)</sup> |

|         | 1 = Port pin is <u>&gt;</u> Viн                            |

|         | 0 = Port pin is <u>&lt;</u> VIL                            |

'0' = Bit is cleared

Note 1: PIC16(L)F18346 only; otherwise read as '0'.

2: Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

#### REGISTER 12-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1               | R/W-1/1               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | <b>TRISC&lt;7:6&gt;</b> : PORTC Tri-State Control bits <sup>(1)</sup><br>1 = PORTC pin configured as an input (tri-stated)<br>0 = PORTC pin configured as an output |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-0 | <b>TRISC&lt;5:0&gt;:</b> PORTC Tri-State Control bits<br>1 = PORTC pin configured as an input (tri-stated)                                                          |

|         | 0 = PORTC pin configured as an output                                                                                                                               |

Note 1: PIC16(L)F18346 only; otherwise read as '0'.

© 2016-2017 Microchip Technology Inc.

| R/W/HS/SC-0/0                                           | R/W-0/0                                                                                                                            | R/W-0/0                                                                | R/W-1/1                                                      | R/W-0/0                                                                                                             | R/W-1/1                                                               | U-0            | U-0         |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------|-------------|

| SHUTDOWN                                                | REN                                                                                                                                | LSBE                                                                   | )<1:0>                                                       | LSAC                                                                                                                | ><1:0>                                                                | —              |             |

| bit 7                                                   |                                                                                                                                    | ·                                                                      |                                                              |                                                                                                                     |                                                                       |                | bit 0       |

|                                                         |                                                                                                                                    |                                                                        |                                                              |                                                                                                                     |                                                                       |                |             |

| Legend:                                                 |                                                                                                                                    |                                                                        |                                                              |                                                                                                                     |                                                                       |                |             |

| R = Readable bit                                        | t                                                                                                                                  | W = Writable                                                           | bit                                                          | U = Unimplem                                                                                                        | ented bit, read                                                       | as '0'         |             |

| u = Bit is unchan                                       | ged                                                                                                                                | x = Bit is unki                                                        | nown                                                         | -n/n = Value a                                                                                                      | t POR and BOR                                                         | Value at all c | ther Resets |

| '1' = Bit is set '0' = Bit is cleared q = Value depende |                                                                                                                                    |                                                                        |                                                              |                                                                                                                     | ends on condition                                                     | on             |             |

| bit 7                                                   | 1 = An auto                                                                                                                        | : Auto-Shutdov<br>-shutdown stat<br>-shutdown eve                      | e is in effect                                               |                                                                                                                     |                                                                       |                |             |

| bit 6                                                   | <ul> <li><b>REN:</b> Auto-Restart Enable bit</li> <li>1 = Auto-restart is enabled</li> <li>0 = Auto-restart is disabled</li> </ul> |                                                                        |                                                              |                                                                                                                     |                                                                       |                |             |

| bit 5-4                                                 | 11 = A logic<br>10 = A logic<br>01 = Pin is tri<br>00 = The ina                                                                    | 1' is placed on<br>0' is placed on<br>i-stated on CW<br>ctive state of | CWGxB/D wh<br>CWGxB/D wh<br>GxB/D when a<br>the pin, inclue  | Shutdown State (<br>nen an auto-shut<br>nen an auto-shut<br>an auto-shutdow<br>ding polarity, is<br>utdown event oc | down event oco<br>down event oco<br>n event occurs.<br>placed on CW   | curs.          | he required |

| bit 3-2                                                 | 11 = A logic '<br>10 = A logic '<br>01 = Pin is tri<br>00 = The ina                                                                | 1' is placed on<br>0' is placed on<br>i-stated on CW<br>ctive state of | CWGxA/C wh<br>CWGxA/C wh<br>G1A/C when a<br>the pin, include | Shutdown State (<br>nen an auto-shut<br>nen an auto-shut<br>an auto-shutdow<br>ding polarity, is<br>utdown event oc | adown event occ<br>adown event occ<br>n event occurs.<br>placed on CW | curs.          | he required |

| bit 1-0                                                 | Unimplemen                                                                                                                         | ted: Read as '                                                         | 0'                                                           |                                                                                                                     |                                                                       |                |             |

|                                                         |                                                                                                                                    |                                                                        |                                                              | 0-1), to place the                                                                                                  | •                                                                     |                | •           |

#### REGISTER 20-6: CWGxAS0: CWG AUTO-SHUTDOWN CONTROL REGISTER 0

2: The outputs will remain in auto-shutdown state until the next rising edge of the CWG data input after this bit is cleared.

| R/W-x/u          | R/W-x/u      | R/W-x/u                              | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|--------------|--------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG3D4T         | LCxG3D4N     | LCxG3D3T                             | LCxG3D3N        | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |

| bit 7            |              |                                      |                 |                |                  |                  | bit (       |

|                  |              |                                      |                 |                |                  |                  |             |

| Legend:          | bit          | W = Writable                         | h:t             |                | nantad hit raad  |                  |             |

| R = Readable bit |              |                                      |                 |                | nented bit, read |                  | than Decete |

| u = Bit is unch  | angeo        | x = Bit is unkr                      |                 | -n/n = value a | at POR and BO    | R/Value at all c | iner Resets |

| '1' = Bit is set |              | '0' = Bit is cle                     | ared            |                |                  |                  |             |

| bit 7            | LCxG3D4T· (  | Gate 2 Data 4 1                      | īrue (non-inve  | rted) hit      |                  |                  |             |

| Sit I            |              | (true) is gated i                    |                 |                |                  |                  |             |

|                  |              | (true) is not gat                    |                 |                |                  |                  |             |

| bit 6            | LCxG3D4N:    | Gate 2 Data 4                        | Negated (inve   | rted) bit      |                  |                  |             |

|                  | 1 = CLCIN3   | (inverted) is ga                     | ted into CLCx   | Gate 2         |                  |                  |             |

|                  | 0 = CLCIN3   | (inverted) is no                     | t gated into Cl | _Cx Gate 2     |                  |                  |             |

| bit 5            | LCxG3D3T: (  | Gate 2 Data 3 1                      | rue (non-inve   | rted) bit      |                  |                  |             |

|                  |              | (true) is gated i                    |                 |                |                  |                  |             |

|                  |              | (true) is not gat                    |                 |                |                  |                  |             |

| bit 4            |              | Gate 2 Data 3                        | •               | ,              |                  |                  |             |

|                  |              | (inverted) is ga<br>(inverted) is no |                 |                |                  |                  |             |

| bit 3            |              | Gate 2 Data 2 1                      | 0               |                |                  |                  |             |

| bit 0            |              | (true) is gated i                    |                 | ,              |                  |                  |             |

|                  |              | (true) is not gat                    |                 |                |                  |                  |             |

| bit 2            | LCxG3D2N:    | Gate 2 Data 2                        | Negated (inve   | rted) bit      |                  |                  |             |

|                  | 1 = CLCIN1 ( | (inverted) is ga                     | ted into CLCx   | Gate 2         |                  |                  |             |

|                  | 0 = CLCIN1   | (inverted) is no                     | t gated into Cl | _Cx Gate 2     |                  |                  |             |

| bit 1            | LCxG3D1T: (  | Gate 2 Data 1 1                      | rue (non-inve   | rted) bit      |                  |                  |             |

|                  |              | (true) is gated i                    |                 |                |                  |                  |             |

|                  |              | (true) is not gat                    |                 |                |                  |                  |             |

| bit 0            |              | Gate 2 Data 1                        | •               | ,              |                  |                  |             |

|                  |              | (inverted) is ga<br>(inverted) is no |                 |                |                  |                  |             |

|                  |              |                                      |                 |                |                  |                  |             |

# REGISTER 21-9: CLCxGLS2: GATE 2 LOGIC SELECT REGISTER

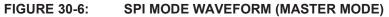

#### 30.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 30-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register. This then, would give waveforms for SPI communication as shown in Figure 30-6, Figure 30-8, Figure 30-9 and Figure 30-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SPPxADD + 1))

Figure 30-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

#### REGISTER 30-2: SSPxCON1: SSP CONTROL REGISTER 1 (CONTINUED)

- bit 3-0 SSPM<3:0>: Synchronous Serial Port Mode Select bits 1111 = I<sup>2</sup>C Slave mode, 10-bit address with Start and Stop bit interrupts enabled  $1110 = I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled 1101 = Reserved 1100 = Reserved  $1011 = I^2C$  firmware controlled Master mode (slave idle) 1010 = SPI Master mode, clock = Fosc/(4 \* (SPPxADD+1))<sup>(5)</sup> 1001 = Reserved  $1000 = I^2C$  Master mode, clock = Fosc / (4 \* (SPPxADD+1))<sup>(4)</sup> 0111 =  $I^2C$  Slave mode, 10-bit address  $0110 = I^2C$  Slave mode. 7-bit address 0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin 0100 = SPI Slave mode, clock = SCK pin,  $\overline{SS}$  pin control enabled 0011 = SPI Master mode, clock = T2 match/2 0010 = SPI Master mode, clock = Fosc/64 0001 = SPI Master mode, clock = Fosc/16 0000 = SPI Master mode. clock = Fosc/4

- **Note 1:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SPPxBUF register.

- **2:** When enabled, these pins must be properly configured as input or output. Use SSP1SSPPS, SSP1CLKPPS, SSP1DATPPS, and RxyPPS to select the pins.

- **3:** When enabled, the SDA and SCL pins must be configured as inputs. Use SSPxCLKPPS, SSPxDATPPS, and RxyPPS to select the pins.

- 4: SPPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

- **5:** SPPxADD value of 0 is not supported. Use SSPM = 0000 instead.

| R/W-0/0             | R/W-0/0                      | R/W-0/0                                        | R/W-0/0            | R/W-0/0        | R-0/0              | R-0/0            | R-x/x       |

|---------------------|------------------------------|------------------------------------------------|--------------------|----------------|--------------------|------------------|-------------|

| SPEN <sup>(1)</sup> | RX9                          | SREN                                           | CREN               | ADDEN          | FERR               | OERR             | RX9D        |

| bit 7               | ·                            | 1                                              | ·                  |                |                    | ·                | bit (       |

| Legend:             |                              |                                                |                    |                |                    |                  |             |

| R = Readable        | e bit                        | W = Writable                                   | bit                | U = Unimple    | mented bit, read   | d as '0'         |             |

| u = Bit is uncl     | nanged                       | x = Bit is unk                                 | nown               | •              | at POR and BC      |                  | ther Resets |

| '1' = Bit is set    |                              | '0' = Bit is cle                               | eared              |                |                    |                  |             |

| bit 7               | SPEN: Seria                  | Il Port Enable b                               | it(1)              |                |                    |                  |             |

|                     | 1 = Serial p<br>0 = Serial p | ort enabled<br>ort disabled (he                | eld in Reset)      |                |                    |                  |             |

| bit 6               | <b>RX9:</b> 9-bit R          | eceive Enable                                  | bit                |                |                    |                  |             |

|                     |                              | 9-bit reception<br>8-bit reception             |                    |                |                    |                  |             |

| bit 5               | SREN: Sing                   | le Receive Ena                                 | ble bit            |                |                    |                  |             |

|                     | Asynchrono                   | <u>us mode</u> :                               |                    |                |                    |                  |             |

|                     |                              | iis mode – valu<br><u>s mode – Mast</u> e      | •                  |                |                    |                  |             |

|                     |                              | single receive                                 |                    |                |                    |                  |             |

|                     |                              | s single receive                               |                    |                |                    |                  |             |

|                     |                              | eared after rece<br>s mode – Slave             |                    | ele.           |                    |                  |             |

|                     | -                            | iis mode – valu                                |                    |                |                    |                  |             |

| bit 4               |                              | inuous Receive                                 | •                  |                |                    |                  |             |

|                     | Asynchrono                   | <u>us mode</u> :                               |                    |                |                    |                  |             |

|                     |                              | s continuous ree<br>s continuous re<br>s mode: |                    | ole bit CREN i | s cleared          |                  |             |

|                     | 1 = Enables                  |                                                |                    | ole bit CREN i | s cleared (CREI    | N overrides SR   | EN)         |

| bit 3               | ADDEN: Ad                    | dress Detect E                                 | nable bit          |                |                    |                  |             |

|                     | Asynchrono                   | us mode 9-bit (                                | RX9 = 1 <u>)</u> : |                |                    |                  |             |

|                     | the rece                     | ive buffer is se                               | t                  | -              | bad of the receiv  |                  |             |

|                     | Asynchrono                   | us mode 8-bit (                                | RX9 = 0):          | are received a | and ninth bit can  | i be used as pa  | rity dit    |

|                     |                              | is mode – valu                                 | e ignored          |                |                    |                  |             |

| bit 2               | FERR: Fram                   | -                                              | undeted by rea     |                | Creatister and re  | anivo novt volic | huto)       |

|                     | 1 = Framing<br>0 = No fram   |                                                |                    | IUNING RUTREC  | G register and re  |                  | i byte)     |

| bit 1               | OERR: Over                   | rrun Error bit                                 |                    |                |                    |                  |             |

|                     | 1 = Overrur<br>0 = No over   | error (can be or<br>run error                  | cleared by clea    | ring bit CREN  | 1)                 |                  |             |

| bit 0               | RX9D: Ninth                  | bit of Receive                                 | d Data             |                |                    |                  |             |

|                     | This can be                  | address/data b                                 | it or a parity bit | and must be    | calculated by us   | ser firmware.    |             |

|                     | e EUSART1 m<br>sociated TRIS |                                                |                    |                | i-state to drive a | as needed. Con   | figure the  |

#### . . . . . . .

| R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0                              | R/W-0         | R/W-0            | R/W-0       |  |

|------------------|-------|-------------------|-------|------------------------------------|---------------|------------------|-------------|--|

|                  |       |                   | SP1BF | RG<15:8>                           |               |                  |             |  |

| bit 7            |       |                   |       |                                    |               |                  | bit 0       |  |

|                  |       |                   |       |                                    |               |                  |             |  |

| Legend:          |       |                   |       |                                    |               |                  |             |  |

| R = Readable     | bit   | W = Writable b    | oit   | U = Unimplemented bit, read as '0' |               |                  |             |  |

| u = Bit is uncha | anged | x = Bit is unkno  | own   | -n/n = Value a                     | at POR and BO | R/Value at all c | ther Resets |  |

| '1' = Bit is set |       | '0' = Bit is clea | red   |                                    |               |                  |             |  |

# **REGISTER 31-7:** SP1BRGH<sup>(1, 2)</sup>: BAUD RATE GENERATOR HIGH REGISTER

bit 7 SP1BRG<15:8>: Upper eight bits of the Baud Rate Generator

**Note 1:** SP1BRGH value is ignored for all modes unless BAUD1CON<BRG16> is active.

2: Writing to SP1BRGH resets the BRG counter.

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|--------|--------|--------|-----------|--------|--------|---------------------|

| TRISA                 | —                     | _                     | TRISA5 | TRISA4 | (2)    | TRISA2    | TRISA1 | TRISA0 | 143                 |

| ANSELA                | _                     | _                     | ANSA5  | ANSA4  | _      | ANSA2     | ANSA1  | ANSA0  | 144                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5 | TRISB4 |        |           |        | _      | 149                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5  | ANSB4  |        | _         |        |        | 150                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5 | TRISC4 | TRISC3 | TRISC2    | TRISC1 | TRISC0 | 155                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5  | ANSC4  | ANSC3  | ANSC2     | ANSC1  | ANSC0  | 157                 |

| INTCON                | GIE                   | PEIE                  | _      | —      | _      | _         | _      | INTEDG | 100                 |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF   | TXIF   | SSP1IF | BCL1IF    | TMR2IF | TMR1IF | 107                 |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE   | TXIE   | SSP1IE | BCL1IE    | TMR2IE | TMR1IE | 102                 |

| RC1STA                | SPEN                  | RX9                   | SREN   | CREN   | ADDEN  | FERR      | OERR   | RX9D   | 384                 |

| TX1STA                | CSRC                  | TX9                   | TXEN   | SYNC   | SENDB  | BRGH      | TRMT   | TX9D   | 383                 |

| BAUD1CON              | ABDOVF                | RCIDL                 | _      | SCKP   | BRG16  | _         | WUE    | ABDEN  | 385                 |

| RC1REG                |                       |                       |        | RC1RE  | G<7:0> |           |        |        | 386                 |

| TX1REG                |                       |                       |        | TX1RE  | G<7:0> |           |        |        | 386                 |

| SP1BRGL               |                       |                       |        | SP1BR  | G<7:0> |           |        |        | 386                 |

| SP1BRGH               |                       | SP1BRG<15:8>          |        |        |        |           |        |        |                     |

| RXPPS                 | —                     | RXPPS<4:0>            |        |        |        |           |        |        | 162                 |

| CLCxSELy              | _                     | _                     | _      |        | L      | CxDyS<4:0 | >      |        | 229                 |

| MDSRC                 | —                     | —                     |        | —      |        | MDMS      | S<3:0> |        | 272                 |

TABLE 31-2: SUMMARY OF REGISTERS ASSOCIATED WITH EUSART1

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the EUSART1 module.

**Note 1:** PIC16(L)F18346 only.

**2:** Unimplemented, read as '1'.

|        |                | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                |                   |                             |                |                   |                             |                |                    |                             |  |

|--------|----------------|-------------------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc           | = 32.00                       | 0 MHz                       | Fosc           | Fosc = 20.000 MHz |                             |                | Fosc = 18.432 MHz |                             |                | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | —              |                               | _                           | _              |                   | _                           | _              |                   | _                           |                | _                  | _                           |  |

| 1200   | —              | _                             | —                           | —              |                   | —                           | —              |                   | —                           | _              |                    | —                           |  |

| 2400   | —              | _                             | —                           | —              |                   | —                           | —              |                   | —                           | _              | _                  | _                           |  |

| 9600   | 9615           | 0.16                          | 207                         | 9615           | 0.16              | 129                         | 9600           | 0.00              | 119                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417          | 0.00                          | 191                         | 10417          | 0.00              | 119                         | 10378          | -0.37             | 110                         | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k         | 0.16                          | 103                         | 19.23k         | 0.16              | 64                          | 19.20k         | 0.00              | 59                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 57.14k         | -0.79                         | 34                          | 56.82k         | -1.36             | 21                          | 57.60k         | 0.00              | 19                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 117.64k        | 2.12                          | 16                          | 113.64k        | -1.36             | 10                          | 115.2k         | 0.00              | 9                           | 115.2k         | 0.00               | 5                           |  |

# TABLE 31-4: BAUD RATE FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                |                  |                             |                   |            |                             |                  |            |                             |

|--------|----------------|-------------------------------|-----------------------------|----------------|------------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000                     | ) MHz                       | Fos            | Fosc = 4.000 MHz |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _                             | —                           | _              |                  | _                           | _                 | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | —              | —                             | —                           | 1202           | 0.16             | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16                          | 207                         | 2404           | 0.16             | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16                          | 51                          | 9615           | 0.16             | 25                          | 9600              | 0.00       | 23                          | —                | _          | _                           |

| 10417  | 10417          | 0.00                          | 47                          | 10417          | 0.00             | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231          | 0.16                          | 25                          | 19.23k         | 0.16             | 12                          | 19.2k             | 0.00       | 11                          | —                | _          | _                           |

| 57.6k  | 55556          | -3.55                         | 8                           | —              | _                | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | —              | _                             | —                           | —              | _                | —                           | 115.2k            | 0.00       | 1                           | —                | —          | —                           |

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                |                   |                             |                |                   |                             |                |                    |                             |  |

|--------|----------------|-------------------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Foso           | : = 32.00                     | 0 MHz                       | Fosc           | Fosc = 20.000 MHz |                             |                | Fosc = 18.432 MHz |                             |                | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0          | 0.00                          | 6666                        | 300.0          | -0.01             | 4166                        | 300.0          | 0.00              | 3839                        | 300.0          | 0.00               | 2303                        |  |

| 1200   | 1200           | -0.02                         | 3332                        | 1200           | -0.03             | 1041                        | 1200           | 0.00              | 959                         | 1200           | 0.00               | 575                         |  |

| 2400   | 2401           | -0.04                         | 832                         | 2399           | -0.03             | 520                         | 2400           | 0.00              | 479                         | 2400           | 0.00               | 287                         |  |

| 9600   | 9615           | 0.16                          | 207                         | 9615           | 0.16              | 129                         | 9600           | 0.00              | 119                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417          | 0.00                          | 191                         | 10417          | 0.00              | 119                         | 10378          | -0.37             | 110                         | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k         | 0.16                          | 103                         | 19.23k         | 0.16              | 64                          | 19.20k         | 0.00              | 59                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 57.14k         | -0.79                         | 34                          | 56.818         | -1.36             | 21                          | 57.60k         | 0.00              | 19                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 117.6k         | 2.12                          | 16                          | 113.636        | -1.36             | 10                          | 115.2k         | 0.00              | 9                           | 115.2k         | 0.00               | 5                           |  |

# PIC16(L)F18326/18346

| ΜΟΥΙΨ            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ \textbf{-32} \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                               |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{FSR + 1 (preincrement)} \\ &\text{FSR - 1 (predecrement)} \\ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{FSR + 1 (all increments)} \\ &\text{FSR - 1 (all decrements)} \\ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                               |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |