Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

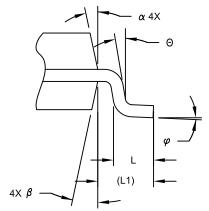

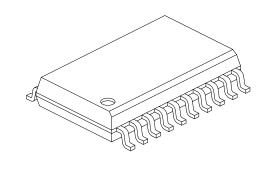

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18326-i-jq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                   | Function | Input<br>Type    | Output<br>Type | Description                            |

|--------------------------------------------------------|----------|------------------|----------------|----------------------------------------|

| RA5/ANA5/T1CKI <sup>(1)</sup> / T3CKI <sup>(1)</sup> / | RA5      | TTL/ST           | CMOS           | General purpose I/O.                   |

| T5CKI <sup>(1)</sup> / SOSCIN/SOSCI/<br>CLKIN/OSC1     | ANA5     | AN               | —              | ADC Channel A5 input.                  |

| CERIN/OSC1                                             | T1CKI    | TTL/ST           | —              | TMR1 Clock input.                      |

|                                                        | T3CKI    | TTL/ST           | _              | TMR3 Clock input.                      |

|                                                        | T5CKI    | TTL/ST           |                | TMR5 Clock input.                      |

|                                                        | SOSCIN   | TTL/ST           | —              | Secondary Oscillator input connection. |

|                                                        | SOSCI    | XTAL             | _              | Secondary Oscillator connection.       |

|                                                        | CLKIN    | TTL/ST           | _              | External clock input.                  |

|                                                        | OSC1     | XTAL             | —              | Crystal/Resonator (LP, XT, HS modes).  |

| RB4/ANB4/SDI1 <sup>(1)</sup> / SDA1 <sup>(1,3)</sup> / | RB4      | TTL/ST           | CMOS           | General purpose I/O.                   |

| CLCIN2 <sup>(1)</sup>                                  | ANB4     | AN               | —              | ADC Channel B4 input.                  |

|                                                        | SDI1     | TTL/ST           | CMOS           | SPI Data input 1.                      |

|                                                        | SDA1     | I <sup>2</sup> C | OD             | I <sup>2</sup> C Data 1.               |

|                                                        | CLCIN2   | TTL/ST           | _              | Configurable Logic Cell 2 input.       |

| RB5/ANB5/SDI2 <sup>(1)</sup> / SDA2 <sup>(1,3)</sup> / | RB5      | TTL/ST           | CMOS           | General purpose I/O.                   |

| RX <sup>(1)</sup> /DT/CLCIN3 <sup>(1)</sup>            | ANB5     | AN               | _              | ADC Channel B5 input.                  |

|                                                        | SDI2     | TTL/ST           | CMOS           | SPI Data input 2.                      |

|                                                        | SDA2     | l <sup>2</sup> C | OD             | I <sup>2</sup> C Data 2.               |

|                                                        | RX       | TTL/ST           | CMOS           | EUSART asynchronous input.             |

|                                                        | DT       | TTL/ST           | CMOS           | EUSART synchronous data output.        |

|                                                        | CLCIN3   | TTL/ST           | _              | Configurable Logic Cell 3 input.       |

| RB6/ANB6/SCK1 <sup>(1)</sup> / SCL1 <sup>(1,3)</sup>   | RB6      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANB6     | AN               | _              | ADC Channel B6 input.                  |

|                                                        | SCK1     | TTL/ST           | CMOS           | SPI Clock 1.                           |

|                                                        | SCL1     | l <sup>2</sup> C | OD             | I <sup>2</sup> C Clock 1.              |

| RB7/ANB7/SCK2 <sup>(1)</sup> / SCL2 <sup>(1,3)</sup>   | RB7      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANB7     | AN               | _              | ADC Channel B7 input.                  |

|                                                        | SCK2     | TTL/ST           | CMOS           | SPI Clock 2.                           |

|                                                        | SCL2     | l <sup>2</sup> C | OD             | I <sup>2</sup> C Clock 2.              |

| RC0/ANC0/C2IN0+                                        | RC0      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANC0     | AN               | _              | ADC Channel C0 input.                  |

|                                                        | C2IN0+   | AN               | _              | Comparator C2 positive input.          |

| RC1/ANC1/C1IN1-/C2IN1-                                 | RC1      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANC1     | AN               | _              | ADC Channel C1 input.                  |

|                                                        | C1IN1-   | AN               | _              | Comparator C1 negative input.          |

|                                                        | C2IN1-   | AN               |                | Comparator C2 negative input.          |

| RC2/ANC2/C1IN2-/C2IN2-/                                | RC2      | TTL/ST           | CMOS           | General purpose I/O.                   |

| MDCIN1 <sup>(1)</sup>                                  | ANC2     | AN               | _              | ADC Channel C2 input.                  |

|                                                        | C1IN2-   | AN               | _              | Comparator C1 negative input.          |

|                                                        | C2IN2-   | AN               | _              | Comparator C2 negative input.          |

|                                                        | MDCIN1   | TTL/ST           | _              | Modular Carrier input 1.               |

TABLE 1-3: PIC16(L)F18346 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| Address | s Name | PIC16(L)F18326         | Bit 7 | Bit 6         | Bit 5      | Bit 4         | Bit 3             | Bit 2  | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|------------------------|-------|---------------|------------|---------------|-------------------|--------|-------|-------|-----------------------|---------------------------------|

| Bank (  | )      |                        |       |               |            |               |                   |        |       |       |                       |                                 |

|         |        |                        |       |               | CPU CORE R | EGISTERS; see | Table 4-2 for spe | cifics |       |       |                       |                                 |

| 00Ch    | PORTA  |                        | —     | _             | RA5        | RA4           | RA3               | RA2    | RA1   | RA0   | xx xxxx               | uu uuuu                         |

| 00Dh    | PORTB  | ORTB X — Unimplemented |       |               |            |               |                   |        |       |       | —                     | —                               |

|         |        | — ×                    | RB7   | RB6           | RB5        | RB4           | _                 | _      | —     | _     | XXXX                  | uuuu                            |

| 00Eh    | PORTC  | X –                    |       | _             | RC5        | RC4           | RC3               | RC2    | RC1   | RC0   | xx xxxx               | uu uuuu                         |

|         |        | — ×                    | RC7   | RC6           | RC5        | RC4           | RC3               | RC2    | RC1   | RC0   | XXXX XXXX             | นนนน นนนน                       |

|         |        |                        |       | Unimplemented |            |               |                   |        |       |       |                       |                                 |

| 00Fh    | —      | _                      |       |               |            | Unimple       | emented           |        |       |       | —                     | —                               |

| 00Eh | PORTC  | Х | — | —             | _         | RC5     | RC4                            | RC3            | RC2    | RC1     | RC0    | xx xxxx   | uu uuuu   |

|------|--------|---|---|---------------|-----------|---------|--------------------------------|----------------|--------|---------|--------|-----------|-----------|

|      |        |   | Х | RC7           | RC6       | RC5     | RC4                            | RC3            | RC2    | RC1     | RC0    | XXXX XXXX | uuuu uuuu |

| 00Fh | —      | - | - | Unimplemented |           |         |                                |                |        |         |        | - 1       | —         |

| 010h | PIR0   |   |   | —             | —         | TMR0IF  | IOCIF                          | —              | —      | —       | INTF   | 000       | 000       |

| 011h | PIR1   |   |   | TMR1GIF       | ADIF      | RCIF    | TXIF                           | SSP1IF         | BCL1IF | TMR2IF  | TMR1IF | 0000 0000 | 0000 0000 |

| 012h | PIR2   |   |   | TMR6IF        | C2IF      | C1IF    | NVMIF                          | SSP2IF         | BCL2IF | TMR4IF  | NCO1IF | 0000 0000 | 0000 0000 |

| 013h | PIR3   |   |   | OSFIF         | CSWIF     | TMR3GIF | TMR3IF                         | CLC4IF         | CLC3IF | CLC2IF  | CLC1IF | 0000 0000 | 0000 0000 |

| 014h | PIR4   |   |   | CWG2IF        | CWG1IF    | TMR5GIF | TMR5IF                         | CCP4IF         | CCP3IF | CCP2IF  | CCP1IF | 0000 0000 | 0000 0000 |

| 015h | TMR0L  |   |   | TMR0L<7:0>    |           |         |                                |                |        |         |        | XXXX XXXX | XXXX XXXX |

| 016h | TMR0H  |   |   | TMR0H<7:0>    |           |         |                                |                |        |         |        | 1111 1111 | 1111 1111 |

| 017h | T0CON0 |   |   | TOEN          |           | TOOUT   | T016BIT                        |                | TOOUT  | PS<3:0> |        | 0-00 0000 | 0-00 0000 |

| 018h | T0CON1 |   |   |               | T0CS<2:0> |         | T0ASYNC                        |                | T0CKP  | S<3:0>  |        | 0000 0000 | 0000 0000 |

| 019h | TMR1L  |   |   |               |           |         | TMR1I                          | _<7:0>         |        |         |        | XXXX XXXX | uuuu uuuu |

| 01Ah | TMR1H  |   |   |               |           |         | TMR1                           | H<7:0>         |        |         |        | XXXX XXXX | uuuu uuuu |

| 01Bh | T1CON  |   |   | TMR1CS        | <1:0>     | T1CKF   | PS<1:0> T1SOSC T1SYNC — TMR1ON |                |        |         |        | 0000 00-0 | uuuu uu-u |

| 01Ch | T1GCON |   |   | TMR1GE        | T1GPOL    | T1GTM   | T1GSPM                         | T1GGO/<br>DONE | T1GVAL | T1GS    | S<1:0> | 00x0 0x00 | uuuu uxuu |

| 01Dh | TMR2   |   |   |               |           |         | TMR2                           | <7:0>          |        |         |        | 0000 0000 | 0000 0000 |

| 01Eh | PR2    |   |   |               |           |         | PR2<                           | <7:0>          |        |         |        | 1111 1111 | 1111 1111 |

|      |        |   |   |               |           |         |                                |                |        |         |        |           |           |

TMR2ON

T2CKPS<1:0>

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

T2OUTPS<3:0>

Note 1: Only on PIC16F18326/18346.

T2CON

01Fh

2: Register accessible from both User and ICD Debugger.

\_

-000 0000 -000 0000

#### 4.4 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 4-4 through Figure 4-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer and does not cause a Reset when either a Stack Overflow or Underflow occur if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

If the STVREN bit in Configuration Words is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

| Note 1: | There are no instructions/mnemonics     |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|--|--|--|--|

|         | called PUSH or POP. These are actions   |  |  |  |  |  |  |  |  |

|         | that occur from the execution of the    |  |  |  |  |  |  |  |  |

|         | CALL, CALLW, RETURN, RETLW and          |  |  |  |  |  |  |  |  |

|         | RETFIE instructions or the vectoring to |  |  |  |  |  |  |  |  |

|         | an interrupt address.                   |  |  |  |  |  |  |  |  |

#### 4.4.1 ACCESSING THE STACK

The stack is accessible through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of Overflow and Underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time, STKPTR can be read to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 4-4 through Figure 4-7 for examples of accessing the stack.

#### FIGURE 4-4: ACCESSING THE STACK EXAMPLE 1

| TOSH:TOSL 0x0F        | STKPTR = 0x1F Stack Reset Disabled<br>(STVREN = 0)                                    |

|-----------------------|---------------------------------------------------------------------------------------|

| 0x0D                  | -                                                                                     |

| 0x0C                  | -                                                                                     |

| 0x0B                  |                                                                                       |

| 0x0A                  | Initial Stock Configuration:                                                          |

| 0x09                  | Initial Stack Configuration:                                                          |

| 0x08                  | After Reset, the stack is empty. The<br>empty stack is initialized so the Stack       |

| 0x07                  | Pointer is pointing at 0x1F. If the Stack<br>Overflow/Underflow Reset is enabled, the |

| 0x06                  | TOSH/TOSL registers will return '0'. If<br>the Stack Overflow/Underflow Reset is      |

| 0x05                  | disabled, the TOSH/TOSL registers will<br>return the contents of stack address 0x0F.  |

| 0x04                  |                                                                                       |

| 0x03                  |                                                                                       |

| 0x02                  |                                                                                       |

| 0x01                  |                                                                                       |

| 0x00                  |                                                                                       |

| TOSH:TOSL 0x1F 0x0000 | STKPTR = 0x1F Stack Reset Enabled (STVREN = 1)                                        |

# 7.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) and New Divider Selection Request (NDIV) bits of the OSCCON1 register. The following clock sources can be selected:

- External Oscillator (EXTOSC)

- High-Frequency Internal Oscillator (HFINTOSC)

- Low-Frequency Internal Oscillator (LFINTOSC)

- Secondary Oscillator (SOSC)

- EXTOSC with 4x PLL

- HFINTOSC with 2x PLL

#### 7.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider Selection Request (NDIV) bits of the OSCCON1 register select the system clock source and frequencies that are used for the CPU and peripherals.

When the new values of NOSC<2:0> and NDIV<3:0> are written to OSCCON1, the current oscillator selection will continue to operate as the system clock while waiting for the new source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same and are ready immediately. The device may enter Sleep while waiting for the switch as described in Section 7.3.3 "Clock Switch and Sleep".

When the new oscillator is ready, the New Oscillator is Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of PIR3 become set (CSWIF = 1). If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the New Oscillator Ready bit (NOSCR) is set and the interrupt (if enabled) will be serviced at the new oscillator setting. If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- Set CSWHOLD = 0 so the switch can complete, or

- Copy COSC into NOSC<2:0> to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

Changing the clock post-divider without changing the clock source (i.e., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

## 7.3.2 PLL INPUT SWITCH

Switching between the PLL and any non-PLL source is managed as described above. The input to the PLL is established when NOSC<2:0> selects the PLL, and maintained by the COSC setting.

When NOSC<2:0> and COSC select the PLL with different input sources, the system continues to run using the COSC setting, and the new source is enabled per NOSC<2:0>. When the new oscillator is ready (and CSWHOLD = 0), system operation is suspended while the PLL input is switched and the PLL acquires lock.

## 7.3.3 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the Clock Switch Interrupt Flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

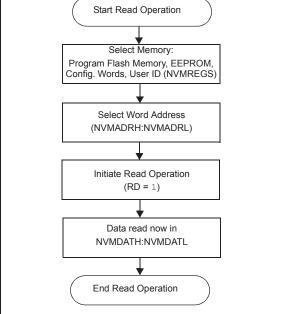

# FIGURE 11-1: PROGRAM FLASH MEMORY READ FLOWCHART

#### EXAMPLE 11-1: PROGRAM FLASH MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG ADDR HI : PROG ADDR LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELNVMADRL; Select Bank for NVMCON registersMOVLWPROG_ADDR_LO;MOVWFNVMADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWFNVMADRH; Store MSB of address

BCF

NVMCON1, NVMREGS ; Do not select Configuration Space

NVMCON1,RD ; Initiate read

BSF

RVMDATL,W ; Get LSB of word

PROG_DATA_LO ; Store in user location

NVMDATH,W ; Get MSB of word

PROG_DATA_HI ; Store in "

MOVF

MOVWF

MOVF

MOVWF

```

### 12.2.6 ANALOG CONTROL

The ANSELA register (Register 12-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 12.2.7 WEAK PULL-UP CONTROL

The WPUA register (Register 12-5) controls the individual weak pull-ups for each PORT pin.

PORTA pin RA3 includes the  $\overline{\text{MCLR}}/\text{VPP}$  input. The MCLR input allows the device to be reset, and can be disabled by the MCLRE bit of Configuration Word 2. A weak pull-up is present on the RA3 port pin. This weak pull-up is enabled when  $\overline{\text{MCLR}}$  is enabled ( $\overline{\text{MCLRE}} = 1$ ) or the WPUA3 bit is set. The weak pull-up is disabled when the  $\overline{\text{MCLR}}$  is disabled and the WPUA3 bit is clear.

#### 12.2.8 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 13.0 "Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

# 13.8 Register Definitions: PPS Input Selection

#### REGISTER 13-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

| U-0             | U-0                                                                                                              | U-0                                                                                                                                                                                                                                                                  | R/W-q/u                                                                                                                        | R/W-q/u        | R/W-q/u          | R/W-q/u          | R/W-q/u     |

|-----------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|-------------|

| _               | —                                                                                                                | —                                                                                                                                                                                                                                                                    |                                                                                                                                |                | xxxPPS<4:0>      |                  |             |

| bit 7           |                                                                                                                  |                                                                                                                                                                                                                                                                      |                                                                                                                                |                |                  |                  | bit         |

|                 |                                                                                                                  |                                                                                                                                                                                                                                                                      |                                                                                                                                |                |                  |                  |             |

| Legend:         |                                                                                                                  |                                                                                                                                                                                                                                                                      |                                                                                                                                |                |                  |                  |             |

| R = Readab      | le bit                                                                                                           | W = Writable                                                                                                                                                                                                                                                         | bit                                                                                                                            | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is und  | changed                                                                                                          | x = Bit is unk                                                                                                                                                                                                                                                       | nown                                                                                                                           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is se | et                                                                                                               | '0' = Bit is cle                                                                                                                                                                                                                                                     | ared                                                                                                                           | q = value dep  | ends on periph   | eral             |             |

| bit 7-5         | Unimplem                                                                                                         | ented: Read as                                                                                                                                                                                                                                                       | ·∩'                                                                                                                            |                |                  |                  |             |

| bit 4-0         | •                                                                                                                | 0>: Peripheral x                                                                                                                                                                                                                                                     |                                                                                                                                | tion hits      |                  |                  |             |

|                 |                                                                                                                  | eserved. Do not                                                                                                                                                                                                                                                      |                                                                                                                                |                |                  |                  |             |

|                 | 10110 = Pe<br>10101 = Pe<br>10100 = Pe<br>10011 = Pe<br>10001 = Pe<br>10000 = Pe<br><br>01111 = Pe<br>01110 = Pe | eripheral input is<br>eripheral input is | RC6 <sup>(1)</sup><br>RC5<br>RC4<br>RC3<br>RC2<br>RC1<br>RC0<br>RB7 <sup>(1)</sup><br>RB6 <sup>(1)</sup><br>RB5 <sup>(1)</sup> |                |                  |                  |             |

|                 | 00101 = Pe<br>00100 = Pe<br>00011 = Pe<br>00010 = Pe<br>00001 = Pe                                               | eserved. Do not<br>eripheral input is<br>eripheral input is<br>eripheral input is<br>eripheral input is<br>eripheral input is<br>eripheral input is                                                                                                                  | RA5<br>RA4<br>RA3<br>RA2<br>RA1                                                                                                |                |                  |                  |             |

**Note 1:** PIC16(L)F18346 only.

| R/W-0/0         | R/W-0/0     | R/W-0/0                                           | R/W-0/0         | R/W-0/0       | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|-------------|---------------------------------------------------|-----------------|---------------|------------------|------------------|--------------|

| NCOMD           | TMR6MD      | TMR5MD                                            | TMR4MD          | TMR3MD        | TMR2MD           | TMR1MD           | TMR0MD       |

| bit 7           |             |                                                   | •               |               |                  |                  | bit (        |

| Logondy         |             |                                                   |                 |               |                  |                  |              |

| Legend:         | e bit       |                                                   | L :4            |               | anted bit read   |                  |              |

| R = Readabl     |             | W = Writable                                      |                 | •             | nented bit, read |                  |              |

| u = Bit is und  | •           | x = Bit is unkr                                   |                 |               |                  | R/Value at all c | ither Resets |

| '1' = Bit is se | t           | '0' = Bit is clea                                 | ared            | q = value dep | ends on condit   | ion              |              |

| bit 7           | 1 = NCO1 m  | able Numerical<br>odule disabled<br>odule enabled | ly Control Osci | llator bit    |                  |                  |              |

| bit 6           | 1 = TMR6 mg | sable Timer TM<br>odule disabled<br>odule enabled | IR6 bit         |               |                  |                  |              |

| bit 5           | 1 = TMR5 mo | sable Timer TM<br>odule disabled<br>odule enabled | IR5 bit         |               |                  |                  |              |

| bit 4           | 1 = TMR4 mo | sable Timer TM<br>odule disabled<br>odule enabled | IR4 bit         |               |                  |                  |              |

| bit 3           | 1 = TMR3 mo | sable Timer TM<br>odule disabled<br>odule enabled | IR3 bit         |               |                  |                  |              |

| bit 2           | 1 = TMR2 m  | sable Timer TM<br>odule disabled<br>odule enabled | IR2 bit         |               |                  |                  |              |

| bit 1           | 1 = TMR1 m  | sable Timer TM<br>odule disabled<br>odule enabled | IR1 bit         |               |                  |                  |              |

| bit 0           | 1 = TMR0 m  | sable Timer TM<br>odule disabled<br>odule enabled | IR0 bit         |               |                  |                  |              |

#### REGISTER 14-2: PMD1: PMD CONTROL REGISTER 1

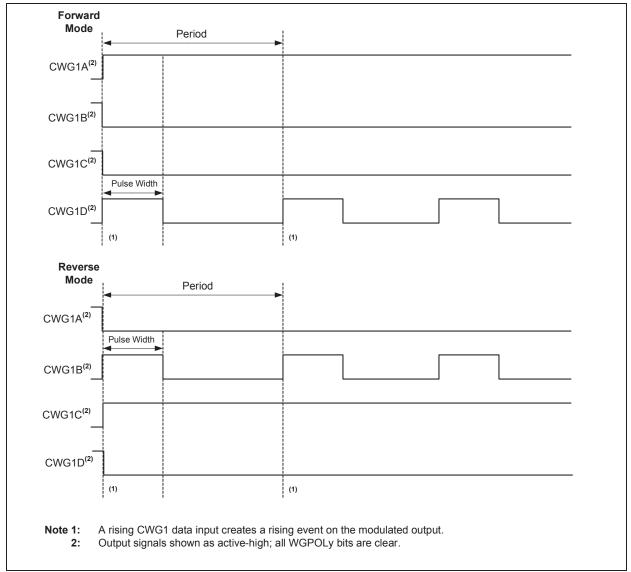

Full-Bridge Reverse Mode

In Full-Bridge Reverse mode (MODE<2:0> = 011),

CWGxC is driven to its active state and CWGxB is modulated while CWGxA and CWGxD are driven to

their inactive state, as illustrated at the bottom of

20.2.4.2

Figure 20-6.

## 20.2.4.1 Full-Bridge Forward Mode

In Full-Bridge Forward mode (MODE<2:0> = 010), CWGxA is driven to its active state and CWGxD is modulated while CWGxB and CWGxC are driven to their inactive state, as illustrated at the top of Figure 20-6.

#### FIGURE 20-6: EXAMPLE OF FULL-BRIDGE OUTPUT

# 20.2.4.3 Direction Change in Full-Bridge Mode

In Full-Bridge mode, changing MODE<2:0> controls the forward/reverse direction. Changes to MODE<2:0> change to the new direction on the next rising edge of the modulated input.

A direction change is initiated in software by changing the MODE<2:0> bits of the WGxCON0 register. The sequence is illustrated in Figure 20-7.

- The associated active output CWGxA and the inactive output CWGxC are switched to drive in the opposite direction.

- The previously modulated output CWGxD is switched to the inactive state, and the previously inactive output CWGxB begins to modulate.

- CWG modulation resumes after the direction-switch dead band has elapsed.

© 2016-2017 Microchip Technology Inc.

| U-0   | U-0 U-0 |  | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|---------|--|-----|---------|---------|---------|---------|

| —     |         |  | _   | MLC4OUT | MLC3OUT | MLC2OUT | MLC10UT |

| bit 7 |         |  |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

- bit 3 MLC4OUT: Mirror copy of LC4OUT bit

- bit 2 MLC3OUT: Mirror copy of LC3OUT bit

- bit 1 MLC2OUT: Mirror copy of LC2OUT bit

- bit 0 MLC10UT: Mirror copy of LC10UT bit

## TABLE 21-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

| Name                  | Bit7                  | Bit6                  | Bit5                                | Bit4     | Blt3     | Bit2     | Bit1       | Bit0     | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|-------------------------------------|----------|----------|----------|------------|----------|---------------------|

| ANSELA                | —                     | —                     | ANSA5                               | ANSA4    | —        | ANSA2    | ANSA1      | ANSA0    | 144                 |

| TRISA                 | —                     | —                     | TRISA5                              | TRISA4   | (2)      | TRISA2   | TRISA1     | TRISA0   | 143                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5                               | ANSB4    | —        | —        | _          | _        | 150                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5                              | TRISB4   | —        | —        | —          | —        | 149                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5                               | ANSC4    | ANSC3    | ANSC2    | ANSC1      | ANSC0    | 157                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5                              | TRISC4   | TRISC3   | TRISC2   | TRISC1     | TRISC0   | 155                 |

| INTCON                | GIE                   | PEIE                  | —                                   | —        | —        | —        | —          | INTEDG   | 100                 |

| PIR3                  | OSFIF                 | CSWIF                 | TMR3GIF                             | TMR3IF   | CLC4IF   | CLC3IF   | CLC2IF     | CLC1IF   | 109                 |

| PIE3                  | OSFIE                 | CSWIE                 | TMR3GIE                             | TMR3IE   | CLC4IE   | CLC3IE   | CLC2IE     | CLC1IE   | 104                 |

| CLC1CON               | LC1EN                 | —                     | LC1OUT LC1INTP LC1INTN LC1MODE<2:0> |          |          |          |            |          | 227                 |

| CLC1POL               | LC1POL                | —                     | —                                   | —        | LC1G4POL | LC1G3POL | LC1G2POL   | LC1G1POL | 228                 |

| CLC1SEL0              | —                     | _                     |                                     |          | LC1D1    | S<5:0>   |            |          | 229                 |

| CLC1SEL1              | —                     | —                     |                                     |          | LC1D2    | 2S<5:0>  |            |          | 229                 |

| CLC1SEL2              | —                     | _                     |                                     |          | LC1D3    | 3S<5:0>  |            |          | 229                 |

| CLC1SEL3              | —                     | _                     |                                     |          | LC1D4    | IS<5:0>  |            |          | 230                 |

| CLC1GLS0              | LC1G1D4T              | LC1G1D4N              | LC1G1D3T                            | LC1G1D3N | LC1G1D2T | LC1G1D2N | LC1G1D1T   | LC1G1D1N | 230                 |

| CLC1GLS1              | LC1G2D4T              | LC1G2D4N              | LC1G2D3T                            | LC1G2D3N | LC1G2D2T | LC1G2D2N | LC1G2D1T   | LC1G2D1N | 231                 |

| CLC1GLS2              | LC1G3D4T              | LC1G3D4N              | LC1G3D3T                            | LC1G3D3N | LC1G3D2T | LC1G3D2N | LC1G3D1T   | LC1G3D1N | 232                 |

| CLC1GLS3              | LC1G4D4T              | LC1G4D4N              | LC1G4D3T                            | LC1G4D3N | LC1G4D2T | LC1G4D2N | LC1G4D1T   | LC1G4D1N | 233                 |

| CLC2CON               | LC2EN                 | _                     | LC2OUT                              | LC2INTP  | LC2INTN  | L        | C2MODE<2:0 | >        | 227                 |

| CLC2POL               | LC2POL                | _                     | _                                   | _        | LC2G4POL | LC2G3POL | LC2G2POL   | LC2G1POL | 228                 |

| CLC2SEL0              | —                     | _                     |                                     |          | LC2D1    | S<5:0>   |            | •        | 229                 |

| CLC2SEL1              | —                     | _                     |                                     |          | LC2D2    | 2S<5:0>  |            |          | 229                 |

| CLC2SEL2              | —                     | _                     |                                     |          | LC2D3    | 3S<5:0>  |            |          | 229                 |

| CLC2SEL3              | —                     | —                     |                                     |          | LC2D4    | IS<5:0>  |            |          | 230                 |

| ADC Clock P         | eriod (TAD) |                             | Device Frequency (Fosc)     |                             |                             |                             |                             |  |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                       |  |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |  |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |  |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |  |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |  |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(2)</sup>      |  |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(2)</sup>      | 64.0 μs <sup>(2)</sup>      |  |  |

| ADCRC               | x11         | 1.0-6.0 μs <sup>(1,4)</sup> |  |  |

## TABLE 22-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

**Note 1:** See TAD parameter for ADCRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the ADCRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

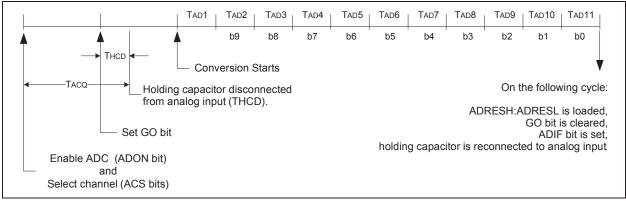

## FIGURE 22-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| R/W-x/u                                 | -x/u R/W-x/u R/W-x/u |   | R/W-x/u | R/W-x/u R/W-x/u                                       |   | R/W-x/u    | R/W-x/u |  |  |  |

|-----------------------------------------|----------------------|---|---------|-------------------------------------------------------|---|------------|---------|--|--|--|

| —                                       | —                    | — | —       | —                                                     | — | ADRES<9:8> |         |  |  |  |

| bit 7 bit 0                             |                      |   |         |                                                       |   |            |         |  |  |  |

|                                         |                      |   |         |                                                       |   |            |         |  |  |  |

| Legend:                                 |                      |   |         |                                                       |   |            |         |  |  |  |

| R = Readable bit W = Writable bit       |                      |   | bit     | U = Unimplemented bit, read as '0'                    |   |            |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                      |   |         | -n/n = Value at POR and BOR/Value at all other Resets |   |            |         |  |  |  |

#### REGISTER 22-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

bit 7-2 Reserved: Do not use.

'1' = Bit is set

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result

#### REGISTER 22-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

'0' = Bit is cleared

| R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| ADRES<7:0>  |         |         |         |         |         |         |         |  |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

# 26.8 Register Definitions: Timer0 Register

| R/W-0/0                                                                  | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                        | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|--------------------------------------------------------------------------|---------|-------------------|---------|------------------------------------------------|---------|---------|---------|

|                                                                          |         |                   | TMR     | )L<7:0>                                        |         |         |         |

| bit 7                                                                    |         |                   |         |                                                |         |         | bit 0   |

|                                                                          |         |                   |         |                                                |         |         |         |

| Legend:                                                                  |         |                   |         |                                                |         |         |         |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |         |                   |         |                                                |         |         |         |

| u = Bit is uncha                                                         | anged   | x = Bit is unkr   | nown    | -n/n = Value at POR and BOR/Value at all other |         |         |         |

| '1' = Bit is set                                                         |         | '0' = Bit is clea | ared    |                                                |         |         |         |

## REGISTER 26-1: TMR0L: TIMER0 COUNT REGISTER

bit 7-0 TMR0L<7:0>:TMR0 Counter bits 7..0

#### REGISTER 26-2: TMR0H: TIMER0 PERIOD REGISTER

| R/W-1/1 | R/W-1/1                  | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |

|---------|--------------------------|---------|---------|---------|---------|---------|---------|--|--|--|

|         | TMR0H<7:0> or TMR0<15:8> |         |         |         |         |         |         |  |  |  |

| bit 7   | bit 7 bit                |         |         |         |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 When T016BIT = 0 TMR0H<7:0>:TMR0 Period Register Bits 7..0 When T016BIT = 1 TMR0<15:8>: TMR0 Counter bits 15..8

## 31.1 EUSART1 Asynchronous Mode

The EUSART1 transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 31-3 for examples of baud rate configurations.

The EUSART1 transmits and receives the LSb first. The EUSART1's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 31.1.1 EUSART1 ASYNCHRONOUS TRANSMITTER

The EUSART1 transmitter block diagram is shown in Figure 31-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TX1REG register.

#### 31.1.1.1 Enabling the Transmitter

The EUSART1 transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART1 control bits are assumed to be in their default state.

Setting the TXEN bit of the TX1STA register enables the transmitter circuitry of the EUSART1. Clearing the SYNC bit of the TX1STA register configures the EUSART1 for asynchronous operation. Setting the SPEN bit of the RC1STA register enables the EUSART1 and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

## 31.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TX1REG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TX1REG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TX1REG until the Stop bit of the previous character has been transmitted. The pending character in the TX1REG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TX1REG.

## 31.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUD1CON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See Section 31.4.1.2 "Clock Polarity".

#### 31.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART1 transmitter is enabled and no character is being held for transmission in the TX1REG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TX1REG. The TXIF flag bit is not cleared immediately upon writing TX1REG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TX1REG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TX1REG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TX1REG.

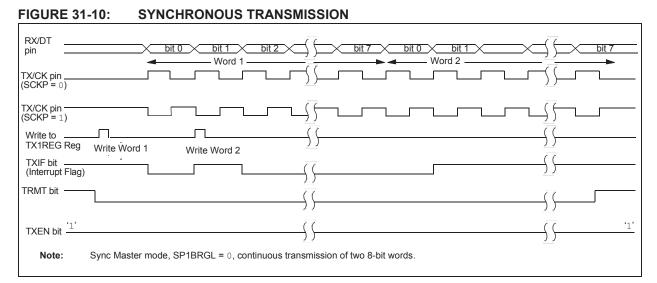

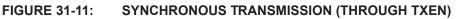

#### 31.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART1 is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RC1STA register) or the Continuous Receive Enable bit (CREN of the RC1STA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence. To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RC1REG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# 31.6 Register Definitions: EUSART1 Control

| R/W-0/0          | R/W-0/0                                                              | R/W-0/0                                               | R/W-0/0                                            | R/W-0/0        | R/W-0/0          | R-1/1            | R/W-0/0      |

|------------------|----------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|----------------|------------------|------------------|--------------|

| CSRC             | TX9                                                                  | TXEN <sup>(1)</sup>                                   | SYNC                                               | SENDB          | BRGH             | TRMT             | TX9D         |

| bit 7            |                                                                      | •                                                     |                                                    |                | ·                |                  | bit (        |

| Legend:          |                                                                      |                                                       |                                                    |                |                  |                  |              |

| R = Readable     | bit                                                                  | W = Writable                                          | bit                                                | U = Unimpler   | mented bit, read | as '0'           |              |

| u = Bit is unch  | anged                                                                | x = Bit is unki                                       | nown                                               | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                                                      | '0' = Bit is cle                                      | ared                                               |                |                  |                  |              |

| bit 7            | Asynchronou<br>Unused in thi<br>Synchronous<br>1 = Master r          | s mode – value                                        | e ignored<br>nerated intern                        |                | )                |                  |              |

| bit 6            | <b>TX9:</b> 9-bit Tra<br>1 = Selects                                 | ansmit Enable I<br>9-bit transmiss<br>8-bit transmiss | oit<br>ion                                         | ,              |                  |                  |              |

| bit 5            | <b>TXEN:</b> Trans<br>1 = Transmit<br>0 = Transmit                   |                                                       | 1)                                                 |                |                  |                  |              |

| bit 4            | SYNC: EUSA<br>1 = Synchron<br>0 = Asynchron                          |                                                       | lect bit                                           |                |                  |                  |              |

| bit 3            | Asynchronou<br>1 = Send SY<br>bit; clear<br>0 = SYNCH<br>Synchronous | NCH BREAK<br>ed by hardware<br>BREAK transm           | on next transr<br>e upon comple<br>iission disable | etion          | bit, followed by | 12 '0' bits, fol | lowed by Sto |

| bit 2            | Asynchronou<br>1 = High spe<br>0 = Low spect<br>Synchronous          | ed<br>ed                                              |                                                    |                |                  |                  |              |

| bit 1            | <b>TRMT:</b> Trans<br>1 = TSR emp<br>0 = TSR full                    | mit Shift Regisi<br>oty                               | er Status bit                                      |                |                  |                  |              |

| bit 0            | TX9D: Ninth<br>Can be addre                                          | bit of Transmit                                       | Data                                               |                |                  |                  |              |

# REGISTER 31-1: TX1STA: TRANSMIT STATUS AND CONTROL REGISTER

Note 1: SREN/CREN overrides TXEN in Sync mode.

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                  |            |                             |                   |            |                             |                |                  |                             |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | 299.9            | -0.02                         | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5          | 0.16             | 207                         |  |

| 1200   | 1199             | -0.08                         | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202           | 0.16             | 51                          |  |

| 2400   | 2404             | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404           | 0.16             | 25                          |  |

| 9600   | 9615             | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | —              | _                | _                           |  |

| 10417  | 10417            | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417          | 0.00             | 5                           |  |

| 19.2k  | 19.23k           | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          | —              | _                | _                           |  |

| 57.6k  | 55556            | -3.55                         | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | —              | _                | _                           |  |

| 115.2k | —                | _                             | —                           | —                | _          | —                           | 115.2k            | 0.00       | 1                           | —              | _                | —                           |  |

# TABLE 31-4: BAUD RATE FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz                                    |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |

| 1200   | 1200                                                 | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |

| 2400   | 2400                                                 | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |

| 9600   | 9604                                                 | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         |

| 10417  | 10417                                                | 0.00       | 767                         | 10417             | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16       | 264                         |

| 19.2k  | 19.18k                                               | -0.08      | 416                         | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         |

| 57.6k  | 57.55k                                               | -0.08      | 138                         | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          |

| 115.2k | 115.9k                                               | 0.64       | 68                          | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          |

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------|------------------------------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |                                                      |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0            | 0.00                                                 | 6666                        | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200             | -0.02                                                | 1666                        | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401             | 0.04                                                 | 832                         | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615             | 0.16                                                 | 207                         | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417            | 0                                                    | 191                         | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k           | 0.16                                                 | 103                         | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k           | -0.79                                                | 34                          | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | —                | _          | _                           |

| 115.2k | 117.6k           | 2.12                                                 | 16                          | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | —                | _          | _                           |

| TABLE 35-9: | PLL CLOCK TIMING SPECIFICATIONS |

|-------------|---------------------------------|

|-------------|---------------------------------|

| Standard Operating Conditions (unless otherwise stated) |         |                                         |       |       |      |       |            |

|---------------------------------------------------------|---------|-----------------------------------------|-------|-------|------|-------|------------|

| Param.<br>No.                                           | Sym.    | Characteristic                          | Min.  | Тур.† | Max. | Units | Conditions |

| PLL01                                                   | Fpllin  | PLL Input Frequency Range               | 4     |       | 8    | MHz   |            |

| PLL02                                                   | FPLLOUT | PLL Output Frequency Range              | 16    | —     | 32   | MHz   |            |

| PLL03                                                   | TPLLST  | PLL Lock Time from Start-up             | —     | 200   | —    | μs    | η          |

| PLL04                                                   | Fplljit | PLL Output Frequency Stability (Jitter) | -0.25 | —     | 0.25 | %     |            |

\* These parameters are characterized but not tested.