# Microchip Technology - PIC16F18326-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

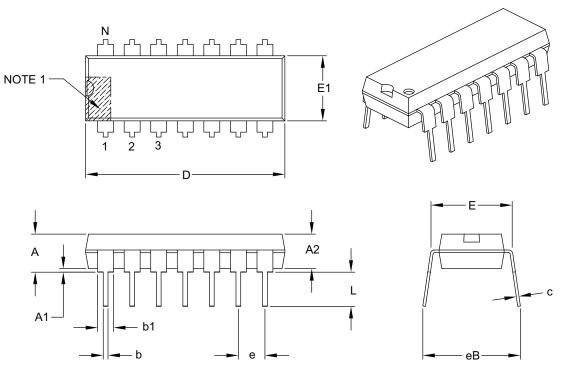

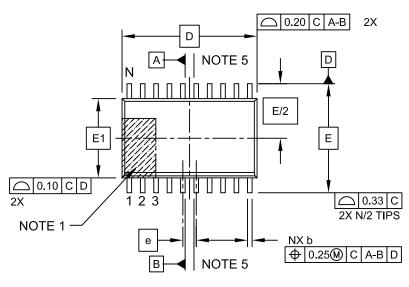

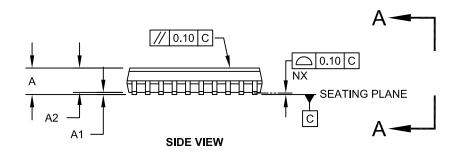

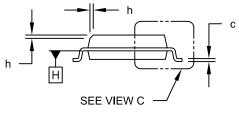

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18326-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                 |        | (0) (0)                          |       |               |       |         |         |             |       |       |                       |                                 |  |  |  |  |

|-------------------------------------------------|--------|----------------------------------|-------|---------------|-------|---------|---------|-------------|-------|-------|-----------------------|---------------------------------|--|--|--|--|

| Address                                         | Name   | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7 | Bit 6         | Bit 5 | Bit 4   | Bit 3   | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |  |  |  |  |

| Bank 2                                          | 29     |                                  |       | ·             |       | •       | -       | •           |       | •     | •                     |                                 |  |  |  |  |

| CPU CORE REGISTERS; see Table 4-2 for specifics |        |                                  |       |               |       |         |         |             |       |       |                       |                                 |  |  |  |  |

| EA0h                                            | RC0PPS |                                  | _     | —             | _     |         |         | RC0PPS<4:0> |       |       | 0 0000                | u uuuu                          |  |  |  |  |

| EA1h                                            | RC1PPS |                                  | —     | —             | —     |         |         | RC1PPS<4:0> |       |       | 0 0000                | u uuuu                          |  |  |  |  |

| EA2h                                            | RC2PPS |                                  | —     | _             | —     |         |         | RC2PPS<4:0> |       |       | 0 0000                | u uuuu                          |  |  |  |  |

| EA3h                                            | RC3PPS |                                  | _     | _             | _     |         |         | RC3PPS<4:0> |       |       | 0 0000                | u uuu                           |  |  |  |  |

| EA4h                                            | RC4PPS |                                  | _     | _             | —     |         |         | RC4PPS<4:0> |       |       | 0 0000                | u uuuu                          |  |  |  |  |

| EA5h                                            | RC5PPS |                                  | _     | _             | _     |         |         | RC5PPS<4:0> |       |       | 0 0000                | u uuuu                          |  |  |  |  |

| EA6h                                            | RC6PPS | X —                              |       | Unimplemented |       |         |         |             | —     | —     |                       |                                 |  |  |  |  |

|                                                 |        | — X                              | _     | _             | _     |         |         | RC6PPS<4:0> |       |       | 0 0000                | u uuuu                          |  |  |  |  |

| EA7h                                            | RC7PPS | X —                              |       |               |       | Unimple | emented |             |       |       | —                     | —                               |  |  |  |  |

|                                                 |        | — X                              | _     | _             | _     |         |         | RC7PPS<4:0> |       |       |                       |                                 |  |  |  |  |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

Only on PIC16F18326/18346. Note 1:

Register accessible from both User and ICD Debugger. 2:

# PIC16(L)F18326/18346

# 5.7 Register Definitions: Device and Revision

| REGISTER 5-5: | DE\      | ID: DEVICE ID | REGISTER |      |        |   |       |  |  |  |

|---------------|----------|---------------|----------|------|--------|---|-------|--|--|--|

|               |          | R             | R        | R    | R      | R | R     |  |  |  |

|               |          |               |          | DEV< | :13:8> |   |       |  |  |  |

|               |          | bit 13        |          |      |        |   | bit 8 |  |  |  |

|               |          |               |          |      |        |   |       |  |  |  |

| R             | R        | R             | R        | R    | R      | R | R     |  |  |  |

|               | DEV<7:0> |               |          |      |        |   |       |  |  |  |

| bit 7         |          |               |          |      |        |   | bit 0 |  |  |  |

|               |          |               |          |      |        |   |       |  |  |  |

# Legend:

R = Readable bit

'1' = Bit is set '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device       | DEVID<13:0> Values              |  |  |  |  |  |  |  |

|--------------|---------------------------------|--|--|--|--|--|--|--|

| PIC16F18326  | 11 0000 1010 0100 <b>(30A4)</b> |  |  |  |  |  |  |  |

| PIC16LF18326 | 11 0000 1010 0110 <b>(30A6)</b> |  |  |  |  |  |  |  |

| PIC16F18346  | 11 0000 1010 0101 <b>(30A5)</b> |  |  |  |  |  |  |  |

| PIC16LF18346 | 11 0000 1010 0111 <b>(30A7)</b> |  |  |  |  |  |  |  |

#### REGISTER 5-6: REVID: REVISION ID REGISTER

| R-1       | R-0 | R | R | R | R     |  |  |  |  |

|-----------|-----|---|---|---|-------|--|--|--|--|

| REV<13:8> |     |   |   |   |       |  |  |  |  |

| bit 13    |     |   |   |   | bit 8 |  |  |  |  |

| R       | R        | R | R | R | R | R | R |  |  |  |  |

|---------|----------|---|---|---|---|---|---|--|--|--|--|

|         | REV<7:0> |   |   |   |   |   |   |  |  |  |  |

| bit 7 b |          |   |   |   |   |   |   |  |  |  |  |

| Legend:          |                      |

|------------------|----------------------|

| R = Readable bit |                      |

| '1' = Bit is set | '0' = Bit is cleared |

bit 13-0 **REV<13:0>:** Revision ID bits

Note: The upper two bits of the Revision ID Register will always read '10'.

# 6.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- · Stack Overflow

- · Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

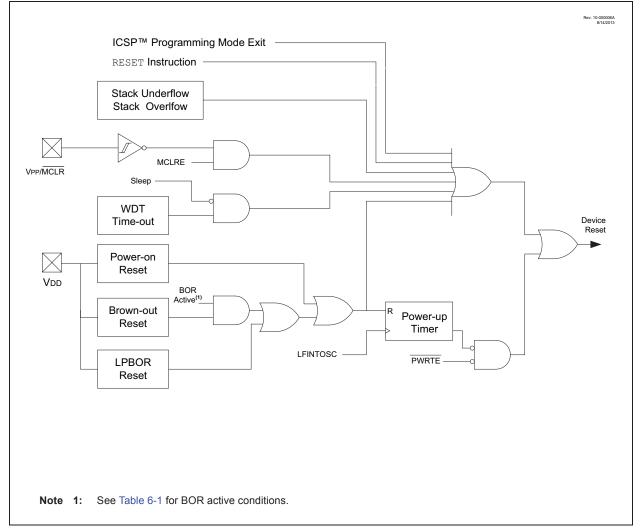

A simplified block diagram of the on-chip Reset circuit is shown in Figure 6-1.

## FIGURE 6-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 6.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

# 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset while VDD is below a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset, and the BOR bit of the PCON0 register will be cleared, indicating that a Brown-out Reset condition occurred. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode  | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep                                                                                                                                                                                                          |  |  |

|------------|--------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 11         | Х      | X            | Active   | In these specific cases, "Release of POR" and<br>"Wake-up from Sleep", there is no delay in start-up.<br>The BOR ready flag, (BORRDY = 1), will be set<br>before the CPU is ready to execute instructions<br>because the BOR circuit is forced on by the<br>BOREN<1:0> bits. |  |  |

| 1.0        | v      | Awake Active |          | Waits for release of BOR (BORRDY = 1)                                                                                                                                                                                                                                        |  |  |

| 10         | Х      | Sleep        | Disabled | BOR ignored when asleep                                                                                                                                                                                                                                                      |  |  |

| 01         | 1      | X            | Active   | In these specific cases, "Release of POR" and<br>"Wake-up from Sleep", there is no delay in start-up.<br>The BOR ready flag, (BORRDY = 1), will be set<br>before the CPU is ready to execute instructions<br>because the BOR circuit is forced on by the<br>BOREN<1:0> bits  |  |  |

|            | 0      | Х            | Disabled | Pagina immediately (POPPDV =)                                                                                                                                                                                                                                                |  |  |

| 0.0        | Х      | Х            | Disabled | Begins immediately (BORRDY = x)                                                                                                                                                                                                                                              |  |  |

TABLE 6-1: BOR OPERATING MODES

© 2016-2017 Microchip Technology Inc.

### 6.11 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |  |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|--|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |  |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |  |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR                                         |  |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |  |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |  |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |  |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |  |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during Normal Operation                                |  |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |  |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |  |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |  |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON0<br>Register |

|------------------------------------|-----------------------|--------------------|-------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x           |

| MCLR Reset during Normal Operation | 0000h                 | u uuuu             | uu Ouuu           |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu           |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu-0 uuuu         |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu-u uuuu         |

| Brown-out Reset                    | 0000h                 | 1 1000             | 00-1 11u0         |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu-u uuuu         |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu-u u0uu         |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu-u uuuu         |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul-u uuuu         |

**Legend:** u = unchanged, x = unknown, – = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# 7.5 Register Definitions: Oscillator Control

| REGISTER 7-1. OSCIONT. OSCIELATOR CONTROL REGISTER T |                        |                           |                        |                            |                        |                        |                        |  |  |

|------------------------------------------------------|------------------------|---------------------------|------------------------|----------------------------|------------------------|------------------------|------------------------|--|--|

| U-0                                                  | R/W-f/f <sup>(1)</sup> | R/W-f/f <sup>(1)</sup>    | R/W-f/f <sup>(1)</sup> | R/W-q/q <sup>(4)</sup>     | R/W-q/q <sup>(4)</sup> | R/W-q/q <sup>(4)</sup> | R/W-q/q <sup>(4)</sup> |  |  |

| —                                                    | 1                      | NOSC<2:0> <sup>(2,3</sup> | 3)                     | NDIV<3:0> <sup>(2,3)</sup> |                        |                        |                        |  |  |

| bit 7                                                |                        |                           |                        |                            |                        |                        | bit 0                  |  |  |

|                                                      |                        |                           |                        |                            |                        |                        |                        |  |  |

#### REGISTER 7-1: OSCCON1: OSCILLATOR CONTROL REGISTER 1

| Legend:                   |                      |                                                       |

|---------------------------|----------------------|-------------------------------------------------------|

| R = Readable bit          | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged      | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set          | '0' = Bit is cleared | f = determined by fuse setting                        |

| q = Reset value is determ | nined by hardware    |                                                       |

| bit 7 | <b>Unimplemented:</b> | Read as  | '0 |

|-------|-----------------------|----------|----|

|       | ommpicinicitica.      | ricuu us | 0  |

| bit 6-4 | NOSC<2:0>: New Oscillator Source Request bits                               |

|---------|-----------------------------------------------------------------------------|

|         | The setting requests a source oscillator and PLL combination per Table 7-1. |

|         | POR value = RSTOSC (Register 5-2).                                          |

|         |                                                                             |

- bit 3-0 NDIV<3:0>: New Divider Selection Request bits The setting determines the new postscaler division ratio per Table 7-2.

- **Note 1:** The default value (f/f) is set equal to the RSTOSC Configuration bits.

- 2: If NOSC is written with a reserved value (Table 7-1), the HFINTOSC will be automatically selected as the clock source.

- 3: When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

- 4: When RSTOSC = 110 (HFINTOSC 1 MHz) the NDIV bits will default to '0010' upon Reset; for all other NOSC settings, the NVID bits will default to '0000' upon Reset.

# REGISTER 7-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-q/q <sup>(1)</sup> |

|-------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| —     | COSC<2:0>            |                      | CDIV<3:0>            |                      |                      |                      |                      |

| bit 7 | t 7                  |                      |                      |                      |                      |                      | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Reset value is determined by hardware             |

bit 7Unimplemented: Read as '0'bit 6-4COSC<2:0>: Current Oscillator Source Select bits (read-only)<br/>Indicates the current source oscillator and PLL combination per Table 7-1.bit 3-0CDIV<3:0>: Current Divider Select bits (read-only)<br/>Indicates the current postscaler division ratio per Table 7-2.

**Note 1:** The Reset value (q/q) will match the NOSC<2:0>/NDIV<3:0> bits.

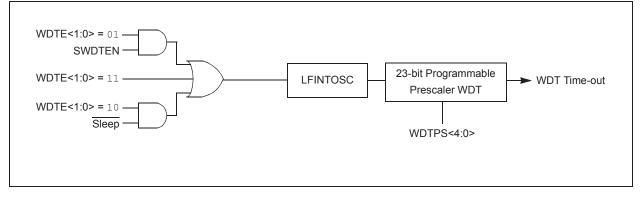

# 10.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- Independent clock source

- Multiple operating modes

- WDT is always ON

- WDT is OFF when in Sleep

- WDT is controlled by software

- WDT is always OFF

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple WDT clearing conditions

- Operation during Sleep

#### FIGURE 10-1: WATCHDOG TIMER BLOCK DIAGRAM

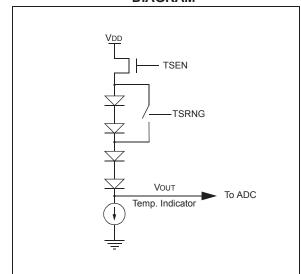

# 17.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between  $-40^{\circ}$ C and  $+85^{\circ}$ C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN2092, *"Using the Temperature Indicator Module"* (DS00002092) for more details regarding the calibration process.

# 17.1 Circuit Operation

Figure 17-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 17-1 describes the output characteristics of the temperature indicator.

# EQUATION 17-1: VOUT RANGES

*High Range: VOUT = VDD - 4VT*

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 16.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower VDD voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 17-1: TEMPERATURE CIRCUIT DIAGRAM

# 17.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 17-1 shows the recommended minimum VDD vs. range setting.

#### TABLE 17-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

# 17.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is provided for the temperature circuit output. Refer to **Section 22.0 "Analog-to-Digital Converter (ADC) Module"** for detailed information.

#### TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWMx

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4    | Bit 3   | Bit 2  | Bit 1       | Bit 0   | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------|----------|---------|--------|-------------|---------|---------------------|

| TRISA                 |                       |                       | TRISA5   | TRISA4   | (2)     | TRISA2 | TRISA1      | TRISA0  | 143                 |

| ANSELA                | _                     |                       | ANSA5    | ANSA4    | _       | ANSA2  | ANSA1       | ANSA0   | 144                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4   | _       | _      |             | _       | 149                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5    | ANSB4    | _       | _      | _           | _       | 150                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4   | TRISC3  | TRISC2 | TRISC1      | TRISC0  | 155                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5    | ANSC4    | ANSC3   | ANSC2  | ANSC1       | ANSC0   | 157                 |

| PWM5CON               | PWM5EN                | _                     | PWM5OUT  | PWM5POL  | _       | _      | _           | _       | 196                 |

| PWM5DCH               |                       |                       |          | PWM5DC<  | 9:2>    |        |             |         | 196                 |

| PWM5DCL               | PWM5                  | DC<1:0>               | —        | _        | _       | _      |             | _       | 196                 |

| PWM6CON               | PWM6EN                | _                     | PWM6OUT  | PWM6POL  | _       | _      | _           | _       | 196                 |

| PWM6DCH               |                       |                       |          | PWM6DC<  | 9:2>    |        |             |         | 196                 |

| PWM6DCL               | PWM6                  | DC<1:0>               | —        | _        | _       | —      | —           | _       | 196                 |

| PWMTMRS               | _                     | _                     | _        | _        | P6TSE   | L<1:0> | P5TSEL<1:0> |         | 197                 |

| INTCON                | GIE                   | PEIE                  | _        | _        | _       | _      | _           | INTEDG  | 100                 |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF     | TXIF     | SSP1IF  | BCL1IF | TMR2IF      | TMR1IF  | 107                 |

| PIR2                  | TMR6IF                | C2IF                  | C1IF     | NVMIF    | SSP2IF  | BCL2IF | TMR4IF      | NCO1IF  | 108                 |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE     | TXIE     | SSP1IE  | BCL1IE | TMR2IE      | TMR1IE  | 102                 |

| PIE2                  | TMR6IE                | C2IE                  | C1IE     | NVMIE    | SSP2IE  | BCL2IE | TMR4IE      | NCO1IE  | 103                 |

| T2CON                 | _                     |                       | T2OUTPS  | S<3:0>   |         | TMR2ON | T2CKP       | S<1:0>  | 298                 |

| T4CON                 | _                     |                       | T4OUTPS  | S<3:0>   |         | TMR4ON | T4CKP       | 'S<1:0> | 292                 |

| T6CON                 | _                     |                       | T6OUTPS  | S<3:0>   |         | TMR6ON | T6CKP       | 'S<1:0> | 292                 |

| TMR2                  |                       |                       |          | TMR2<7:0 | )>      |        |             |         | 299                 |

| TMR4                  |                       |                       |          | TMR4<7:( | )>      |        |             |         | 299                 |

| TMR6                  |                       |                       |          | TMR6<7:0 | )>      |        |             |         | 299                 |

| PR2                   |                       |                       |          | PR2<7:0  | >       |        |             |         | 299                 |

| PR4                   |                       |                       |          | PR4<7:0  | >       |        |             |         | 299                 |

| PR6                   |                       |                       |          | PR6<7:0  | >       |        |             |         | 299                 |

| CWGxDAT               |                       |                       | —        |          |         | DAT<   | <3:0>       |         | 215                 |

| CLCxSELy              | —                     | —                     |          | ·        | LCxDyS< | 5:0>   |             |         | 229                 |

| MDSRC                 |                       | _                     | _        |          |         | MDMS   | 3:0>        |         | 272                 |

| MDCARH                |                       | MDCHPOL               | MDCHSYNC |          |         | MDCH   | <3:0>       |         | 273                 |

| MDCARL                |                       | MDCLPOL               | MDCLSYNC | —        |         | MDCL   | <3:0>       |         | 274                 |

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by the PWM module.

Note 1: PIC16(L)F18346 only.

2: Unimplemented, read as '1'.

| R/W-x/u          | R/W-x/u      | R/W-x/u                                | R/W-x/u                                 | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |

|------------------|--------------|----------------------------------------|-----------------------------------------|----------------|------------------|------------------|-------------|--|

| LCxG4D4T         | LCxG4D4N     | LCxG4D3T                               | LCxG4D3N                                | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N    |  |

| bit 7            |              |                                        |                                         |                |                  |                  | bit 0       |  |

|                  |              |                                        |                                         |                |                  |                  |             |  |

| Legend:          |              |                                        |                                         |                |                  |                  |             |  |

| R = Readable     |              | W = Writable                           |                                         |                | nented bit, read |                  |             |  |

| u = Bit is unch  | anged        | x = Bit is unkr                        |                                         | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |

| '1' = Bit is set |              | '0' = Bit is clea                      | ared                                    |                |                  |                  |             |  |

|                  |              |                                        | _ , .                                   | 6 N.1.4        |                  |                  |             |  |

| bit 7            |              | Gate 3 Data 4 1                        |                                         | ,              |                  |                  |             |  |

|                  |              | (true) is gated i<br>(true) is not gat |                                         |                |                  |                  |             |  |

| bit 6            |              | Gate 3 Data 4 I                        |                                         |                |                  |                  |             |  |

| bit o            |              | (inverted) is ga                       | •                                       | ,              |                  |                  |             |  |

|                  |              | · · · ·                                | inverted) is not gated into CLCx Gate 3 |                |                  |                  |             |  |

| bit 5            | LCxG4D3T: 0  | Gate 3 Data 3 1                        | rue (non-inve                           | rted) bit      |                  |                  |             |  |

|                  |              | (true) is gated i                      |                                         |                |                  |                  |             |  |

|                  |              | (true) is not gat                      |                                         |                |                  |                  |             |  |

| bit 4            |              | Gate 3 Data 3                          | •                                       |                |                  |                  |             |  |

|                  |              | (inverted) is ga<br>(inverted) is no   |                                         |                |                  |                  |             |  |

| bit 3            | LCxG4D2T:    | Gate 3 Data 2 1                        | rue (non-inve                           | rted) bit      |                  |                  |             |  |

|                  | 1 = CLCIN1 ( | (true) is gated i                      | nto CLCx Gat                            | e 3            |                  |                  |             |  |

|                  | 0 = CLCIN1 ( | (true) is not gat                      | ed into CLCx                            | Gate 3         |                  |                  |             |  |

| bit 2            | LCxG4D2N:    | Gate 3 Data 2 I                        | Negated (inve                           | rted) bit      |                  |                  |             |  |

|                  |              | (inverted) is ga                       |                                         |                |                  |                  |             |  |

|                  |              | (inverted) is no                       | •                                       |                |                  |                  |             |  |

| bit 1            |              | Gate 3 Data 1 1                        |                                         | ,              |                  |                  |             |  |

|                  |              | (true) is gated i<br>(true) is not gat |                                         |                |                  |                  |             |  |

| bit 0            |              | Gate 3 Data 1 I                        |                                         |                |                  |                  |             |  |

|                  |              | (inverted) is ga                       | •                                       | ,              |                  |                  |             |  |

|                  |              | (inverted) is no                       |                                         |                |                  |                  |             |  |

# REGISTER 21-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

# 22.2 ADC Operation

#### 22.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit will not be set in the  |

|-------|-----------------------------------------|

|       | same instruction that turns on the ADC. |

|       | Refer to Section 22.2.5 "ADC Conver-    |

|       | sion Procedure".                        |

#### 22.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

#### 22.2.3 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the ADCRC option. When the ADCRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than ADCRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 22.2.4 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The Auto-conversion Trigger source is selected with the ADACT<4:0> bits of the ADACT register.

See Table 22-2 for auto-conversion sources.

| <b>TABLE 22-2:</b> | ADC AUTO-CONVERSIO |  |  |

|--------------------|--------------------|--|--|

|                    | TABLE              |  |  |

| Source<br>Peripheral | Description                  |

|----------------------|------------------------------|

| TMR0                 | Timer0 Overflow condition    |

| TMR1                 | Timer1 Overflow condition    |

| TMR3                 | Timer3 Overflow condition    |

| TMR5                 | Timer5 Overflow condition    |

| TMR2                 | Match between Timer2 and PR2 |

| TMR4                 | Match between Timer4 and PR4 |

| TMR6                 | Match between Timer6 and PR6 |

| C1                   | Comparator C1 output         |

| C2                   | Comparator C2 output         |

| CLC1                 | CLC1 output                  |

| CLC2                 | CLC2 output                  |

| CLC3                 | CLC3 output                  |

| CLC4                 | CLC4 output                  |

| CCP1                 | CCP1 output                  |

| CCP2                 | CCP2 output                  |

| CCP3                 | CCP3 output                  |

| CCP4                 | CCP4 output                  |

| R/W-0/0         | R/W-0/0                                              | R/W-0/0                                                                       | R/W-0/0                        | U-0            | R/W-0/0          | R/W-0/0             | R/W-0/0      |

|-----------------|------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------|----------------|------------------|---------------------|--------------|

| ADFM            |                                                      | ADCS<2:0>                                                                     |                                | —              | ADNREF           | ADPRE               | EF<1:0>      |

| bit 7           | •                                                    |                                                                               |                                |                |                  |                     | bit          |

| Levendu         |                                                      |                                                                               |                                |                |                  |                     |              |

| Legend:         | . 1.10                                               |                                                                               |                                |                |                  |                     |              |

| R = Readable    |                                                      | W = Writable b                                                                |                                |                | mented bit, read |                     |              |

| u = Bit is unc  | •                                                    | x = Bit is unkn                                                               |                                | -n/n = value   | at POR and BO    | R/value at all      | other Resets |

| '1' = Bit is se | t                                                    | '0' = Bit is clea                                                             | ired                           |                |                  |                     |              |

| bit 7           | 1 = Right ju<br>loaded.                              | Result Format S<br>stified. Six Most<br>tified. Six Least                     | Significant bi                 |                |                  |                     |              |

| bit 6-4         | 111 = ADCI<br>110 = Fosc<br>101 = Fosc<br>100 = Fosc | /16<br>/4<br>RC (dedicated R <sup>i</sup><br>/32<br>/8                        | C oscillator)                  | ct bits        |                  |                     |              |

| bit 3           | Unimpleme                                            | nted: Read as '0                                                              | )'                             |                |                  |                     |              |

| bit 2           | When ADO<br>0 = VREF- is                             | /D Negative Volta<br>N = 0, all multiple<br>connected to A<br>connected to ex | exer inputs an<br>/ss          | •              |                  |                     |              |

| bit 1-0         | 11 = VREF+                                           |                                                                               | nternal Fixed<br>external VREF | Voltage Refere |                  | lule <sup>(1)</sup> |              |

#### REGISTER 22-2: ADCON1: ADC CONTROL REGISTER 1

**Note 1:** When selecting the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See Table 35-13 for details.

| R/W-0/             | 0 R/W-0/0                                                                                 | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                    | U-0                                                                                               | U-0              | R/W-0/0          | R/W-0/0      |

|--------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------|------------------|--------------|

|                    | N1PWS<2:0>                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |                                                                                                   | _                | N1CKS<1:0>       |              |

| bit 7              |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |                                                                                                   |                  |                  | bit (        |

| Legend:            |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |                                                                                                   |                  |                  |              |

| R = Read           | able bit                                                                                  | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | oit                                                                                                    | U = Unimplen                                                                                      | nented bit, read | d as '0'         |              |

| u = Bit is u       | unchanged                                                                                 | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | own                                                                                                    | -n/n = Value a                                                                                    | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is       | set                                                                                       | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | red                                                                                                    |                                                                                                   |                  |                  |              |

| bit 4-2            | 101 = NCO<br>100 = NCO<br>011 = NCO<br>010 = NCO<br>001 = NCO<br>000 = NCO                | 1 output is active<br>1 outp | e for 32 input<br>e for 16 input<br>e for 8 input<br>e for 4 input<br>e for 2 input<br>e for 1 input o | clock periods<br>clock periods<br>clock periods<br>clock periods<br>clock periods<br>clock period |                  |                  |              |

| bit 1-0<br>Note 1: | N1CKS<1:0><br>11 =Reserved<br>10 = CLC10U<br>01 = Fosc<br>00 = HFINTO<br>N1PWS applies of | JT<br>PSC (16 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |                                                                                                   | le               |                  |              |

|                    | If NCO1 pulse wi                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |                                                                                                   |                  |                  |              |

# REGISTER 23-2: NCO1CLK: NCO1 INPUT CLOCK CONTROL REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | NCO1A   | ACC<7:0>       |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable I    | oit     | U = Unimplen   | nented bit, read | d as '0'         |              |

| u = Bit is unch  | nanged  | x = Bit is unkn   | own     | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 NCO1ACC<7:0>: NCO1 Accumulator, low byte

# 29.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains four standard Capture/Compare/PWM modules (CCP1, CCP2, CCP3 and CCP4).

The Capture and Compare functions are identical for all CCP modules.

# 29.1 CCP/PWM Clock Selection

The PIC16(L)F18326/18346 devices allow each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

As there are up to three 8-bit timers with auto-reload (Timer2, Timer4, and Timer6), PWM mode on the CCP and PWM modules can use any of these timers.

The CCPTMRS register is used to select which timer is used.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

# 29.2 Capture Mode

Capture mode makes use of either the 16-bit Timer0 or Timer1 resource. When an event occurs on the capture source, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR0H:TMR0L or TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxMODE<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIR4 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 29-1 shows a simplified diagram of the capture operation.

#### 29.2.1 CAPTURE SOURCES

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a Capture condition.

The capture source is selected by configuring the CCPxCTS<3:0> bits of the CCPxCAP register. The following sources can be selected:

- · CCPxPPS input

- C1 output

- C2\_output

- NCO\_output

- IOC\_interrupt

- LC1\_output

- LC2\_output

- LC3\_output

- LC4\_output

# 31.6 Register Definitions: EUSART1 Control

| R/W-0/0          | R/W-0/0                                                              | R/W-0/0                                               | R/W-0/0                                            | R/W-0/0        | R/W-0/0          | R-1/1            | R/W-0/0      |

|------------------|----------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|----------------|------------------|------------------|--------------|

| CSRC             | TX9                                                                  | TXEN <sup>(1)</sup>                                   | SYNC                                               | SENDB          | BRGH             | TRMT             | TX9D         |

| bit 7            |                                                                      | •                                                     |                                                    |                |                  |                  | bit (        |

| Legend:          |                                                                      |                                                       |                                                    |                |                  |                  |              |