Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18326t-i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC16(L)F183XX MICROCONTROLLERS

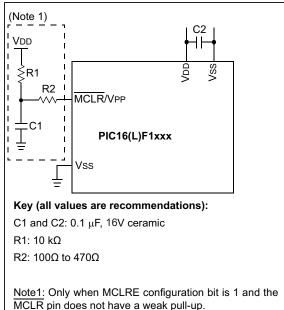

#### 2.1 Basic Connection Requirements

Getting started with the PIC16(L)F183XX family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and VSS pins

(see Section 2.2 "Power Supply Pins")

- MCLR pin (when configured for external operation)

(see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- ICSPCLK/ICSPDAT pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.4 "ICSP<sup>™</sup> Pins")

- OSC1 and OSC2 pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

The minimum mandatory connections are shown in Figure 2-1.

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins (VDD and Vss) is required. All VDD and Vss pins must be connected. None can be left floating.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-25V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

#### 7.2.2.3 Internal Oscillator Frequency Adjustment

The HFINTOSC and LFINTOSC internal oscillators are both factory-calibrated. TH HFINTOSC oscillator can be adjusted in software by writing to the OSCTUNE register (Register 7-3). OSCTUNE does not affect the LFINTOSC frequency.

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the HFINTOSC oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

## 7.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory-calibrated 31 kHz internal clock source.

The LFINTOSC is the clock source for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM). The LFINTOSC can also be used as the system clock, or as a clock or input source to certain peripherals.

The LFINTOSC is selected as the clock source through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register.

#### 7.2.2.5 Oscillator Status and Manual Enable

The 'ready' status of each oscillator is displayed in the OSCSTAT1 register (Register 7-4). The oscillators can also be manually enabled through the OSCEN register (Register 7-5). Manual enables make it possible to verify the operation of the EXTOSC or SOSC crystal oscillators. This can be achieved by enabling the selected oscillator, then watching the corresponding 'ready' state of the oscillator in the OSCSTAT1 register.

| U-0              | U-0           | R/W/HS-0/0                              | R-0                  | U-0             | U-0              | U-0             | R/W/HS-0/0   |

|------------------|---------------|-----------------------------------------|----------------------|-----------------|------------------|-----------------|--------------|

| _                | —             | TMR0IF                                  | IOCIF <sup>(1)</sup> | —               | —                | —               | INTF         |

| bit 7            |               |                                         |                      |                 | ·                |                 | bit 0        |

| Legend:          |               |                                         |                      |                 |                  |                 |              |

| R = Readable     | bit           | W = Writable I                          | bit                  | U = Unimpler    | mented bit, read | as '0'          |              |

| u = Bit is uncha | anged         | x = Bit is unkn                         | own                  | -n/n = Value    | at POR and BO    | R/Value at all  | other Resets |

| '1' = Bit is set |               | '0' = Bit is clea                       | ared                 | HS= Hardwa      | re Set           |                 |              |

|                  |               |                                         |                      |                 |                  |                 |              |

| bit 7-6          | Unimpleme     | nted: Read as '                         | )'                   |                 |                  |                 |              |

| bit 5            |               | IR0 Overflow Int                        | 1 0                  |                 |                  |                 |              |

|                  |               | register has over<br>register did not o |                      | t be cleared in | software)        |                 |              |

| bit 4            |               | upt-on-Change                           |                      | bit (road only) | N N              |                 |              |

| DIL 4            |               | bled edge was c                         |                      |                 |                  | CF bits is set. |              |

|                  |               | bled edge is wa                         |                      |                 |                  |                 | et.          |

|                  | Pins are indi | vidually masked                         | via IOCxP ar         | nd IOCxN.       |                  |                 |              |

| bit 3-1          | Unimpleme     | nted: Read as '                         | )'                   |                 |                  |                 |              |

| bit 0            |               | xternal Interrupt                       | •                    |                 |                  |                 |              |

|                  |               | T external interru                      |                      |                 | ed in software)  |                 |              |

| Note 4. The      |               | T external interru                      | •                    |                 | Therefore to a   | lear the IOCIE  | flog         |

|                  |               | he logical OR of<br>are must clear al   |                      | •               |                  |                 | nay,         |

| upp              |               |                                         |                      |                 |                  |                 |              |

|                  |               |                                         |                      |                 |                  |                 |              |

#### REGISTER 8-7: PIR0: PERIPHERAL INTERRUPT REQUEST REGISTER 0

| Note: | Interrupt flag bits are set when an interrupt<br>condition occurs, regardless of the state of |  |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | its corresponding enable bit or the Global                                                    |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.                                                      |  |  |  |  |  |  |  |

|       | User software should ensure the                                                               |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear                                                     |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.                                                               |  |  |  |  |  |  |  |

© 2016-2017 Microchip Technology Inc

Preliminary

## 15.6 Register Definitions: Interrupt-on-Change Control

| U-0              | U-0                                   | R/W-0/0           | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------|---------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

|                  | —                                     | IOCAP5            | IOCAP4                                                | IOCAP3                             | IOCAP2  | IOCAP1  | IOCAP0  |  |

| bit 7            | •                                     |                   |                                                       |                                    |         | •       | bit 0   |  |

|                  |                                       |                   |                                                       |                                    |         |         |         |  |

| Legend:          |                                       |                   |                                                       |                                    |         |         |         |  |

| R = Readable b   | oit                                   | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is uncha | = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set |                                       | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

#### REGISTER 15-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCAP<5:0>:** Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-change disabled for the associated pin

#### REGISTER 15-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0              | U-0                                                                           | R/W-0/0           | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------|-------------------------------------------------------------------------------|-------------------|---------|------------------------------------|---------|---------|---------|--|

|                  |                                                                               | IOCAN5            | IOCAN4  | IOCAN3                             | IOCAN2  | IOCAN1  | IOCAN0  |  |

| bit 7            | -                                                                             | -                 |         |                                    |         |         | bit 0   |  |

|                  |                                                                               |                   |         |                                    |         |         |         |  |

| Legend:          |                                                                               |                   |         |                                    |         |         |         |  |

| R = Readable     | bit                                                                           | W = Writable      | bit     | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is uncha | it is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |                   |         | ther Resets                        |         |         |         |  |

| '1' = Bit is set |                                                                               | '0' = Bit is clea | ared    |                                    |         |         |         |  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

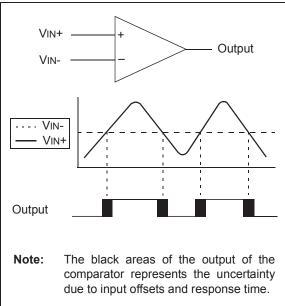

# 18.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Programmable input selection

- Selectable voltage reference

- Programmable output polarity

- Rising/falling output edge interrupts

- · Wake-up from Sleep

- CWG Auto-shutdown source

#### 18.1 Comparator Overview

A single comparator is shown in Figure 18-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 18-1.

#### TABLE 18-1: AVAILABLE COMPARATORS

| Device         | C1 | C2 |

|----------------|----|----|

| PIC16(L)F18326 | •  | •  |

| PIC16(L)F18346 | ٠  | •  |

#### FIGURE 18-1:

SINGLE COMPARATOR

## 18.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- Interrupt on positive/negative edge enables

- Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 13-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 18.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-2 shows the output state versus input conditions, including polarity control.

#### TABLE 18-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 18.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 35-14 for more information.

## 18.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 27.5 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 18.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

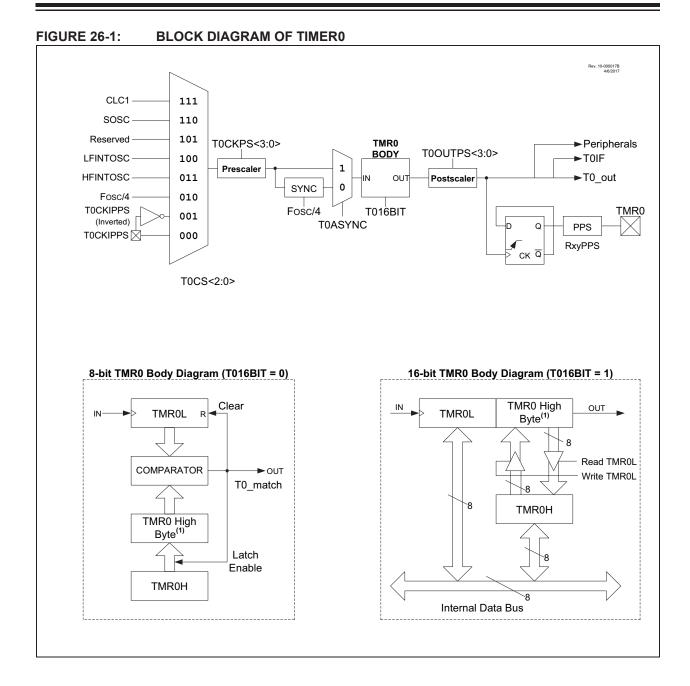

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. This allows the timer/counter to synchronize with the CxOUT bit so that the software sees no ambiguity due to timing. See the Comparator Block Diagram (Figure 18-2) and the Timer1 Block Diagram (Figure 27-1) for more information.

| Name                  | Bit 7                 | Bit 6                 | Bit 5     | Bit 4  | Bit 3   | Bit 2    | Bit 1   | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|-----------|--------|---------|----------|---------|--------|---------------------|

| INTCON                | GIE                   | PEIE                  |           | —      | —       | —        |         | INTEDG | 100                 |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE      | TXIE   | SSP1IE  | BCL1IE   | TMR2IE  | TMR1IE | 102                 |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF      | TXIF   | SSP1IF  | BCL1IF   | TMR2IF  | TMR1IF | 107                 |

| TRISA                 | —                     | —                     | TRISA5    | TRISA4 | (2)     | TRISA2   | TRISA1  | TRISA0 | 143                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5    | TRISB4 | —       | —        | _       | _      | 149                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5    | TRISC4 | TRISC3  | TRISC2   | TRISC1  | TRISC0 | 155                 |

| ANSELA                | —                     | —                     | ANSA5     | ANSA4  |         | ANSA2    | ANSA1   | ANSA0  | 144                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5     | ANSB4  |         | _        | _       |        | 150                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5     | ANSC4  | ANSC3   | ANSC2    | ANSC1   | ANSC0  | 157                 |

| ADCON0                |                       |                       | CHS<      | 5:0>   |         |          | GO/DONE | ADON   | 244                 |

| ADCON1                | ADFM                  | A                     | ADCS<2:0> | •      |         | ADNREF   | ADPRE   | F<1:0> | 245                 |

| ADACT                 | —                     | —                     |           |        |         | ADACT<4: | )>      |        | 246                 |

| ADRESH                |                       |                       |           | ADRES  | SH<7:0> |          |         |        | 247                 |

| ADRESL                |                       |                       |           | ADRES  | SL<7:0> |          |         |        | 247                 |

| FVRCON                | FVREN                 | FVRRDY                | TSEN      | TSRNG  |         |          |         |        |                     |

| DAC1CON1              | —                     | —                     |           |        |         | DAC1R<4: | 0>      |        | 264                 |

| OSCSTAT1              | EXTOR                 | HFOR                  |           | LFOR   | SOR     | ADOR     | _       | PLLR   | 91                  |

#### TABLE 22-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** -= unimplemented read as '0'. Shaded cells are not used for the ADC module.

**Note 1:** PIC16(L)F18346 only.

**2:** Unimplemented, read as '1'.

| R/W-0/0          | R/W-0/0 | R/W-0/0                                                 | R/W-0/0 | R/W-0/0                                            | R/W-0/0 | R/W-0/0 | R/W-0/0      |

|------------------|---------|---------------------------------------------------------|---------|----------------------------------------------------|---------|---------|--------------|

|                  |         |                                                         | NCO1I   | NC<15:8>                                           |         |         |              |

| bit 7            |         |                                                         |         |                                                    |         |         | bit 0        |

|                  |         |                                                         |         |                                                    |         |         |              |

| Legend:          |         |                                                         |         |                                                    |         |         |              |

| R = Readable     | bit     | bit W = Writable bit U = Unimplemented bit, read as '0' |         |                                                    |         |         |              |

| u = Bit is unch  | anged   | x = Bit is unkno                                        | own     | -n/n = Value at POR and BOR/Value at all other Res |         |         | other Resets |

| '1' = Bit is set |         | '0' = Bit is clear                                      | red     |                                                    |         |         |              |

# **REGISTER 23-7:** NCO1INCH<sup>(1)</sup>: NCO1 INCREMENT REGISTER – HIGH BYTE

bit 7-0 NCO1INC<15:8>: NCO1 Increment, high byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

# **REGISTER 23-8:** NCO1INCU<sup>(1)</sup>: NCO1 INCREMENT REGISTER – UPPER BYTE

|       |     |     | • • • • • • • • • • • • • • • • • • • • |                |         |         |         |  |

|-------|-----|-----|-----------------------------------------|----------------|---------|---------|---------|--|

| U-0   | U-0 | U-0 | U-0                                     | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

| —     | —   | —   | —                                       | NCO1INC<19:16> |         |         |         |  |

| bit 7 |     |     |                                         |                |         |         | bit 0   |  |

# Legend:

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1INC<19:16>: NCO1 Increment, upper byte

**Note 1:** The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

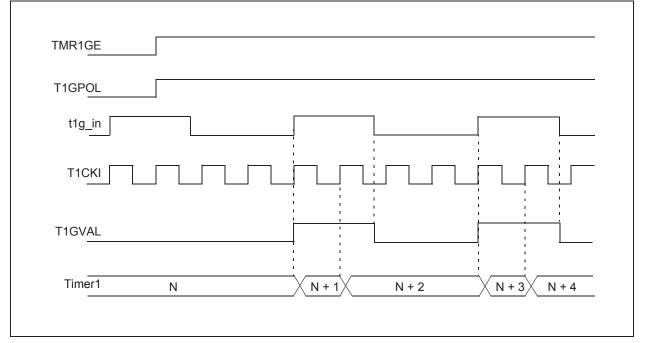

## FIGURE 27-3: TIMER1 GATE ENABLE MODE

# **REGISTER 27-3:** TMRxL<sup>(1)</sup>: TIMERx LOW BYTE REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                              | R/W-x/u          | R/W-x/u  | R/W-x/u |  |

|------------------|---------|-------------------|---------|------------------------------------------------------|------------------|----------|---------|--|

|                  |         |                   | TMRx    | L<7:0>                                               |                  |          |         |  |

| bit 7            |         |                   |         |                                                      |                  |          | bit 0   |  |

|                  |         |                   |         |                                                      |                  |          |         |  |

| Legend:          |         |                   |         |                                                      |                  |          |         |  |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler                                         | nented bit, read | d as '0' |         |  |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | n -n/n = Value at POR and BOR/Value at all other Res |                  |          |         |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                      |                  |          |         |  |

bit 7-0 TMRxL<7:0>: TMRx Low Byte bits

Note 1: 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

# REGISTER 27-4: TMRxH<sup>(1)</sup>: TIMERx HIGH BYTE REGISTER

| bit 7   |         |         |         |         |         |         | bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | TMRxH   | 1<7:0>  |         |         |         |

| R/W-x/u |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>: TMRx High Byte bits

**Note 1:** 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

#### EQUATION 29-2: PULSE WIDTH

| Pulse Width = | (CCPRxH: | CCPRxL register pair) • |

|---------------|----------|-------------------------|

|               | Tora     | (TMD) Duran la Valua)   |

TOSC • (TMR2 Prescale Value)

## EQUATION 29-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$

The CCPRxH:CCPRxL register pair and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering provides glitchless PWM operation.

The 8-bit timer TMR2/4/6 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 29-4).

### 29.4.6 PWM RESOLUTION

PWM resolution, expressed in number of bits, defines the maximum number of discrete steps that can be present in a single PWM period. For example, a 10-bit resolution will result in 1024 discrete steps, whereas an 8-bit resolution will result in 256 discrete steps.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 29-4.

## EQUATION 29-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| IABLE 29-1: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|-------------|---------------------------------------------------------|

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 29-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 29.4.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2/4/6 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2/4/6 will continue from its previous state.

#### 29.4.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 7.0 "Oscillator Module"** for additional details.

#### 29.4.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

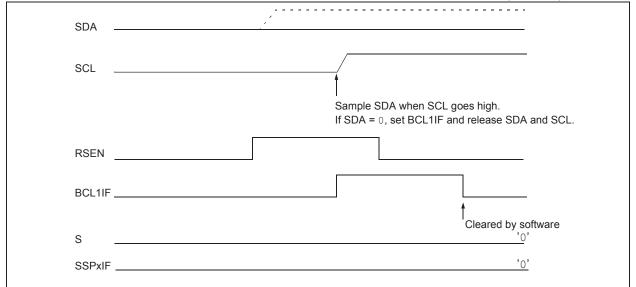

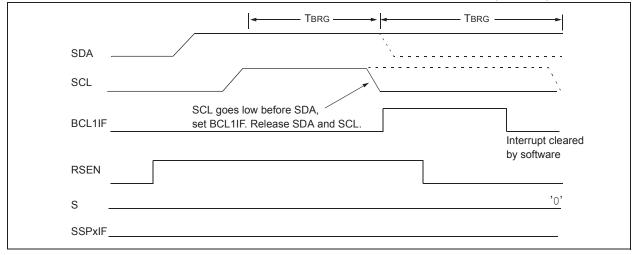

# 30.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 30-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 30-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 30-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 30-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

| R/C/HS-0/0       | R/C/HS-0/0                                                                                                                                                                                                         | R/W-0/0                               | R/W-0/0                     | R/W-0/0              | R/W-0/0            | R/W-0/0          | R/W-0/0      |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|----------------------|--------------------|------------------|--------------|--|

| WCOL             | SSPOV <sup>(1)</sup>                                                                                                                                                                                               | SSPEN                                 | CKP                         |                      | SSPM               | <3:0>            |              |  |

| bit 7            | •                                                                                                                                                                                                                  | •                                     | •                           | •                    |                    |                  | bit          |  |

|                  |                                                                                                                                                                                                                    |                                       |                             |                      |                    |                  |              |  |

| Legend:          |                                                                                                                                                                                                                    |                                       |                             |                      |                    |                  |              |  |

| R = Readable     | bit                                                                                                                                                                                                                | W = Writable                          | bit                         | U = Unimplen         | nented bit, read   | as '0'           |              |  |

| u = Bit is unch  | anged                                                                                                                                                                                                              | x = Bit is unki                       | nown                        | -n/n = Value a       | at POR and BO      | R/Value at all o | ther Resets  |  |

| '1' = Bit is set |                                                                                                                                                                                                                    | '0' = Bit is cle                      | ared                        | HS = Bit is se       | t by hardware      | C = User clea    | red          |  |

|                  |                                                                                                                                                                                                                    |                                       |                             |                      |                    |                  |              |  |

| bit 7            |                                                                                                                                                                                                                    | Collision Dete                        |                             |                      |                    |                  |              |  |

|                  | 1 = The SPP<br>software)                                                                                                                                                                                           | •                                     | is written while            | e it is still transr | nitting the previo | ous word (mus    | t be cleared |  |

|                  | 0 = No collisi                                                                                                                                                                                                     |                                       |                             |                      |                    |                  |              |  |

| bit 6            | SSPOV: Rece                                                                                                                                                                                                        | eive Overflow I                       | ndicator bit <sup>(1)</sup> |                      |                    |                  |              |  |

|                  | In SPI mode:                                                                                                                                                                                                       |                                       |                             |                      |                    |                  |              |  |

|                  | 1 = A new byte is received while the SPPxBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. In Slave mode, the user must read |                                       |                             |                      |                    |                  |              |  |

|                  |                                                                                                                                                                                                                    |                                       |                             |                      | tting overflow. In |                  |              |  |

|                  |                                                                                                                                                                                                                    |                                       |                             |                      | is initiated by wr |                  |              |  |

|                  | •                                                                                                                                                                                                                  | cleared in softw                      | /are).                      |                      |                    |                  | · ·          |  |

|                  | 0 = No overfl                                                                                                                                                                                                      | low                                   |                             |                      |                    |                  |              |  |

|                  | $\frac{\ln l^2 C \mod e}{1 = A \text{ byte is}}$                                                                                                                                                                   | received while                        | the SPPxBUF                 | reaister is still    | holding the prev   | vious byte. SSF  | POV is a "do |  |

|                  |                                                                                                                                                                                                                    |                                       |                             | red in software      |                    |                  |              |  |

|                  | 0 = No overfl                                                                                                                                                                                                      | low                                   |                             |                      |                    |                  |              |  |

| bit 5            |                                                                                                                                                                                                                    | chronous Seria                        |                             |                      |                    |                  |              |  |

|                  | In both modes, when enabled, the following pins must be properly configured as input or output<br>In SPI mode:                                                                                                     |                                       |                             |                      |                    |                  |              |  |

|                  | $\overline{1}$ = Enables serial port and configures SCK, SDO, SDI and $\overline{SS}$ as the source of the serial port pins <sup>(2)</sup>                                                                         |                                       |                             |                      |                    |                  |              |  |

|                  | 0 = Disables serial port and configures these pins as I/O port pins                                                                                                                                                |                                       |                             |                      |                    |                  |              |  |

|                  | $\frac{\ln l^2 C}{1}$ mode:<br>1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins <sup>(3)</sup>                                                                |                                       |                             |                      |                    |                  |              |  |

|                  |                                                                                                                                                                                                                    |                                       |                             | ese pins as I/O      |                    |                  | P - P -      |  |

| bit 4            | CKP: Clock F                                                                                                                                                                                                       | Polarity Select I                     | oit                         |                      |                    |                  |              |  |

|                  | In SPI mode:                                                                                                                                                                                                       | for electric o b                      | inh loval                   |                      |                    |                  |              |  |

|                  |                                                                                                                                                                                                                    | for clock is a h<br>for clock is a lo | -                           |                      |                    |                  |              |  |

|                  | In I <sup>2</sup> C Slave r                                                                                                                                                                                        |                                       |                             |                      |                    |                  |              |  |

|                  | SCL release                                                                                                                                                                                                        |                                       |                             |                      |                    |                  |              |  |

|                  | 1 = Enable clo<br>0 = Holds clo                                                                                                                                                                                    |                                       | tratch) (Llsad              | to onsuro data       | setun time )       |                  |              |  |

|                  |                                                                                                                                                                                                                    |                                       |                             |                      |                    |                  |              |  |

|                  | In I <sup>2</sup> C Master<br>Unused in this                                                                                                                                                                       | mode:                                 |                             | to ensure data       | setup time.)       |                  |              |  |

# 35.2 Standard Operating Conditions

| The standard operating conditions for any device are defined as: |

|------------------------------------------------------------------|

| Operating Voltage: $VDDMIN \le VDD \le VDDMAX$                   |

| Operating Temperature: $TA\_MIN \le TA \le TA\_MAX$              |

| VDD — Operating Supply Voltage <sup>(1)</sup>                    |

| PIC16LF18326/18346                                               |

| VDDMIN (Fosc $\leq$ 16 MHz) +1.8V                                |

| VDDMIN (Fosc $\leq$ 32 MHz)                                      |

| VDDMAX                                                           |

| PIC16F18326/18346                                                |

| VDDMIN (Fosc ≤ 16 MHz)+2.3V                                      |

| VDDMIN (Fosc $\leq$ 32 MHz) +2.5V                                |

| VDDMAX                                                           |

| TA — Operating Ambient Temperature Range                         |

| Industrial Temperature                                           |

| TA_MIN                                                           |

| TA_MAX                                                           |

| Extended Temperature                                             |

| TA_MIN                                                           |

| TA_MAX                                                           |

| Note 1: See Parameter D002, DC Characteristics: Supply Voltage.  |

|                                                                  |

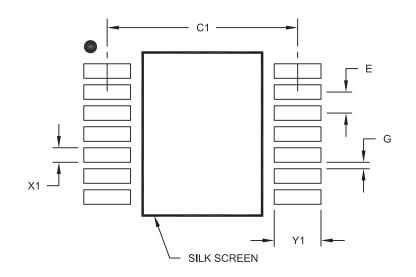

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units            |          |      |      |

|--------------------------|------------------|----------|------|------|

| Dimensior                | Dimension Limits |          |      | MAX  |

| Contact Pitch            | E                | 0.65 BSC |      |      |

| Contact Pad Spacing      | C1               |          | 5.90 |      |

| Contact Pad Width (X14)  | X1               |          |      | 0.45 |

| Contact Pad Length (X14) | Y1               |          |      | 1.45 |

| Distance Between Pads    | G                | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

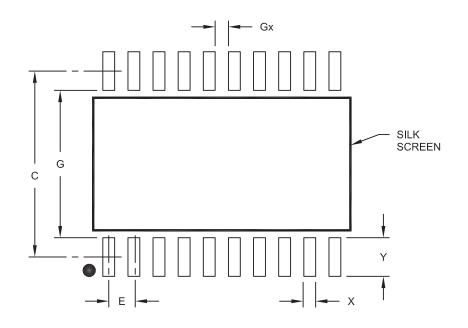

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units            |          |      | S    |  |

|--------------------------|------------------|----------|------|------|--|

| Dimension                | Dimension Limits |          |      | MAX  |  |

| Contact Pitch            | E                | 1.27 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 9.40 |      |  |

| Contact Pad Width (X20)  | Х                |          |      | 0.60 |  |

| Contact Pad Length (X20) | Y                |          |      | 1.95 |  |

| Distance Between Pads    | Gx               | 0.67     |      |      |  |

| Distance Between Pads    | G                | 7.45     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A

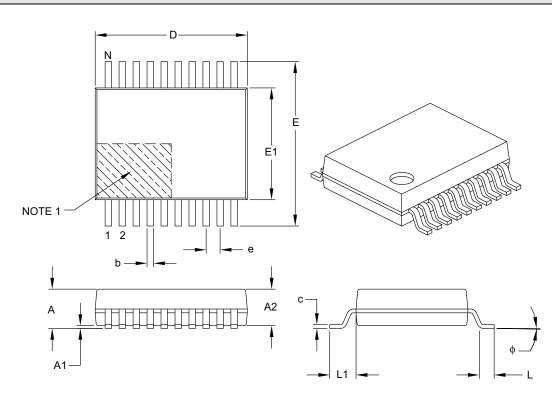

## 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS | 6    |

|--------------------------|------------------|----------|-------------|------|

| Dimensior                | Dimension Limits |          |             | MAX  |

| Number of Pins           | N                |          | 20          |      |

| Pitch                    | е                |          | 0.65 BSC    |      |

| Overall Height           | Α                | -        | -           | 2.00 |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85 |

| Standoff                 | A1               | 0.05     | -           | -    |

| Overall Width            | E                | 7.40     | 7.80        | 8.20 |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60 |

| Overall Length           | D                | 6.90     | 7.20        | 7.50 |

| Foot Length              | L                | 0.55     | 0.75        | 0.95 |

| Footprint                | L1               | 1.25 REF |             |      |

| Lead Thickness           | с                | 0.09     | -           | 0.25 |

| Foot Angle               | ¢                | 0°       | 4°          | 8°   |

| Lead Width               | b                | 0.22     | -           | 0.38 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B