# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

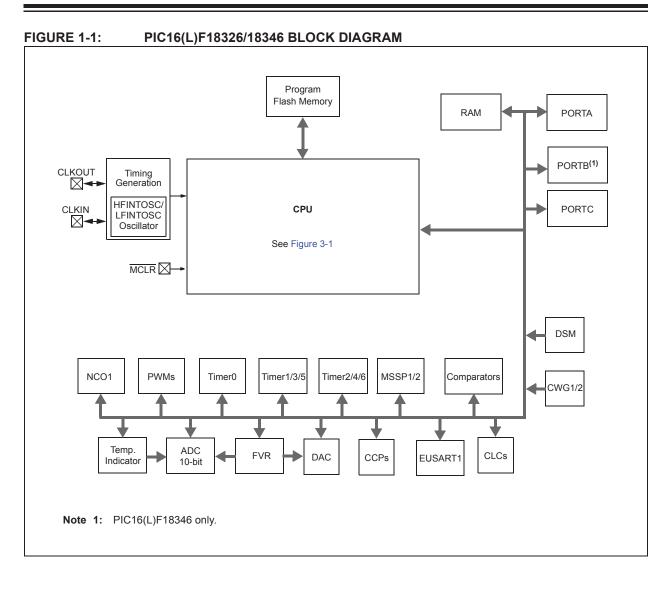

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18346-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F18326/18346

| TABLE 4-4: | SPECIAL FUNCTION RE | EGISTER SUMMARY B | ANKS 0-31 ( | CONTINUE | )) |  |

|------------|---------------------|-------------------|-------------|----------|----|--|

|            |                     |                   |             |          |    |  |

| Address         | Name    | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7  | Bit 6  | Bit 5       | Bit 4           | Bit 3             | Bit 2      | Bit 1      | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------|---------|----------------------------------|--------|--------|-------------|-----------------|-------------------|------------|------------|---------|-----------------------|---------------------------------|

| Bank 2          |         |                                  |        |        |             |                 |                   |            |            |         |                       |                                 |

|                 |         |                                  |        |        | CPU CORE RE | EGISTERS; see 1 | Table 4-2 for spe | cifics     |            |         |                       |                                 |

| 10Ch            | LATA    |                                  | —      | —      | LATA5       | LATA4           | _                 | LATA2      | LATA1      | LATA0   | xx -xxx               | uu -uuu                         |

| 10Dh            | LATB    | X —                              |        |        |             | Unimple         | mented            |            |            |         | —                     | —                               |

|                 |         | — X                              | LATB7  | LATB6  | LATB5       | LATB4           | _                 | _          | _          | —       | XXXX                  | uuuu                            |

| 10Eh            | LATC    | X —                              | _      | —      | LATC5       | LATC4           | LATC3             | LATC2      | LATC1      | LATC0   | xx xxxx               | uu uuuu                         |

|                 |         | — X                              | LATC7  | LATC6  | LATC5       | LATC4           | LATC3             | LATC2      | LATC1      | LATC0   | XXXX XXXX             | uuuu uuuu                       |

| 10Fh            | —       | —                                |        |        |             | Unimple         | mented            |            |            |         | —                     | —                               |

| 110h            | —       | —                                |        |        |             | Unimple         | mented            |            |            |         | —                     | _                               |

| 111h            | CM1CON0 |                                  | C10N   | C1OUT  | _           | C1POL           | _                 | C1SP       | C1HYS      | C1SYNC  | 00-0 -100             | 00-0 -100                       |

| 112h            | CM1CON1 |                                  | C1INTP | C1INTN |             | C1PCH<2:0>      |                   |            | C1NCH<2:0> |         | 0000 0000             | 0000 0000                       |

| 113h            | CM2CON0 |                                  | C2ON   | C2OUT  | _           | C2POL           | —                 | C2SP       | C2HYS      | C2SYNC  | 00-0 -100             | 00-0 -100                       |

| 114h            | CM2CON1 |                                  | C2INTP | C2INTN |             | C2PCH<2:0>      |                   |            | C2NCH<2:0> |         | 0000 0000             | 0000 0000                       |

| 115h            | CMOUT   |                                  | —      | —      |             | _               | _                 | _          | MC2OUT     | MC1OUT  | 00                    | 00                              |

| 116h            | BORCON  |                                  | SBOREN | —      | _           | _               | _                 | —          |            | BORRDY  | 1 q                   | u u                             |

| 117h            | FVRCON  |                                  | FVREN  | FVRRDY | TSEN        | TSRNG           | CDAFV             | R<1:0>     | ADFVI      | R<1:0>  | 0000 00p0             | 0000 00p0                       |

| 118h            | DACCON0 |                                  | DAC1EN | —      | DAC10E      |                 | DAC1PS            | SS<1:0>    | _          | DAC1NSS | 0-0- 00-0             | 0-0- 00-0                       |

| 119h            | DACCON1 |                                  |        | —      | _           |                 |                   | DAC1R<4:0> |            |         | 0 0000                | 0 0000                          |

| 11Ah to<br>11Fh | -       | _                                |        |        |             | Unimplemented   |                   |            |            |         | _                     | —                               |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Only on PIC16F18326/18346. Legend:

Note 1:

Register accessible from both User and ICD Debugger. 2:

| TABLE 4-4: SP | PECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|---------------|---------------------------------------------------------|

|---------------|---------------------------------------------------------|

| IADLL   |         | •                                |        |               |             |                   |                   | -,      |         |         |                       |                                 |

|---------|---------|----------------------------------|--------|---------------|-------------|-------------------|-------------------|---------|---------|---------|-----------------------|---------------------------------|

| Address | Name    | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7  | Bit 6         | Bit 5       | Bit 4             | Bit 3             | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank 5  |         |                                  |        |               |             |                   |                   |         |         |         |                       |                                 |

|         |         |                                  |        |               | CPU CORE RE | EGISTERS; see 1   | Table 4-2 for spe | ecifics |         |         |                       |                                 |

| 28Ch    | ODCONA  |                                  | _      | _             | ODCA5       | ODCA4             | _                 | ODCA2   | ODCA1   | ODCA0   | 00 -000               | 00 -000                         |

| 28Dh    | ODCONB  | X —                              |        |               |             | Unimple           | mented            |         |         |         | -                     | —                               |

|         |         | — X                              | ODCB7  | ODCB6         | ODCB5       | ODCB4             | _                 | _       | _       | _       | 0000                  | 0000                            |

| 28Eh    | ODCONC  | X —                              | _      | —             | ODCC5       | ODCC4             | ODCC3             | ODCC2   | ODCC1   | ODCC0   | 00 0000               | 00 0000                         |

|         |         | — X                              | ODCC7  | ODCC6         | ODCC5       | ODCC4             | ODCC3             | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                       |

| 28Fh    | —       | —                                |        | Unimplemented |             |                   |                   |         |         |         | -                     | —                               |

| 290h    | —       | —                                |        | Unimplemented |             |                   |                   |         |         |         | -                     | _                               |

| 291h    | CCPR1L  |                                  |        |               |             | CCPR <sup>2</sup> | 1<7:0>            |         |         |         | XXXX XXXX             | XXXX XXXX                       |

| 292h    | CCPR1H  |                                  |        |               |             | CCPR1             | <15:8>            |         |         |         | XXXX XXXX             | XXXX XXXX                       |

| 293h    | CCP1CON |                                  | CCP1EN | —             | CCP10UT     | CCP1FMT           |                   | CCP1MC  | DE<3:0> |         | 0-x0 0000             | 0-x0 0000                       |

| 294h    | CCP1CAP |                                  | —      |               | _           | _                 |                   | CCP1C   | TS<3:0> |         | 0000                  | xxxx                            |

| 295h    | CCPR2L  |                                  |        |               |             | CCPR2             | 2<7:0>            |         |         |         | XXXX XXXX             | XXXX XXXX                       |

| 296h    | CCPR2H  |                                  |        |               |             | CCPR2             | <15:8>            |         |         |         | XXXX XXXX             | XXXX XXXX                       |

| 297h    | CCP2CON |                                  | CCP2EN | —             | CCP2OUT     | CCP2FMT           |                   | CCP2MC  | DE<3:0> |         | 0-x0 0000             | 0-x0 0000                       |

| 298h    | CCP2CAP |                                  | —      | —             | _           |                   |                   | CCP2C   | TS<3:0> |         | 0000                  | xxxx                            |

| 299h    | —       | —                                |        |               |             | Unimple           | mented            |         |         |         | —                     | -                               |

| 29Ah    | —       | —                                |        |               |             | Unimple           | mented            |         |         |         | —                     | -                               |

| 29Bh    | —       | —                                |        |               |             | Unimple           | mented            |         |         |         | _                     | _                               |

| 29Ch    | —       | —                                |        |               |             | Unimple           | mented            |         |         |         | _                     | _                               |

| 29Dh    | —       | —                                |        |               |             | Unimple           | mented            |         |         |         | _                     | _                               |

| 29Eh    | —       | —                                |        |               |             | Unimple           | mented            |         |         |         | _                     | _                               |

| 29Fh    | CCPTMRS |                                  | C4TSEL | <1:0>         | C3TSE       | EL<1:0>           | C2TSE             | L<1:0>  | C1TSE   | EL<1:0> | 0101 0101             | 0101 0101                       |

Legend:

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Only on PIC16F18326/18346.

2: Register accessible from both User and ICD Debugger.

|                  |                    |                                                            |                 |              | REGISTER 4       |                  |             |

|------------------|--------------------|------------------------------------------------------------|-----------------|--------------|------------------|------------------|-------------|

| R/W-0/0          | R/W-0/0            | R/W-0/0                                                    | R/W-0/0         | R/W-0/0      | R/W-0/0          | R/W-0/0          | R/W-0/0     |

| CWG2IE           | CWG1IE             | TMR5GIE                                                    | TMR5IE          | CCP4IE       | CCP3IE           | CCP2IE           | CCP1IE      |

| bit 7            |                    |                                                            | L.              | 1            |                  |                  | bit (       |

|                  |                    |                                                            |                 |              |                  |                  |             |

| Legend:          |                    |                                                            |                 |              |                  |                  |             |

| R = Readable     | bit                | W = Writable                                               | bit             | U = Unimplei | mented bit, read | l as '0'         |             |

| u = Bit is unch  | anged              | x = Bit is unkr                                            | nown            | -n/n = Value | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |                    | '0' = Bit is clea                                          | ared            | HS = Hardwa  | are set          |                  |             |

| bit 7            | 1 = CWG2 int       | /G 2 Interrupt E<br>terrupt enabled<br>terrupt not enal    |                 |              |                  |                  |             |

| bit 6            | 1 = CWG1 i         | /G 1 Interrupt E<br>nterrupt enable<br>nterrupt not ena    | d               |              |                  |                  |             |

| bit 5            | 1 <b>= TMR5 Ga</b> | mer5 Gate Inte<br>ate interrupt is e<br>ate interrupt is r | nabled          | bit          |                  |                  |             |

| bit 4            | 1 = TMR5 ove       | R5 Overflow Int<br>erflow interrupt<br>erflow interrupt    | is enabled      |              |                  |                  |             |

| bit 3            | 1 = CCP4 inte      | P4 Interrupt Ena<br>errupt is enable<br>errupt is not ena  | d               |              |                  |                  |             |

| bit 2            | 1 = CCP3 inte      | P3 Interrupt En<br>errupt is enable<br>errupt is not en    | d               |              |                  |                  |             |

| bit 1            | 1 = CCP2 in        | P2 Interrupt En<br>Iterrupt is enab<br>Iterrupt is not e   | led             |              |                  |                  |             |

| bit 0            | CCP1IE: CCF        | P1 Interrupt En<br>Interrupt is enab                       | able bit<br>led |              |                  |                  |             |

#### **REGISTER 8-6: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4**

# 12.0 I/O PORTS

TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device         | PORTA | PORTB | PORTC |

|----------------|-------|-------|-------|

| PIC16(L)F18326 | •     |       | ٠     |

| PIC16(L)F18346 | •     | ٠     | ٠     |

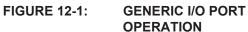

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- · LATx registers (output latch)

- · TRISx registers (data direction)

- · ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

# 12.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 13.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

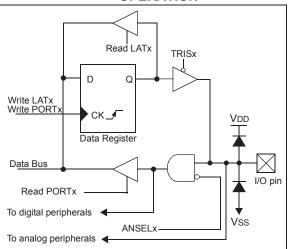

# 18.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, may have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will provide an input based on their level as either a TTL or ST input buffer.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

### FIGURE 18-3: ANALOG INPUT MODEL

# 21.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- Data selection

- Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

### 21.1.1 DATA SELECTION

There are 36 signals available as inputs to the configurable logic.

Data selection is through four multiplexers as indicated on the left side of Figure 21-2. Data inputs in the figure are identified by 'LCx\_in' signal name.

Table 21-1 correlates the input number to the actual signal for each CLC module. The column labeled 'LCxDyS<5:0> Value' indicates the MUX selection code for the selected data input. LCxDyS is an abbreviation for the MUX select input codes: LCxD1S<5:0> through LCxD4S<5:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 21-3 through Register 21-6).

# TABLE 21-1: CLCx DATA INPUT SELECTION

| TABLE 21-1.          | CLCX DATA INPUT SELECTION |

|----------------------|---------------------------|

| LCxDyS<5:0><br>Value | CLCx Input Source         |

| 100011 <b>[35]</b>   | TMR6/PR6 match            |

| 100010 <b>[34]</b>   | TMR5 overflow             |

| 100001 <b>[33]</b>   | TMR4/PR4 match            |

| 100000 <b>[32]</b>   | TMR3 overflow             |

| 11111 <b>[31]</b>    | Fosc                      |

| 11110 <b>[30]</b>    | HFINTOSC                  |

| 11101 <b>[29]</b>    | LFINTOSC                  |

| 11100 <b>[28]</b>    | ADCRC                     |

| 11011 <b>[27]</b>    | IOCIF int flag bit        |

| 11010 <b>[26]</b>    | TMR2/PR2 match            |

| 11001 <b>[25]</b>    | TMR1 overflow             |

| 11000 <b>[24]</b>    | TMR0 overflow             |

| 10111 <b>[23]</b>    | EUSART1 (DT) output       |

| 10110 <b>[22]</b>    | EUSART1 (TX/CK) output    |

| 10101 <b>[21]</b>    | SDA2                      |

| 10100 <b>[20]</b>    | SCL2                      |

| 10011 <b>[19]</b>    | SDA1                      |

| 10010 <b>[18]</b>    | SCL1                      |

| 10001 [17]           | PWM6 output               |

| 10000 <b>[16]</b>    | PWM5 output               |

| 01111 <b>[15]</b>    | CCP4 output               |

| 01110 [14]           | CCP3 output               |

| 01101 <b>[13]</b>    | CCP2 output               |

| 01100 [12]           | CCP1 output               |

| 01011 [11]           | CLKR output               |

| 01010 <b>[10]</b>    | DSM output                |

| 01001 [9]            | C2 output                 |

| 01000 [8]            | C1 output                 |

| 00111 [7]            | CLC4 output               |

| 00110 [6]            | CLC3 output               |

| 00101 [5]            | CLC2 output               |

| 00100 [4]            | CLC1 output               |

| 00011 <b>[3]</b>     | CLCIN3PPS                 |

| 00010 [2]            | CLCIN2PPS                 |

| 00001 [1]            | CLCIN1PPS                 |

| 00000 <b>[0]</b>     | CLCIN0PPS                 |

|                      |                           |

| R/W-x/u                 | R/W-x/u                                         | R/W-x/u                                                                                        | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |  |  |  |

|-------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|--|--|

| LCxG3D4T                | LCxG3D4N                                        | LCxG3D3T                                                                                       | LCxG3D3N       | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |  |  |  |  |  |

| bit 7                   |                                                 |                                                                                                |                |                |                  |                  | bit (       |  |  |  |  |  |

|                         |                                                 |                                                                                                |                |                |                  |                  |             |  |  |  |  |  |

| Legend:<br>R = Readable | bit                                             | W = Writable                                                                                   | h:t            |                | nantad hit raad  |                  |             |  |  |  |  |  |

|                         |                                                 |                                                                                                |                |                | nented bit, read |                  | than Decete |  |  |  |  |  |

| u = Bit is unch         | angeo                                           | x = Bit is unkr                                                                                |                | -n/n = value a | at POR and BO    | R/Value at all c | iner Resets |  |  |  |  |  |

| '1' = Bit is set        |                                                 | '0' = Bit is cle                                                                               | ared           |                |                  |                  |             |  |  |  |  |  |

| bit 7                   | LCxG3D4T· (                                     | Gate 2 Data 4 1                                                                                | īrue (non-inve | rted) hit      |                  |                  |             |  |  |  |  |  |

| Sit I                   |                                                 | (true) is gated i                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                         |                                                 | (true) is not gat                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 6                   | LCxG3D4N:                                       | Gate 2 Data 4                                                                                  | Negated (inve  | rted) bit      |                  |                  |             |  |  |  |  |  |

|                         | 1 = CLCIN3                                      | = CLCIN3 (inverted) is gated into CLCx Gate 2                                                  |                |                |                  |                  |             |  |  |  |  |  |

|                         | 0 = CLCIN3                                      | 0 = CLCIN3 (inverted) is not gated into CLCx Gate 2                                            |                |                |                  |                  |             |  |  |  |  |  |

| bit 5                   | LCxG3D3T: Gate 2 Data 3 True (non-inverted) bit |                                                                                                |                |                |                  |                  |             |  |  |  |  |  |

|                         |                                                 | I2 (true) is gated into CLCx Gate 2<br>I2 (true) is not gated into CLCx Gate 2                 |                |                |                  |                  |             |  |  |  |  |  |

|                         |                                                 |                                                                                                |                |                |                  |                  |             |  |  |  |  |  |

| bit 4                   |                                                 | Gate 2 Data 3                                                                                  | •              | ,              |                  |                  |             |  |  |  |  |  |

|                         |                                                 | CLCIN2 (inverted) is gated into CLCx Gate 2<br>CLCIN2 (inverted) is not gated into CLCx Gate 2 |                |                |                  |                  |             |  |  |  |  |  |

| bit 3                   |                                                 | Gate 2 Data 2 1                                                                                | 0              |                |                  |                  |             |  |  |  |  |  |

| bit 0                   |                                                 | (true) is gated i                                                                              |                | ,              |                  |                  |             |  |  |  |  |  |

|                         |                                                 | (true) is not gat                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 2                   | LCxG3D2N:                                       | Gate 2 Data 2                                                                                  | Negated (inve  | rted) bit      |                  |                  |             |  |  |  |  |  |

|                         | 1 = CLCIN1 (                                    | 1 = CLCIN1 (inverted) is gated into CLCx Gate 2                                                |                |                |                  |                  |             |  |  |  |  |  |

|                         | 0 = CLCIN1                                      | = CLCIN1 (inverted) is not gated into CLCx Gate 2                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 1                   | LCxG3D1T: (                                     | Gate 2 Data 1 1                                                                                | rue (non-inve  | rted) bit      |                  |                  |             |  |  |  |  |  |

|                         |                                                 | CLCIN0 (true) is gated into CLCx Gate 2                                                        |                |                |                  |                  |             |  |  |  |  |  |

|                         |                                                 | (true) is not gat                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 0                   |                                                 | Gate 2 Data 1                                                                                  | •              | ,              |                  |                  |             |  |  |  |  |  |

|                         |                                                 | (inverted) is ga<br>(inverted) is no                                                           |                |                |                  |                  |             |  |  |  |  |  |

|                         |                                                 |                                                                                                |                |                |                  |                  |             |  |  |  |  |  |

# REGISTER 21-9: CLCxGLS2: GATE 2 LOGIC SELECT REGISTER

# 23.0 NUMERICALLY CONTROLLED OSCILLATOR (NCO1) MODULE

The Numerically Controlled Oscillator (NCO1) module is a timer that uses the overflow from the addition of an increment value to divide the input frequency. The advantage of the addition method over simple counter-driven timer is that the output frequency resolution does not vary with the divider value. The NCO1 is most useful for applications that require frequency accuracy and fine resolution at a fixed duty cycle.

Features of the NCO1 include:

- 20-bit increment function

- Fixed Duty Cycle (FDC) mode

- Pulse Frequency (PF) mode

- Output pulse-width control

- Multiple clock input sources

- Output polarity control

- Interrupt capability

Figure 23-1 is a simplified block diagram of the NCO1 module.

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4     | Bit 3  | Bit 2  | Bit 1     | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------|-----------|--------|--------|-----------|--------|---------------------|

| TRISA                 | _                     | _                     | TRISA5   | TRISA4    | (2)    | TRISA2 | TRISA1    | TRISA0 | 143                 |

| ANSELA                | —                     |                       | ANSA5    | ANSA4     | _      | ANSA2  | ANSA1     | ANSA0  | 144                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4    | —      | —      | —         | —      | 149                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5    | ANSB4     | —      | —      | —         | —      | 150                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4    | TRISC3 | TRISC2 | TRISC1    | TRISC0 | 155                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5    | ANSC4     | ANSC3  | ANSC2  | ANSC1     | ANSC0  | 157                 |

| PIR2                  | TMR6IF                | C2IF                  | C1IF     | NVMIF     | SSP2IF | BCL2IF | TMR4IF    | NCO1IF | 108                 |

| PIE2                  | TMR6IE                | C2IE                  | C1IE     | NVMIE     | SSP2IE | BCL2IE | TMR4IE    | NCO1IE | 103                 |

| INTCON                | GIE                   | PEIE                  |          | _         | _      | _      | _         | INTEDG | 100                 |

| NCO1CON               | N1EN                  | _                     | N1OUT    | N1POL     |        | _      |           | N1PFM  | 256                 |

| NCO1CLK               |                       | N1PWS<2:0             | )>       |           |        |        | N1CK      | S<1:0> | 257                 |

| NCO1ACCL              |                       |                       | NC       | CO1ACC <7 | :0>    |        | •         |        | 257                 |

| NCO1ACCH              |                       |                       | NC       | 01ACC <18 | 5:8>   |        |           |        | 258                 |

| NCO1ACCU              | _                     |                       | _        | _         |        | NCO1AC | C <19:16> | >      | 258                 |

| NCO1INCL              |                       |                       | N        | CO1INC<7: | 0>     |        |           |        | 258                 |

| NCO1INCH              |                       |                       | NC       | CO1INC<15 | :8>    |        |           |        | 259                 |

| NCO1INCU              | _                     |                       | _        |           |        | NCO1IN | C<19:16>  |        | 259                 |

| CWG1DAT               | _                     |                       |          |           |        | DAT    | <3:0>     |        | 215                 |

| MDSRC                 | _                     |                       |          | _         |        | MDM    | S<3:0>    |        | 272                 |

| MDCARH                |                       | MDCHPOL               | MDCHSYNC |           |        | MDCI   | H<3:0>    |        | 273                 |

| MDCARL                | _                     | MDCLPOL               | MDCLSYNC | _         |        | MDC    | L<3:0>    |        | 274                 |

| CCPxCAP               | —                     | —                     | —        | _         |        | CCPxC  | TS<3:0>   |        | 309                 |

# TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCO1

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for NCO1 module.

Note 1: PIC16(L)F18346 only.

2: Unimplemented, read as '1'.

# PIC16(L)F18326/18346

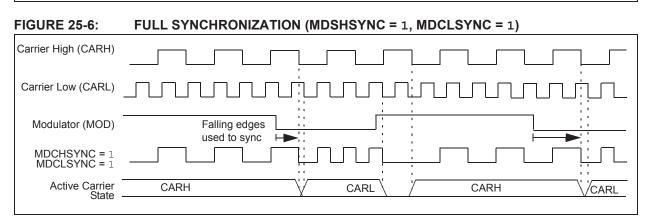

| FIGURE 25-5:                 | CARRIER LOW SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 1) |

|------------------------------|----------------------------------------------------------|

| Carrier High (CARH)          |                                                          |

| Carrier Low (CARL)           |                                                          |

| Modulator (MOD)              |                                                          |

| MDCHSYNC = 0<br>MDCLSYNC = 1 |                                                          |

| Active Carrier<br>State -    | CARH X CARL CARH X CARL                                  |

| R/W-x/x          | R/W-x/x  | R/W-x/x           | R/W-x/x       | R/W-x/x        | R/W-x/x          | R/W-x/x        | R/W-x/x     |

|------------------|----------|-------------------|---------------|----------------|------------------|----------------|-------------|

|                  |          |                   | CCPR          | xL<7:0>        |                  |                |             |

| bit 7            |          |                   |               |                |                  |                | bit 0       |

|                  |          |                   |               |                |                  |                |             |

| Legend:          |          |                   |               |                |                  |                |             |

| R = Readable     | bit      | W = Writable b    | oit           | U = Unimpler   | nented bit, read | d as '0'       |             |

| u = Bit is unch  | anged    | x = Bit is unkn   | own           | -n/n = Value a | at POR and BC    | R/Value at all | other Reset |

| '1' = Bit is set |          | '0' = Bit is clea | ared          |                |                  |                |             |

|                  |          |                   |               |                |                  |                |             |

| bit 7-0          | CCPxMODE | = Capture mode    | <u>e</u>      |                |                  |                |             |

|                  | CCPRx    | I <7:0>: Capture  | d value of TM | /R1/3/5I       |                  |                |             |

### REGISTER 29-3: CCPRxL REGISTER: CCPx REGISTER LOW BYTE

# REGISTER 29-4: CCPRxH REGISTER: CCPx REGISTER HIGH BYTE

| R/W-x/x | R/W-x/x           | R/W-x/x                                     | R/W-x/x                                             | R/W-x/x                                                                                     | R/W-x/x                                                                                                             | R/W-x/x                                                                                                                                                                          |  |  |

|---------|-------------------|---------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         |                   | CCPR                                        | xH<7:0>                                             |                                                                                             |                                                                                                                     |                                                                                                                                                                                  |  |  |

|         |                   |                                             |                                                     |                                                                                             |                                                                                                                     | bit 0                                                                                                                                                                            |  |  |

|         |                   |                                             |                                                     |                                                                                             |                                                                                                                     |                                                                                                                                                                                  |  |  |

|         |                   |                                             |                                                     |                                                                                             |                                                                                                                     |                                                                                                                                                                                  |  |  |

| bit     | W = Writable      | bit                                         | U = Unimplemented bit, read as '0'                  |                                                                                             |                                                                                                                     |                                                                                                                                                                                  |  |  |

| anged   | x = Bit is unkn   | iown                                        | -n/n = Value at POR and BOR/Value at all other Rese |                                                                                             |                                                                                                                     |                                                                                                                                                                                  |  |  |

|         | '0' = Bit is clea | ared                                        |                                                     |                                                                                             |                                                                                                                     |                                                                                                                                                                                  |  |  |

|         | bit               | bit W = Writable I<br>anged x = Bit is unkn | CCPR:<br>bit W = Writable bit                       | CCPRxH<7:0><br>bit W = Writable bit U = Unimpler<br>anged x = Bit is unknown -n/n = Value a | CCPRxH<7:0> bit W = Writable bit U = Unimplemented bit, read<br>anged x = Bit is unknown -n/n = Value at POR and BC | CCPRxH<7:0>         bit       W = Writable bit       U = Unimplemented bit, read as '0'         anged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all of |  |  |

| bit 7-0 | CCPxMODE = Capture mode                                          |

|---------|------------------------------------------------------------------|

|         | CCPRxH<7:0>: Captured value of TMR1/3/5H                         |

|         | CCPxMODE = Compare mode                                          |

|         | CCPRxH<7:0>: MS Byte compared to TMR1/3/5H                       |

|         | CCPxMODE = PWM modes when CCPxFMT = 0                            |

|         | CCPRxH<7:2>: Not used                                            |

|         | CCPRxH<1:0>: CCPW<9:8> – Pulse-width Most Significant two bits   |

|         | CCPxMODE = PWM modes when CCPxFMT = 1                            |

|         | CCPRxH<7:0>: CCPW<9:2> – Pulse-width Most Significant eight bits |

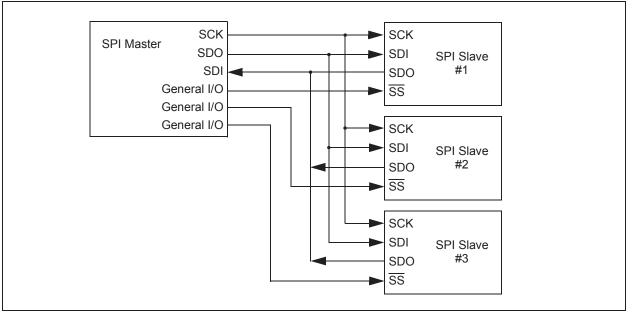

# 30.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 30-1 shows the block diagram of the MSSPx module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection can be used to address each slave individually.

Figure 30-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. Data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 30-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions must be performed in multiples of eight clock pulses. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

# 30.2.1 SPI MODE REGISTERS

The MSSPx module has five registers for SPI mode operation. These are:

- MSSPx STATUS register (SSPxSTAT)

- MSSPx Control register 1 (SSPxCON1)

- MSSPx Control register 3 (SSPxCON3)

- MSSPx Data Buffer register (SSPxBUF)

- MSSPx Address register (SSPxADD)

- MSSPx Shift register (SSPxSR)

- (Not directly accessible)

SSPxCON1 and SSPSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI Master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in Section 30.7 "Baud Rate Generator".

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

# 30.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCONy registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDI must have corresponding TRIS bit set

- SDO must have corresponding TRIS bit cleared

SCK (Master mode) must have corresponding

- TRIS bit cleared

- SCK (Slave mode) must have corresponding <u>TRIS</u> bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

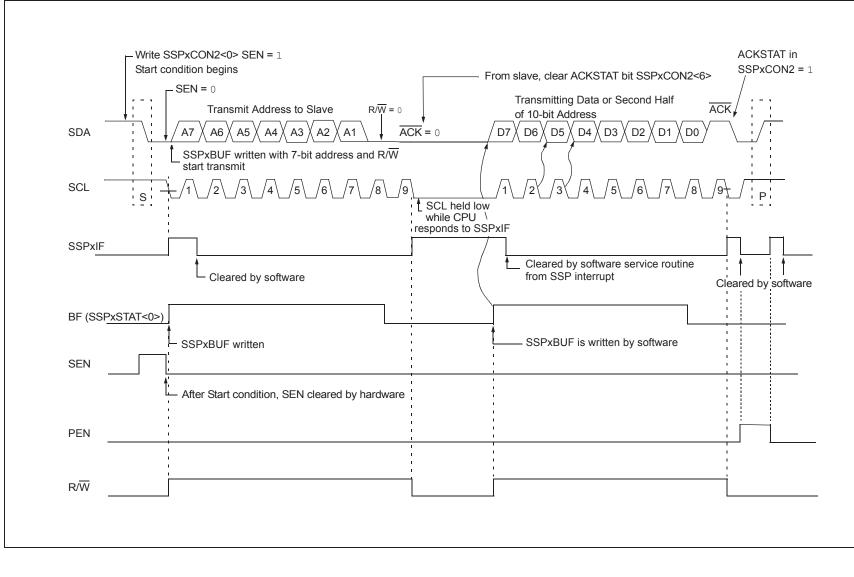

# 30.4.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, the clock is stretched, allowing the slave time to change the  $\overrightarrow{ACK}$  value before it is sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 30.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

# 30.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 30-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 30-5) affects the address matching process. See **Section 30.5.9** "SSP **Mask Register**" for more information.

### 30.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

### 30.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

# FIGURE 30-28: I<sup>2</sup>C MASTER MODE WAVEFORM (TRANSMISSION, 7 OR 10-BIT ADDRESS)

<u>6</u>

)F18326/18346

# PIC16(L)F18326/18346

#### 35.4 **AC Characteristics**

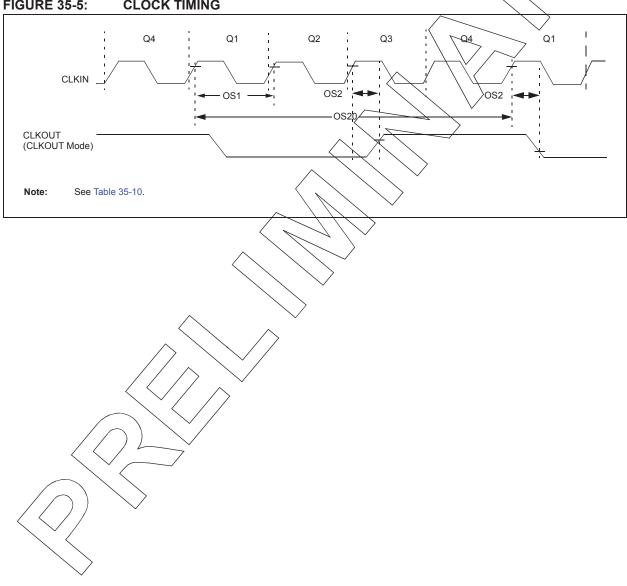

#### FIGURE 35-5: **CLOCK TIMING**

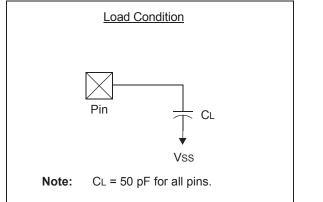

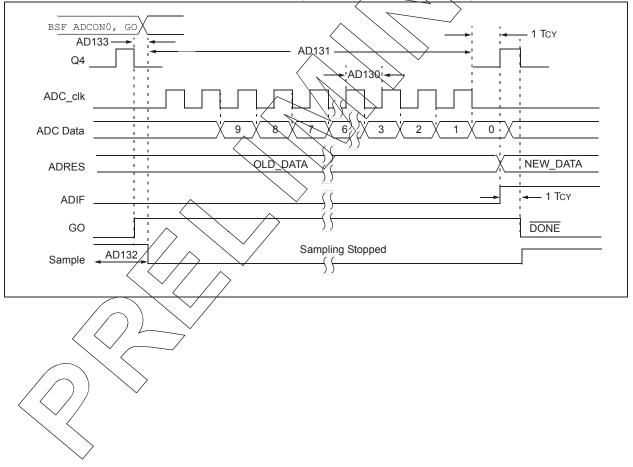

# TABLE 35-13: ANALOG-TO DIGITAL CONVERTER (ADC) CONVERSION TIMING SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |      |                           |      |       |      |       |                                                             |  |

|---------------------------------------------------------|------|---------------------------|------|-------|------|-------|-------------------------------------------------------------|--|

| Param.<br>No.                                           | Sym. | Characteristic            | Min. | Typ.† | Max. | Units | Conditions                                                  |  |

| AD20                                                    | TAD  | ADC Clock Period          | 1    |       | 9    | us    | Using Fosc as the ADC clock source;<br>ADCS $! = \times 11$ |  |

| AD21                                                    |      |                           | 1    | 2     | 6    | us    | Using ADCRC as the<br>ADC clock source,<br>ADCS = 11        |  |

| AD22                                                    | TCNV | Conversion Time           | _    | 11    | _    | TAD   | Set of GO/DONE bit to<br>Clear of GO/DONE bit               |  |

| AD23                                                    | TACQ | Acquisition Time          | _    | 2     | _    | us    |                                                             |  |

| AD24                                                    | THCD | Sample and Hold Capacitor |      | _     | _    | us <  | Fosc based clock source                                     |  |

|                                                         |      | Disconnect Time           |      |       | _    | us    | ADCRC based clock source                                    |  |

| * These parameters are characterized but not tested     |      |                           |      |       | (    |       |                                                             |  |

These parameters are characterized but not tested.

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

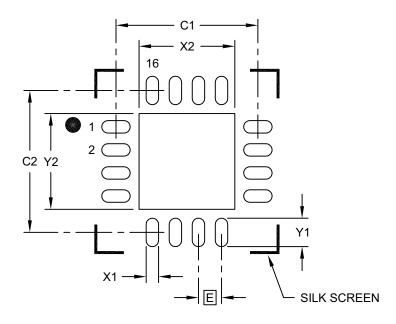

# 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                            | Units             | N        | 1ILLIMETER | c    |

|----------------------------|-------------------|----------|------------|------|

|                            | IVIILLIIVIE I ERS |          |            |      |

| Dimensior                  | MIN               | NOM      | MAX        |      |

| Contact Pitch              | E                 | 0.65 BSC |            |      |

| Optional Center Pad Width  | X2                |          |            | 2.70 |

| Optional Center Pad Length | Y2                |          |            | 2.70 |

| Contact Pad Spacing        | C1                |          | 4.00       |      |

| Contact Pad Spacing        | C2                |          | 4.00       |      |

| Contact Pad Width (X16)    | X1                |          |            | 0.35 |

| Contact Pad Length (X16)   | Y1                |          |            | 0.80 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

# ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

# EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820