Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18346-i-gz |

| <u> </u>               |

|------------------------|

| 6                      |

|                        |

| $\dot{\boldsymbol{+}}$ |

|                        |

| $\infty$               |

| $\omega$               |

| 6                      |

| 3                      |

| $\infty$               |

| ည                      |

| 6                      |

| Address | Name       | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7 | Bit 6         | Bit 5       | Bit 4         | Bit 3            | Bit 2          | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|----------------------------------|-------|---------------|-------------|---------------|------------------|----------------|-------|-------|-----------------------|---------------------------------|

| Bank 2  | 3          |                                  |       |               |             |               |                  |                |       |       |                       |                                 |

|         |            |                                  |       |               | CPU CORE RI | EGISTERS; see | Table 4-2 for sp | ecifics        |       |       |                       |                                 |

| E21h    | SSP1DATPPS | X   -                            | _     | _             | _           |               | S                | SP1DATPPS<4:0  | )>    |       | 1 0001                | u uuu                           |

|         |            | _ x                              | _     | _             | _           |               | S                | SP1DATPPS<4:(  | )>    |       | 0 1100                | u uuu                           |

| E22h    | SSP1SSPPS  | X  -                             | _     | _             | _           |               | 9                | SSP1SSPPS<4:0  | >     |       | 1 0011                | u uuu                           |

|         |            | _ X                              | _     | _             | _           |               | 5                | SSP1SSPPS<4:0  | >     |       | 1 0100                | u uuu                           |

| E23h    | _          |                                  |       |               |             | Unimple       | emented          |                |       |       | _                     | _                               |

| E24h    | RXPPS      | X —                              | _     | _             | _           |               |                  | RXPPS<4:0>     |       |       | 1 0101                | u uuu                           |

|         |            | _ X                              | _     | _             | _           |               | RXPPS<4:0>       |                |       |       |                       |                                 |

| E25h    | TXPPS      | X   -                            | _     | _             | _           |               | TXPPS<4:0>       |                |       |       |                       |                                 |

|         |            | _ X                              | _     | _             | _           |               | TXPPS<4:0>       |                |       |       |                       |                                 |

| E26h    | _          | _                                |       | Unimplemented |             |               |                  |                |       |       |                       |                                 |

| E27h    | _          |                                  |       | Unimplemented |             |               |                  |                |       |       |                       | _                               |

| E28h    | CLCIN0PPS  | X —                              | _     | _             | _           |               | (                | CLCIN0PPS<4:0  | >     |       | 1 0011                | u uuu                           |

|         |            | _ X                              | _     | _             | _           |               | (                | CLCIN0PPS<4:0  | >     |       | 0 0010                | u uuu                           |

| E29h    | CLCIN1PPS  | X —                              | _     | _             | _           |               | (                | CLCIN1PPS<4:0  | >     |       | 0 0100                | u uuuı                          |

|         |            | _ X                              | _     | _             | _           |               | (                | CLCIN1PPS<4:0  | >     |       | 1 0011                | u uuuı                          |

| E2Ah    | CLCIN2PPS  | X —                              |       | _             | _           |               |                  | CLCIN2PPS<4:0: | >     |       | 1 0001                | u uuuı                          |

|         |            | _ X                              | _     | _             | _           |               | (                | CLCIN2PPS<4:0: | >     |       | 0 1100                | u uuu                           |

| E2Bh    | CLCIN3PPS  | X —                              |       | _             | _           |               |                  | CLCIN3PPS<4:0  | >     |       | 0 0101                | u uuu                           |

|         |            | _ X                              | _     | _             | _           |               | (                | CLCIN3PPS<4:0  | >     |       | 0 1101                | u uuuı                          |

| E2Ch    | T3CKIPPS   | X —                              |       | _             | _           |               |                  | T3CKIPPS<4:0>  |       |       | 1 0001                | u uuuı                          |

|         |            | _ X                              | _     | _             | _           |               |                  | T3CKIPPS<4:0>  |       |       | 0 0101                | u uuuı                          |

| E2Dh    | T3GPPS     | X —                              | _     | _             | _           |               |                  | T3GPPS<4:0>    |       |       | 1 0001                | u uuuı                          |

|         |            | _ X                              | _     | _             | _           |               |                  | T3GPPS<4:0>    |       |       | 1 0100                | u uuuı                          |

| E2Eh    | T5CKIPPS   | x —                              | _     | _             | _           |               |                  | T5CKIPPS<4:0>  |       |       | 1 0001                | u uuuı                          |

|         |            | _ X                              | _     | _             | _           |               |                  | T5CKIPPS<4:0>  |       |       | 0 0101                | u uuuı                          |

| E2Fh    | T5GPPS     | X —                              |       | _             | _           |               |                  | T5GPPS<4:0>    |       |       | 1 0001                | u uuuı                          |

|         |            | _  X                             | _     | _             | _           |               |                  | T5GPPS<4:0>    |       |       | 1 0100                | u uuui                          |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Only on PIC16F18326/18346.

Note 1:

Register accessible from both User and ICD Debugger.

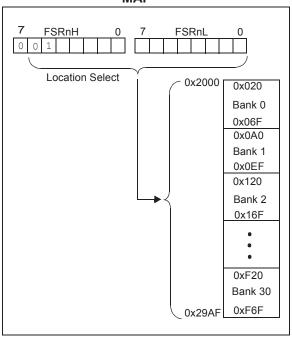

#### 4.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 4-10: LINEAR DATA MEMORY MAP

#### 4.5.3 DATA EEPROM MEMORY

The EEPROM memory can be read or written through the NVMCON register interface (see Section 11.2 "Data EEPROM"). However, to make access to the EEPROM easier, read-only access to the EEPROM contents are also available through indirect addressing via an FSR. When the MSP of the FSR (ex: FSRxH) is set to 0x70, the lower 8-bit address value (in FSRxL) determines the EEPROM location that may be read via the INDF register). In other words, the EEPROM address range 0x00-0xFF is mapped into the FSR address space between 0x7000 and 0x70FF. Writing to the EEPROM cannot be accomplished via the FSR/INDF interface. Reads from the EEPROM through the FSR/INDF interface will require one additional instruction cycle to complete.

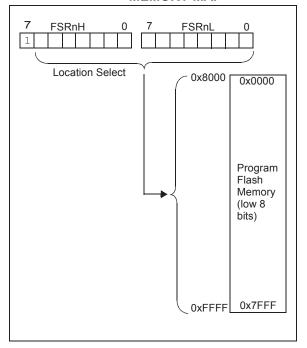

#### 4.5.4 PROGRAM FLASH MEMORY

To make constant data access easier, the entire Program Flash Memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location are accessible via INDF. Writing to the Program Flash Memory cannot be accomplished via the FSR/INDF interface. All instructions that access Program Flash Memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 4-11: PROGRAM FLASH MEMORY MAP

# 6.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

# 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset while VDD is below a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset, and the BOR bit of the PCON0 register will be cleared, indicating that a Brown-out Reset condition occurred. See Figure 6-2 for more information.

TABLE 6-1: BOR OPERATING MODES

| BOREN<1:0> | SBOREN | Device Mode  | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep                                                                                                                                                                                           |

|------------|--------|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | X      | Х            | Active   | In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits. |

| 10         | X      | Awake Active |          | Waits for release of BOR (BORRDY = 1)                                                                                                                                                                                                                         |

| 10         | X      | Sleep        | Disabled | BOR ignored when asleep                                                                                                                                                                                                                                       |

| 01         | 1      | х            | Active   | In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits  |

|            | 0      | Х            | Disabled | Pagina immediately (POPPDV =)                                                                                                                                                                                                                                 |

| 00         | X      | X            | Disabled | Begins immediately (BORRDY = x)                                                                                                                                                                                                                               |

# 6.13 Register Definitions: Power Control

#### REGISTER 6-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

Legend:

HC = Bit is cleared by hardware HS = Bit is set by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -m/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 STKOVF: Stack Overflow Flag bit

1 = A Stack Overflow occurred

0 = A Stack Overflow has not occurred or has been cleared by firmware

bit 6 STKUNF: Stack Underflow Flag bit

1 = A Stack Underflow occurred

0 = A Stack Underflow has not occurred or has been cleared by firmware

bit 5 **Unimplemented:** Read as '0'

bit 4 RWDT: Watchdog Timer Reset Flag bit

1 = A Watchdog Timer Reset has not occurred or set to '1' by firmware

0 = A Watchdog Timer Reset has occurred (cleared by hardware)

bit 3 RMCLR: MCLR Reset Flag bit

1 = A MCLR Reset has not occurred or set to '1' by firmware

$0 = A \overline{MCLR}$  Reset has occurred (cleared by hardware)

bit 2 RESET Instruction Flag bit

1 = A RESET instruction has not been executed or set to '1' by firmware

0 = A RESET instruction has been executed (cleared by hardware)

bit 1 POR: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset

occurs)

### TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0  | Register on Page |

|--------|--------|--------|-------|-------|--------|-------|-------|--------|------------------|

| BORCON | SBOREN | _      |       |       | _      | _     |       | BORRDY | 76               |

| PCON0  | STKOVF | STKUNF | _     | RWDT  | RMCLR  | RI    | POR   | BOR    | 77               |

| STATUS | _      | 1      | 1     | TO    | PD     | Z     | DC    | С      | 30               |

| WDTCON | _      | _      |       | V     | SWDTEN | 121   |       |        |                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

#### 7.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

There is also a secondary oscillator block which is optimized for a 32.768 kHz external clock source, which can be used as an alternate clock source.

There are two internal oscillator blocks:

- HFINTOSC

- LFINTOSC

The HFINTOSC can produce clock frequencies from 1-16 MHz. The LFINTOSC generates a 31 kHz clock frequency.

There is a PLL that can be used by the external oscillator. See **Section 7.2.1.4** "4x PLL" for more details. Additionally, there is a PLL that can be used by the HFINTOSC at certain frequencies. See **Section 7.2.2.2** "2x PLL" for more details.

#### 7.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> and NDIV<3:0> bits in the OSCCON1 register to switch the system clock source.

See Section 7.3 "Clock Switching" for more information.

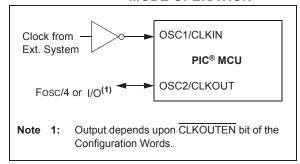

#### 7.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the CLKIN input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 7-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, <= 32 MHz

- ECM Medium power, <= 8 MHz

- ECL Low power, <= 0.1 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC® MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

#### 9.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0). If the SLEEP instruction is executed while the IDLEN bit is set (IDLEN = 1), the CPU will enter the Idle mode (Section 9.2.3 "Low-Power Sleep Mode").

Upon entering Sleep mode, the following conditions exist:

- Resets other than WDT are not affected by Sleep mode; WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The PD bit of the STATUS register is cleared

- 3. The TO bit of the STATUS register is set

- 4. The CPU and System clocks are disabled

- 31 kHz LFINTOSC, HFINTOSC and SOSC will remain enabled if any peripheral has requested them as a clock source or if the HFOEN, LFOEN, or SOSCEN bits of the OSCEN register are set.

- 6. ADC is unaffected if the dedicated ADCRC oscillator is selected. When the ADC clock is something other than ADCRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains active.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low, or high-impedance) only if no peripheral connected to the I/O port is active.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

$\mbox{I/O}$  pins that are high-impedance inputs should be pulled to  $\mbox{VDD}$  or  $\mbox{VSS}$  externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 24.0 "5-bit Digital-to-Analog Converter (DAC1) Module" and Section 16.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 9.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled

- Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last two events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to Section 6.11 "Determining the Cause of a Reset".

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

#### 9.2.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs during or after the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

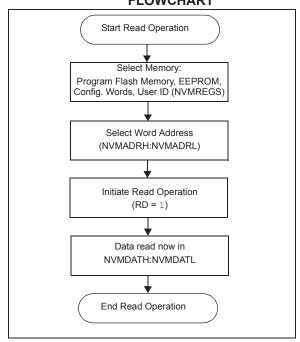

FIGURE 11-1: PROGRAM FLASH MEMORY READ FLOWCHART

# **EXAMPLE 11-1: PROGRAM FLASH MEMORY READ**

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

* data will be returned in the variables;

* PROG_DATA_HI, PROG_DATA_LO

BANKSEL NVMADRL ; Select Bank for NVMCON registers

MOVLW PROG_ADDR_LO ;

MOVWF NVMADRL ; Store LSB of address

MOVLW PROG_ADDR_HI ;

MOVWF NVMADRH ; Store MSB of address

BCF NVMCON1,NVMREGS ; Do not select Configuration Space

BSF NVMCON1,RD ; Initiate read

MOVF NVMDATL,W ; Get LSB of word

MOVWF PROG_DATA_LO ; Store in user location

MOVF NVMDATH,W ; Get MSB of word

MOVF PROG_DATA_HI ; Store in user location

```

# 11.5 Register Definitions: Program Flash Memory Control

# REGISTER 11-1: NVMDATL: NONVOLATILE MEMORY DATA LOW BYTE REGISTER

| R/W-0/0     | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|

| NVMDAT<7:0> |             |         |         |         |         |         |         |  |  |  |

| bit 7       | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 NVMDAT<7:0>: Read/Write Value for Least Significant bits of Program Memory

#### REGISTER 11-2: NVMDATH: NONVOLATILE MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------|-----|---------|--------------|---------|---------|---------|---------|--|--|

| _     | _   |         | NVMDAT<13:8> |         |         |         |         |  |  |

| bit 7 |     |         |              |         |         |         | bit 0   |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **NVMDAT<13:8>**: Read/Write Value for Most Significant bits of Program Memory<sup>(1)</sup>

Note 1: This byte is ignored when writing to EEPROM.

#### REGISTER 11-3: NVMADRL: NONVOLATILE MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0     | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|--|

| NVMADR<7:0> |             |         |         |         |         |         |         |  |  |  |  |

| bit 7       | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **NVMADR<7:0>**: Specifies the Least Significant bits for Program Memory Address

### REGISTER 11-4: NVMADRH: NONVOLATILE MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-------|---------|--------------|---------|---------|---------|---------|---------|--|--|--|

| _     |         | NVMADR<14:8> |         |         |         |         |         |  |  |  |

| bit 7 |         |              |         |         |         |         | bit 0   |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **Unimplemented:** Read as '1'

bit 6-0 NVMADR<14:8>: Specifies the Most Significant bits for Program Memory Address

#### REGISTER 12-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| _     | _   | SLRA5   | SLRA4   | _   | SLRA2   | SLRA1   | SLRA0   |

| bit 7 |     |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 SLRA<5:4>: PORTA Slew Rate Enable bits

For RA<5:4> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

bit 3 **Unimplemented:** Read as '0'

bit 2-0 SLRA<2:0>: PORTA Slew Rate Enable bits

For RA<2:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

#### REGISTER 12-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 INLVLA<5:0>: PORTA Input Level Select bits

For RA<5:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

# REGISTER 14-6: PMD5: PMD CONTROL REGISTER 5

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|---------|---------|---------|

| _     | _   | _   | CLC4MD  | CLC3MD  | CLC2MD  | CLC1MD  | DSMMD   |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                     |

|---------|------------------------------------------------------------------------------------------------|

| bit 4   | CLC4MD: Disable CLC4 bit  1 = CLC4 module disabled  0 = CLC4 module enabled                    |

| bit 3   | CLC3MD: Disable CLC3 bit  1 = CLC3 module disabled  0 = CLC3 module enabled                    |

| bit 2   | CLC2MD: Disable CLC2 bit  1 = CLC2 module disabled  0 = CLC2 module enabled                    |

| bit 1   | CLC1MD: Disable CLC1 bit  1 = CLC1 module disabled  0 = CLC1 module enabled                    |

| bit 0   | <b>DSMMD:</b> Disable Data Signal Modulator bit 1 = DSM module disabled 0 = DSM module enabled |

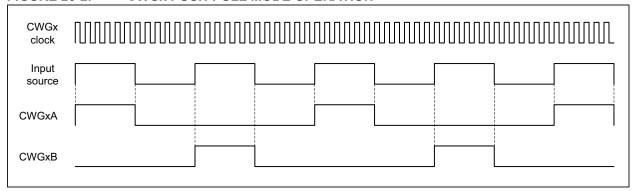

#### 20.2.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 20-2. This alternation creates the push-pull effect required for driving some transformer based power supply designs. Dead-band control is not used in Push-Pull mode. Steering modes are not used in Push-Pull mode.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWGxA.

The unused outputs CWGxC and CWGxD drive copies of CWGxA and CWGxB, respectively, but with polarity controlled by POLC and POLD.

FIGURE 20-2: CWGx PUSH-PULL MODE OPERATION

#### 20.2.3 STEERING MODES

In both Synchronous and Asynchronous Steering modes, the modulated input signal can be steered to any combination of four CWG outputs and a fixed-value will be presented on all the outputs not used for the PWM output. Each output has independent polarity, steering, and shutdown options. Dead-band control is not used in either Steering mode.

When STRy = 0 (Register 20-5), the corresponding pin is held at the level defined by SDATy (Register 20-5). When STRy = 1, the pin is driven by the modulated input signal.

The POLy bits (Register 20-2) control the signal polarity only when STRy = 1.

The CWG auto-shutdown operation also applies to Steering modes as described in Section 20.11 "Register Definitions: CWG Control".

**Note:** Only the WGSTRy bits are synchronized; the WGSDATy (data) bits are not synchronized.

#### 26.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system oscillator (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

#### 26.2 Clock Source Selection

The T0CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 26-4 displays the clock source selections.

#### 26.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, Timer0 operates as a timer and will increment on multiples of the clock source, as determined by the Timer0 prescaler.

#### 26.2.2 EXTERNAL CLOCK SOURCE

When an external clock source is selected, Timer0 can operate as either a timer or a counter. Timer0 will increment on multiples of the rising edge of the external clock source, as determined by the Timer0 prescaler.

#### 26.3 Programmable Prescaler

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the T0CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register, the T0CON0 register, or the T0CON1 register.

### 26.4 Programmable Postscaler

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the TOOUTPS<3:0> bits of the TOCON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register, the T0CON0 register, or the T0CON1 register.

#### 26.5 Operation During Sleep

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

#### 26.6 Timer0 Interrupts

The Timer0 Interrupt Flag bit (TMR0IF) is set when either of the following conditions occur:

- · 8-bit TMR0L matches the TMR0H value

- · 16-bit TMR0 rolls over from FFFFh

When the postscaler bits (T0OUTPS<3:0>) are set to 1:1 operation (no division), the T0IF Flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF Flag bit will be set every T0OUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE0 register = 1), the CPU will be interrupted and the device may wake from Sleep (see Section 26.5 "Operation During Sleep" for more details).

### 26.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see Section 13.0 "Peripheral Pin Select (PPS) Module" for additional information). The Timer0 output can also be used by other peripherals, such as the auto-conversion trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 Output bit (T0OUT) of the T0CON0 register (Register 26-3).

TMR0\_out will be one postscaled clock period when a match occurs between TMR0L and TMR0H in 8-bit mode, or when TMR0 rolls over in 16-bit mode. When a match condition occurs, the Timer0 output will toggle every T0OUTPS + 1 match. The total Timer0 period takes two match events to occur, and creates a 50% duty cycle output.

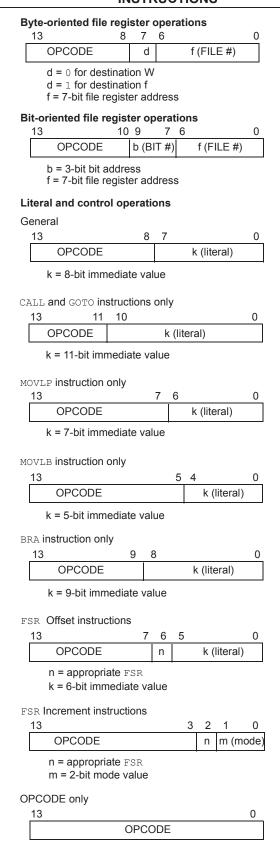

# FIGURE 34-1: GENERAL FORMAT FOR INSTRUCTIONS

| TRIS             | Load TRIS Register with W                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] TRIS f                                                                                                                         |

| Operands:        | $5 \leq f \leq 7$                                                                                                                        |

| Operation:       | $(W) \to TRIS \ register \ 'f'$                                                                                                          |

| Status Affected: | None                                                                                                                                     |

| Description:     | Move data from W register to TRIS register. When 'f' = 5, TRISA is loaded. When 'f' = 6, TRISB is loaded. When 'f' = 7, TRISC is loaded. |

| XORLW            | Exclusive OR literal with W                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] XORWF f,d                                                                                                                                                             |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

**TABLE 35-22: SPI MODE CHARACTERISTICS**

| Standard Operating Conditions (unless otherwise stated) |                       |                                          |               |       |              |       |                                                  |

|---------------------------------------------------------|-----------------------|------------------------------------------|---------------|-------|--------------|-------|--------------------------------------------------|

| Param.<br>No.                                           | Symbol                | Characteristic                           | Min.          | Тур.† | Max.         | Units | Conditions                                       |

| SP70*                                                   | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | 2.25*TcY      | _     | _            | ns    |                                                  |

| SP71*                                                   | TscH                  | SCK input high time (Slave mode)         | Tcy + 20      | _     | _            | ns    |                                                  |

| SP72*                                                   | TscL                  | SCK input low time (Slave mode)          | Tcy + 20      | _     | _            | ns    |                                                  |

| SP73*                                                   | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK edge | 100           | _     | _            | ns /  |                                                  |

| SP74*                                                   | TSCH2DIL,<br>TSCL2DIL | Hold time of SDI data input to SCK edge  | 100           | _     | _/           | ns    |                                                  |

| SP75*                                                   | TDOR                  | SDO data output rise time                | _             | 10    | <b>2</b> 5 < | ns    | 3.0∀ ≤ <b>Y</b> DD ≤ 5.5V                        |

|                                                         |                       |                                          | _             | 25    | 50           | ns    | 1.8∀ ≤ VDD ≤ 5.5V                                |

| SP76*                                                   | TDOF                  | SDO data output fall time                | _             | 10    | 25           | ns    |                                                  |

| SP77*                                                   | TssH2DoZ              | SS↑ to SDO output high-impedance         | 10            | (-    | 50_          | ns    |                                                  |

| SP78*                                                   | TscR                  | SCK output rise time                     | _             | 10    | 25_          | ng    | $3.0 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$ |

|                                                         |                       | (Master mode)                            | _ <u>,</u>    | 25    | 50           | ns    | $1.8V \leq V \text{DD} \leq 5.5V$                |

| SP79*                                                   | TscF                  | SCK output fall time (Master mode)       | $\overline{}$ | 10 \  | 25           | ns    |                                                  |

| SP80*                                                   | TscH2DoV,             | SDO data output valid after SCK          |               | _     | √50          | ns    | $3.0V \leq V \text{DD} \leq 5.5V$                |

|                                                         | TscL2DoV              | edge                                     |               |       | 145          | ns    | $1.8V \leq V \text{DD} \leq 5.5V$                |

| SP81*                                                   | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK edge        | 1, Tcy        |       | _            | ns    |                                                  |

| SP82*                                                   | TssL2DoV              | SDO data output valid after \$8 edge     |               | _     | 50           | ns    |                                                  |

| SP83*                                                   | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                      | 1.5 TcY + 40  | _     | _            | ns    |                                                  |

<sup>\*</sup> These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0 v. 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

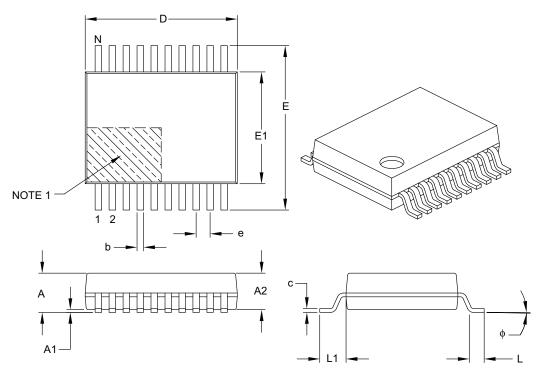

# 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS | 3        |  |  |  |  |

|--------------------------|------------------|----------|-------------|----------|--|--|--|--|

| Dimer                    | Dimension Limits |          |             | MAX      |  |  |  |  |

| Number of Pins           |                  |          | 20          |          |  |  |  |  |

| Pitch                    | е                |          | 0.65 BSC    | 0.65 BSC |  |  |  |  |

| Overall Height           | Α                | -        | _           | 2.00     |  |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85     |  |  |  |  |

| Standoff                 | A1               | 0.05     | -           | -        |  |  |  |  |

| Overall Width            | E                | 7.40     | 7.80        | 8.20     |  |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60     |  |  |  |  |

| Overall Length           | D                | 6.90     | 7.20        | 7.50     |  |  |  |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95     |  |  |  |  |

| Footprint                |                  | 1.25 REF |             |          |  |  |  |  |

| Lead Thickness           | С                | 0.09     | -           | 0.25     |  |  |  |  |

| Foot Angle               | ф                | 0°       | 4°          | 8°       |  |  |  |  |

| Lead Width               | b                | 0.22     | _           | 0.38     |  |  |  |  |

# Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (04/2016)

Initial release of the document.

# Revision B (04/2017)

Updated pin diagrams; Minor corrections to Table 1-1; Added "Guidelines for Getting Started With PIC16(L)F183XX" chapter; updated Figure 2-1; Added section 4.1.1.3 NVMREG Access; Section 4.2.1. BANK SELECTION; Updated ADACT Register; Added new Figure 4-8; Section 4.5.4 DATA EEPROM MEMORY; Updated Figure 18-2; Minor changes to all chapters.