# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18346-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |  |

|------------|----------------------------------------------------------|--|

| Address | Name       | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7 | Bit 6 | Bit 5       | Bit 4           | Bit 3            | Bit 2         | Bit 1 | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|----------------------------------|-------|-------|-------------|-----------------|------------------|---------------|-------|-----------|-----------------------|---------------------------------|

| Bank 2  | 8          |                                  |       |       |             |                 |                  |               |       |           |                       |                                 |

|         |            |                                  |       |       | CPU CORE RI | EGISTERS; see 1 | Table 4-2 for sp | ecifics       |       |           |                       |                                 |

| E0Ch    | _          | -                                |       |       |             | Unimple         | mented           |               |       |           | _                     | _                               |

| E0Dh    | —          | —                                |       |       |             | Unimple         | mented           |               |       |           | -                     | _                               |

| E0Eh    | —          | —                                |       |       |             | Unimple         | mented           |               |       |           | -                     | _                               |

| E0Fh    | PPSLOCK    |                                  | _     | —     | —           | —               | _                | _             | —     | PPSLOCKED | 0                     | (                               |

| E10h    | INTPPS     |                                  | _     | —     | —           |                 |                  | INTPPS<4:0>   |       |           | 0 0010                | u uuuu                          |

| E11h    | TOCKIPPS   |                                  | _     | —     | —           |                 |                  | T0CKIPPS<4:0> |       |           | 0 0010                | u uuuu                          |

| E12h    | T1CKIPPS   |                                  | —     | _     | —           |                 | T1CKIPPS<4:0>    |               |       |           | 0 0101                | u uuu                           |

| E13h    | T1GPPS     |                                  | _     | —     | —           | T1GPPS<4:0>     |                  |               |       | 0 0100    | u uuu                 |                                 |

| E14h    | CCP1PPS    |                                  | —     | _     | —           | CCP1PPS<4:0>    |                  |               |       |           | 1 0011                | u uuu                           |

| E15h    | CCP2PPS    |                                  | _     | —     | —           | CCP2PPS<4:0>    |                  |               |       |           | 1 0101                | u uuuu                          |

| E16h    | CCP3PPS    |                                  | —     | _     | —           |                 | CCP3PPS<4:0>     |               |       |           | 0 0010                | u uuu                           |

| E17h    | CCP4PPS    | X —                              | —     | —     | —           |                 |                  | CCP4PPS<4:0>  |       |           | 1 0001                | u uuu                           |

|         |            | — X                              | —     | _     | —           |                 |                  | CCP4PPS<4:0>  |       |           | 0 0100                | u uuuu                          |

| E18h    | CWG1PPS    |                                  | —     | —     | —           |                 |                  | CWG1PPS<4:0>  |       |           | 0 0010                | u uuuu                          |

| E19h    | CWG2PPS    |                                  | —     | _     | —           |                 |                  | CWG2PPS<4:0>  |       |           | 0 0010                | u uuuu                          |

| E1Ah    | MDCIN1PPS  |                                  | —     |       | —           |                 | Ν                | IDCIN1PPS<4:0 | >     |           | 1 0010                | u uuu                           |

| E1Bh    | MDCIN2PPS  |                                  | —     | _     | —           |                 | Ν                | IDCIN2PPS<4:0 | >     |           | 1 0101                | u uuu                           |

| E1Ch    | MDMINPPS   |                                  | _     | —     | —           |                 | I                | MDMINPPS<4:0> | •     |           | 1 0011                | u uuu                           |

| E1Dh    | SSP2CLKPPS | X —                              | —     | _     | —           |                 | S                | SP2CLKPPS<4:0 | )>    |           | 1 0100                | u uuu                           |

|         |            | — X                              | —     | —     | —           |                 | SSP2CLKPPS<4:0>  |               |       |           | 0 1111                | u uuu                           |

| E1Eh    | SSP2DATPPS | X —                              | _     | —     | —           | SSP2DATPPS<4:0> |                  |               |       | 1 0101    | u uuu                 |                                 |

|         |            | — X                              | —     | —     | —           |                 | S                | SP2DATPPS<4:0 | )>    |           | 0 1101                | u uuuu                          |

| E1Fh    | SSP2SSPPS  | Х —                              | —     | —     | —           |                 | 5                | SP2SSPPS<4:0  | >     |           | 0 0000                | u uuu                           |

|         |            | — X                              | —     | —     | —           |                 | S                | SP2SSPPS<4:0  | >     |           | 0 0001                | u uuu                           |

| E20h    | SSP1CLKPPS | X —                              | —     | _     | —           |                 | S                | SP1CLKPPS<4:0 | )>    |           | 1 0000                | u uuuu                          |

|         |            | — X                              | _     | —     | —           |                 | S                | SP1CLKPPS<4:0 | )>    |           | 0 1110                | u uuu                           |

PIC16(L)F18326/18346

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Only on PIC16F18326/18346.

2: Register accessible from both User and ICD Debugger.

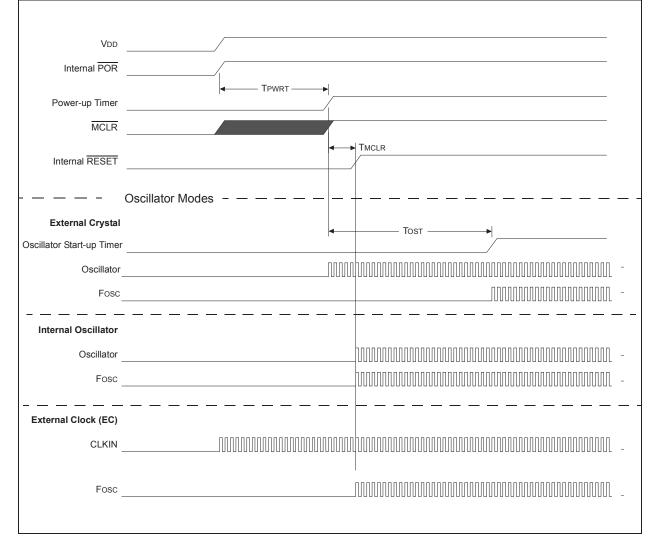

# 6.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

- 3. Oscillator start-up timer runs to completion (if required for oscillator source).

The total time out will vary based on oscillator configuration and Power-up Timer Configuration. See Section 7.0, Oscillator Module for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after ten Fosc cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

# 6.13 Register Definitions: Power Control

| R/W/HS-0/q       | R/W/HS-0/q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                 | R/W/HC-1/q     | R/W/HC-1/q     | R/W/HC-1/q                   | R/W/HC-q/u       | R/W/HC-q/u    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------|----------------|------------------------------|------------------|---------------|

| STKOVF           | STKUNF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —                                                   | RWDT           | RMCLR          | RI                           | POR              | BOR           |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |                |                |                              |                  | bit 0         |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |                |                |                              |                  |               |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |                |                |                              |                  |               |

| HC = Bit is clea | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | are                                                 |                | HS = Bit is se | et by hardware               |                  |               |

| R = Readable I   | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W = Writable                                        | bit            | U = Unimpler   | mented bit, read             | <b>as</b> '0'    |               |

| u = Bit is uncha | anged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | x = Bit is unki                                     | nown           | -m/n = Value   | at POR and BC                | R/Value at all o | other Resets  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '0' = Bit is cle                                    | ared           | q = Value dep  | pends on condit              | ion              |               |

| bit 7            | 1 = A Stack C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ick Overflow Fl<br>Overflow occur<br>Overflow has n | red            | has been clea  | red by firmware              |                  |               |

| bit 6            | 6 STKUNF: Stack Underflow Flag bit<br>1 = A Stack Underflow occurred<br>0 = A Stack Underflow has not occurred or has been cleared by firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |                |                |                              |                  |               |

| bit 5            | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ted: Read as '                                      | 0'             |                |                              |                  |               |

| bit 4            | 1 = A Watcho                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ndog Timer Re<br>dog Timer Res<br>dog Timer Res     | et has not occ |                | '1' by firmware<br>hardware) |                  |               |

| bit 3            | 1 = A MCLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _R Reset Flag<br>Reset has not<br>Reset has occ     | occurred or se |                |                              |                  |               |

| bit 2            | <b>RI:</b> RESET Instruction Flag bit<br>1 = A RESET instruction has not been executed or set to '1' by firmware<br>0 = A RESET instruction has been executed (cleared by hardware)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |                |                |                              |                  |               |

| bit 1            | <b>POR:</b> Power-on Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |                |                |                              |                  | s)            |

| bit 0            | <ul> <li>BOR: Brown-out Reset Status bit</li> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Routed (must be set in software after a Power-on Reset or Brown-out Routed (must be set in software after a Power-on Reset or Brown-out Routed (must be set in software after a Power-on Reset or Brown-out Routed (must be set in software after a Power-on Reset or Brown-out Routed (must be set in software after a Power-on Reset or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out Routed or Brown-out Routed or Brown-out Routed or Brown-out Routed (must be set in software after a Power-on Routed or Brown-out R</li></ul> |                                                     |                |                |                              |                  | own-out Reset |

#### REGISTER 6-2: PCON0: POWER CONTROL REGISTER 0

| <b>TABLE 6-5</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH RESETS |

|--------------------|---------------------------------------------|

|--------------------|---------------------------------------------|

| Name   | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|------------|-------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN |        |            | _     | _     | _     |       | BORRDY | 76                  |

| PCON0  | STKOVF | STKUNF | _          | RWDT  | RMCLR | RI    | POR   | BOR    | 77                  |

| STATUS | _      | _      | _          | TO    | PD    | Z     | DC    | С      | 30                  |

| WDTCON |        |        | WDTPS<4:0> |       |       |       |       | SWDTEN | 121                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

© 2016-2017 Microchip Technology Inc.

#### 7.2.2.3 Internal Oscillator Frequency Adjustment

The HFINTOSC and LFINTOSC internal oscillators are both factory-calibrated. TH HFINTOSC oscillator can be adjusted in software by writing to the OSCTUNE register (Register 7-3). OSCTUNE does not affect the LFINTOSC frequency.

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the HFINTOSC oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

# 7.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory-calibrated 31 kHz internal clock source.

The LFINTOSC is the clock source for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM). The LFINTOSC can also be used as the system clock, or as a clock or input source to certain peripherals.

The LFINTOSC is selected as the clock source through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register.

#### 7.2.2.5 Oscillator Status and Manual Enable

The 'ready' status of each oscillator is displayed in the OSCSTAT1 register (Register 7-4). The oscillators can also be manually enabled through the OSCEN register (Register 7-5). Manual enables make it possible to verify the operation of the EXTOSC or SOSC crystal oscillators. This can be achieved by enabling the selected oscillator, then watching the corresponding 'ready' state of the oscillator in the OSCSTAT1 register.

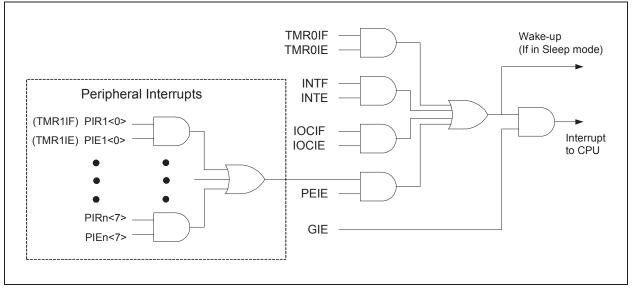

# 8.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 8-1.

#### FIGURE 8-1: INTERRUPT LOGIC

# 8.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIEx registers).

The PIR1, PIR2, PIR3 and PIR4 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 8.5 "Automatic Context Saving")

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | inte | rrupt | flag  | bits | s are | set,  |

|---------|-------------|------|-------|-------|------|-------|-------|

|         | regardless  | of   | the   | state | of   | any   | other |

|         | enable bits | -    |       |       |      |       |       |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 8.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. The interrupt is sampled during Q1 of the instruction cycle. The actual interrupt latency then depends on the instruction that is executing at the time the interrupt is detected. See Figure 8-2 and Figure 8-3 for more details.

| REGISTE      | R 8-3: PIE             | 1: PERIPHERA                                                       | L INTERRU                        | PT ENABLE           | REGISTER 1       |                  |             |

|--------------|------------------------|--------------------------------------------------------------------|----------------------------------|---------------------|------------------|------------------|-------------|

| R/W-0/       | 0 R/W-0/               | 0 R/W-0/0                                                          | R/W-0/0                          | R/W-0/0             | R/W-0/0          | R/W-0/0          | R/W-0/0     |

| TMR1G        | IE ADIE                | RCIE                                                               | TXIE                             | SSP1IE              | BCL1IE           | TMR2IE           | TMR1IE      |

| bit 7        |                        |                                                                    |                                  |                     |                  |                  | bit (       |

| Legend:      |                        |                                                                    |                                  |                     |                  |                  |             |

| R = Read     | able bit               | W = Writable                                                       | bit                              | U = Unimpler        | nented bit, read | d as '0'         |             |

| u = Bit is ı | unchanged              | x = Bit is unk                                                     | nown                             | -n/n = Value a      | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is | set                    | '0' = Bit is cle                                                   | ared                             |                     |                  |                  |             |

| bit 7        | 1 = Enabl              | : Timer1 Gate Inte<br>es the Timer1 gate<br>les the Timer1 gat     | e acquisition ir                 | nterrupt            |                  |                  |             |

| bit 6        | ADIE: An<br>1 = Enabl  | alog-to-Digital Cor<br>es the ADC interru<br>les the ADC interru   | verter (ADC)<br>upt              | -                   | e bit            |                  |             |

| bit 5        | 1 = Enabl              | SART Receive Int<br>es the EUSART re<br>les the EUSART re          | ceive interrup                   | t                   |                  |                  |             |

| bit 4        | 1 = Enabl              | SART Transmit Inf<br>es the EUSART tr<br>les the EUSART tr         | ansmit interru                   | ot                  |                  |                  |             |

| bit 3        | SSP1IE: S<br>1 = Enabl | Synchronous Seria<br>es the MSSP inter<br>les the MSSP inte        | al Port (MSSP)<br>rupt           | •                   | ole bit          |                  |             |

| bit 2        | BCL1IE:<br>1 = MSSF    | MSSP1 Bus Collis<br>P bus collision inter<br>P bus collision inter | ion Interrupt E<br>rrupt enabled |                     |                  |                  |             |

| bit 1        | TMR2IE:<br>1 = Enabl   | TMR2 to PR2 Mat<br>es the Timer2 to P<br>les the Timer2 to P       | ch Interrupt Er<br>R2 match inte | nable bit<br>errupt |                  |                  |             |

| bit 0        | TMR1IE:<br>1 = Enabl   | Timer1 Overflow I<br>es the Timer1 ove<br>les the Timer1 ove       | nterrupt Enablerflow interrupt   | e bit               |                  |                  |             |

| Note:        |                        | e INTCON register                                                  |                                  |                     |                  |                  |             |

# REGISTER 8-3: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0              | R/W-0/0 | R/W-0/0            | R/W-0/0 | U-0            | U-0              | U-0              | U-0         |

|----------------------|---------|--------------------|---------|----------------|------------------|------------------|-------------|

| WPUB7                | WPUB6   | WPUB5              | WPUB4   |                | —                | —                | —           |

| bit 7                |         | •                  |         |                | •                |                  | bit 0       |

|                      |         |                    |         |                |                  |                  |             |

| Legend:              |         |                    |         |                |                  |                  |             |

| R = Readable         | bit     | W = Writable       | bit     | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unchanged |         | x = Bit is unknown |         | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set     |         | '0' = Bit is clea  | ared    |                |                  |                  |             |

|                      |         |                    |         |                |                  |                  |             |

#### REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER

| bit 7-4 | WPUB<7:4>: Weak Pull-up Register bits |

|---------|---------------------------------------|

|         | 1 = Weak Pull-up enabled              |

|         | 0 = Weak Pull-up disabled             |

| bit 3-0 | Unimplemented: Read as '0'            |

#### REGISTER 12-14: ODCONB: PORTB OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| ODCB7   | ODCB6   | ODCB5   | ODCB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 **ODCB<7:4>:** PORTB Open-Drain Configuration bits For RB<7:4> pins, respectively: 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

bit 3-0 Unimplemented: Read as '0'

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0                                               | U-0                                | U-0 | U-0 | U-0   |  |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|------------------------------------|-----|-----|-------|--|

| IOCBN7                                  | IOCBN6  | IOCBN5            | IOCBN4                                                | —                                  | —   | —   | —     |  |

| bit 7                                   |         |                   |                                                       |                                    |     |     | bit 0 |  |

|                                         |         |                   |                                                       |                                    |     |     |       |  |

| Legend:                                 |         |                   |                                                       |                                    |     |     |       |  |

| R = Readable I                          | bit     | W = Writable I    | bit                                                   | U = Unimplemented bit, read as '0' |     |     |       |  |

| u = Bit is unchanged x = Bit is unknown |         | own               | -n/n = Value at POR and BOR/Value at all other Resets |                                    |     |     |       |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |                                    |     |     |       |  |

# REGISTER 15-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER<sup>(1)</sup>

| bit 7-4 | <b>IOCBN&lt;7:4&gt;:</b> Interrupt-on-Change PORTB Negative Edge Enable bits<br>1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>be set upon detecting an edge.</li><li>0 = Interrupt-on-Change disabled for the associated pin</li></ul>                                                                     |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                           |

|         |                                                                                                                                                                                      |

# **Note 1:** PIC16(L)F18346 only.

# **REGISTER 15-6:** IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER<sup>(1)</sup>

| R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------|------------|------------|------------|-----|-----|-----|-------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | _   | —   | —   | —     |

| bit 7      |            |            |            |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-4 **IOCBF<7:4>:** Interrupt-on-Change PORTB Flag bits 1 = An enabled change was detected on the associated pin

Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

0 = No change was detected, or the user cleared the detected change.

#### bit 3-0 Unimplemented: Read as '0'

**Note 1:** PIC16(L)F18346 only.

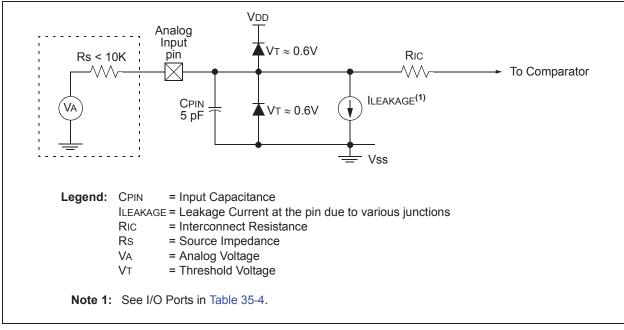

# 18.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, may have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will provide an input based on their level as either a TTL or ST input buffer.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 18-3: ANALOG INPUT MODEL

# 20.11 Register Definitions: CWG Control

| R/W/HC-0/0<br>LD <sup>(1)</sup><br>it<br>nged<br>EN: CWGx E                    | U-0<br>—<br>W = Writable I<br>x = Bit is unkn<br>'0' = Bit is clea                                        | iown                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0<br>MODE<2:0><br>d as '0'<br>DR/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0/0<br>bit 0                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| it<br>nged<br><b>EN:</b> CWGx E                                                | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nged                                                                           | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |