Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18346t-i-gz |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|------------|----------------------------------------------------------|

|------------|----------------------------------------------------------|

| Address | Name                                            | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------------------|----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| Bank 30 |                                                 |                                  |       |       |       |       |       |       |       |       |                       |                                 |

|         | CPU CORE REGISTERS; see Table 4-2 for specifics |                                  |       |       |       |       |       |       |       |       |                       |                                 |

PIC16(L)F18326/18346

| F0Ch | —        | — |          |               |          | Unimple       | mented   |          |              |          | —         | —         |  |

|------|----------|---|----------|---------------|----------|---------------|----------|----------|--------------|----------|-----------|-----------|--|

| F0Dh | —        | - |          | Unimplemented |          |               |          |          |              |          |           | _         |  |

| F0Eh | -        | — |          |               |          | Unimplemented |          |          |              |          |           | _         |  |

| F0Fh | CLCDATA  |   | _        | —             | _        | —             | MLC4OUT  | MLC3OUT  | MLC2OUT      | MLC1OUT  | 0000      | 0000      |  |

| F10h | CLC1CON  |   | LC1EN    | —             | LC10UT   | LC1INTP       | LC1INTN  |          | LC1MODE<2:0> | >        | 0-00 0000 | 0-00 0000 |  |

| F11h | CLC1POL  |   | LC1POL   | _             | —        | —             | LC1G4POL | LC1G3POL | LC1G2POL     | LC1G1POL | 0 xxxx    | 0 uuuu    |  |

| F12h | CLC1SEL0 |   | _        | —             |          |               | LC1D1    | S<5:0>   |              |          | xx xxxx   | uu uuuu   |  |

| F13h | CLC1SEL1 |   | —        | —             |          | LC1D2S<5:0>   |          |          |              |          |           |           |  |

| F14h | CLC1SEL2 |   | _        | —             |          | LC1D3S<5:0>   |          |          |              |          |           |           |  |

| F15h | CLC1SEL3 |   | _        | —             |          | LC1D4S<5:0>   |          |          |              |          |           | uu uuuu   |  |

| F16h | CLC1GLS0 |   | LC1G1D4T | LC1G1D4N      | LC1G1D3T | LC1G1D3N      | LC1G1D2T | LC1G1D2N | LC1G1D1T     | LC1G1D1N | XXXX XXXX | uuuu uuuu |  |

| F17h | CLC1GLS1 |   | LC1G2D4T | LC1G2D4N      | LC1G2D3T | LC1G2D3N      | LC1G2D2T | LC1G2D2N | LC1G2D1T     | LC1G2D1N | XXXX XXXX | uuuu uuuu |  |

| F18h | CLC1GLS2 |   | LC1G3D4T | LC1G3D4N      | LC1G3D3T | LC1G3D3N      | LC1G3D2T | LC1G3D2N | LC1G3D1T     | LC1G3D1N | XXXX XXXX | uuuu uuuu |  |

| F19h | CLC1GLS3 |   | LC1G4D4T | LC1G4D4N      | LC1G4D3T | LC1G4D3N      | LC1G4D2T | LC1G4D2N | LC1G4D1T     | LC1G4D1N | XXXX XXXX | uuuu uuuu |  |

| F1Ah | CLC2CON  |   | LC2EN    | —             | LC2OUT   | LC2INTP       | LC2INTN  |          | LC2MODE<2:0> | >        | 0-00 0000 | 0-00 0000 |  |

| F1Bh | CLC2POL  |   | LC2POL   | —             | _        | —             | LC2G4POL | LC2G3POL | LC2G2POL     | LC2G1POL | 0 xxxx    | 0 uuuu    |  |

| F1Ch | CLC2SEL0 |   | _        | —             |          |               | LC2D1    | S<5:0>   |              |          | xx xxxx   | uu uuuu   |  |

| F1Dh | CLC2SEL1 |   | —        | —             |          |               | LC2D2    | S<5:0>   |              |          | xx xxxx   | uu uuuu   |  |

| F1Eh | CLC2SEL2 |   | _        | —             |          |               | LC2D3    | S<5:0>   |              |          | xx xxxx   | uu uuuu   |  |

| F1Fh | CLC2SEL3 |   | _        | —             |          |               | LC2D4    | S<5:0>   |              |          | xx xxxx   | uu uuuu   |  |

|      | 01020210 |   |          |               |          | 1 1 1 (a)     |          |          |              |          |           | uu uu     |  |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Only on PIC16F18326/18346. Legend:

Note 1:

2: Register accessible from both User and ICD Debugger.

# 6.3 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) circuit provides alternative protection against Brown-out conditions. When VDD falls below the LPBOR threshold, the device is held in Reset. When this occurs, the BOR bit of the PCON0 register is cleared to indicate that a Brown-out Reset occurred. The BOR bit will be cleared when either the BOR or the LPBOR circuitry detects a BOR condition. The LPBOR feature can be used with or without BOR enabled.

When used while BOR is enabled, the LPBOR can be used as a secondary protection circuit in case the BOR circuit fails to detect the BOR condition. Additionally, when BOR is enabled except while in Sleep (BOREN<1:0> = 10), the LPBOR circuit will hold the device in Reset while VDD is lower than the LPBOR threshold, and will also re-arm the POR. (see Figure 35-11 for LPBOR Reset voltage levels).

When used without BOR enabled, the LPBOR circuit provides a single Reset trip point with the benefit of reduced current consumption.

#### 6.3.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

#### 6.3.1.1 LPBOR Module Output

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is OR'd together with the Reset signal of the BOR module to provide the generic BOR signal, which goes to the PCON register and to the power control block.

# 6.4 MCLR

The  $\overline{\text{MCLR}}$  is an <u>optional</u> external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

TABLE 6-2:

MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

# 6.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

Note: A Reset does not drive the MCLR pin low.

# 6.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 12.2** "**PORTA Registers**" for more information.

# 6.5 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register as well as the RWDT bit in the PCON register, are changed to indicate the WDT Reset. See **Section 10.0 "Watchdog Timer (WDT)"** for more information.

# 6.6 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

# 6.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 4.4 "Stack**" for more information.

# 6.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a device Reset had just occurred.

# 6.9 Power-up Timer

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note *AN607*, *Power-up Trouble Shooting* (DS00607).

| R/W-1/u                                                                                       | R/W-0-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |  |  |  |

|-----------------------------------------------------------------------------------------------|----------|-----|-----|-----|-----|-----|--------|--|--|--|

| SBOREN <sup>(1)</sup>                                                                         | Reserved | —   | —   | —   | —   | —   | BORRDY |  |  |  |

| bit 7 bit 0                                                                                   |          |     |     |     |     |     |        |  |  |  |

|                                                                                               |          |     |     |     |     |     |        |  |  |  |

| Legend:                                                                                       |          |     |     |     |     |     |        |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                          |          |     |     |     |     |     |        |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |          |     |     |     |     |     |        |  |  |  |

q = Value depends on condition

#### **BORCON: BROWN-OUT RESET CONTROL REGISTER** REGISTER 6-1:

'0' = Bit is cleared

| bit 7   | <b>SBOREN:</b> Software Brown-out Reset Enable bit <sup>(1)</sup><br><u>If BOREN &lt;1:0&gt; in Configuration Words <math>\neq 01</math>:</u><br>SBOREN is read/write, but has no effect on the BOR.<br>If BOREN <1:0> in Configuration Words = 01: |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = BOR Enabled<br>0 = BOR Disabled                                                                                                                                                                                                                 |

| bit 6   | Reserved: Bit must be maintained as '0'                                                                                                                                                                                                             |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                          |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit                                                                                                                                                                                                    |

|         | <ul><li>1 = The Brown-out Reset circuit is active</li><li>0 = The Brown-out Reset circuit is inactive</li></ul>                                                                                                                                     |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

#### 6.12 **Power Control (PCON) Register**

The Power Control (PCON) register contains flag bits to differentiate between a:

Power-on Reset (POR)

1' = Bit is set

- Brown-out Reset (BOR)

- RESET Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON0 register bits are shown in Register 6-2.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 6-4).

Software should reset the bit to the inactive state after the restart (hardware will not reset the bit).

Software may also set any PCON bit to the active state, so that user code may be tested, but no Reset action will be generated.

# 8.3 Interrupts During Sleep

All interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 9.0** "**Power-Saving Operation Modes**" for more details.

# 8.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the PIE0 register. The INTEDG bit of the INTCON register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the PIR0 register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

# 8.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

## 9.2.3 LOW-POWER SLEEP MODE

The PIC16F18326/18346 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC16F18326/18346 allows the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. Depending on the configuration of this bit, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

#### 9.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 9.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- External interrupt pin/Interrupt-on-change pins

- Timer 1 (with external clock source)

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

Note: The PIC16LF18326/18346 does not have a configurable Low-Power Sleep mode. PIC16LF18326/18346 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC16F18326/18346. See Section 35.0 "Electrical Specifications" for more information.

# 11.2 Data EEPROM

Data EEPROM consists of 256 bytes of user data memory. The EEPROM provides storage locations for 8-bit user defined data.

EEPROM can be read and/or written through:

- FSR/INDF indirect access (Section 11.3 "FSR and INDF Access")

- NVMREG access (Section 11.4 "NVMREG Access")

- In-Circuit Serial Programming (ICSP)

Unlike Program Flash Memory, which must be written to by row, EEPROM can be written to byte-by-byte.

# 11.3 FSR and INDF Access

The FSR and INDF registers allow indirect access to the Program Flash Memory or EEPROM.

#### 11.3.1 FSR READ

With the intended address loaded into an FSR register, a MOVIW instruction or read of INDF will read data from the Program Flash Memory or EEPROM. The CPU operation is suspended during the read, and resumes immediately after. Read operations return a single word of memory. When the MSB of the FSR (ex: FSRxH) is set to 0x70, the lower 8-bit address value (in FSRxL) determines the EEPROM location that may be read from (through the INDF register). In other words, the EEPROM address range 0x00-0xFF is mapped into the FSR address space between 0x7000-0x70FF. Writing to the EEPROM cannot be accomplished via the FSR/INDF interface.

#### 11.3.2 FSR WRITE

Writing/erasing the NVM through the FSR registers (ex. MOVWI instruction) is not supported in the PIC16(L)F18326/18346 devices.

# 11.4 NVMREG Access

The NVMREG interface allows read/write access to all the locations accessible by FSRs, and also read/write access to the User ID locations and EEPROM, and read-only access to the device identification, revision, and Configuration data.

Reading, writing, or erasing of NVM via the NVMREG interface is prevented when the device is code-protected.

#### 11.4.1 NVMREG READ OPERATION

To read a NVM location using the NVMREG interface, the user must:

- Clear the NVMREGS bit of the NVMCON1 register if the user intends to access Program Flash Memory locations, or set NVMREGS if the user intends to access User ID, Configuration, or EEPROM locations.

- 2. Write the desired address into the NVMADRH:NVMADRL register pair (Table 11-2).

- 3. Set the RD bit of the NVMCON1 register to initiate the read.

Once the read control bit is set, the CPU operation is suspended during the read, and resumes immediately after. The data is available in the very next cycle, in the NVMDATH:NVMDATL register pair; therefore, it can be read as two bytes in the following instructions.

NVMDATH:NVMDATL register pair will hold this value until another read or until it is written to by the user.

Upon completion, the RD bit is cleared by hardware.

# 12.4 PORTB Registers (PIC16(L)F18346 Only)

## 12.4.1 DATA REGISTER

PORTB is a 4-bit wide bidirectional port and is only available in the PIC16(L)F18346 devices. The corresponding data direction register is TRISB (Register 12-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 12-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read; this value is modified and then written to the PORT data latch (LATB).

The PORT data latch LATB (Register 12-11) holds the output port data, and contains the latest value of a LATB or PORTB write.

# 12.4.2 DIRECTION CONTROL

The TRISB register (Register 12-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 12.4.3 INPUT THRESHOLD CONTROL

The INLVLB register (Register 12-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 35-4 for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 12.4.4 OPEN-DRAIN CONTROL

The ODCONB register (Register 12-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

# 12.4.5 SLEW RATE CONTROL

The SLRCONB register (Register 12-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, the corresponding port pin drive slews at the maximum rate possible.

#### 12.4.6 ANALOG CONTROL

The ANSELB register (Register 12-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

# 12.4.7 WEAK PULL-UP CONTROL

The WPUB register (Register 12-13) controls the individual weak pull-ups for each PORT pin.

#### 12.4.8 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 13.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| R/W/HS-0/0                                                                                                                                                                                                                                                    | R/W/HS-0/0            | R/W/HS-0/0      | R/W/HS-0/0 | R/W/HS-0/0     | R/W/HS-0/0    | R/W/HS-0/0       | R/W/HS-0/0  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|------------|----------------|---------------|------------------|-------------|--|--|--|--|--|

| IOCCF7 <sup>(1)</sup>                                                                                                                                                                                                                                         | IOCCF6 <sup>(1)</sup> | IOCCF5          | IOCCF4     | IOCCF3         | IOCCF2        | IOCCF1           | IOCCF0      |  |  |  |  |  |

| bit 7                                                                                                                                                                                                                                                         | bit 7 bit 0           |                 |            |                |               |                  |             |  |  |  |  |  |

|                                                                                                                                                                                                                                                               |                       |                 |            |                |               |                  |             |  |  |  |  |  |

| Legend:                                                                                                                                                                                                                                                       |                       |                 |            |                |               |                  |             |  |  |  |  |  |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$                                                                                                                                                                                      |                       |                 |            |                |               |                  |             |  |  |  |  |  |

| u = Bit is und                                                                                                                                                                                                                                                | hanged                | x = Bit is unkr | nown       | -n/n = Value a | at POR and BO | R/Value at all c | ther Resets |  |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared HS - Bit is set in hardware                                                                                                                                                                                             |                       |                 |            |                |               |                  |             |  |  |  |  |  |

| bit 7-6                                                                                                                                                                                                                                                       |                       |                 |            |                |               |                  |             |  |  |  |  |  |

| bit 5-0 <b>IOCCF&lt;5:0&gt;:</b> Interrupt-on-Change PORTC Flag bits<br>1 = An enabled change was detected on the associated pin.<br>Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a<br>falling edge was detected on RCx. |                       |                 |            |                |               |                  |             |  |  |  |  |  |

#### REGISTER 15-9: IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER

0 = No change was detected, or the user cleared the detected change.

**Note 1:** PIC16(L)F18346 only.

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|--------|---------|--------|--------|--------|--------|---------------------|

| ANSELA                | _                     | _                     | ANSA4  | ANSA4   | _      | ANSA2  | ANSA1  | ANSA0  | 144                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5  | ANSB4   | —      | —      | —      | —      | 150                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5  | ANSC4   | ANSC3  | ANSC2  | ANSC1  | ANSC0  | 157                 |

| TRISA                 | _                     | —                     | TRISA5 | TRISA4  | (2)    | TRISA2 | TRISA1 | TRISA0 | 143                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5 | TRISB4  | _      | —      | _      | —      | 149                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5 | TRISC4  | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 155                 |

| INTCON                | GIE                   | PEIE                  | _      | —       | _      | —      | _      | INTEDG | 100                 |

| PIE0                  | _                     | —                     | TMR0IE | IOCIE   | _      | —      | _      | INTE   | 101                 |

| IOCAP                 | _                     | _                     | IOCAP5 | IOCAP4  | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 174                 |

| IOCAN                 | _                     | —                     | IOCAN5 | IOCAN4  | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 174                 |

| IOCAF                 | _                     | _                     | IOCAF5 | IOCAF4  | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 175                 |

| IOCBP <sup>(1)</sup>  | IOCBP7                | IOCBP6                | IOCBP5 | IOCBP4  | _      |        |        |        | 175                 |

| IOCBN <sup>(1)</sup>  | IOCBN7                | IOCBN6                | IOCBN5 | IOCBN4  | _      |        |        |        | 176                 |

| IOCBF <sup>(1)</sup>  | IOCBF7                | IOCBF6                | IOCBF5 | IIOCBF4 | —      | —      | —      | —      | 176                 |

| IOCCP                 | IOCCP7 <sup>(1)</sup> | IOCCP6 <sup>(1)</sup> | IOCCP5 | IOCCP4  | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 177                 |

| IOCCN                 | IOCCN7 <sup>(1)</sup> | IOCCN6 <sup>(1)</sup> | IOCCN5 | IOCCN4  | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 177                 |

| IOCCF                 | IOCCF7 <sup>(1)</sup> | IOCCF6 <sup>(1)</sup> | IOCCF5 | IOCCF4  | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 178                 |

#### TABLE 15-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

**Note 1:** PIC16(L)F18346 only.

2: Unimplemented, read as '1'.

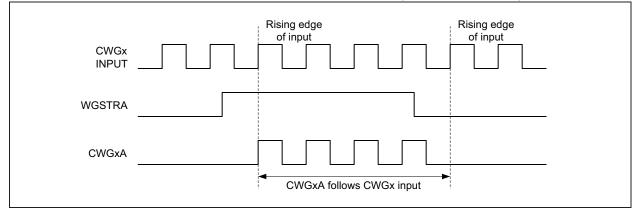

#### 20.2.3.1 Synchronous Steering Mode

In Synchronous Steering mode (MODE<2:0> bits = 001, Register 20-1), changes to steering selection registers take effect on the next rising edge of the modulated data input (Figure 20-3). In Synchronous Steering mode, the output will always produce a complete waveform.

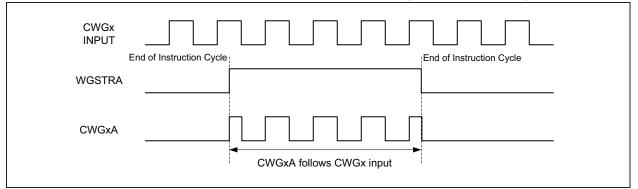

#### 20.2.3.2 Asynchronous Steering Mode

In Asynchronous mode (MODE<2:0> bits = 000, Register 20-1), steering takes effect at the end of the instruction cycle that writes to WGxSTR. In Asynchronous Steering mode, the output signal may be an incomplete waveform (Register 20-4). This operation may be useful when the user firmware needs to immediately remove a signal from the output pin.

#### FIGURE 20-4: EXAMPLE OF ASYNCHRONOUS STEERING (MODE<2:0> = 000)

#### 20.2.3.3 Start-up Considerations

The application hardware must use the proper external pull-up and/or pull-down resistors on the CWG output pins. This is required because all I/O pins are forced to high-impedance at Reset.

The POLy bits (Register 20-2) allow the user to choose whether the output signals are active-high or active-low.

© 2016-2017 Microchip Technology Inc.

#### **REGISTER 22-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u                                                                                       | R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u |

|-----------------------------------------------------------------------------------------------|---------|--------------|---------|--------------|------------------|----------|---------|

|                                                                                               |         |              | ADRE    | S<9:2>       |                  |          |         |

| bit 7                                                                                         |         |              |         |              |                  |          | bit 0   |

|                                                                                               |         |              |         |              |                  |          |         |

| Legend:                                                                                       |         |              |         |              |                  |          |         |

| R = Readable                                                                                  | bit     | W = Writable | bit     | U = Unimpler | nented bit, read | d as '0' |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |         |              |         |              |                  |          |         |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

'1' = Bit is set

#### **REGISTER 22-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

'0' = Bit is cleared

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | S<1:0>  | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| R = Readable bit V     | V = Writable bit    | U = Unimplemented bit, read as '0'                    |

|------------------------|---------------------|-------------------------------------------------------|

| u = Bit is unchanged x | c = Bit is unknown  | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set '0    | 0' = Bit is cleared |                                                       |

bit 7-6 **ADRES<1:0>**: ADC Result Register bits Lower two bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

# 25.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

# 25.6 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

# 25.7 Modulated Output Polarity

The modulated output signal provided on the DSM pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

# 25.8 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the SLR bit of the SLRCON register associated with that pin. For example, clearing the slew rate limitation for pin RA5 would require clearing the SLRA5 bit of the SLRCONA register.

# 25.9 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

# 25.10 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

#### 26.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system oscillator (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

## 26.2 Clock Source Selection

The T0CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 26-4 displays the clock source selections.

#### 26.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, Timer0 operates as a timer and will increment on multiples of the clock source, as determined by the Timer0 prescaler.

# 26.2.2 EXTERNAL CLOCK SOURCE

When an external clock source is selected, Timer0 can operate as either a timer or a counter. Timer0 will increment on multiples of the rising edge of the external clock source, as determined by the Timer0 prescaler.

#### 26.3 Programmable Prescaler

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the T0CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register, the T0CON0 register, or the T0CON1 register.

#### 26.4 Programmable Postscaler

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the T0OUTPS<3:0> bits of the T0CON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register, the T0CON0 register, or the T0CON1 register.

# 26.5 Operation During Sleep

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

## 26.6 Timer0 Interrupts

The Timer0 Interrupt Flag bit (TMR0IF) is set when either of the following conditions occur:

- 8-bit TMR0L matches the TMR0H value

- 16-bit TMR0 rolls over from FFFFh

When the postscaler bits (TOOUTPS<3:0>) are set to 1:1 operation (no division), the TOIF Flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF Flag bit will be set every TOOUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE0 register = 1), the CPU will be interrupted and the device may wake from Sleep (see Section 26.5 "Operation During Sleep" for more details).

# 26.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see Section 13.0 "Peripheral Pin Select (PPS) Module" for additional information). The Timer0 output can also be used by other peripherals, such as the auto-conversion trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 Output bit (T0OUT) of the T0CON0 register (Register 26-3).

TMR0\_out will be one postscaled clock period when a match occurs between TMR0L and TMR0H in 8-bit mode, or when TMR0 rolls over in 16-bit mode. When a match condition occurs, the Timer0 output will toggle every T0OUTPS + 1 match. The total Timer0 period takes two match events to occur, and creates a 50% duty cycle output.

#### EQUATION 29-2: PULSE WIDTH

| Pulse Width = | (CCPRxH. | • CCPRxL register pair) |

|---------------|----------|-------------------------|

|               | Tora     | (TMD) Duran la Valua)   |

TOSC • (TMR2 Prescale Value)

# EQUATION 29-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$

The CCPRxH:CCPRxL register pair and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering provides glitchless PWM operation.

The 8-bit timer TMR2/4/6 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 29-4).

## 29.4.6 PWM RESOLUTION

PWM resolution, expressed in number of bits, defines the maximum number of discrete steps that can be present in a single PWM period. For example, a 10-bit resolution will result in 1024 discrete steps, whereas an 8-bit resolution will result in 256 discrete steps.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 29-4.

# EQUATION 29-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| IABLE 29-1: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|-------------|---------------------------------------------------------|

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 29-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 29.4.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2/4/6 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2/4/6 will continue from its previous state.

#### 29.4.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 7.0 "Oscillator Module"** for additional details.

#### 29.4.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

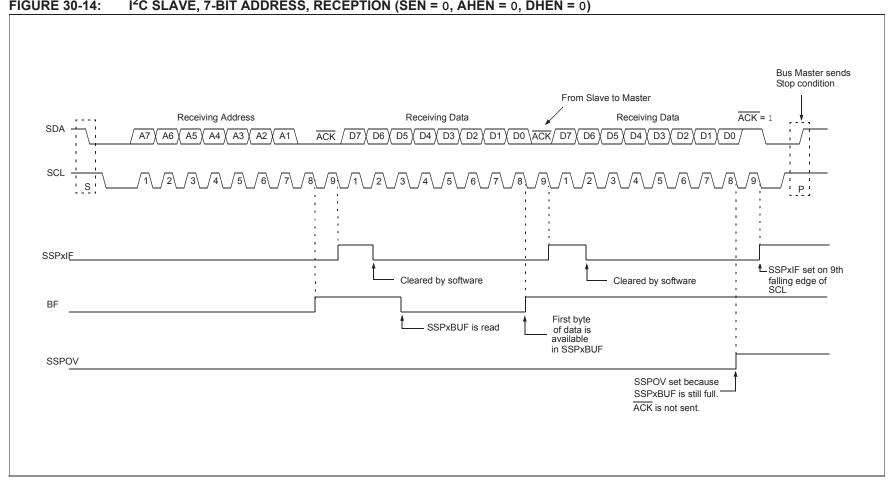

#### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 0, DHEN = 0) FIGURE 30-14:

PIC16(L)F18326/18346

| R/W-1/1                           | R/W-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-1/1                                               | R/W-1/1        | R/W-1/1                                         | R/W-1/1                               | R/W-1/1                     | R/W-1/1      |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------|-------------------------------------------------|---------------------------------------|-----------------------------|--------------|

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       | SSPxN          | /ISK<7:0>                                       |                                       |                             |              |

| bit 7                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |                |                                                 |                                       |                             | bit 0        |

| Legend:                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |                |                                                 |                                       |                             |              |

| R = Readable bit W = Writable bit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |                | U = Unimpler                                    | nented bit, read                      | l as '0'                    |              |

| u = Bit is und                    | u = Bit is unchanged x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       | nown           | -n/n = Value a                                  | at POR and BO                         | R/Value at all o            | other Resets |

| '1' = Bit is se                   | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '0' = Bit is cle                                      | ared           |                                                 |                                       |                             |              |

| bit 7-1                           | 1 = The rec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7:1>: Mask bits<br>eived address b<br>eived address b | oit n is compa | red to SPPxADI<br>ed to detect I <sup>2</sup> C | D <n> to detect<br/>address match</n> | l <sup>2</sup> C address ma | atch         |

| bit 0                             | <ul> <li>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</li> <li>SSPxMSK&lt;0&gt;: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address</li> <li>I<sup>2</sup>C Slave mode, 10-bit address (SSPM&lt;3:0&gt; = 0111 or 1111):</li> <li>1 = The received address bit 0 is compared to SPPxADD&lt;0&gt; to detect I<sup>2</sup>C address match</li> <li>0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match</li> <li>I<sup>2</sup>C Slave mode, 7-bit address:</li> </ul> |                                                       |                |                                                 |                                       |                             |              |

#### REGISTER 30-5: SSPxMSK: SSP MASK REGISTER

# REGISTER 30-6: SSPxADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

|                 |         |                  |         |              |                  | ``       | ,       |

|-----------------|---------|------------------|---------|--------------|------------------|----------|---------|

| R/W-0/0         | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|                 |         |                  | SSPxAD  | DD<7:0>      |                  |          |         |

| bit 7           |         |                  |         |              |                  |          | bit 0   |

|                 |         |                  |         |              |                  |          |         |

| Legend:         |         |                  |         |              |                  |          |         |

| R = Readable bi | t       | W = Writable bit |         | U = Unimpler | nented bit, read | l as '0' |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode:

| bit 7-0 | SSPxADD<7:0>: Baud Rate Clock Divider bits      |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### 10-bit Slave mode – Most Significant Address Byte:

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 SSPxADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 10-bit Slave mode – Least Significant Address Byte:

bit 7-0 SSPxADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-bit Slave mode:

| bit 7-1 SSPxADD<7:1>: 7-bit addres | SS |

|------------------------------------|----|

|------------------------------------|----|

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

# 31.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See Section 7.2.2.3 "Internal Oscillator Frequency Adjustment" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section 31.3.1 "Auto-Baud Detect"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

# 31.3 EUSART1 Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART1 operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUD1CON register selects 16-bit mode.

The SP1BRGH, SP1BRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TX1STA register and the BRG16 bit of the BAUD1CON register. In Synchronous mode, the BRGH bit is ignored.

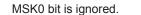

Table 31-1 contains the formulas for determining the baud rate. Example 31-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 31-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SP1BRGH, SP1BRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

# EXAMPLE 31-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit SPR1BRG:

$Desired Baud Rate = \frac{Fosc}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SP1BRGH:SP1BRGL:

# 31.5 EUSART1 Operation During Sleep

The EUSART1 will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

# 31.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RC1STA and TX1STA Control registers must be configured for Synchronous Slave Reception (see Section 31.4.2.4 "Synchronous Slave Reception Setup").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RC1REG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 31.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RC1STA and TX1STA Control registers must be configured for synchronous slave transmission (see Section 31.4.2.2 "Synchronous Slave Transmission Setup").

- The TXIF interrupt flag must be cleared by writing the output data to the TX1REG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TX1REG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TX1REG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

# TABLE 35-8: OSCILLATOR PARAMETERS<sup>(1)</sup>

| Standard Operating Conditions (unless otherwise stated) |          |                                              |              |                          |              |            |                          |  |

|---------------------------------------------------------|----------|----------------------------------------------|--------------|--------------------------|--------------|------------|--------------------------|--|

| Param.<br>No.                                           | Sym.     | Characteristic                               | Min.         | Typ.†                    | Max.         | Units      | Conditions               |  |

| OS20                                                    | FHFOSC   | Precision Calibrated HFINTOSC<br>Frequency   | 3.92         | 4                        | 4.08         | MHz        | 25°C                     |  |

| OS20                                                    | FHFOSC   | Precision Calibrated HFINTOSC<br>Frequency   | _            | 4<br>8<br>12<br>16<br>32 |              | MHz        | -40°C to 125°C (2)       |  |

| OS21                                                    | FHFOSCLP | Low-Power Optimized HFINTOSC<br>Frequency    | 0.93<br>1.86 | 1<br>2                   | 1.07<br>2.14 | MHz<br>MHz |                          |  |

| OS23                                                    | Flfosc   | Internal LFINTOSC Frequency                  | _            | 31                       | _            | kHz ∢      |                          |  |

| OS24                                                    | THFOSCST | HFINTOSC Wake-up from Sleep<br>Start-up Time | -            | 11<br>50                 | 20           | μs<br>μs   | VREGPM = 0<br>VREGPM = 1 |  |

| OS26                                                    | TLFOSCST | LFINTOSC Wake-up from Sleep<br>Start-up Time | _            | 0.2                      | $-\langle$   | ms         |                          |  |

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

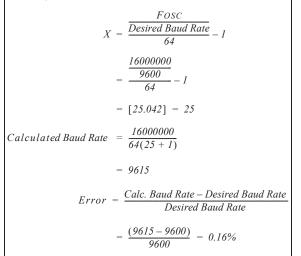

**2:** See Figure 35-6.

FIGURE 35-6: PRECISION CALIBRATED HEINTOSC FREQUENCY ACCURACY OVER DEVICE

#### TABLE 35-22: SPI MODE CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated) |                       |                                                                                |              |                           |      |       |                                  |  |  |

|---------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------|--------------|---------------------------|------|-------|----------------------------------|--|--|

| Param.<br>No.                                           | Symbol                | Characteristic                                                                 | Min.         | Typ.†                     | Max. | Units | Conditions                       |  |  |

| SP70*                                                   | TssL2scH,<br>TssL2scL | $\overline{\mathrm{SS}}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | 2.25*Tcy     |                           |      | ns    |                                  |  |  |

| SP71*                                                   | TscH                  | SCK input high time (Slave mode)                                               | Tcy + 20     | —                         | _    | ns    | $\land$                          |  |  |

| SP72*                                                   | TscL                  | SCK input low time (Slave mode)                                                | Tcy + 20     | —                         | _    | ns    |                                  |  |  |

| SP73*                                                   | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK edge                                       | 100          | _                         | _    | ns _  |                                  |  |  |

| SP74*                                                   | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                                        | 100          | —                         |      | ns    |                                  |  |  |

| SP75*                                                   | TDOR                  | SDO data output rise time                                                      |              | 10                        | 25 < | ns    | <del>3.0∀ ≤ V</del> DD ≤ 5.5V    |  |  |

|                                                         |                       |                                                                                |              | 25                        | 50   | nş    | 1.8∀ ≤ VDD ≤ 5.5V                |  |  |

| SP76*                                                   | TDOF                  | SDO data output fall time                                                      | —            | 10                        | 25   | ns    |                                  |  |  |

| SP77*                                                   | TssH2doZ              | SS↑ to SDO output high-impedance                                               | 10           | (-                        | -50_ | ns    | /                                |  |  |

| SP78*                                                   | TscR                  | SCK output rise time                                                           |              | 10                        | 25   | ns    | $3.0V \le V\text{DD} \le 5.5V$   |  |  |

|                                                         |                       | (Master mode)                                                                  | — <u> </u>   | 25                        | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |  |  |

| SP79*                                                   | TscF                  | SCK output fall time (Master mode)                                             | $\prec$      | 10 \                      | 25   | ns    |                                  |  |  |

| SP80*                                                   | TscH2doV,             | SDO data output valid after SCK                                                | \            |                           | √50  | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |  |  |

|                                                         | TscL2doV              | edge                                                                           |              | $\rightarrow \rightarrow$ | 145  | ns    | $1.8V \le V\text{DD} \le 5.5V$   |  |  |

| SP81*                                                   | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK edge                                              | 1 TCY        |                           | _    | ns    |                                  |  |  |

| SP82*                                                   | TssL2doV              | SDO data output valid after SS<br>edge                                         | $\int f$     | _                         | 50   | ns    |                                  |  |  |

| SP83*                                                   | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                            | 1.5 TCY + 40 | —                         | —    | ns    |                                  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.