Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

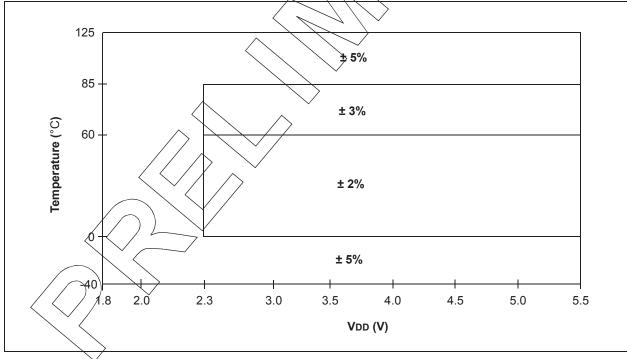

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18346t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16(L)F18326/18346

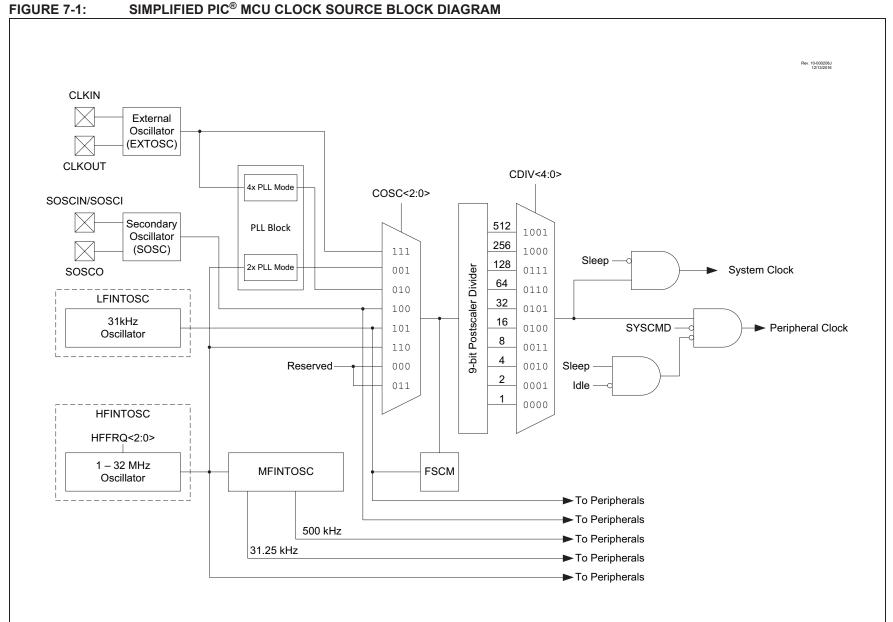

# 7.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

There is also a secondary oscillator block which is optimized for a 32.768 kHz external clock source, which can be used as an alternate clock source.

There are two internal oscillator blocks:

- HFINTOSC

- LFINTOSC

The HFINTOSC can produce clock frequencies from 1-16 MHz. The LFINTOSC generates a 31 kHz clock frequency.

There is a PLL that can be used by the external oscillator. See **Section 7.2.1.4 "4x PLL"** for more details. Additionally, there is a PLL that can be used by the HFINTOSC at certain frequencies. See **Section 7.2.2.2 "2x PLL"** for more details.

#### 7.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> and NDIV<3:0> bits in the OSCCON1 register to switch the system clock source.

See **Section 7.3 "Clock Switching"** for more information.

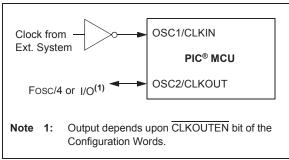

# 7.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the CLKIN input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 7-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, <= 32 MHz

- ECM Medium power, <= 8 MHz

- ECL Low power, <= 0.1 MHz</li>

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

# 11.5 Register Definitions: Program Flash Memory Control REGISTER 11-1: NVMDATL: NONVOLATILE MEMORY DATA LOW BYTE REGISTER

|                                   |         |                    |         |                                    | LON DITE       | ILE OIO I EIL      |         |

|-----------------------------------|---------|--------------------|---------|------------------------------------|----------------|--------------------|---------|

| R/W-0/0                           | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                            | R/W-0/0        | R/W-0/0            | R/W-0/0 |

|                                   |         |                    | NVME    | )AT<7:0>                           |                |                    |         |

| bit 7                             |         |                    |         |                                    |                |                    | bit 0   |

|                                   |         |                    |         |                                    |                |                    |         |

| Legend:                           |         |                    |         |                                    |                |                    |         |

| R = Readable bit W = Writable bit |         |                    | it      | U = Unimplemented bit, read as '0' |                |                    |         |

| u = Bit is unchar                 | nged    | x = Bit is unkno   | wn      | -n/n = Value a                     | t POR and BOR/ | Value at all other | Resets  |

| '1' = Bit is set                  |         | '0' = Bit is clear | ed      |                                    |                |                    |         |

bit 7-0

NVMDAT<7:0>: Read/Write Value for Least Significant bits of Program Memory

# REGISTER 11-2: NVMDATH: NONVOLATILE MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|----------|---------|---------|

| —     | —   |         |         | NVMDA   | AT<13:8> |         |         |

| bit 7 |     |         |         |         |          |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-0 | <b>NVMDAT&lt;13:8&gt;:</b> Read/Write Value for Most Significant bits of Program Memory <sup>(1)</sup> |

|---------|--------------------------------------------------------------------------------------------------------|

|         | it in bit i total tinto talao for moot orgimoant bit of thogram monory                                 |

**Note 1:** This byte is ignored when writing to EEPROM.

#### REGISTER 11-3: NVMADRL: NONVOLATILE MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-------------|---------|---------|---------|---------|---------|---------|

|         | NVMADR<7:0> |         |         |         |         |         |         |

| bit 7   | bit 7 bit 0 |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

NVMADR<7:0>: Specifies the Least Significant bits for Program Memory Address

#### REGISTER 11-4: NVMADRH: NONVOLATILE MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| _     |         |         |         | NVMADR<14:8 | }>      |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 NVMADR<14:8>: Specifies the Most Significant bits for Program Memory Address

| U-0                                     | U-0                             | R/W-1/1                                                                                                                                             | R/W-1/1                                               | U-0              | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|---------|---------|---------|

| _                                       | —                               | SLRA5                                                                                                                                               | SLRA4                                                 |                  | SLRA2   | SLRA1   | SLRA0   |

| bit 7                                   |                                 |                                                                                                                                                     |                                                       |                  |         |         | bit 0   |

|                                         |                                 |                                                                                                                                                     |                                                       |                  |         |         |         |

| Legend:                                 |                                 |                                                                                                                                                     |                                                       |                  |         |         |         |

| R = Readable bit W = Writable bit       |                                 | bit                                                                                                                                                 | U = Unimpler                                          | mented bit, read | as '0'  |         |         |

| u = Bit is unchanged x = Bit is unknown |                                 | nown                                                                                                                                                | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |         |         |

| '1' = Bit is set '0' = Bit is cleared   |                                 |                                                                                                                                                     |                                                       |                  |         |         |         |

|                                         |                                 |                                                                                                                                                     |                                                       |                  |         |         |         |

| bit 7-6                                 | Unimplemen                      | ted: Read as '                                                                                                                                      | 0'                                                    |                  |         |         |         |

| bit 5-4                                 |                                 |                                                                                                                                                     |                                                       |                  |         |         |         |

|                                         |                                 | lews at maxim                                                                                                                                       |                                                       |                  |         |         |         |

| bit 3                                   | it 3 Unimplemented: Read as '0' |                                                                                                                                                     |                                                       |                  |         |         |         |

| bit 2-0                                 | For RA<2:0><br>1 = Port pin s   | SLRA<2:0>: PORTA Slew Rate Enable bits<br>For RA<2:0> pins, respectively<br>1 = Port pin slew rate is limited<br>0 = Port pin slews at maximum rate |                                                       |                  |         |         |         |

# REGISTER 12-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

#### REGISTER 12-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 INLVLA<5:0>: PORTA Input Level Select bits

For RA<5:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

| R/W-1/1              | R/W-1/1                                                                                           | R/W-1/1            | R/W-1/1 | R/W-1/1                            | R/W-1/1       | R/W-1/1        | R/W-1/1      |  |

|----------------------|---------------------------------------------------------------------------------------------------|--------------------|---------|------------------------------------|---------------|----------------|--------------|--|

| ANSC7 <sup>(1)</sup> | ANSC6 <sup>(1)</sup>                                                                              | ANSC5              | ANSC4   | ANSC3                              | ANSC2         | ANSC1          | ANSC0        |  |

| bit 7                |                                                                                                   | ·                  |         |                                    |               |                | bit          |  |

|                      |                                                                                                   |                    |         |                                    |               |                |              |  |

| Legend:              |                                                                                                   |                    |         |                                    |               |                |              |  |

| R = Readable bit     |                                                                                                   | W = Writable bit   |         | U = Unimplemented bit, read as '0' |               |                |              |  |

| u = Bit is unchanged |                                                                                                   | x = Bit is unknown |         | -n/n = Value a                     | at POR and BO | R/Value at all | other Resets |  |

| '1' = Bit is set     | '0' = Bit is cleared                                                                              |                    | ared    |                                    |               |                |              |  |

|                      |                                                                                                   |                    |         |                                    |               |                |              |  |

| bit 7-6              |                                                                                                   |                    |         |                                    |               |                |              |  |

|                      | 1 = Analog input. Pin is assigned as analog input <sup>(2)</sup> . Digital input buffer disabled. |                    |         |                                    |               |                |              |  |

# **REGISTER 12-20: ANSELC: PORTC ANALOG SELECT REGISTER**

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- **ANSC<5:0>**: Analog Select between Analog or Digital Function on pins RC<5:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled. bit 5-0

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- Note 1: PIC16(L)F18346 only; otherwise read as '0'.

- 2: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# REGISTER 12-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-0/0              | R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| WPUC7 <sup>(1)</sup> | WPUC6 <sup>(1)</sup> | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7                | •                    |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | WPUC<7:6> <sup>(1)</sup> : Weak Pull-up Register bits <sup>(2)</sup><br>1 = Pull-up enabled<br>0 = Pull-up disabled |

|---------|---------------------------------------------------------------------------------------------------------------------|

| bit 5-0 | WPUC<5:0>: Weak Pull-up Register bits <sup>(2)</sup><br>1 = Pull-up enabled<br>0 = Pull-up disabled                 |

Note 1: PIC16(L)F18346 only; otherwise read as '0'.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

# 20.11 Register Definitions: CWG Control

| R/W/HC-0/0<br>LD <sup>(1)</sup><br>it<br>nged<br>EN: CWGx E                                                                                                                                                                    | U-0<br>—<br>W = Writable I<br>x = Bit is unkn<br>'0' = Bit is clea                                        | iown                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0<br>MODE<2:0><br>d as '0'<br>DR/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0/0<br>bit 0                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| it<br>nged<br><b>EN:</b> CWGx E                                                                                                                                                                                                | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nged                                                                                                                                                                                                                           | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nged                                                                                                                                                                                                                           | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                            |

| nged                                                                                                                                                                                                                           | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EN: CWGx E                                                                                                                                                                                                                     | '0' = Bit is clea                                                                                         |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                                                                | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                |                                                                                                           | ared                                                                                                                                                                                                                                     | HS/HC = Bit                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                | nable bit                                                                                                 |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                        | is set/cleared b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | y hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 = CWGX is<br>0 = CWGX is                                                                                                                                                                                                     | enabled                                                                                                   |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>LD: CWG Load Buffers bit<sup>(1)</sup></li> <li>1 = Dead-band count buffers to be loaded on CWG data rising edge following first falling edge after this bit is set.</li> <li>0 = Buffers remain unchanged</li> </ul> |                                                                                                           |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Unimplemen                                                                                                                                                                                                                     | ted: Read as 'o                                                                                           | )'                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 111 = Reser<br>110 = Reser<br>101 = CWG<br>100 = CWG<br>011 = CWG<br>010 = CWG                                                                                                                                                 | ved<br>ved<br>outputs operate<br>outputs operate<br>outputs operate<br>outputs operate<br>outputs operate | e in Push-Pull<br>e in Half-Bridg<br>e in Reverse f<br>e in Forward f<br>e in Synchron                                                                                                                                                   | ge mode<br>Full-Bridge mod<br>Full-Bridge mod<br>lous Steering m                                                                                                                                                                                                                                                       | de<br>node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                | MODE<2:0>:<br>111 = Reser<br>100 = Reser<br>101 = CWG<br>100 = CWG<br>111 = CWG<br>100 = CWG<br>100 = CWG | MODE<2:0>: CWGx Mode b<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate<br>100 = CWG outputs operate<br>101 = CWG outputs operate<br>100 = CWG outputs operate<br>100 = CWG outputs operate<br>100 = CWG outputs operate | MODE<2:0>: CWGx Mode bits<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate in Push-Pul<br>100 = CWG outputs operate in Half-Bridg<br>111 = CWG outputs operate in Reverse<br>101 = CWG outputs operate in Forward I<br>101 = CWG outputs operate in Synchron<br>100 = CWG outputs operate in Asynchron | MODE<2:0>: CWGx Mode bits<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>111 = CWG outputs operate in Reverse Full-Bridge mode<br>102 = CWG outputs operate in Forward Full-Bridge mode<br>103 = CWG outputs operate in Synchronous Steering mode<br>104 = CWG outputs operate in Asynchronous Steering mode<br>105 = CWG outputs operate in Asynchronous Steering mode<br>106 = CWG outputs operate in Asynchronous Steering mode<br>107 = CWG outputs operate in Asynchronous Steering mode<br>108 = CWG outputs operate in Asynchronous Steering mode<br>109 = CWG outputs operate in Asynchronous Steering mode<br>100 = CWG outputs operate in Asynchronous Steering | MODE<2:0>: CWGx Mode bits<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>111 = CWG outputs operate in Reverse Full-Bridge mode<br>102 = CWG outputs operate in Forward Full-Bridge mode<br>103 = CWG outputs operate in Synchronous Steering mode<br>104 = CWG outputs operate in Asynchronous Steering mode<br>105 = CWG outputs operate in Asynchronous Steering mode | MODE<2:0>: CWGx Mode bits         11 = Reserved         10 = Reserved         01 = CWG outputs operate in Push-Pull mode         00 = CWG outputs operate in Half-Bridge mode         011 = CWG outputs operate in Reverse Full-Bridge mode         011 = CWG outputs operate in Reverse Full-Bridge mode         010 = CWG outputs operate in Forward Full-Bridge mode         010 = CWG outputs operate in Synchronous Steering mode |

# REGISTER 20-1: CWGxCON0: CWGx CONTROL REGISTER 0

**Note 1:** This bit can only be set after EN = 1; it cannot be set in the same cycle when EN is set.

|                 | 20-2. 000                                                                                                |                                |                |                |                  |                  |             |

|-----------------|----------------------------------------------------------------------------------------------------------|--------------------------------|----------------|----------------|------------------|------------------|-------------|

| U-0             | U-0                                                                                                      | R-x                            | U-0            | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

| _               | —                                                                                                        | IN                             | —              | POLD           | POLC             | POLB             | POLA        |

| bit 7           |                                                                                                          |                                |                |                |                  | ·                | bit (       |

| Legend:         |                                                                                                          |                                |                |                |                  |                  |             |

| R = Readab      | le bit                                                                                                   | W = Writable                   | bit            | U = Unimpler   | mented bit, read | l as '0'         |             |

| u = Bit is une  | changed                                                                                                  | x = Bit is unk                 | nown           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is se | et                                                                                                       | '0' = Bit is cle               | eared          | q = Value de   | pends on condit  | ion              |             |

|                 |                                                                                                          |                                |                |                |                  |                  |             |

| bit 7-6         | Unimplem                                                                                                 | ented: Read as                 | '0'            |                |                  |                  |             |

| bit 5           | IN: CWGx                                                                                                 | Data Input Signa               | ll (read-only) |                |                  |                  |             |

| bit 4           | Unimplem                                                                                                 | Unimplemented: Read as '0'     |                |                |                  |                  |             |

| bit 3           | POLD: WG                                                                                                 | SxD Output Polar               | ity bit        |                |                  |                  |             |

|                 | •                                                                                                        | output is inverted             |                |                |                  |                  |             |

|                 | •                                                                                                        | output is normal               |                |                |                  |                  |             |

| bit 2           | POLC: WGxC Output Polarity bit                                                                           |                                |                |                |                  |                  |             |

|                 | 1 = Signal output is inverted polarity                                                                   |                                |                |                |                  |                  |             |

| 1.11 A          | •                                                                                                        | output is normal               |                |                |                  |                  |             |

| bit 1           |                                                                                                          | POLB: WGxB Output Polarity bit |                |                |                  |                  |             |

|                 | 1 = Signal output is inverted polarity<br>0 = Signal output is normal polarity                           |                                |                |                |                  |                  |             |

| bit 0           | 0                                                                                                        | SxA Output Polar               | . ,            |                |                  |                  |             |

|                 |                                                                                                          |                                | 5              |                |                  |                  |             |

|                 | <ul> <li>1 = Signal output is inverted polarity</li> <li>0 = Signal output is normal polarity</li> </ul> |                                |                |                |                  |                  |             |

#### REGISTER 20-2: CWGxCON1: CWGx CONTROL REGISTER 1

# REGISTER 20-3: CWGxCLKCON: CWGx CLOCK INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|-----|---------|

| —     | _   | _   | _   | —   | —   | _   | CS      |

| bit 7 |     |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-1 Unimplemented: Read as '0'

CS: CWG Clock Source Selection Select bits

| WGCLK | Clock Source                              |

|-------|-------------------------------------------|

| 0     | Fosc                                      |

| 1     | HFINTOSC (remains operating during Sleep) |

bit 0

| REGISTER 2                                                                                                |                                                  | A31. CWG A                       |                |                 | NOL NEGIST       |                  |              |  |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------|----------------|-----------------|------------------|------------------|--------------|--|

| U-0                                                                                                       | U-0                                              | U-0                              | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

| _                                                                                                         | —                                                | —                                | AS4E           | AS3E            | AS2E             | AS1E             | AS0E         |  |

| bit 7                                                                                                     |                                                  |                                  |                |                 |                  | •                | bit C        |  |

| Legend:                                                                                                   |                                                  |                                  |                |                 |                  |                  |              |  |

| R = Readable                                                                                              | bit                                              | W = Writable                     | bit            | U = Unimpler    | mented bit, read | l as '0'         |              |  |

| u = Bit is unch                                                                                           | anged                                            | x = Bit is unkr                  | Iown           | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is set                                                                                          |                                                  | '0' = Bit is clea                | ared           | q = Value de    | pends on condit  | ion              |              |  |

|                                                                                                           |                                                  |                                  |                |                 |                  |                  |              |  |

| bit 7-5                                                                                                   | Unimplemen                                       | ted: Read as '                   | )'             |                 |                  |                  |              |  |

| bit 4                                                                                                     | AS4E: CWG                                        | Auto-Shutdowr                    | n Source 4 (CL | .C4) Enable bit | I                |                  |              |  |

|                                                                                                           | 1 = Auto-shutdown for CLC4 is enabled            |                                  |                |                 |                  |                  |              |  |

|                                                                                                           |                                                  | utdown for CLC                   |                |                 |                  |                  |              |  |

| bit 3                                                                                                     |                                                  | Auto-Shutdowr                    | (              | ,               | :                |                  |              |  |

|                                                                                                           |                                                  | utdown from Cl<br>utdown from Cl |                | -               |                  |                  |              |  |

| bit 2                                                                                                     |                                                  | Auto-Shutdowr                    |                | -               |                  |                  |              |  |

|                                                                                                           |                                                  | utdown from Co                   | ``             | /               |                  |                  |              |  |

|                                                                                                           |                                                  | utdown from Co                   |                |                 |                  |                  |              |  |

| bit 1                                                                                                     | AS1E: CWG Auto-Shutdown Source 1 (C1) Enable bit |                                  |                |                 |                  |                  |              |  |

| 1 = Auto-shutdown from Comparator 1 is enabled                                                            |                                                  |                                  |                |                 |                  |                  |              |  |

|                                                                                                           |                                                  |                                  |                |                 |                  |                  |              |  |

| bit 0                                                                                                     |                                                  | Auto-Shutdowr                    | •              | ,               | ole bit          |                  |              |  |

| <ol> <li>Auto-shutdown from CWGxPPS is enabled</li> <li>Auto-shutdown from CWGxPPS is disabled</li> </ol> |                                                  |                                  |                |                 |                  |                  |              |  |

|                                                                                                           | 0 = Auto-shi                                     |                                  | NGXFP3 IS UI   | Sableu          |                  |                  |              |  |

# REGISTER 20-7: CWGxAS1: CWG AUTO-SHUTDOWN CONTROL REGISTER 1

#### REGISTER 20-8: CWGxDBR: CWGx RISING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   |         |         | DBR     | <5:0>   |         |         |

| bit 7 | •   |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                             |                             |  |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz 16 MHz               |                             | 8 MHz                       | 4 MHz                       | 1 MHz                       |  |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |  |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |  |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |  |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |  |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(2)</sup>      |  |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(2)</sup>      | 64.0 μs <sup>(2)</sup>      |  |  |

| ADCRC               | x11         | 1.0-6.0 μs <sup>(1,4)</sup> |  |  |

# TABLE 22-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

**Note 1:** See TAD parameter for ADCRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the ADCRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

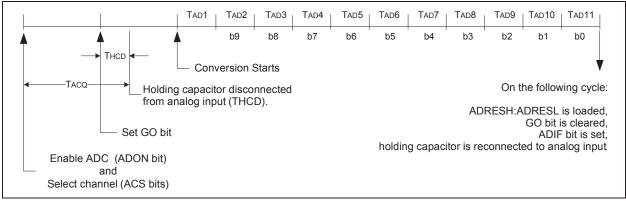

# FIGURE 22-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

# PIC16(L)F18326/18346

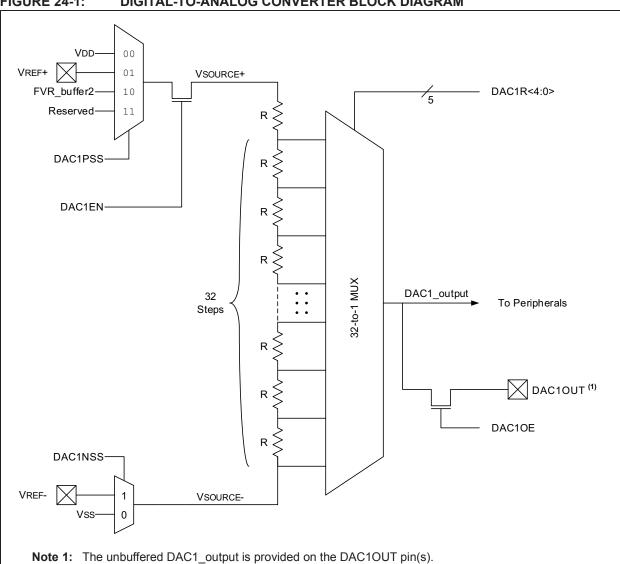

# FIGURE 24-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

# 25.0 DATA SIGNAL MODULATOR (DSM) MODULE

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of key modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- Carrier Source Polarity Select

- Carrier Source Pin Disable

- Programmable Modulator Data

- Modulator Source Pin Disable

- Modulated Output Polarity Select

- Slew Rate Control

Figure 25-1 shows a simplified block diagram of the Data Signal Modulator peripheral.

# 26.0 TIMER0 MODULE

The Timer0 module is an 8/16-bit timer/counter with the following features:

- 16-bit timer/counter

- 8-bit timer/counter with programmable period

- Synchronous or asynchronous operation

- · Selectable clock sources

- Programmable prescaler (independent of Watchdog Timer)

- · Programmable postscaler

- Operation during Sleep mode

- · Interrupt on match or overflow

- Output on I/O pin (via PPS) or to other peripherals

# 26.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

When used with an FOSC/4 clock source, the module is a timer and increments on every instruction cycle. When used with any other clock source, the module can be used as either a timer or a counter and increments on every rising edge of the external source.

#### 26.1.1 16-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

# 26.1.1.1 Timer0 Reads and Writes in 16-bit Mode