Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

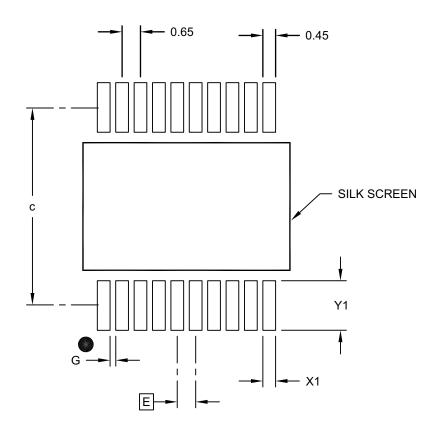

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18326-i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F18326/18346

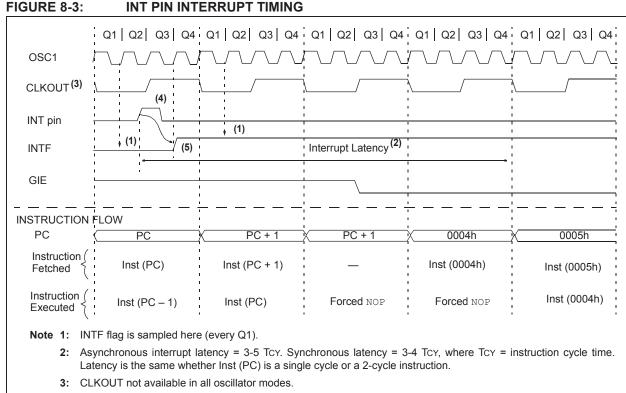

4: For minimum width of INT pulse, refer to AC specifications in Section 35.0 "Electrical Specifications"".

**5:** INTF is enabled to be set any time during the Q4-Q1 cycles.

|                  |                                                                                                                           |                                                           |                 |              | REGISTER 4       |                  |             |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|--------------|------------------|------------------|-------------|--|

| R/W-0/0          | R/W-0/0                                                                                                                   | R/W-0/0                                                   | R/W-0/0         | R/W-0/0      | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |

| CWG2IE           | CWG1IE                                                                                                                    | TMR5GIE                                                   | TMR5IE          | CCP4IE       | CCP3IE           | CCP2IE           | CCP1IE      |  |

| bit 7            |                                                                                                                           |                                                           | L.              | 1            |                  |                  | bit (       |  |

|                  |                                                                                                                           |                                                           |                 |              |                  |                  |             |  |

| Legend:          |                                                                                                                           |                                                           |                 |              |                  |                  |             |  |

| R = Readable     | bit                                                                                                                       | W = Writable                                              | bit             | U = Unimplei | mented bit, read | l as '0'         |             |  |

| u = Bit is unch  | anged                                                                                                                     | x = Bit is unknown                                        |                 | -n/n = Value | at POR and BO    | R/Value at all c | ther Resets |  |

| '1' = Bit is set |                                                                                                                           | '0' = Bit is clea                                         | ared            | HS = Hardwa  | are set          |                  |             |  |

| bit 7            | 1 = CWG2 int                                                                                                              | /G 2 Interrupt E<br>terrupt enabled<br>terrupt not enal   |                 |              |                  |                  |             |  |

| bit 6            | CWG1IE: CWG 1 Interrupt Enable bit<br>1 = CWG1 interrupt enabled<br>0 = CWG1 interrupt not enabled                        |                                                           |                 |              |                  |                  |             |  |

| bit 5            | TMR5GIE: Timer5 Gate Interrupt Enable bit<br>1 = TMR5 Gate interrupt is enabled<br>0 = TMR5 Gate interrupt is not enabled |                                                           |                 |              |                  |                  |             |  |

| bit 4            | 1 = TMR5 ove                                                                                                              | R5 Overflow Int<br>erflow interrupt<br>erflow interrupt   | is enabled      |              |                  |                  |             |  |

| bit 3            | 1 = CCP4 inte                                                                                                             | P4 Interrupt Ena<br>errupt is enable<br>errupt is not ena | d               |              |                  |                  |             |  |

| bit 2            | 1 = CCP3 inte                                                                                                             | P3 Interrupt En<br>errupt is enable<br>errupt is not en   | d               |              |                  |                  |             |  |

| bit 1            | 1 = CCP2 in                                                                                                               | P2 Interrupt En<br>Iterrupt is enab<br>Iterrupt is not e  | led             |              |                  |                  |             |  |

| bit 0            | CCP1IE: CCF                                                                                                               | P1 Interrupt En<br>Interrupt is enab                      | able bit<br>led |              |                  |                  |             |  |

#### **REGISTER 8-6: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4**

# 11.0 NONVOLATILE MEMORY (NVM) CONTROL

NVM is separated into two types: Program Flash Memory and Data EEPROM.

NVM is accessible by using both the FSR and INDF registers, or through the NVMREG register interface.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways; by either code protection or write protection.

Code protection (CP and CPD bits in Configuration Word 4) disables access, reading and writing, to both the Program Flash Memory and EEPROM via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be Reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits, and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Program Flash Memory, as defined by the WRT<1:0> bits of Configuration Word 3. Write protection does not affect a device programmer's ability to read, write, or erase the device.

## 11.1 Program Flash Memory

Program Flash Memory consists of 16,384 14-bit words as user memory, with additional words for User ID information, Configuration Words, and interrupt vectors. Program Flash Memory provides storage locations for:

- User program instructions

- User defined data

Program Flash Memory data can be read and/or written to through:

- CPU instruction fetch (read-only)

- FSR/INDF indirect access (read-only) (Section 11.3 "FSR and INDF Access")

- NVMREG access (Section 11.4 "NVMREG Access"

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

Read operations return a single word of memory. When write and erase operations are done on a row basis, the row size is defined in Table 11-1. Program Flash Memory will erase to a logic '1' and program to a logic '0'.

#### TABLE 11-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device         | Row Erase<br>(words) | Write<br>Latches<br>(words) |  |

|----------------|----------------------|-----------------------------|--|

| PIC16(L)F18326 | 32                   | 32                          |  |

| PIC16(L)F18346 | 52                   | 52                          |  |

It is important to understand the Program Flash Memory structure for erase and programming operations. Program Flash Memory is arranged in rows. A row consists of 32 14-bit program memory words. A row is the minimum size that can be erased by user software.

All or a portion of a row can be programmed. Data to be written into the program memory row is written to 14-bit wide data write latches. These latches are not directly accessible to the user, but may be loaded via sequential writes to the NVMDATH:NVMDATL register pair.

| Note: | To modify only a partian of a provinyaly     |

|-------|----------------------------------------------|

| Note: | To modify only a portion of a previously     |

|       | programmed row, then the contents of the     |

|       | entire row must be read and saved in         |

|       | RAM prior to the erase. Then, the new        |

|       | data and retained data can be written into   |

|       | the write latches to reprogram the row of    |

|       | Program Flash Memory. Any                    |

|       | unprogrammed locations can be written        |

|       | without first erasing the row. In this case, |

|       | it is not necessary to save and rewrite the  |

|       | other previously programmed locations        |

#### 11.1.1 PROGRAM MEMORY VOLTAGES

The Program Flash Memory is readable and writable during normal operation over the full VDD range.

#### 11.1.1.1 Programming Externally

The program memory cell and control logic support write and Bulk Erase operations down to the minimum device operating voltage.

#### 11.1.1.2 Self-Programming

The program memory cell and control logic will support write and row erase operations across the entire VDD range. Bulk Erase is not supported when self-programming.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |  |

|---------|---------|---------|---------|---------|-------|-------|-------|-------|---------------------|--|

| PORTB   | RB7     | RB6     | RB5     | RB4     |       | _     | _     |       | 149                 |  |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | _     |       |       | _     | 149                 |  |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | —     | _     | _     | —     | 150                 |  |

| ANSELB  | ANSB7   | ANSB6   | ANSB5   | ANSB4   | —     | _     | _     | —     | 150                 |  |

| WPUB    | WPUB7   | WPU6    | WPUB5   | WPUB4   | _     |       |       | _     | 151                 |  |

| ODCONB  | ODCB7   | ODCB6   | ODCB5   | ODCB4   | —     | _     | _     | _     | 151                 |  |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | _     |       | _     | _     | 152                 |  |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | _     |       | _     | _     | 152                 |  |

#### TABLE 12-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

| R/W-0/0              | R/W-0/0                                                                                                                                                                                                                                                        | R/W-0/0           | R/W-0/0 | R/W-0/0      | R/W-0/0                                               | R/W-0/0 | R/W-0/0 |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|--------------|-------------------------------------------------------|---------|---------|--|--|

| ODCC7 <sup>(1)</sup> | ODCC6 <sup>(1)</sup>                                                                                                                                                                                                                                           | ODCC5             | ODCC4   | ODCC3        | ODCC2                                                 | ODCC1   | ODCC0   |  |  |

| bit 7                |                                                                                                                                                                                                                                                                |                   |         |              |                                                       |         |         |  |  |

|                      |                                                                                                                                                                                                                                                                |                   |         |              |                                                       |         |         |  |  |

| Legend:              |                                                                                                                                                                                                                                                                |                   |         |              |                                                       |         |         |  |  |

| R = Readable b       | bit                                                                                                                                                                                                                                                            | W = Writable I    | oit     | U = Unimpler | nented bit, read                                      | as '0'  |         |  |  |

| u = Bit is uncha     | u = Bit is unchanged x = Bit is unknown                                                                                                                                                                                                                        |                   |         |              | -n/n = Value at POR and BOR/Value at all other Resets |         |         |  |  |

| '1' = Bit is set     |                                                                                                                                                                                                                                                                | '0' = Bit is clea | ared    |              |                                                       |         |         |  |  |

| bit 7-6<br>bit 5-0   | bit 7-6 <b>ODCC&lt;7:6&gt;</b> : PORTC Open-Drain Enable bits <sup>(1)</sup><br>For RC<7:6> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |                   |         |              |                                                       |         |         |  |  |

#### REGISTER 12-22: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

Note 1: PIC16(L)F18346 only; otherwise read as '0'.

### REGISTER 12-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| SLRC7 <sup>(1)</sup> | SLRC6 <sup>(1)</sup> | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | <b>SLRC&lt;7:6&gt;:</b> PORTC Slew Rate Enable bits <sup>(1)</sup><br>For RC<7:6> pins, respectively<br>1 = Port pin slew rate is limited<br>0 = Port pin slews at maximum rate |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-0 | SLRC<5:0>: PORTC Slew Rate Enable bits<br>For RC<5:0> pins, respectively<br>1 = Port pin slew rate is limited<br>0 = Port pin slews at maximum rate                             |

Note 1: PIC16(L)F18346 only; otherwise read as '0'.

# 20.11 Register Definitions: CWG Control

| R/W/HC-0/0<br>LD <sup>(1)</sup><br>it<br>nged<br>EN: CWGx E                    | U-0<br>—<br>W = Writable I<br>x = Bit is unkn<br>'0' = Bit is clea                                        | iown                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0<br>MODE<2:0><br>d as '0'<br>DR/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0/0<br>bit 0                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| it<br>nged<br><b>EN:</b> CWGx E                                                | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nged                                                                           | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nged                                                                           | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                            |

| nged                                                                           | x = Bit is unkn<br>'0' = Bit is clea                                                                      | iown                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                         | at POR and BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EN: CWGx E                                                                     | '0' = Bit is clea                                                                                         |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                                                                | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                |                                                                                                           | ared                                                                                                                                                                                                                                     | HS/HC = Bit                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                | nable bit                                                                                                 |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                        | is set/cleared b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | y hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 = CWGX is<br>0 = CWGX is                                                     | enabled                                                                                                   |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 = Dead-bai<br>this bit is                                                    |                                                                                                           | s to be loade                                                                                                                                                                                                                            | d on CWG dat                                                                                                                                                                                                                                                                                                           | a rising edge fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ollowing first fall                                                                                                                                                                                                                                                                                                                                                                                                                                             | ing edge afte                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Unimplemen                                                                     | ted: Read as 'o                                                                                           | )'                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 111 = Reser<br>110 = Reser<br>101 = CWG<br>100 = CWG<br>011 = CWG<br>010 = CWG | ved<br>ved<br>outputs operate<br>outputs operate<br>outputs operate<br>outputs operate<br>outputs operate | e in Push-Pull<br>e in Half-Bridg<br>e in Reverse f<br>e in Forward f<br>e in Synchron                                                                                                                                                   | ge mode<br>Full-Bridge mod<br>Full-Bridge mod<br>lous Steering m                                                                                                                                                                                                                                                       | de<br>node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                | MODE<2:0>:<br>111 = Reser<br>100 = Reser<br>101 = CWG<br>100 = CWG<br>111 = CWG<br>100 = CWG<br>100 = CWG | MODE<2:0>: CWGx Mode b<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate<br>100 = CWG outputs operate<br>111 = CWG outputs operate<br>100 = CWG outputs operate<br>100 = CWG outputs operate<br>100 = CWG outputs operate | MODE<2:0>: CWGx Mode bits<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate in Push-Pul<br>100 = CWG outputs operate in Half-Bridg<br>111 = CWG outputs operate in Reverse<br>101 = CWG outputs operate in Forward I<br>101 = CWG outputs operate in Synchron<br>100 = CWG outputs operate in Asynchron | MODE<2:0>: CWGx Mode bits<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>111 = CWG outputs operate in Reverse Full-Bridge mode<br>102 = CWG outputs operate in Forward Full-Bridge mode<br>103 = CWG outputs operate in Synchronous Steering mode<br>104 = CWG outputs operate in Asynchronous Steering mode<br>105 = CWG outputs operate in Asynchronous Steering mode<br>106 = CWG outputs operate in Asynchronous Steering mode<br>107 = CWG outputs operate in Asynchronous Steering mode<br>108 = CWG outputs operate in Asynchronous Steering mode<br>109 = CWG outputs operate in Asynchronous Steering mode<br>100 = CWG outputs operate in Asynchronous Steering | MODE<2:0>: CWGx Mode bits<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>111 = CWG outputs operate in Reverse Full-Bridge mode<br>102 = CWG outputs operate in Forward Full-Bridge mode<br>103 = CWG outputs operate in Synchronous Steering mode<br>104 = CWG outputs operate in Asynchronous Steering mode<br>105 = CWG outputs operate in Asynchronous Steering mode | MODE<2:0>: CWGx Mode bits         11 = Reserved         10 = Reserved         01 = CWG outputs operate in Push-Pull mode         00 = CWG outputs operate in Half-Bridge mode         011 = CWG outputs operate in Reverse Full-Bridge mode         010 = CWG outputs operate in Reverse Full-Bridge mode         010 = CWG outputs operate in Forward Full-Bridge mode         010 = CWG outputs operate in Synchronous Steering mode |

### REGISTER 20-1: CWGxCON0: CWGx CONTROL REGISTER 0

**Note 1:** This bit can only be set after EN = 1; it cannot be set in the same cycle when EN is set.

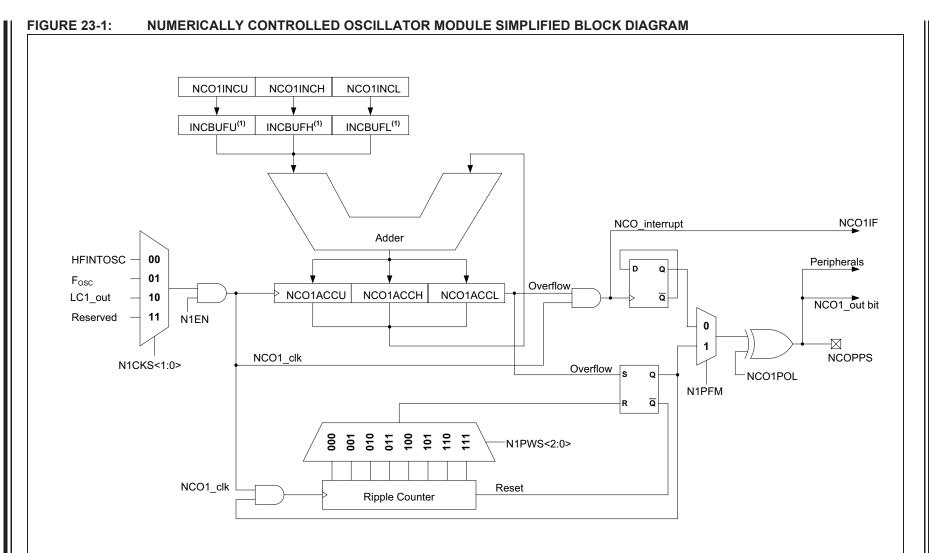

Note 1: The increment registers are double-buffered to allow for value changes to be made without first disabling the NCO1 module. They are shown for reference only and are not user accessible.

PIC16(L)F18326/18346

|                                                                                | R/W-x/u                                                             | R/W-x/u                                                                                                                                                                         | U-0         | R/W-x/u         | R/W-x/u          | R/W-x/u              | R/W-x/u     |  |  |  |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|------------------|----------------------|-------------|--|--|--|

|                                                                                | MDCLPOL                                                             | MDCLSYNC                                                                                                                                                                        | _           |                 | MDCL             | <3:0> <sup>(1)</sup> |             |  |  |  |

| bit 7                                                                          |                                                                     | · · ·                                                                                                                                                                           |             |                 |                  |                      | bit         |  |  |  |

| Legend:                                                                        |                                                                     |                                                                                                                                                                                 |             |                 |                  |                      |             |  |  |  |

| R = Readable                                                                   | e bit                                                               | W = Writable bi                                                                                                                                                                 | t           | U = Unimpler    | nented bit, read | d as '0'             |             |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at a |                                                                     |                                                                                                                                                                                 |             |                 |                  |                      | ther Resets |  |  |  |

| '1' = Bit is set                                                               |                                                                     | '0' = Bit is clear                                                                                                                                                              | ed          |                 |                  |                      |             |  |  |  |

| bit 7                                                                          | Unimplomo                                                           | nted: Read as '0'                                                                                                                                                               |             |                 |                  |                      |             |  |  |  |

| bit 6                                                                          | -                                                                   |                                                                                                                                                                                 | arrior Dola | rity Soloct bit |                  |                      |             |  |  |  |

| DILO                                                                           |                                                                     | Modulator Low Ca                                                                                                                                                                |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | <ul> <li>1 = Selected low carrier signal is inverted</li> <li>0 = Selected low carrier signal is not inverted</li> </ul>                                                        |             |                 |                  |                      |             |  |  |  |

| bit 5                                                                          |                                                                     | •                                                                                                                                                                               |             |                 | able hit         |                      |             |  |  |  |

| bit 5                                                                          |                                                                     | <b>MDCLSYNC:</b> Modulator Low Carrier Synchronization Enable bit<br>1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the high |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | time carrier                                                                                                                                                                    |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | 0 = Modulator output is not synchronized to the low time carrier signal <sup>(1)</sup>                                                                                          |             |                 |                  |                      |             |  |  |  |

| bit 4                                                                          |                                                                     | nted: Read as '0'                                                                                                                                                               |             |                 | 0                |                      |             |  |  |  |

| bit 3-0                                                                        | MDCL<3:0> Modulator Data High Carrier Selection bits <sup>(1)</sup> |                                                                                                                                                                                 |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | 1111 = CLC4 output                                                                                                                                                              |             |                 |                  |                      |             |  |  |  |

|                                                                                | 1110 = CL(                                                          |                                                                                                                                                                                 |             |                 |                  |                      |             |  |  |  |

|                                                                                | 1101 = CL(                                                          |                                                                                                                                                                                 |             |                 |                  |                      |             |  |  |  |

|                                                                                | 1100 = CLC                                                          | •                                                                                                                                                                               |             |                 |                  |                      |             |  |  |  |

|                                                                                | 1011 = HFI                                                          | NTOSC                                                                                                                                                                           |             |                 |                  |                      |             |  |  |  |

|                                                                                | 1010 = Fos                                                          | SC                                                                                                                                                                              |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | 1001 = Reserved. No channel connected.                                                                                                                                          |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | 1000 = NCO1 output                                                                                                                                                              |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | 0111 = PWM6 output                                                                                                                                                              |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | 0110 = PWM5 output                                                                                                                                                              |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | P2 output (PWM (                                                                                                                                                                |             |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     | P1 output (PWM (<br>erence clock mod                                                                                                                                            |             |                 |                  |                      |             |  |  |  |

|                                                                                | 0011 = Ret                                                          | aranca ciack maa                                                                                                                                                                | uie signal  |                 |                  |                      |             |  |  |  |

|                                                                                |                                                                     |                                                                                                                                                                                 | ale olgital |                 |                  |                      |             |  |  |  |

|                                                                                | 0010 = MD<br>0001 = MD                                              | CIN2PPS                                                                                                                                                                         | ale olgriai |                 |                  |                      |             |  |  |  |

#### REGISTER 25-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

# **REGISTER 27-3:** TMRxL<sup>(1)</sup>: TIMERx LOW BYTE REGISTER

| R/W-x/u          | R/W-x/u                                                       | R/W-x/u           | R/W-x/u | R/W-x/u                                            | R/W-x/u | R/W-x/u | R/W-x/u |

|------------------|---------------------------------------------------------------|-------------------|---------|----------------------------------------------------|---------|---------|---------|

|                  |                                                               |                   | TMRx    | L<7:0>                                             |         |         |         |

| bit 7            |                                                               |                   |         |                                                    |         |         | bit 0   |

|                  |                                                               |                   |         |                                                    |         |         |         |

| Legend:          |                                                               |                   |         |                                                    |         |         |         |

| R = Readable     | dable bit W = Writable bit U = Unimplemented bit, read as '0' |                   |         |                                                    |         |         |         |

| u = Bit is unch  | anged                                                         | x = Bit is unkn   | nown    | -n/n = Value at POR and BOR/Value at all other Res |         |         |         |

| '1' = Bit is set |                                                               | '0' = Bit is clea | ared    |                                                    |         |         |         |

bit 7-0 TMRxL<7:0>: TMRx Low Byte bits

Note 1: 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

# REGISTER 27-4: TMRxH<sup>(1)</sup>: TIMERx HIGH BYTE REGISTER

| bit 7   |         |         |         |         |         |         | bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | TMRxH   | 1<7:0>  |         |         |         |

| R/W-x/u |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>: TMRx High Byte bits

**Note 1:** 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

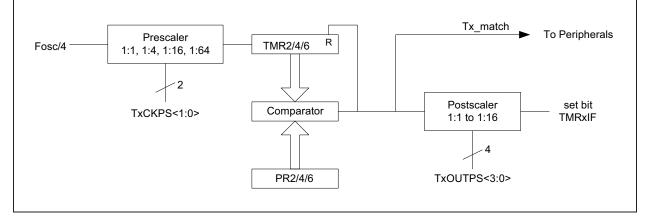

# 28.0 TIMER 2/4/6 MODULE

Timer2/4/6 modules are 8-bit timers that incorporate the following features:

- 8-bit Timer and Period registers (TMR2/4/6 and PR2/4/6, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2/4/6 match with PR2/4/6

- Optional use as the shift clock for the MSSPx module

See Figure 28-1 for a block diagram of Timer2/4/6.

- Note 1: In devices with more than one Timer module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the T2CON and T4CON control the same operational aspects of two completely different Timer modules.

- 2: Throughout this section, generic references to Timer2 module in any of its operating modes may be interpreted as being equally applicable to Timerx module. Register names, module signals, I/O pins and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

### FIGURE 28-1: TIMER2/4/6 BLOCK DIAGRAM

#### TABLE 30-2: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FcLock<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 35-4 to ensure the system is designed to support IOL requirements.

-n/n = Value at POR and BOR/Value at all other Resets

#### REGISTER 30-7: SSPxBUF: MSSP BUFFER REGISTER

| R/W-x/u        | R/W-x/u | R/W-x/u          | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u | R/W-x/u |

|----------------|---------|------------------|---------|--------------|------------------|---------|---------|

|                |         |                  | SSPxB   | UF<7:0>      |                  |         |         |

| bit 7          |         |                  |         |              |                  |         | bit 0   |

|                |         |                  |         |              |                  |         |         |

| Legend:        |         |                  |         |              |                  |         |         |

| R = Readable b | it      | W = Writable bit | t       | U = Unimpler | nented bit, read | as '0'  |         |

bit 7-0 **SSPxBUF<7:0>:** MSSP Buffer bits

u = Bit is unchanged

'1' = Bit is set

#### TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH MSSPx

x = Bit is unknown

'0' = Bit is cleared

| Name                  | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|------------------------|------------------------|---------|---------|---------|-----------|---------|---------|---------------------|

| TRISA                 | —                      | _                      | TRISA5  | TRISA4  | (3)     | TRISA2    | TRISA1  | TRISA0  | 143                 |

| ANSELA                | _                      | _                      | ANSA5   | ANSA4   | _       | ANSA2     | ANSA1   | ANSA0   | 144                 |

| INLVLA <sup>(1)</sup> | —                      | _                      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2   | INLVLA1 | INLVLA0 | 146                 |

| TRISB <sup>(2)</sup>  | TRISB7                 | TRISB6                 | TRISB5  | TRISB4  | _       | _         | _       | _       | 149                 |

| ANSELB <sup>(2)</sup> | ANSB7                  | ANSB6                  | ANSB5   | ANSB4   | _       | _         | _       | _       | 150                 |

| INLVLB <sup>(2)</sup> | INLVLB7                | INLVLB6                | INLVLB5 | INLVLB4 | _       | _         | _       | _       | 152                 |

| TRISC                 | TRISC7 <sup>(2)</sup>  | TRISC6 <sup>(2)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2    | TRISC1  | TRISC0  | 155                 |

| ANSELC                | ANSC7 <sup>(2)</sup>   | ANSC6 <sup>(2)</sup>   | ANSC5   | ANSC4   | ANSC3   | ANSC2     | ANSC1   | ANSC0   | 157                 |

| INLVLC <sup>(1)</sup> | INLVLC7 <sup>(2)</sup> | INLVLC6 <sup>(2)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2   | INLVLC1 | INLVLC0 | 159                 |

| INTCON                | GIE                    | PEIE                   | _       | _       | _       | _         | _       | INTEDG  | 100                 |

| PIR1                  | TMR1GIF                | ADIF                   | RCIF    | TXIF    | SSP1IF  | BCL1IF    | TMR2IF  | TMR1IF  | 107                 |

| PIE1                  | TMR1GIE                | ADIE                   | RCIE    | TXIE    | SSP1IE  | BCL1IE    | TMR2IE  | TMR1IE  | 102                 |

| PIR2                  | TMR6IF                 | C2IF                   | C1IF    | NVMIF   | SSP2IF  | BCL2IF    | TMR4IF  | NCO1IF  | 108                 |

| PIE2                  | TMR6IE                 | C2IE                   | C1IE    | NVMIE   | SSP2IE  | BCL2IE    | TMR4IE  | NCO1IE  | 103                 |

| SSPxSTAT              | SMP                    | CKE                    | D/A     | Р       | S       | R/W       | UA      | BF      | 359                 |

| SSPxCON1              | WCOL                   | SSPOV                  | SSPEN   | CKP     |         | SSPM      | <3:0>   |         | 360                 |

| SSPxCON2              | GCEN                   | ACKSTAT                | ACKDT   | ACKEN   | RCEN    | PEN       | RSEN    | SEN     | 362                 |

| SSPxCON3              | ACKTIM                 | PCIE                   | SCIE    | BOEN    | SDAHT   | SBCDE     | AHEN    | DHEN    | 363                 |

| SSPxMSK               |                        |                        |         | SSPxMS  | K<7:0>  |           |         |         | 364                 |

| SSPxADD               |                        |                        |         | SSPxAD  | D<7:0>  |           |         |         | 364                 |

| SSPxBUF               |                        |                        |         | SSPxBU  | F<7:0>  |           |         |         | 365                 |

| SSPxCLKPPS            | —                      | _                      |         |         | SSP     | xCLKPPS<  | 4:0>    |         | 162                 |

| SSPxDATPPS            | _                      | —                      | _       |         | SSF     | xDATPPS<  | 4:0>    |         | 162                 |

| SSPxSSPPS             | —                      | _                      | _       |         | SSI     | PxSSPPS<4 | :0>     |         | 162                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP module

Note 1: When using designated  $I^2C$  pins, the associated pin values in INLVLx will be ignored.

2: PIC16(L)F18346 only.

3: Unimplemented, read as '1'.

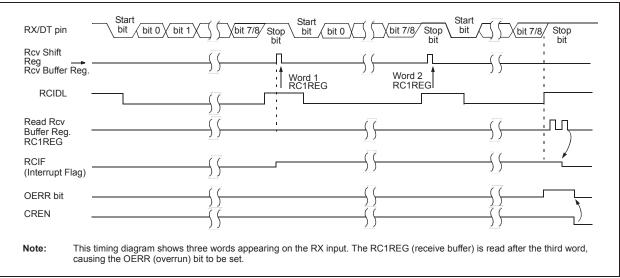

- 31.1.2.8 Asynchronous Reception Setup

- Initialize the SP1BRGH, SP1BRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 31.3 "EUSART1 Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.