Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                             |

| Supplier Device Package    | 14-TSSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18326-i-st |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|------------|----------------------------------------------------------|

|------------|----------------------------------------------------------|

| Address | Name                                            | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------------------|----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| Bank 3  | Bank 3                                          |                                  |       |       |       |       |       |       |       |       |                       |                                 |

|         | CPU CORE REGISTERS; see Table 4-2 for specifics |                                  |       |       |       |       |       |       |       |       |                       |                                 |

| 18Ch | ANSELA                 |   |   | —      | —             | ANSA5 | ANSA4   | —      | ANSA2 | ANSA1  | ANSA0     | xx -xxx   | uu -uuu   |

|------|------------------------|---|---|--------|---------------|-------|---------|--------|-------|--------|-----------|-----------|-----------|

| 18Dh | ANSELB                 | Х | — |        | Unimplemented |       |         |        |       |        |           | —         | —         |

|      |                        | — | Х | ANSB7  | ANSB6         | ANSB5 | ANSB4   | —      | —     | —      | —         | xxxx      | uuuu      |

| 18Eh | ANSELC                 | Х |   | -      | _             | ANSC5 | ANSC4   | ANSC3  | ANSC2 | ANSC1  | ANSC0     | xx xxxx   | uu uuuu   |

|      |                        | — | Х | ANSC7  | ANSC6         | ANSC5 | ANSC4   | ANSC3  | ANSC2 | ANSC1  | ANSC0     | XXXX XXXX | uuuu uuuu |

| 18Fh | —                      | _ |   |        |               |       | Unimple | mented |       |        |           | —         | —         |

| 190h | —                      | _ |   |        |               |       | Unimple | mented |       |        |           | —         | —         |

| 191h | —                      | _ |   |        |               |       | Unimple | mented |       |        |           | —         | —         |

| 192h | —                      | _ |   |        | Unimplemented |       |         |        |       |        |           | —         | —         |

| 193h | _                      | _ |   |        | Unimplemented |       |         |        |       |        |           | _         | —         |

| 194h | _                      | _ |   |        | Unimplemented |       |         |        |       |        |           |           | _         |

| 195h | —                      | _ |   |        | Unimplemented |       |         |        |       |        |           | —         | —         |

| 196h | —                      | _ |   |        |               |       | Unimple | mented |       |        |           | —         | —         |

| 197h | VREGCON <sup>(1)</sup> |   |   | —      | —             | _     | —       | _      | —     | VREGPM | Reserved  | 01        | 01        |

| 198h | —                      |   | - |        |               |       | Unimple | mented |       |        |           | —         | —         |

| 199h | RC1REG                 |   |   |        |               |       | RC1RE   | G<7:0> |       |        |           | 0000 0000 | 0000 0000 |

| 19Ah | TX1REG                 |   |   |        |               |       | TX1RE   | G<7:0> |       |        |           | 0000 0000 | 0000 0000 |

| 19Bh | SP1BRGL                |   |   |        | SP1BRG<7:0>   |       |         |        |       |        |           | 0000 0000 | 0000 0000 |

| 19Ch | SP1BRGH                |   |   |        | SP1BRG<15:8>  |       |         |        |       |        | 0000 0000 | 0000 0000 |           |

| 19Dh | RC1STA                 |   |   | SPEN   | RX9           | SREN  | CREN    | ADDEN  | FERR  | OERR   | RX9D      | 0000 000x | 0000 000x |

| 19Eh | TX1STA                 |   |   | CSRC   | TX9           | TXEN  | SYNC    | SENDB  | BRGH  | TMRT   | TX9D      | 0000 0010 | 0000 0010 |

| 19Fh | BAUD1CON               |   |   | ABDOVF | RCIDL         | —     | SCKP    | BRG16  | —     | WUE    | ABDEN     | 01-0 0-00 | 01-0 0-00 |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Only on PIC16F18326/18346.

2: Register accessible from both User and ICD Debugger.

## PIC16(L)F18326/18346

## 7.0 OSCILLATOR MODULE

#### 7.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 7-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 determine the type of oscillator that will be used when the device is reset, including when it is first powered-up.

The internal clock modes, LFINTOSC, HFINTOSC (set at 1 MHz), or HFINTOSC (set at 32 MHz) can be set through the RSTOSC bits.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the External Clock mode.

The external oscillator module can be configured in one of the following clock modes by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (<= 100 kHz)

- ECM External Clock Medium-Power mode (<= 8 MHz)</li>

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS Clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The INTOSC internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 7-1).

### TABLE 7-1: NOSC/COSC BIT SETTINGS

| NOSC<2:0><br>COSC<2:0> | Clock Source                     |

|------------------------|----------------------------------|

| 111                    | EXTOSC <sup>(1)</sup>            |

| 110                    | HFINTOSC (1 MHz)                 |

| 101                    | Reserved                         |

| 100                    | LFINTOSC                         |

| 011                    | SOSC                             |

| 010                    | Reserved                         |

| 001                    | EXTOSC with 4xPLL <sup>(1)</sup> |

| 000                    | HFINTOSC with 2x PLL<br>(32 MHz) |

|                        |                                  |

Note 1: EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 5-1).

#### TABLE 7-2: NDIV/CDIV BIT SETTINGS

| NDIV<3:0><br>CDIV<3:0> | Clock Divider |

|------------------------|---------------|

| 1111-1010              | Reserved      |

| 1001                   | 512           |

| 1000                   | 256           |

| 0111                   | 128           |

| 0110                   | 64            |

| 0101                   | 32            |

| 0100                   | 16            |

| 0011                   | 8             |

| 0010                   | 4             |

| 0001                   | 2             |

| 0000                   | 1             |

#### REGISTER 7-3: OSCCON3: OSCILLATOR CONTROL REGISTER 3

| R/W/HC-0/0 | R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | U-0 | U-0 | U-0   |

|------------|---------|---------|-------|-------|-----|-----|-------|

| CSWHOLD    | SOSCPWR | SOSCBE  | ORDY  | NOSCR | —   | —   | —     |

| bit 7      |         |         |       |       |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Reset value is determined by hardware             |

| bit 7   | CSWHOLD: Clock Switch Hold bit                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Clock switch will hold (with interrupt) when the oscillator selected by NOSC is ready                                   |

|         | 0 = Clock switch may proceed when the oscillator selected by NOSC is ready; if this bit                                     |

|         | is set at the time that NOSCR becomes '1', the switch and interrupt will occur.                                             |

| bit 6   | SOSCPWR: Secondary Oscillator Power Mode Select bit                                                                         |

|         | If SOSCBE = 0                                                                                                               |

|         | 1 = Secondary oscillator operating in High-Power mode                                                                       |

|         | 0 = Secondary oscillator operating in Low-Power mode                                                                        |

|         | If SOSCBE = 1                                                                                                               |

|         | x = Bit is ignored                                                                                                          |

| bit 5   | SOSCBE: Secondary Oscillator Bypass Enable bit                                                                              |

|         | <ul> <li>Secondary oscillator SOSCI is configured as an external clock input (ST-buffer); SOSCO is not<br/>used.</li> </ul> |

|         | 0 = Secondary oscillator is configured as a crystal oscillator using SOSCO and SOSCI pins.                                  |

| bit 4   | ORDY: Oscillator Ready bit (read-only)                                                                                      |

|         | 1 = OSCCON1 = OSCCON2; the current system clock is the clock specified by NOSC                                              |

|         | 0 = A clock switch is in progress                                                                                           |

| bit 3   | NOSCR: New Oscillator is Ready bit (read-only)                                                                              |

|         | 1 = A clock switch is in progress and the oscillator selected by NOSC indicates a Ready condition                           |

|         | 0 = A clock switch is not in progress, or the NOSC-selected oscillator is not yet ready                                     |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                  |

|         |                                                                                                                             |

#### REGISTER 8-11: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4 (CONTINUED)

#### bit 1

CCP2IF: CCP2 Interrupt Flag bit

| Value | CCPM Mode                                         |                                                      |                                                             |  |  |  |  |  |

|-------|---------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| value | Capture                                           | Compare                                              | PWM                                                         |  |  |  |  |  |

| 1     | Capture occurred<br>(must be cleared in software) | Compare match occurred (must be cleared in software) | Output trailing edge occurred (must be cleared in software) |  |  |  |  |  |

| 0     | Capture did not occur                             | Compare match did not occur                          | Output trailing edge did not occur                          |  |  |  |  |  |

bit 0

#### CCP1IF: CCP1 Interrupt Flag bit

| Value | CCPM Mode                                         |                                                      |                                                             |  |  |  |  |

|-------|---------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| value | Capture                                           | Compare                                              | PWM                                                         |  |  |  |  |

| 1     | Capture occurred<br>(must be cleared in software) | Compare match occurred (must be cleared in software) | Output trailing edge occurred (must be cleared in software) |  |  |  |  |

| 0     | Capture did not occur                             | Compare match did not occur                          | Output trailing edge did not occur                          |  |  |  |  |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name   | Bit 7   | Bit 6  | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|---------|--------|---------|--------|--------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | _       | _      | _      | _      | _      | INTEDG | 100                 |

| PIE0   | —       | —      | TMR0IE  | IOCIE  | _      | —      | _      | INTE   | 101                 |

| PIE1   | TMR1GIE | ADIE   | RCIE    | TXIE   | SSP1IE | BCL1IE | TMR2IE | TMR1IE | 102                 |

| PIE2   | TMR6IE  | C2IE   | C1IE    | NVMIE  | SSP2IE | BCL2IE | TMR4IE | NCO1IE | 103                 |

| PIE3   | OSFIE   | CSWIE  | TMR3GIE | TMR3IE | CLC4IE | CLC3IE | CLC2IE | CLC1IE | 104                 |

| PIE4   | CWG2IE  | CWG1IE | TMR5GIE | TMR5IE | CCP4IE | CCP3IE | CCP2IE | CCP1IE | 105                 |

| PIR0   | —       | —      | TMR0IF  | IOCIF  | _      | —      | _      | INTF   | 106                 |

| PIR1   | TMR1GIF | ADIF   | RCIF    | TXIF   | SSP1IF | BCL1IF | TMR2IF | TMR1IF | 107                 |

| PIR2   | TMR6IF  | C2IF   | C1IF    | NVMIF  | SSP2IF | BCL2IF | TMR4IF | NCO1IF | 108                 |

| PIR3   | OSFIF   | CSWIF  | TMR3GIF | TMR3IF | CLC4IF | CLC3IF | CLC2IF | CLC1IF | 109                 |

| PIR4   | CWG2IF  | CWG1IF | TMR5GIF | TMR5IF | CCP4IF | CCP3IF | CCP2IF | CCP1IF | 110                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

# PIC16(L)F18326/18346

### 25.1 DSM Operation

The DSM module can be enabled by setting the MDEN bit in the MDCON register. Clearing the MDEN bit in the MDCON register, disables the DSM module by automatically switching the carrier high and carrier low signals to the Vss signal source. The modulator signal source is also switched to the MDBIT in the MDCON register. This not only assures that the DSM module is inactive, but that it is also consuming the least amount of current.

The values used to select the carrier high, carrier low, and modulator sources held by the Modulation Source, Modulation High Carrier, and Modulation Low Carrier control registers are not affected when the MDEN bit is cleared and the DSM module is disabled. The values inside these registers remain unchanged while the DSM is inactive. The sources for the carrier high, carrier low and modulator signals will once again be selected when the MDEN bit is set and the DSM module is again enabled and active.

The modulated output signal can be disabled without shutting down the DSM module. The DSM module will remain active and continue to mix signals, but the output value will not be sent to the DSM pin. During the time that the output is disabled, the DSM pin will remain low. The modulated output can be disabled by clearing the MDEN bit in the MDCON register.

#### 25.2 Modulator Signal Sources

The modulator signal can be supplied from the following sources:

- CCP1 Output

- CCP2 Output

- PWM5 Output

- PWM6 Output

- MSSP1 SDO1 (SPI mode only)

- MSSP2 SDO2 (SPI mode only)

- Comparator C1 Output

- Comparator C2 Output

- EUSART1 TX Output

- External Signal on MDMIN pin

- NCO1 Output

- CLC1 Output

- CLC2 Output

- CLC3 Output

- CLC4 Output

- · MDBIT bit in the MDCON register

The modulator signal is selected by configuring the MDMS <3:0> bits in the MDSRC register.

## 25.3 Carrier Signal Sources

The carrier high signal and carrier low signal can be supplied from the following sources:

- CCP1 Output

- CCP2 Output

- PWM5 Output

- PWM6 Output

- NCO1 Output

- Fosc (System Clock)

- HFINTOSC

- CLC1 Output

- CLC2 Output

- CLC3 Output

- CLC4 Output

- CLKR

- External Signal on MDCIN1 pin

- External Signal on MDCIN2 pin

- Vss

The carrier high signal is selected by configuring the MDCH <3:0> bits in the MDCARH register. The carrier low signal is selected by configuring the MDCL <3:0> bits in the MDCARL register.

### 25.4 Carrier Synchronization

During the time when the DSM switches between carrier high and carrier low signal sources, the carrier data in the modulated output signal can become truncated. To prevent this, the carrier signal can be synchronized to the modulator signal. When the modulator signal transitions away from the synchronized carrier, the unsynchronized carrier source is immediately active, while the synchronized carrier remains active until its next falling edge. When the modulator signal transitions back to the synchronized carrier, the unsynchronized carrier is immediately disabled, and the modulator waits until the next falling edge of the synchronized carrier before the synchronized carrier becomes active.

Synchronization is enabled separately for the carrier high and carrier low signal sources. Synchronization for the carrier high signal is enabled by setting the MDCHSYNC bit in the MDCARH register. Synchronization for the carrier low signal is enabled by setting the MDCLSYNC bit in the MDCARL register.

Figure 25-1 through Figure 25-6 show timing diagrams of using various synchronization methods.

## 25.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

## 25.6 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

### 25.7 Modulated Output Polarity

The modulated output signal provided on the DSM pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

## 25.8 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the SLR bit of the SLRCON register associated with that pin. For example, clearing the slew rate limitation for pin RA5 would require clearing the SLRA5 bit of the SLRCONA register.

### 25.9 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

### 25.10 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

## **REGISTER 27-3:** TMRxL<sup>(1)</sup>: TIMERx LOW BYTE REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | TMRx    | L<7:0>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 TMRxL<7:0>: TMRx Low Byte bits

Note 1: 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

## REGISTER 27-4: TMRxH<sup>(1)</sup>: TIMERx HIGH BYTE REGISTER

| bit 7   |         |         |         |         |         |         | bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | TMRxH   | 1<7:0>  |         |         |         |

| R/W-x/u |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>: TMRx High Byte bits

**Note 1:** 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

### **REGISTER 28-2:** TMRx<sup>(1)</sup>: TIMERx COUNT REGISTER

| R/W-0/0         R/W-0/0 <t< th=""><th></th></t<> |                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 R/W-0/0        |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 0            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | all other Resets |

| '1' = Bit is set '0' = Bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

bit 7-0 TMRx<7:0>: TMRx Counter bits 7..0

**Note 1:** 'x' refers to either '2,' 4' or '6' for the respective Timer2/4/6 registers.

#### REGISTER 28-3: PRx: TIMERx PERIOD REGISTER<sup>(1)</sup>

| R/W-1/1         | R/W-1/1 | R/W-1/1         | R/W-1/1 | R/W-1/1      | R/W-1/1         | R/W-1/1  | R/W-1/1 |

|-----------------|---------|-----------------|---------|--------------|-----------------|----------|---------|

|                 |         |                 | PRx<    | :7:0>        |                 |          |         |

| bit 7           |         |                 |         |              |                 |          | bit 0   |

|                 |         |                 |         |              |                 |          |         |

| Legend:         |         |                 |         |              |                 |          |         |

| R = Readable bi | it      | W = Writable bi | ŀ       | =   Inimpler | mented hit read | 1 as '0' |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 PRx<7:0>: TMRx Counter bits 7..0

When TMRx = PRx, the next clock will reset the counter; counter period is (PRx+1)

**Note 1:** 'x' refers to either '2,' 4' or '6' for the respective Timer2/4/6 registers.

© 2016-2017 Microchip Technology Inc.

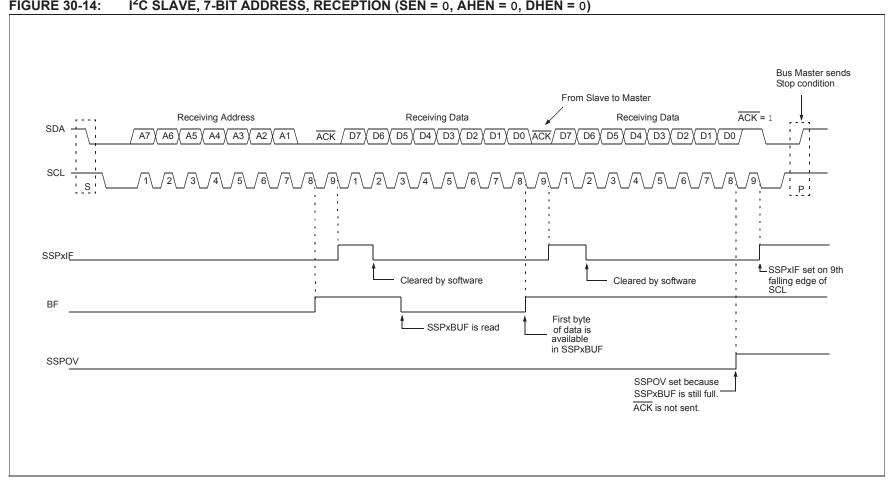

#### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 0, DHEN = 0) FIGURE 30-14:

© 2016-2017 Microchip Technology Inc

Preliminary

PIC16(L)F18326/18346

#### 30.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 30-19 displays a standard waveform of a 7-bit address slave transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCL line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads ACKTIM bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: <u>SSPxBUF</u> cannot be loaded until after the ACK.

- 13. Slave sets the CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

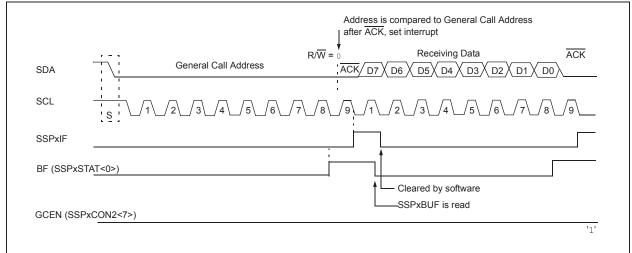

#### 30.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^{2}C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with

the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 30-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### FIGURE 30-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 30.5.9 SSP MASK REGISTER

An SSP Mask (SPPxMSK) register (Register 30-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

# PIC16(L)F18326/18346

| ΜΟΥΙΨ            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ \textbf{-32} \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                               |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{FSR + 1 (preincrement)} \\ &\text{FSR - 1 (predecrement)} \\ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{FSR + 1 (all increments)} \\ &\text{FSR - 1 (all decrements)} \\ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                               |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

| Syntax:          | [ <i>label</i> ]MOVLB k                                              |

|------------------|----------------------------------------------------------------------|

| Operands:        | $0 \leq k \leq 31$                                                   |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                                                         |

|------------------|------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]MOVLP k                                                                        |

| Operands:        | $0 \leq k \leq 127$                                                                            |

| Operation:       | $k \rightarrow PCLATH$                                                                         |

| Status Affected: | None                                                                                           |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                      |

| MOVLW            | Move literal to W                                                                              |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                       |

| Operands:        | $0 \le k \le 255$                                                                              |

| Operation:       | $k \rightarrow (W)$                                                                            |

| Status Affected: | None                                                                                           |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                              |

| Cycles:          | 1                                                                                              |

| Example:         | MOVLW 0x5A                                                                                     |

|                  | After Instruction<br>W = 0x5A                                                                  |

| MOVWF            | Move W to f                                                                                    |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                       |

| Operands:        | $0 \leq f \leq 127$                                                                            |

| Operation:       | $(W) \to (f)$                                                                                  |

| Status Affected: | None                                                                                           |

| Description:     | Move data from W register to register 'f'.                                                     |

| Words:           | 1                                                                                              |

| Cycles:          | 1                                                                                              |

| Example:         | MOVWF OPTION_REG                                                                               |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F                                            |

|                  | After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F                                             |

# PIC16(L)F18326/18346

| SLEEP            | Enter Sleep mode                                                                                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                  |

| Operands:        | None                                                                                                                                                                                                           |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                     |

| Status Affected: | TO, PD                                                                                                                                                                                                         |

| Description:     | The power-down Status bit, <u>PD</u> is<br>cleared. Time-out Status bit, <u>TO</u> is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>See <b>Section 9.2 "Sleep Mode"</b> for<br>more information. |

| SUBWF            | Subtract W from f                                                                                                                                                              |                 |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| Syntax:          | [label] Sl                                                                                                                                                                     | JBWF f,d        |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |                 |  |  |

| Operation:       | (f) - $(W)$ → $(c)$                                                                                                                                                            | lestination)    |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |                 |  |  |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f. |                 |  |  |

|                  | <b>C =</b> 0                                                                                                                                                                   | W > f           |  |  |

|                  | <b>C =</b> 1                                                                                                                                                                   | $W \leq f$      |  |  |

|                  | DC = 0                                                                                                                                                                         | W<3:0> > f<3:0> |  |  |

|                   | DC = 0                | W<3:0> > f<3:0>      |

|-------------------|-----------------------|----------------------|

|                   | DC = 1                | W<3:0> ≤ f<3:0>      |

|                   |                       |                      |

|                   |                       |                      |

|                   |                       |                      |

| SUBWFB            | Subtract              | W from f with Borrow |

| SUBWFB<br>Syntax: | Subtract<br>SUBWFB    |                      |

|                   | SUBWFB<br>0 ≤ f ≤ 127 | 6 f {,d}             |

| Syntax:           | SUBWFB                | 6 f {,d}             |

| Syntax:          | SUBWFB f{,d}                                                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                 |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                     |

| Status Affected: | C, DC, Z                                                                                                                                                                                          |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'. |

| SUBLW            | Subtract W from literal                                                                                                  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                 |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |  |  |  |

| Operation:       | $k - (W) \to (W)$                                                                                                        |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |

|                  | C = 0 W > k                                                                                                              |  |  |  |

|                  |                                                                                                                          |  |  |  |

| register.              |                   |  |  |  |

|------------------------|-------------------|--|--|--|

| <b>C =</b> 0           | W > k             |  |  |  |

| <b>C =</b> 1           | $W \leq k$        |  |  |  |

| DC = (                 | 0 W<3:0> > k<3:0> |  |  |  |

| DC = 1 W<3:0> ≤ k<3:0> |                   |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                             |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |  |  |

| Status Affected: | None                                                                                                                                                                   |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |  |  |

| IABLE         | ABLE 35-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS <sup>17</sup> |                        |                    |                     |             |       |                |

|---------------|------------------------------------------------------------------------|------------------------|--------------------|---------------------|-------------|-------|----------------|

| Standar       | Standard Operating Conditions (unless otherwise stated)                |                        |                    |                     |             |       |                |

| Param.<br>No. | Sym.                                                                   | Characteristic         | Min.               | Тур.†               | Max.        | Units | Conditions     |

| ECL Os        | cillator                                                               |                        |                    |                     |             |       |                |

| OS1           | FECL                                                                   | Clock Frequency        | —                  | —                   | 500         | kHz   |                |

| OS2           | TECL_DC                                                                | Clock Duty Cycle       | 40                 | —                   | 60          | %     |                |

| ECM Os        | cillator                                                               | •                      |                    |                     |             | •     |                |

| OS3           | FECM                                                                   | Clock Frequency        | —                  | —                   | 4           | MHz   | Nøte 4         |

| OS4           | TECM_DC                                                                | Clock Duty Cycle       | 40                 | —                   | 60          | %     |                |

| ECH Os        | cillator                                                               | •                      |                    |                     |             |       |                |

| OS5           | Fech                                                                   | Clock Frequency        | —                  | —                   | 32          | MHz   |                |

| OS6           | TECH_DC                                                                | Clock Duty Cycle       | 40                 | —                   | 60          | %     |                |

| LP Osci       | LP Oscillator                                                          |                        |                    |                     |             |       |                |

| OS7           | Flp                                                                    | Clock Frequency        | —                  | —                   | (100        | KHZ   | Note 4         |

| XT Osci       | XT Oscillator                                                          |                        |                    |                     |             |       | $\geq$         |

| OS8           | Fхт                                                                    | Clock Frequency        | —                  | $\overline{}$       | 4           | MHz   | Note 4         |

| HS Osci       | HS Oscillator                                                          |                        |                    |                     |             |       |                |

| OS9           | FHS                                                                    | Clock Frequency        | - /                |                     | 20          | ∕∕MHz | Note 4         |

| System        | System Clock                                                           |                        |                    |                     |             |       |                |

| OS20          | Fosc                                                                   | System Clock Frequency | $\langle  \rangle$ | $\langle - \rangle$ | 32          | MHz   | Note 2, Note 3 |

| OS21          | Fcy                                                                    | Instruction Frequency  | $\left[ \right] $  | Fosc/4              | $\rangle -$ | MHz   |                |

| OS22          | Тсү                                                                    | Instruction Period     | 125                | 1/Fey               | —           | ns    |                |

| *             | <b>T</b> I                                                             |                        |                    | <u> </u>            |             |       |                |

#### TABLE 35-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS<sup>(1)</sup>

These parameters are characterized but not tested.

+ Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (Tcy) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" no clock) for all devices.

- 2: The system clock frequency (Fosc) is selected by the "main clock switch controls" as described in Section 7.3 "Clock Switching".

- 3: The system clock frequency (Fosc) must meet the voltage requirements defined in the Section 35.2 "Standard Operating Conditions". LP, XT and HS oscillator modes require an appropriate crystal or resonator to be connected to the device.

- 4: For clocking the device with an external square wave, one of the EC mode selections must be used.

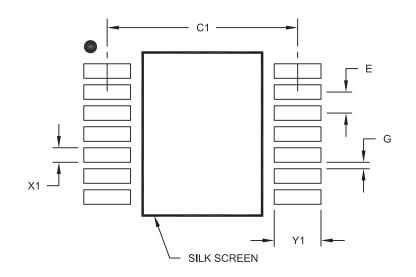

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units            |      |          | S    |

|--------------------------|------------------|------|----------|------|

| Dimensior                | Dimension Limits |      | NOM      | MAX  |

| Contact Pitch            | E                |      | 0.65 BSC |      |

| Contact Pad Spacing      | C1               |      | 5.90     |      |

| Contact Pad Width (X14)  | X1               |      |          | 0.45 |

| Contact Pad Length (X14) | Y1               |      |          | 1.45 |

| Distance Between Pads    | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

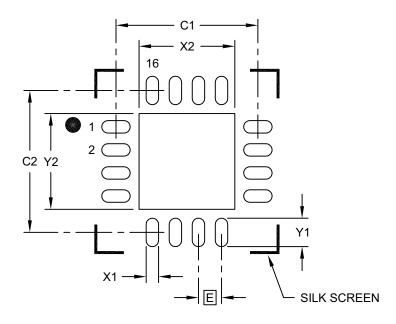

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |                   |          |      |

|----------------------------|-------------|-------------------|----------|------|

|                            | Units       | IVIILLIIVIE I ERS |          |      |

| Dimensior                  | Limits      | MIN               | NOM      | MAX  |

| Contact Pitch              | E           |                   | 0.65 BSC |      |

| Optional Center Pad Width  | X2          |                   |          | 2.70 |

| Optional Center Pad Length | Y2          |                   |          | 2.70 |

| Contact Pad Spacing        | C1          |                   | 4.00     |      |

| Contact Pad Spacing        | C2          |                   | 4.00     |      |

| Contact Pad Width (X16)    | X1          |                   |          | 0.35 |

| Contact Pad Length (X16)   | Y1          |                   |          | 0.80 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A

## 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |          |      |  |

|-------------------------|-------------|-----------|----------|------|--|

| Dimension               | Limits      | MIN       | NOM      | MAX  |  |

| Number of Terminals     | N           |           | 20       |      |  |

| Pitch                   | е           |           | 0.50 BSC |      |  |

| Overall Height          | Α           | 0.45      | 0.50     | 0.55 |  |

| Standoff                | A1          | 0.00      | 0.02     | 0.05 |  |

| Terminal Thickness      | A3          | 0.127 REF |          |      |  |

| Overall Width           | E           |           | 4.00 BSC |      |  |

| Exposed Pad Width       | E2          | 2.60      | 2.70     | 2.80 |  |

| Overall Length          | D           | 4.00 BSC  |          |      |  |

| Exposed Pad Length      | D2          | 2.60      | 2.70     | 2.80 |  |

| Terminal Width          | b           | 0.20      | 0.25     | 0.30 |  |

| Terminal Length         | L           | 0.30      | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | К           | 0.20      | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-255A Sheet 2 of 2

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> X     /XX     XXX       T     T     T     T       Tape and Reel     Temperature     Package     Pattern       Option     Range | Examples:<br>a) PIC16LF18326- E/P<br>Extended temperature<br>PDIP package                                                                                                                                                                                                                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F18326, PIC16LF18326,<br>PIC16F18346, PIC16LF18346.                                                                                          | b) PIC16LF18346- E/SO<br>Extended temperature,<br>SOIC package                                                                                                                                                                                                                                 |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                                     |                                                                                                                                                                                                                                                                                                |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                                         |                                                                                                                                                                                                                                                                                                |

| Package: <sup>(2)</sup>  | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                              | Note 1: Tape and Reel identifier only appears in<br>the catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package.<br>Check with your Microchip Sales Office<br>for package availability with the Tape and<br>Reel option. |

| Pattern:                 | QTP, SQTP, Code or Special Requirements<br>(blank otherwise)                                                                                      | 2: Small form-factor packaging options may<br>be available. Check<br>www.microchip.com/packaging for<br>small-form factor package availability, or<br>contact your local Sales Office.                                                                                                         |

© 2016-2017 Microchip Technology Inc.