# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18346-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3:20-PIN ALLOCATION TABLE (PIC16(L)F18346) (CONTINUED)

| IADLL              | •.                    |             |      |           |                  |      |     |                       |        |                     |      |                |                                            |        |                       |      |           |         |       |

|--------------------|-----------------------|-------------|------|-----------|------------------|------|-----|-----------------------|--------|---------------------|------|----------------|--------------------------------------------|--------|-----------------------|------|-----------|---------|-------|

| I/O <sup>(2)</sup> | 20-Pin PDIP/SOIC/SSOP | 20-Pin UQFN | ADC  | Reference | Comparator       | NCO  | DAC | WSQ                   | Timers | ссь                 | PWM  | CWG            | ASSM                                       | EUSART | CLC                   | CLKR | Interrupt | Pull-up | Basic |

| RC3                | 7                     | 4           | ANC3 | —         | C1IN3-<br>C2IN3- | —    | _   | MDMIN <sup>(1)</sup>  | _      | CCP2 <sup>(1)</sup> | _    | _              | —                                          | _      | CLCIN1 <sup>(1)</sup> | —    | IOC       | Y       | —     |

| RC4                | 6                     | 3           | ANC4 | —         | —                | —    | _   | _                     | _      | _                   | _    | _              | —                                          | _      | _                     | —    | IOC       | Y       | _     |

| RC5                | 5                     | 2           | ANC5 | _         | —                | —    | _   | MDCIN2 <sup>(1)</sup> | _      | CCP1 <sup>(1)</sup> | _    | _              | _                                          | _      | _                     | —    | IOC       | Y       | _     |

| RC6                | 8                     | 5           | ANC6 | —         | —                | —    | _   | —                     | _      | —                   | —    | _              | SS1 <sup>(1)</sup>                         | —      | —                     | —    | IOC       | Y       | _     |

| RC7                | 9                     | 6           | ANC7 | —         | —                | —    | _   | —                     | _      | —                   | _    | —              | —                                          | _      | —                     | —    | IOC       | Y       | _     |

| Vdd                | 1                     | 18          | —    | —         | —                | —    | —   | —                     | —      | —                   | —    | —              | —                                          | —      | —                     | —    | —         | —       | Vdd   |

| Vss                | 20                    | 17          | —    | —         | —                | —    | _   | —                     | _      | —                   | _    | —              | —                                          | _      | —                     | —    | _         | —       | Vss   |

|                    | _                     | _           | —    | —         | C1OUT            | NCO1 | —   | DSM                   | TMR0   | CCP1                | PWM5 | CWG1A<br>CWG2A | SDO1<br>SDO2                               | DT     | CLC1OUT               | CLKR | _         | —       | —     |

| OUT <sup>(2)</sup> | _                     | —           | —    | —         | C2OUT            | _    | _   | —                     | _      | CCP2                | PWM6 | CWG1B<br>CWG2B | SCK1<br>SCK2                               | СК     | CLC2OUT               | —    | _         | _       | —     |

| 0010               | _                     | _           | _    | _         | _                | _    | _   | _                     | _      | CCP3                | -    | CWG1C<br>CWG2C | SCL1 <sup>(3)</sup><br>SCL2 <sup>(3)</sup> | ТΧ     | CLC3OUT               | _    | _         | _       | _     |

|                    | _                     | _           | _    | —         | _                | _    | _   | _                     | _      | CCP4                | _    | CWG1D<br>CWG2D | SDA1 <sup>(3)</sup><br>SDA2 <sup>(3)</sup> | —      | CLC4OUT               | —    | _         | _       | —     |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

**3:** These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I<sup>2</sup>C logic levels; clock and data signals may be assigned to any of these pins. Assignments to other pins (e.g., RA5) will operate, but logic levels will be standard TTL/ST as selected by the INLVL register.

| Name                                                   | Function | Input<br>Type    | Output<br>Type | Description                            |

|--------------------------------------------------------|----------|------------------|----------------|----------------------------------------|

| RA5/ANA5/T1CKI <sup>(1)</sup> / T3CKI <sup>(1)</sup> / | RA5      | TTL/ST           | CMOS           | General purpose I/O.                   |

| T5CKI <sup>(1)</sup> / SOSCIN/SOSCI/<br>CLKIN/OSC1     | ANA5     | AN               | —              | ADC Channel A5 input.                  |

| CERIN/OSC1                                             | T1CKI    | TTL/ST           | —              | TMR1 Clock input.                      |

|                                                        | T3CKI    | TTL/ST           | _              | TMR3 Clock input.                      |

|                                                        | T5CKI    | TTL/ST           |                | TMR5 Clock input.                      |

|                                                        | SOSCIN   | TTL/ST           | —              | Secondary Oscillator input connection. |

|                                                        | SOSCI    | XTAL             | _              | Secondary Oscillator connection.       |

|                                                        | CLKIN    | TTL/ST           | _              | External clock input.                  |

|                                                        | OSC1     | XTAL             | —              | Crystal/Resonator (LP, XT, HS modes).  |

| RB4/ANB4/SDI1 <sup>(1)</sup> / SDA1 <sup>(1,3)</sup> / | RB4      | TTL/ST           | CMOS           | General purpose I/O.                   |

| CLCIN2 <sup>(1)</sup>                                  | ANB4     | AN               | —              | ADC Channel B4 input.                  |

|                                                        | SDI1     | TTL/ST           | CMOS           | SPI Data input 1.                      |

|                                                        | SDA1     | I <sup>2</sup> C | OD             | I <sup>2</sup> C Data 1.               |

|                                                        | CLCIN2   | TTL/ST           | _              | Configurable Logic Cell 2 input.       |

| RB5/ANB5/SDI2 <sup>(1)</sup> / SDA2 <sup>(1,3)</sup> / | RB5      | TTL/ST           | CMOS           | General purpose I/O.                   |

| RX <sup>(1)</sup> /DT/CLCIN3 <sup>(1)</sup>            | ANB5     | AN               | _              | ADC Channel B5 input.                  |

|                                                        | SDI2     | TTL/ST           | CMOS           | SPI Data input 2.                      |

|                                                        | SDA2     | l <sup>2</sup> C | OD             | I <sup>2</sup> C Data 2.               |

|                                                        | RX       | TTL/ST           | CMOS           | EUSART asynchronous input.             |

|                                                        | DT       | TTL/ST           | CMOS           | EUSART synchronous data output.        |

|                                                        | CLCIN3   | TTL/ST           | _              | Configurable Logic Cell 3 input.       |

| RB6/ANB6/SCK1 <sup>(1)</sup> / SCL1 <sup>(1,3)</sup>   | RB6      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANB6     | AN               | _              | ADC Channel B6 input.                  |

|                                                        | SCK1     | TTL/ST           | CMOS           | SPI Clock 1.                           |

|                                                        | SCL1     | l <sup>2</sup> C | OD             | I <sup>2</sup> C Clock 1.              |

| RB7/ANB7/SCK2 <sup>(1)</sup> / SCL2 <sup>(1,3)</sup>   | RB7      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANB7     | AN               | _              | ADC Channel B7 input.                  |

|                                                        | SCK2     | TTL/ST           | CMOS           | SPI Clock 2.                           |

|                                                        | SCL2     | l <sup>2</sup> C | OD             | I <sup>2</sup> C Clock 2.              |

| RC0/ANC0/C2IN0+                                        | RC0      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANC0     | AN               | _              | ADC Channel C0 input.                  |

|                                                        | C2IN0+   | AN               | _              | Comparator C2 positive input.          |

| RC1/ANC1/C1IN1-/C2IN1-                                 | RC1      | TTL/ST           | CMOS           | General purpose I/O.                   |

|                                                        | ANC1     | AN               | _              | ADC Channel C1 input.                  |

|                                                        | C1IN1-   | AN               | _              | Comparator C1 negative input.          |

|                                                        | C2IN1-   | AN               |                | Comparator C2 negative input.          |

| RC2/ANC2/C1IN2-/C2IN2-/                                | RC2      | TTL/ST           | CMOS           | General purpose I/O.                   |

| MDCIN1 <sup>(1)</sup>                                  | ANC2     | AN               | _              | ADC Channel C2 input.                  |

|                                                        | C1IN2-   | AN               | _              | Comparator C1 negative input.          |

|                                                        | C2IN2-   | AN               | _              | Comparator C2 negative input.          |

|                                                        | MDCIN1   | TTL/ST           | _              | Modular Carrier input 1.               |

TABLE 1-3: PIC16(L)F18346 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| R/W-0/0                                                                                                                                                | R/W-0/0                                                                               | R/W-0/0                                           | R/W-0/0         | R/W-0/0       | R/W-0/0        | R/W-0/0 | R/W-0/0      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|---------------|----------------|---------|--------------|--|

| NCOMD                                                                                                                                                  | TMR6MD                                                                                | TMR5MD                                            | TMR4MD          | TMR3MD        | TMR2MD         | TMR1MD  | TMR0MD       |  |

| bit 7                                                                                                                                                  |                                                                                       |                                                   | •               |               |                |         | bit (        |  |

| Logondy                                                                                                                                                |                                                                                       |                                                   |                 |               |                |         |              |  |

| Legend:                                                                                                                                                | e bit                                                                                 | \\/ \\/##abla                                     | L :4            |               | anted bit read |         |              |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other |                                                                                       |                                                   |                 |               |                |         |              |  |

|                                                                                                                                                        | •                                                                                     | x = Bit is unkr                                   |                 |               |                |         | ither Resets |  |

| '1' = Bit is se                                                                                                                                        | t                                                                                     | '0' = Bit is clea                                 | ared            | q = value dep | ends on condit | ion     |              |  |

| bit 7                                                                                                                                                  | 1 = NCO1 m                                                                            | able Numerical<br>odule disabled<br>odule enabled | ly Control Osci | llator bit    |                |         |              |  |

| bit 6                                                                                                                                                  | TMR6MD: Disable Timer TMR6 bit<br>1 = TMR6 module disabled<br>0 = TMR6 module enabled |                                                   |                 |               |                |         |              |  |

| bit 5                                                                                                                                                  | 1 = TMR5 mo                                                                           | sable Timer TM<br>odule disabled<br>odule enabled | IR5 bit         |               |                |         |              |  |

| bit 4                                                                                                                                                  | 1 = TMR4 mo                                                                           | sable Timer TM<br>odule disabled<br>odule enabled | IR4 bit         |               |                |         |              |  |

| bit 3                                                                                                                                                  | 1 = TMR3 mo                                                                           | sable Timer TM<br>odule disabled<br>odule enabled | IR3 bit         |               |                |         |              |  |

| bit 2                                                                                                                                                  | 1 = TMR2 m                                                                            | sable Timer TM<br>odule disabled<br>odule enabled | IR2 bit         |               |                |         |              |  |

| bit 1                                                                                                                                                  | 1 = TMR1 m                                                                            | sable Timer TM<br>odule disabled<br>odule enabled | IR1 bit         |               |                |         |              |  |

| bit 0                                                                                                                                                  | 1 = TMR0 m                                                                            | sable Timer TM<br>odule disabled<br>odule enabled | IR0 bit         |               |                |         |              |  |

# REGISTER 14-2: PMD1: PMD CONTROL REGISTER 1

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | U-0                                                   | U-0              | U-0    | U-0   |  |

|------------------|---------|-------------------|---------|-------------------------------------------------------|------------------|--------|-------|--|

| IOCBN7           | IOCBN6  | IOCBN5            | IOCBN4  | —                                                     | —                | —      | —     |  |

| bit 7            |         |                   |         |                                                       |                  |        | bit 0 |  |

|                  |         |                   |         |                                                       |                  |        |       |  |

| Legend:          |         |                   |         |                                                       |                  |        |       |  |

| R = Readable I   | bit     | W = Writable I    | bit     | U = Unimpler                                          | nented bit, read | as '0' |       |  |

| u = Bit is uncha | anged   | x = Bit is unkn   | own     | -n/n = Value at POR and BOR/Value at all other Resets |                  |        |       |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                       |                  |        |       |  |

# REGISTER 15-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER<sup>(1)</sup>

| bit 7-4 | <b>IOCBN&lt;7:4&gt;:</b> Interrupt-on-Change PORTB Negative Edge Enable bits<br>1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>be set upon detecting an edge.</li><li>0 = Interrupt-on-Change disabled for the associated pin</li></ul>                                                                     |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                           |

|         |                                                                                                                                                                                      |

# **Note 1:** PIC16(L)F18346 only.

# **REGISTER 15-6:** IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER<sup>(1)</sup>

| R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------|------------|------------|------------|-----|-----|-----|-------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | _   | —   | —   | —     |

| bit 7      |            |            |            |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-4 **IOCBF<7:4>:** Interrupt-on-Change PORTB Flag bits 1 = An enabled change was detected on the associated pin

Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

0 = No change was detected, or the user cleared the detected change.

# bit 3-0 Unimplemented: Read as '0'

**Note 1:** PIC16(L)F18346 only.

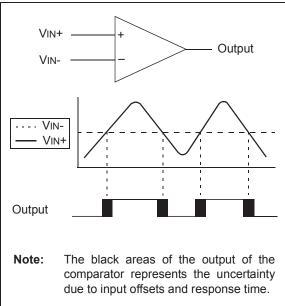

# 18.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Programmable input selection

- Selectable voltage reference

- Programmable output polarity

- Rising/falling output edge interrupts

- · Wake-up from Sleep

- CWG Auto-shutdown source

# 18.1 Comparator Overview

A single comparator is shown in Figure 18-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 18-1.

# TABLE 18-1: AVAILABLE COMPARATORS

| Device         | C1 | C2 |

|----------------|----|----|

| PIC16(L)F18326 | •  | •  |

| PIC16(L)F18346 | ٠  | •  |

#### FIGURE 18-1:

SINGLE COMPARATOR

| Name                  | Bit 7                 | Bit 6                 | Bit 5     | Bit 4  | Bit 3   | Bit 2    | Bit 1   | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|-----------|--------|---------|----------|---------|--------|---------------------|

| INTCON                | GIE                   | PEIE                  |           | —      | —       | —        |         | INTEDG | 100                 |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE      | TXIE   | SSP1IE  | BCL1IE   | TMR2IE  | TMR1IE | 102                 |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF      | TXIF   | SSP1IF  | BCL1IF   | TMR2IF  | TMR1IF | 107                 |

| TRISA                 | —                     | —                     | TRISA5    | TRISA4 | (2)     | TRISA2   | TRISA1  | TRISA0 | 143                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5    | TRISB4 | —       | —        | _       | _      | 149                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5    | TRISC4 | TRISC3  | TRISC2   | TRISC1  | TRISC0 | 155                 |

| ANSELA                | —                     | —                     | ANSA5     | ANSA4  |         | ANSA2    | ANSA1   | ANSA0  | 144                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5     | ANSB4  |         | _        | _       |        | 150                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5     | ANSC4  | ANSC3   | ANSC2    | ANSC1   | ANSC0  | 157                 |

| ADCON0                |                       |                       | CHS<      | 5:0>   |         |          | GO/DONE | ADON   | 244                 |

| ADCON1                | ADFM                  | A                     | ADCS<2:0> | •      |         | ADNREF   | ADPRE   | F<1:0> | 245                 |

| ADACT                 | —                     | —                     |           |        |         | ADACT<4: | )>      |        | 246                 |

| ADRESH                |                       |                       |           | ADRES  | SH<7:0> |          |         |        | 247                 |

| ADRESL                |                       |                       |           | ADRES  | SL<7:0> |          |         |        | 247                 |

| FVRCON                | FVREN                 | FVRRDY                | TSEN      | TSRNG  | CDAFV   | /R<1:0>  | ADFVR   | <1:0>  | 180                 |

| DAC1CON1              | —                     | —                     |           |        |         | DAC1R<4: | 0>      |        | 264                 |

| OSCSTAT1              | EXTOR                 | HFOR                  |           | LFOR   | SOR     | ADOR     | _       | PLLR   | 91                  |

# TABLE 22-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** -= unimplemented read as '0'. Shaded cells are not used for the ADC module.

**Note 1:** PIC16(L)F18346 only.

**2:** Unimplemented, read as '1'.

U

**S**

F18326/18346

DS40001839B-page 254

Preliminary

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|------------------|---------|--------------------|---------|----------------------------------------------------|---------|---------|---------|--|--|

|                  |         |                    | NCO1I   | NC<15:8>                                           |         |         |         |  |  |

| bit 7            |         |                    |         |                                                    |         |         | bit 0   |  |  |

|                  |         |                    |         |                                                    |         |         |         |  |  |

| Legend:          |         |                    |         |                                                    |         |         |         |  |  |

| R = Readable     | bit     | W = Writable b     | it      | U = Unimplemented bit, read as '0'                 |         |         |         |  |  |

| u = Bit is unch  | anged   | x = Bit is unkno   | own     | -n/n = Value at POR and BOR/Value at all other Res |         |         |         |  |  |

| '1' = Bit is set |         | '0' = Bit is clear | red     |                                                    |         |         |         |  |  |

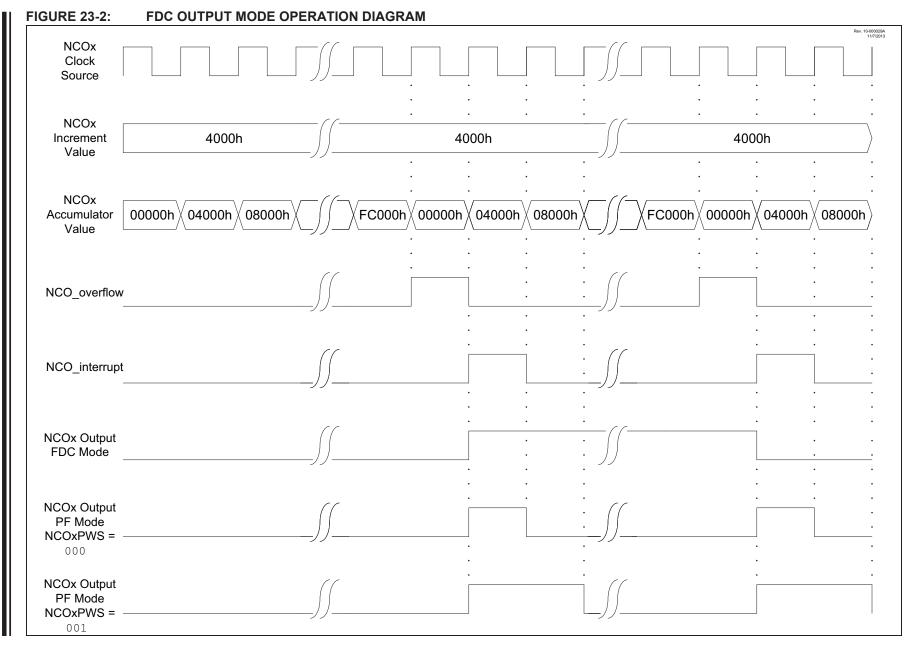

# **REGISTER 23-7:** NCO1INCH<sup>(1)</sup>: NCO1 INCREMENT REGISTER – HIGH BYTE

bit 7-0 NCO1INC<15:8>: NCO1 Increment, high byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

# **REGISTER 23-8:** NCO1INCU<sup>(1)</sup>: NCO1 INCREMENT REGISTER – UPPER BYTE

|       |     |     | • • • • • • • • • • • • • • • • • • • • |                |         |         |         |  |  |

|-------|-----|-----|-----------------------------------------|----------------|---------|---------|---------|--|--|

| U-0   | U-0 | U-0 | U-0                                     | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

| —     | —   | —   | —                                       | NCO1INC<19:16> |         |         |         |  |  |

| bit 7 |     |     |                                         |                |         |         | bit 0   |  |  |

# Legend:

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1INC<19:16>: NCO1 Increment, upper byte

**Note 1:** The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

# 25.11 Register Definitions: Modulation Control

|                                                                                                                                                                                                            | -R 25-1. WDCC                      |                                                                                   |                                |                |                   |                    |                      |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|----------------|-------------------|--------------------|----------------------|--|--|

| R/W-0/                                                                                                                                                                                                     | /0 U-0                             | U-0                                                                               | R/W-0/0                        | R-0/0          | U-0               | U-0                | R/W-0/0              |  |  |

| MDEN                                                                                                                                                                                                       | v —                                | _                                                                                 | MDOPOL                         | MDOUT          | _                 | _                  | MDBIT <sup>(2)</sup> |  |  |

| bit 7                                                                                                                                                                                                      | ·                                  |                                                                                   |                                |                | •                 |                    | bit 0                |  |  |

|                                                                                                                                                                                                            |                                    |                                                                                   |                                |                |                   |                    |                      |  |  |

| Legend:                                                                                                                                                                                                    |                                    |                                                                                   |                                |                |                   |                    |                      |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                                                                                                         |                                    |                                                                                   |                                |                |                   |                    |                      |  |  |

| u = Bit is                                                                                                                                                                                                 | unchanged                          | x = Bit is unk                                                                    | nown                           | -n/n = Value a | at POR and BO     | R/Value at all c   | other Resets         |  |  |

| '1' = Bit is                                                                                                                                                                                               | set                                | '0' = Bit is cle                                                                  | ared                           |                |                   |                    |                      |  |  |

| bit 7<br>bit 6-5                                                                                                                                                                                           | 1 = Modulate<br>0 = Modulate       | ulator Module E<br>or module is en<br>or module is dis<br>n <b>ted:</b> Read as ' | abled and mix<br>abled and has | • • •          | als               |                    |                      |  |  |

| bit 4                                                                                                                                                                                                      |                                    | lodulator Outpu                                                                   |                                | ct hit         |                   |                    |                      |  |  |

|                                                                                                                                                                                                            | 1 = Modulat                        | or output signal                                                                  | is inverted; id                | le high output |                   |                    |                      |  |  |

| bit 3                                                                                                                                                                                                      | MDOUT: Mo                          | dulator Output                                                                    | oit                            |                |                   |                    |                      |  |  |

|                                                                                                                                                                                                            | Displays the                       | current output                                                                    | alue of the mo                 | odulator modu  | le <sup>(1)</sup> |                    |                      |  |  |

| bit 2-1                                                                                                                                                                                                    | bit 2-1 Unimplemented: Read as '0' |                                                                                   |                                |                |                   |                    |                      |  |  |

| bit 0                                                                                                                                                                                                      | MDBIT: Allow                       | vs software to r                                                                  | nanually set m                 | odulation sour | rce input to mod  | ule <sup>(2)</sup> |                      |  |  |

| <b>Note 1:</b> The modulated output frequency can be greater and asynchronous from the clock that updates this register bit, the bit value may not be valid for higher speed modulator or carrier signals. |                                    |                                                                                   |                                |                |                   |                    |                      |  |  |

### REGISTER 25-1: MDCON: MODULATION CONTROL REGISTER

2: MDBIT must be selected as the modulation source in the MDSRC register for this operation.

| U-0              | U-0     | U-0                 | U-0            | R/W-x/u          | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------|---------------------|----------------|------------------|------------------|------------------|-------------|

|                  | —       | —                   | —              |                  | MDMS             | S<3:0>           |             |

| bit 7            | •       | ·                   |                |                  |                  |                  | bit C       |

|                  |         |                     |                |                  |                  |                  |             |

| Legend:          |         |                     |                |                  |                  |                  |             |

| R = Readable     | bit     | W = Writable        | bit            | U = Unimpler     | mented bit, read | l as '0'         |             |

| u = Bit is unch  | nanged  | x = Bit is unkr     | nown           | -n/n = Value a   | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set | Ū.      | '0' = Bit is clea   | ared           |                  |                  |                  |             |

|                  |         |                     |                |                  |                  |                  |             |

| bit 7-4          | Unimple | mented: Read as '   | ∩ <b>'</b>     |                  |                  |                  |             |

| bit 3-0          |         | 3:0> Modulation Sou |                | n hita           |                  |                  |             |

| DIL 3-0          |         |                     |                | IT DILS          |                  |                  |             |

|                  |         | CLC4 output         |                |                  |                  |                  |             |

|                  |         | CLC3 output         |                |                  |                  |                  |             |

|                  |         | CLC2 output         |                |                  |                  |                  |             |

|                  |         | CLC1 output         |                |                  |                  |                  |             |

|                  |         | NCO1 output         |                |                  |                  |                  |             |

|                  |         | EUSART1 TX outp     |                |                  |                  |                  |             |

|                  |         | MSSP2 SDO2 outp     |                |                  |                  |                  |             |

|                  |         | MSSP1 SDO1 outp     |                |                  |                  |                  |             |

|                  |         | C2 (Comparator 2)   |                |                  |                  |                  |             |

|                  | 0110 =  | C1 (Comparator 1)   | output         |                  |                  |                  |             |

|                  | 0101 =  | PWM6 output         |                |                  |                  |                  |             |

|                  |         | PWM5 output         |                |                  |                  |                  |             |

|                  | 0011 =  | CCP2 output (PWN    | 1 Output mod   | de only)         |                  |                  |             |

|                  | 0010 =  | CCP1 output (PWN    | 1 Output mod   | de only)         |                  |                  |             |

|                  | 0001 =  | MDMINPPS            |                |                  |                  |                  |             |

|                  | 0000 =  | MDBIT bit of MDCC   | ON register is | s modulation sou | urce             |                  |             |

# REGISTER 25-2: MDSRC: MODULATION SOURCE CONTROL REGISTER

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4                              | Bit 3                                        | Bit 2   | Bit 1 | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|--------|------------------------------------|----------------------------------------------|---------|-------|--------|---------------------|

| TRISA                 | _                     |                       | TRISA5 | TRISA4                             | TRISA4 — <sup>(2)</sup> TRISA2 TRISA1 TRISA0 |         |       |        |                     |

| ANSELA                |                       | _                     | ANSA5  | ANSA4                              | ANSA4 — ANSA2 ANSA1 ANSA0                    |         |       |        |                     |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5 | TRISB4                             | _                                            | —       | _     | —      | 149                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5  | ANSB4                              | _                                            | —       |       | —      | 150                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5 | TRISC4 TRISC3 TRISC2 TRISC1 TRISC0 |                                              |         |       |        |                     |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5  | ANSC4                              | ANSC3                                        | ANSC2   | ANSC1 | ANSC0  | 157                 |

| TMR0L                 | TMR0L<7:0>            |                       |        |                                    |                                              |         |       |        | 279                 |

| TMR0H                 |                       |                       | TN     | /IR0H<7:0>                         | or TMR0<15:8>                                |         |       |        | 279                 |

| T0CON0                | <b>T0EN</b>           | —                     | T0OUT  | T016BIT                            | Т                                            | 00UTPS< | :3:0> |        | 280                 |

| T0CON1                | 7                     | F0CS<2:0>             |        | TOASYNC                            |                                              | T0CKPS< | 3:0>  |        | 281                 |

| <b>T0CKIPPS</b>       | _                     | _                     | _      |                                    | TOCKIF                                       | PS<4:0> |       |        | 162                 |

| TMR0PPS               |                       |                       |        |                                    | TMR0F                                        | PS<4:0> |       |        | 162                 |

| ADACT                 | _                     | _                     | _      | ADACT<4:0>                         |                                              |         |       |        |                     |

| CLCxSELy              | _                     | _                     |        | LCxDyS<5:0>                        |                                              |         |       |        |                     |

| T1GCON                | TMR1GE                | T1GPOL                | T1GTM  | T1GSPM                             | T1GGO/DONE                                   | T1GVAL  | T1GSS | S<1:0> | 293                 |

| INTCON                | GIE                   | PEIE                  |        | _                                  | _                                            | _       | _     | INTEDG | 100                 |

| PIR0                  |                       |                       | TMR0IF | IOCIF                              | —                                            | _       |       | INTF   | 106                 |

| PIE0                  | _                     | _                     | TMR0IE | IOCIE                              | _                                            | —       | —     | INTE   | 101                 |

# TABLE 26-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

**Note 1:** PIC16(L)F18346 only.

2: Unimplemented, read as '1'.

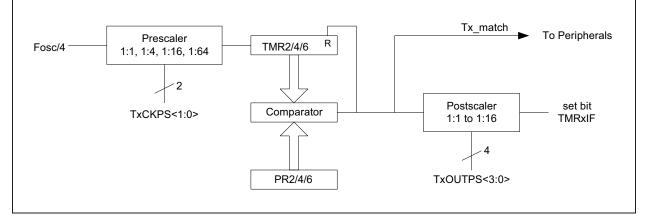

# 28.0 TIMER 2/4/6 MODULE

Timer2/4/6 modules are 8-bit timers that incorporate the following features:

- 8-bit Timer and Period registers (TMR2/4/6 and PR2/4/6, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2/4/6 match with PR2/4/6

- Optional use as the shift clock for the MSSPx module

See Figure 28-1 for a block diagram of Timer2/4/6.

- Note 1: In devices with more than one Timer module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the T2CON and T4CON control the same operational aspects of two completely different Timer modules.

- 2: Throughout this section, generic references to Timer2 module in any of its operating modes may be interpreted as being equally applicable to Timerx module. Register names, module signals, I/O pins and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

# 30.4.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, the clock is stretched, allowing the slave time to change the  $\overrightarrow{ACK}$  value before it is sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 30.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

# 30.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 30-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 30-5) affects the address matching process. See **Section 30.5.9** "SSP **Mask Register**" for more information.

# 30.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

### 30.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

# PIC16(L)F18326/18346

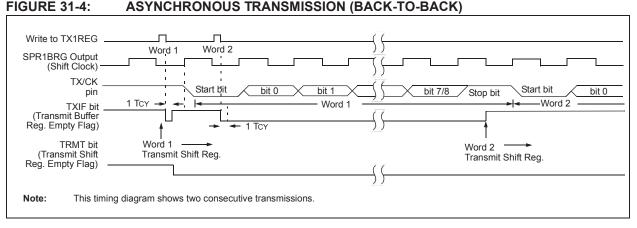

### 31.1.2 EUSART1 ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 31-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART1 receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RC1REG register.

# 31.1.2.1 Enabling the Receiver

The EUSART1 receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART1 control bits are assumed to be in their default state.

Setting the CREN bit of the RC1STA register enables the receiver circuitry of the EUSART1. Clearing the SYNC bit of the TX1STA register configures the EUSART1 for asynchronous operation. Setting the SPEN bit of the RC1STA register enables the EUSART1. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

Note: If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# 31.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 31.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART1 receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RC1REG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the Overrun condition is cleared. See Section 31.1.2.5 "Receive Overrun Error" for more information on overrun errors.

# 31.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART1 is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RC1STA register) or the Continuous Receive Enable bit (CREN of the RC1STA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence. To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RC1REG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# PIC16(L)F18326/18346

# FIGURE 34-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                |

|---------------------------------------------------------------------------------------|

| OPCODE d f (FILE #)                                                                   |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |

| Bit-oriented file register operations                                                 |

| OPCODE b (BIT #) f (FILE #)                                                           |

| b = 3-bit bit address<br>f = 7-bit file register address                              |

| Literal and control operations                                                        |

| General                                                                               |

| 13 8 7 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 8-bit immediate value                                                             |

| CALL and GOTO instructions only                                                       |

|                                                                                       |

| OPCODE k (literal)                                                                    |

| k = 11-bit immediate value                                                            |

| 13 7 6 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 7-bit immediate value                                                             |

| MOVLB instruction only<br>13 54 0                                                     |

| OPCODE k (literal)                                                                    |

| k = 5-bit immediate value                                                             |

| BRA instruction only<br>13 9 8 0                                                      |

| OPCODE k (literal)                                                                    |

| k = 9-bit immediate value                                                             |

| FSR Offset instructions<br>13 7 6 5 0                                                 |

| OPCODE n k (literal)                                                                  |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |

| FSR Increment instructions133210                                                      |

| OPCODE n m (mode)                                                                     |

| n = appropriate FSR<br>m = 2-bit mode value                                           |

| OPCODE only<br>13 0                                                                   |

| OPCODE                                                                                |

|                                                                                       |

| Standar       | rd Operating | g Conditions (unless otherwise sta | ted)       |                           |                                                          |

|---------------|--------------|------------------------------------|------------|---------------------------|----------------------------------------------------------|

| Param.<br>No. | Sym.         | Characteristic                     | Тур.       | Units                     | Conditions                                               |

| TH01          | θJA          | Thermal Resistance Junction to     | 70.0       | °C/W                      | 14-pin PDIP package                                      |

|               |              | Ambient                            | 95.3       | °C/W                      | 14-pin SOIC package                                      |

|               |              |                                    | 100.0      | °C/W                      | 14-pin TSSOP package                                     |

|               |              |                                    | 51.5       | °C/W                      | 16-pin UQFN 4x4mm package                                |

|               |              |                                    | 62.2       | °C/W                      | 20-pin PDIP package                                      |

|               |              |                                    | 87.3       | °C/W                      | 20-pin SSOP package                                      |

|               |              |                                    | 77.7       | °C/W                      | 20-pin SOIC package                                      |

|               |              |                                    | 43.0       | °C/W                      | 20-pin UQFN 4x4mm package                                |

| TH02          | θJC          | Thermal Resistance Junction to     | 32.75      | °C/W                      | 14-pin PDIR package                                      |

|               |              | Case                               | 31.0       | °C/W                      | 14-pin SOIC package                                      |

|               |              |                                    | 24.4       | °C/W                      | 14-pin-ISSOP package                                     |

|               |              |                                    | 5.4        | °C/W                      | 16-ph UQFN 4x4mm package                                 |

|               |              |                                    | 27.5       | °C/W                      | 20-pin PDIP package                                      |

|               |              |                                    | 31.1       | °CTW                      | 20-pin SSOP package                                      |

|               |              |                                    | 23.1       | °C/W                      | 20-pin SOIC package                                      |

|               |              |                                    | 5,3        | °C/W                      | 20-pin UQFN 4x4mm package                                |

| TH03          | TJMAX        | Maximum Junction Temperature       | _150       | Q                         |                                                          |

| TH04          | PD           | Power Dissipation                  | 0.800      | /W/                       | PD = PINTERNAL + PI/O                                    |

| TH05          | PINTERNAL    | Internal Power Dissipation         |            | $\mathbb{V}^{\mathbb{V}}$ | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06          | Pi/o         | I/O Power Dissipation              |            | Ŵ                         | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07          | Pder         | Derated Power                      | $\searrow$ | Ŵ                         | Pder = PDmax (Τj - Ta)/θja <sup>(2)</sup>                |

# TABLE 35-6: THERMAL CHARACTERISTICS

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

# PIC16(L)F18326/18346

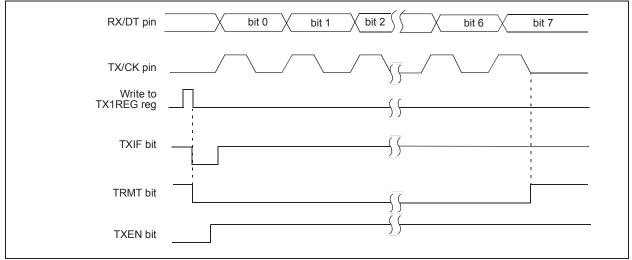

#### FIGURE 35-12: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

# TABLE 35-17: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Standa        | rd Operating | g Conditions (un                                     | less otherwis                                           | se stated) 🖉 🦯    |                                           | $\sim$ |        |       |                       |

|---------------|--------------|------------------------------------------------------|---------------------------------------------------------|-------------------|-------------------------------------------|--------|--------|-------|-----------------------|

| Param.<br>No. | Sym.         | Characteristic                                       |                                                         |                   | Min.                                      | Typ.†  | Max.   | Units | Conditions            |

| 40*           | T⊤0H         | T0CKI High Pulse                                     | Width No Prescaler                                      |                   | 0.5 TCY + 20                              | —      | —      | ns    |                       |

|               |              |                                                      |                                                         | With Rrescaler    | 10                                        | —      | —      | ns    |                       |

| 41*           | TT0L         | T0CKI Low Pulse                                      | Width                                                   | No Rrescaler      | 0.5 TCY + 20                              | —      | —      | ns    |                       |

|               |              |                                                      | $\sim$                                                  | With Prescaler    | 10                                        | —      | —      | ns    |                       |

| 42*           | Тт0Р         | T0CKI Period                                         |                                                         |                   | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | —      | ns    | N = prescale<br>value |

| 45*           | T⊤1H         | T1CKI High Time                                      | Synchronou                                              | s, No Prescaler   | 0.5 Tcy + 20                              | —      | —      | ns    |                       |

|               |              |                                                      | Synchronou                                              | s, with Prescaler | 15                                        | —      | —      | ns    |                       |

|               |              |                                                      | Asynchrono                                              | us                | 30                                        | —      | —      | ns    |                       |

| 46*           | TT1L         | T1CKI Low Time                                       | Synchronou                                              | s, No Prescaler   | 0.5 Tcy + 20                              | —      | —      | ns    |                       |

|               |              |                                                      | Synchronou                                              | s, with Prescaler | 15                                        | —      | —      | ns    |                       |

|               |              |                                                      | Asynchrono                                              | us                | 30                                        | _      |        | ns    |                       |

| 47*           | Тт1Р         | T1CKI Input<br>Period                                | Synchronous                                             |                   | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | —      | ns    | N = prescale<br>value |

|               |              |                                                      |                                                         |                   | 60                                        | —      | —      | ns    |                       |

| 48            | FT1          |                                                      | itor Input Frequency Range<br>I by setting bit T10SCEN) |                   | 32.4                                      | 32.768 | 33.1   | kHz   |                       |

| 49*           | TCKEZTMR1    | Delay from External Clock Edge to Timer<br>Increment |                                                         |                   | 2 Tosc                                    | —      | 7 Tosc | —     | Timers in Sync mode   |

| / (*          | These paran  | eters are character                                  | rized but not t                                         | ested.            | 1                                         | 1      | 1      | 1     | ı                     |

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

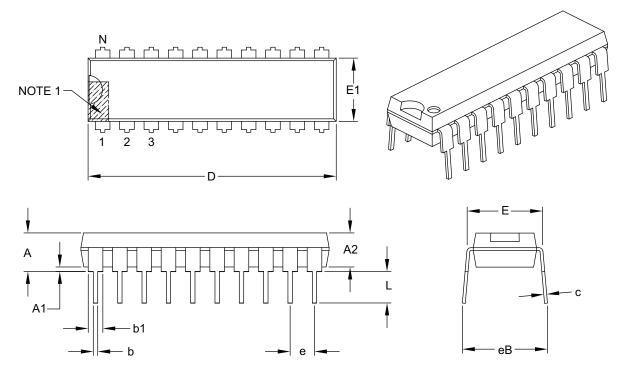

# 20-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      |          | INCHES |  |  |  |

|----------------------------|----------|------|----------|--------|--|--|--|

| Dimension                  | n Limits | MIN  | NOM      | MAX    |  |  |  |

| Number of Pins             | Ν        | 20   |          |        |  |  |  |

| Pitch                      | е        |      | .100 BSC |        |  |  |  |

| Top to Seating Plane       | Α        | -    | -        | .210   |  |  |  |

| Molded Package Thickness   | A2       | .115 | .130     | .195   |  |  |  |

| Base to Seating Plane      | A1       | .015 | -        | _      |  |  |  |

| Shoulder to Shoulder Width | E        | .300 | .310     | .325   |  |  |  |

| Molded Package Width       | E1       | .240 | .250     | .280   |  |  |  |

| Overall Length             | D        | .980 | 1.030    | 1.060  |  |  |  |

| Tip to Seating Plane       | L        | .115 | .130     | .150   |  |  |  |

| Lead Thickness             | С        | .008 | .010     | .015   |  |  |  |

| Upper Lead Width           | b1       | .045 | .060     | .070   |  |  |  |

| Lower Lead Width           | b        | .014 | .018     | .022   |  |  |  |

| Overall Row Spacing §      | eB       | _    | _        | .430   |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

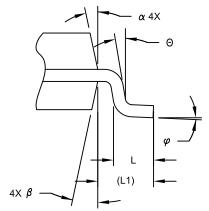

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | MILLIMETERS |          |           |      |  |  |

|--------------------------|-------------|----------|-----------|------|--|--|

| Dimension Lim            | nits        | MIN      | NOM       | MAX  |  |  |

| Number of Pins           | N           |          | 20        |      |  |  |

| Pitch                    | е           |          | 1.27 BSC  |      |  |  |

| Overall Height           | A           | -        | -         | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05     | -         | -    |  |  |

| Standoff §               | A1          | 0.10     | -         | 0.30 |  |  |

| Overall Width            | E           |          | 10.30 BSC |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC |           |      |  |  |

| Overall Length D         |             |          | 12.80 BSC |      |  |  |

| Chamfer (Optional)       | h           | 0.25     | -         | 0.75 |  |  |

| Foot Length              | L           | 0.40     | -         | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF |           |      |  |  |

| Lead Angle               | Θ           | 0°       | -         | -    |  |  |

| Foot Angle               | φ           | 0°       | -         | 8°   |  |  |

| Lead Thickness           | С           | 0.20     | -         | 0.33 |  |  |

| Lead Width               | b           | 0.31     | -         | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°       | -         | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -         | 15°  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2