Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18346-e-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16(L)F18326/18346

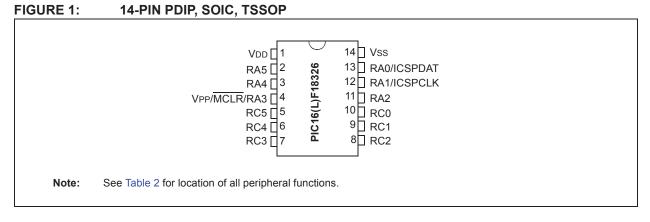

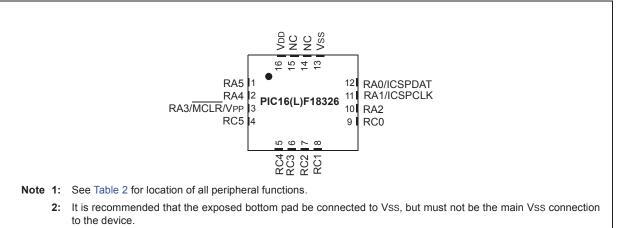

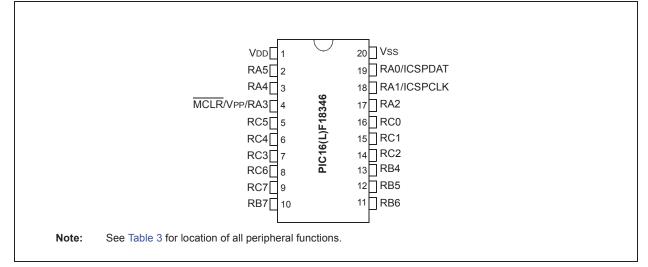

## **Pin Diagrams**

## FIGURE 2: 16-PIN UQFN (4x4)

## FIGURE 3: 20-PIN PDIP, SOIC, SSOP

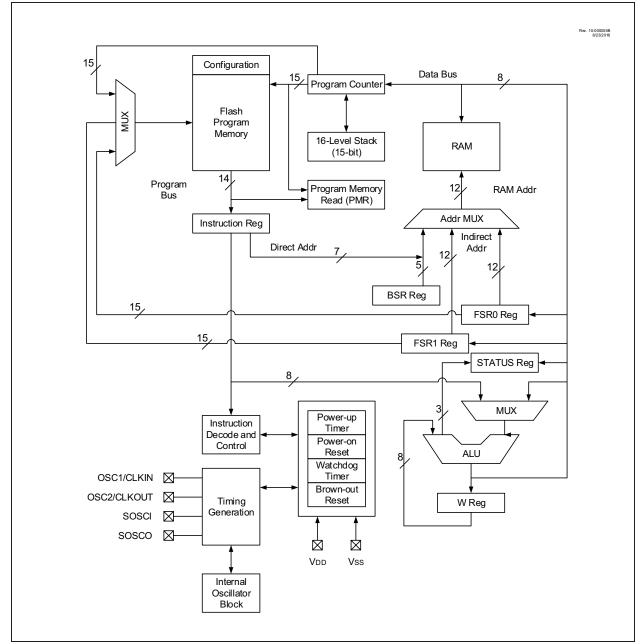

## 3.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 48 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16-levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

FIGURE 3-1: CORE BLOCK DIAGRAM

| TABLE                                           | 4-4: SPEC  | IAL F                            | <b>UNCTION RE</b> | GISTER S | UMMARY B | ANKS 0-31 ( | CONTINUE | <b>)</b> ) |           |       |                       |                                 |

|-------------------------------------------------|------------|----------------------------------|-------------------|----------|----------|-------------|----------|------------|-----------|-------|-----------------------|---------------------------------|

| Address                                         | Name       | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7             | Bit 6    | Bit 5    | Bit 4       | Bit 3    | Bit 2      | Bit 1     | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank 1                                          | 3          |                                  |                   |          |          |             |          |            |           |       |                       |                                 |

| CPU CORE REGISTERS; see Table 4-2 for specifics |            |                                  |                   |          |          |             |          |            |           |       |                       |                                 |

| 68Ch                                            | —          | —                                |                   |          |          | Unimple     | mented   |            |           |       | _                     | —                               |

| 68Dh                                            | —          | —                                |                   |          |          | Unimple     | mented   |            |           |       | _                     | —                               |

| 68Eh                                            | —          | —                                |                   |          |          | Unimple     | mented   |            |           |       | —                     | —                               |

| 68Fh                                            | —          | —                                |                   |          |          | Unimple     | mented   |            |           |       | -                     | —                               |

| 690h                                            | —          | —                                |                   |          |          | Unimple     | mented   |            |           |       | -                     | —                               |

| 691h                                            | CWG1CLKCON |                                  | —                 | —        | —        | _           | —        | —          | —         | CS    | 0                     | 0                               |

| 692h                                            | CWG1DAT    |                                  | —                 | _        | —        | _           |          | DAT        | <3:0>     |       | 0000                  | 0000                            |

| 693h                                            | CWG1DBR    |                                  | —                 | _        |          |             | DBR∢     | <5:0>      |           |       | 00 0000               | 00 0000                         |

| 694h                                            | CWG1DBF    |                                  | —                 | _        |          |             | DBF<     | <5:0>      |           |       | 00 0000               | 00 0000                         |

| 695h                                            | CWG1CON0   |                                  | EN                | LD       | —        | _           | —        |            | MODE<2:0> |       | 00000                 | 00000                           |

| 696h                                            | CWG1CON1   |                                  | —                 | _        | IN       | _           | POLD     | POLC       | POLB      | POLA  | x- 0000               | x- 0000                         |

| 697h                                            | CWG1AS0    |                                  | SHUTDOWN          | REN      | LSBE     | )<1:0>      | LSAC     | <1:0>      | —         | —     | 0001 01               | 0001 01                         |

AS4E

**OVRA**

Unimplemented

AS2E

STRC

AS3E

STRD

AS1E

STRB

AS0E

STRA

---0 0000

0000 0000 0000 0000

---0 0000

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

\_

OVRB

Only on PIC16F18326/18346. Note 1:

CWG1AS1

CWG1STR

Register accessible from both User and ICD Debugger. 2:

\_

\_

OVRD

\_

OVRC

698h

699h

69Fh

69Ah to

## PIC16(L)F18326/18346

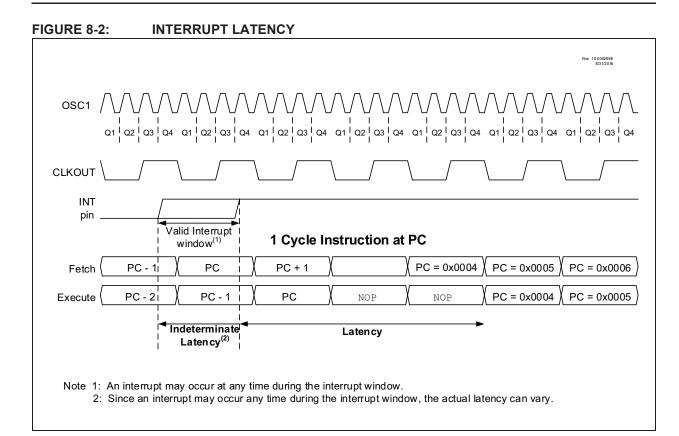

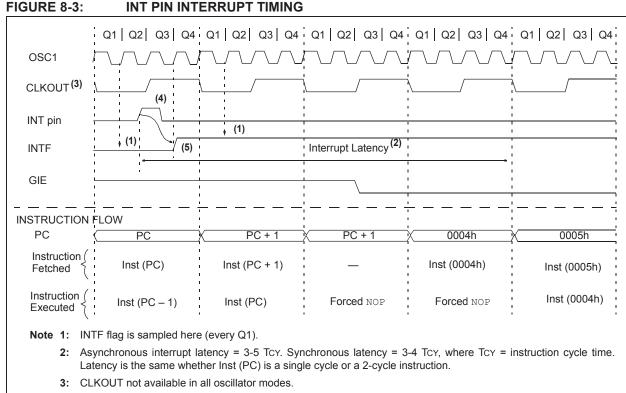

4: For minimum width of INT pulse, refer to AC specifications in Section 35.0 "Electrical Specifications"".

**5:** INTF is enabled to be set any time during the Q4-Q1 cycles.

| R/W-0/0                  | R/W-0/0                    | R/W-0/0           | R/W-0/0 | R/W-0/0       | R/W-0/0          | R/W-0/0 | R/W-0/0     |

|--------------------------|----------------------------|-------------------|---------|---------------|------------------|---------|-------------|

| CWG2MD                   | CWG1MD                     | PWM6MD            | PWM5MD  | CCP4MD        | CCP3MD           | CCP2MD  | CCP1MD      |

| bit 7                    |                            |                   |         |               | •                |         | bit         |

| Legend:                  |                            |                   |         |               |                  |         |             |

| R = Readable             | , bit                      | W = Writable      | bit     |               | nented bit, read | as 'O'  |             |

|                          |                            |                   |         |               | it POR and BO    |         | ther Pecets |

| (1) = Bit is unclthe set | •                          | 0' = Bit is clear |         |               | ends on condit   |         |             |

| I - DILIS SEL            |                            |                   | areu    | q – value uep |                  |         |             |

| bit 7                    | CWG2MD: Di                 | isable CWG2 b     | it      |               |                  |         |             |

|                          |                            | odule disabled    |         |               |                  |         |             |

|                          | 0 = CWG2 m                 | odule enabled     |         |               |                  |         |             |

| bit 6                    |                            | isable CWG1 b     | it      |               |                  |         |             |

|                          |                            | odule disabled    |         |               |                  |         |             |

| bit 5                    |                            | isable PWM6 b     | :+      |               |                  |         |             |

| DIL 5                    |                            | odule disabled    | IL      |               |                  |         |             |

|                          |                            | odule enabled     |         |               |                  |         |             |

| bit 4                    | PWM5MD: Di                 | isable PWM5 b     | it      |               |                  |         |             |

|                          | 1 = PWM5 m                 | odule disabled    |         |               |                  |         |             |

|                          | 0 = PWM5 m                 | odule enabled     |         |               |                  |         |             |

| bit 3                    |                            | sable CCP4 bit    |         |               |                  |         |             |

|                          | 1 = CCP4 mo<br>0 = CCP4 mo |                   |         |               |                  |         |             |

| <b>h</b> it 0            |                            |                   |         |               |                  |         |             |

| bit 2                    |                            | sable CCP3 bit    |         |               |                  |         |             |

|                          | 0 = CCP3 mc                |                   |         |               |                  |         |             |

| bit 1                    | CCP2MD: Dis                | sable CCP2 bit    |         |               |                  |         |             |

|                          | 1 = CCP2 m                 | odule disabled    |         |               |                  |         |             |

|                          | 0 = CCP2 m                 | odule enabled     |         |               |                  |         |             |

| bit 0                    |                            | sable CCP1 bit    |         |               |                  |         |             |

|                          |                            | odule disabled    |         |               |                  |         |             |

|                          | 0 = CCP1 m                 | odule enabled     |         |               |                  |         |             |

## REGISTER 14-4: PMD3: PMD CONTROL REGISTER 3

## 15.0 INTERRUPT-ON-CHANGE

All pins on all ports can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual pin, or combination of pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable

- Rising and falling edge detection

- Individual pin configuration

- · Individual pin interrupt flags

Figure 15-1 is a block diagram of the IOC module.

## 15.1 Enabling the Module

To allow individual pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 15.2 Individual Pin Configuration

For each pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting the associated bits in both of the IOCxP and IOCxN registers.

## 15.3 Interrupt Flags

The bits located in the IOCxF registers are status flags that correspond to the interrupt-on-change pins of each port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIR0 register reflects the status of all IOCxF bits.

## 15.4 Clearing Interrupt Flags

The individual status flags, (IOCxF register bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

### EXAMPLE 15-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 15.5 Operation in Sleep

The interrupt-on-change interrupt event will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the affected IOCxF register will be updated prior to the first instruction executed out of Sleep.

## **19.2 Register Definitions: PWM Control**

| REGISTER         | 9-1: PVVIVIX                             |                   | CONTROL         | EGISTER          |                  |                  |              |

|------------------|------------------------------------------|-------------------|-----------------|------------------|------------------|------------------|--------------|

| R/W-0/0          | U-0                                      | R-0               | R/W-0/0         | U-0              | U-0              | U-0              | U-0          |

| PWMxEN           | —                                        | PWMxOUT           | PWMxPOL         | —                | —                | —                | —            |

| bit 7            |                                          |                   |                 |                  |                  |                  | bit 0        |

| r                |                                          |                   |                 |                  |                  |                  |              |

| Legend:          |                                          |                   |                 |                  |                  |                  |              |

| R = Readable     | bit                                      | W = Writable      | bit             | U = Unimpler     | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged                                    | x = Bit is unkr   | nown            | -n/n = Value a   | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                          | '0' = Bit is clea | ared            |                  |                  |                  |              |

|                  |                                          |                   |                 |                  |                  |                  |              |

| bit 7            | PWMxEN: PV                               | VM Module En      | able bit        |                  |                  |                  |              |

|                  | 1 = PWM mc                               | dule is enable    | d               |                  |                  |                  |              |

|                  | 0 = PWM mc                               | dule is disable   | d               |                  |                  |                  |              |

| bit 6            | Unimplemen                               | ted: Read as '    | 0'              |                  |                  |                  |              |

| bit 5            | PWMxOUT: F                               | PWM Module C      | output Level wl | nen bit is read. |                  |                  |              |

| bit 4            | PWMxPOL: PWMx Output Polarity Select bit |                   |                 |                  |                  |                  |              |

|                  | 1 = PWM out                              | put is active-lo  | w.              |                  |                  |                  |              |

|                  | 0 = PWM out                              | tput is active-hi | gh.             |                  |                  |                  |              |

| bit 3-0          | Unimplemen                               | ted: Read as '    | 0'              |                  |                  |                  |              |

|                  |                                          |                   |                 |                  |                  |                  |              |

## REGISTER 19-1: PWMxCON: PWM CONTROL REGISTER

## REGISTER 19-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PWMxE   | )C<9:2> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PWMxDC<9:2>:** PWM Duty Cycle Most Significant bits

These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 19-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| PWMxDC  | C<1:0>  | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 **PWMxDC<1:0>:** PWM Duty Cycle Least Significant bits These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register.

bit 5-0 Unimplemented: Read as '0'

## 25.1 DSM Operation

The DSM module can be enabled by setting the MDEN bit in the MDCON register. Clearing the MDEN bit in the MDCON register, disables the DSM module by automatically switching the carrier high and carrier low signals to the Vss signal source. The modulator signal source is also switched to the MDBIT in the MDCON register. This not only assures that the DSM module is inactive, but that it is also consuming the least amount of current.

The values used to select the carrier high, carrier low, and modulator sources held by the Modulation Source, Modulation High Carrier, and Modulation Low Carrier control registers are not affected when the MDEN bit is cleared and the DSM module is disabled. The values inside these registers remain unchanged while the DSM is inactive. The sources for the carrier high, carrier low and modulator signals will once again be selected when the MDEN bit is set and the DSM module is again enabled and active.

The modulated output signal can be disabled without shutting down the DSM module. The DSM module will remain active and continue to mix signals, but the output value will not be sent to the DSM pin. During the time that the output is disabled, the DSM pin will remain low. The modulated output can be disabled by clearing the MDEN bit in the MDCON register.

## 25.2 Modulator Signal Sources

The modulator signal can be supplied from the following sources:

- CCP1 Output

- CCP2 Output

- PWM5 Output

- PWM6 Output

- MSSP1 SDO1 (SPI mode only)

- MSSP2 SDO2 (SPI mode only)

- Comparator C1 Output

- Comparator C2 Output

- EUSART1 TX Output

- External Signal on MDMIN pin

- NCO1 Output

- CLC1 Output

- CLC2 Output

- CLC3 Output

- CLC4 Output

- · MDBIT bit in the MDCON register

The modulator signal is selected by configuring the MDMS <3:0> bits in the MDSRC register.

## 25.3 Carrier Signal Sources

The carrier high signal and carrier low signal can be supplied from the following sources:

- CCP1 Output

- CCP2 Output

- PWM5 Output

- PWM6 Output

- NCO1 Output

- Fosc (System Clock)

- HFINTOSC

- CLC1 Output

- CLC2 Output

- CLC3 Output

- CLC4 Output

- CLKR

- External Signal on MDCIN1 pin

- External Signal on MDCIN2 pin

- Vss

The carrier high signal is selected by configuring the MDCH <3:0> bits in the MDCARH register. The carrier low signal is selected by configuring the MDCL <3:0> bits in the MDCARL register.

## 25.4 Carrier Synchronization

During the time when the DSM switches between carrier high and carrier low signal sources, the carrier data in the modulated output signal can become truncated. To prevent this, the carrier signal can be synchronized to the modulator signal. When the modulator signal transitions away from the synchronized carrier, the unsynchronized carrier source is immediately active, while the synchronized carrier remains active until its next falling edge. When the modulator signal transitions back to the synchronized carrier, the unsynchronized carrier is immediately disabled, and the modulator waits until the next falling edge of the synchronized carrier before the synchronized carrier becomes active.

Synchronization is enabled separately for the carrier high and carrier low signal sources. Synchronization for the carrier high signal is enabled by setting the MDCHSYNC bit in the MDCARH register. Synchronization for the carrier low signal is enabled by setting the MDCLSYNC bit in the MDCARL register.

Figure 25-1 through Figure 25-6 show timing diagrams of using various synchronization methods.

## **REGISTER 27-3:** TMRxL<sup>(1)</sup>: TIMERx LOW BYTE REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | TMRx    | L<7:0>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 TMRxL<7:0>: TMRx Low Byte bits

Note 1: 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

## REGISTER 27-4: TMRxH<sup>(1)</sup>: TIMERx HIGH BYTE REGISTER

| bit 7      |         |         |         |         |         |         | bit 0   |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| TMRxH<7:0> |         |         |         |         |         |         |         |  |

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>: TMRx High Byte bits

**Note 1:** 'x' refers to either '1', '3' or '5' for the respective Timer1/3/5 registers.

| R/W-x/x          | R/W-x/x | R/W-x/x                            | R/W-x/x | R/W-x/x      | R/W-x/x          | R/W-x/x        | R/W-x/x     |

|------------------|---------|------------------------------------|---------|--------------|------------------|----------------|-------------|

|                  |         |                                    | CCPR    | xL<7:0>      |                  |                |             |

| bit 7            |         |                                    |         |              |                  |                | bit 0       |

|                  |         |                                    |         |              |                  |                |             |

| Legend:          |         |                                    |         |              |                  |                |             |

| R = Readable     | bit     | W = Writable bi                    | t       | U = Unimpler | mented bit, read | d as '0'       |             |

| u = Bit is unch  | anged   | x = Bit is unkno                   | wn      | -n/n = Value | at POR and BC    | R/Value at all | other Reset |

| '1' = Bit is set |         | '0' = Bit is clear                 | ed      |              |                  |                |             |

|                  |         |                                    |         |              |                  |                |             |

| bit 7-0          |         | = Capture mode<br>L<7:0>: Captured |         | /R1/3/5I     |                  |                |             |

### REGISTER 29-3: CCPRxL REGISTER: CCPx REGISTER LOW BYTE

| Capture mode<br>Captured value of TMR1/3/5L                |

|------------------------------------------------------------|

| Compare mode                                               |

| 7:0>: LS Byte compared to TMR1/3/5L                        |

| PWM modes when CCPxFMT = 0                                 |

| 7:0>: CCPW<7:0> – Pulse-width Least Significant eight bits |

| PWM modes when CCPxFMT = 1                                 |

| 7:6>: CCPW<1:0> – Pulse-width Least Significant two bits   |

| <5:0>: Not used.                                           |

|                                                            |

## REGISTER 29-4: CCPRxH REGISTER: CCPx REGISTER HIGH BYTE

| R/W-x/x          | R/W-x/x | R/W-x/x           | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x        | R/W-x/x     |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|-------------|

|                  |         |                   | CCPR    | xH<7:0>        |                  |                |             |

| bit 7            |         |                   |         |                |                  |                | bit 0       |

|                  |         |                   |         |                |                  |                |             |

| Legend:          |         |                   |         |                |                  |                |             |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimpler   | mented bit, read | d as '0'       |             |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BC    | R/Value at all | other Reset |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |             |

|                  |         |                   |         |                |                  |                |             |

| bit 7-0 | CCPxMODE = Capture mode                                          |

|---------|------------------------------------------------------------------|

|         | CCPRxH<7:0>: Captured value of TMR1/3/5H                         |

|         | CCPxMODE = Compare mode                                          |

|         | CCPRxH<7:0>: MS Byte compared to TMR1/3/5H                       |

|         | CCPxMODE = PWM modes when CCPxFMT = 0                            |

|         | CCPRxH<7:2>: Not used                                            |

|         | CCPRxH<1:0>: CCPW<9:8> – Pulse-width Most Significant two bits   |

|         | CCPxMODE = PWM modes when CCPxFMT = 1                            |

|         | CCPRxH<7:0>: CCPW<9:2> – Pulse-width Most Significant eight bits |

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4   | Bit 3   | Bit 2       | Bit 1   | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------|---------|---------|-------------|---------|--------|---------------------|

| TRISA                 | —                     | _                     | TRISA5   | TRISA4  | (2)     | TRISA2      | TRISA1  | TRISA0 | 143                 |

| ANSELA                | _                     | _                     | ANSA5    | ANSA4   | _       | ANSA2       | ANSA1   | ANSA0  | 144                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4  | _       | —           | _       | —      | 149                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5    | ANSB4   | _       | —           |         | —      | 150                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4  | TRISC3  | TRISC2      | TRISC1  | TRISC0 | 155                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5    | ANSC4   | ANSC3   | ANSC2       | ANSC1   | ANSC0  | 157                 |

| INTCON                | GIE                   | PEIE                  | —        | —       | _       | _           | _       | INTEDG | 100                 |

| PIR4                  | CWG2IF                | CWG1IF                | TMR5GIF  | TMR5IF  | CCP4IF  | CCP3IF      | CCP2IF  | CCP1IF | 110                 |

| PIE4                  | CWG2IE                | CWGIE                 | TMR5GIE  | TMR5IE  | CCP4IE  | CCP3IE      | CCP2IE  | CCP1IE | 105                 |

| CCPxCON               | CCPxEN                | _                     | CCPxOUT  | CCPxFMT |         | CCPxMO      | DE<3:0> |        | 308                 |

| CCPxCAP               | —                     | _                     | _        | _       |         | CCPxC       | S<3:0>  |        | 309                 |

| CCPRxL                |                       |                       |          | CCPRx<7 | 7:0>    |             |         |        | 310                 |

| CCPRxH                |                       |                       |          | CCPRx<1 | 5:8>    |             |         |        | 310                 |

| CCPTMRS               | C4TSI                 | EL<1:0>               | C3TSEL   | .<1:0>  | C2TSE   | EL<1:0>     | C1TSE   | L<1:0> | 311                 |

| CCP1PPS               | —                     | _                     | _        |         | C       | CP1PPS<4:0  | >       |        | 162                 |

| CCP2PPS               | _                     | _                     | _        |         | C       | CP2PPS<4:0  | >       |        | 162                 |

| CCP3PPS               | —                     | _                     | _        |         | С       | CP3PPS<4:0  | >       |        | 162                 |

| CCP4PPS               | _                     | _                     | _        |         | C       | CP4PPS<4:0  | >       |        | 162                 |

| RxyPPS                | —                     | _                     | _        |         | F       | RxyPPS<4:0> |         |        | 163                 |

| ADACT                 | —                     | _                     | _        |         |         | ADACT<4:0>  |         |        | 246                 |

| CLCxSELy              | —                     | _                     |          |         | LCxDyS- | <5:0>       |         |        | 229                 |

| CWGxDAT               | —                     | —                     | —        | —       |         | DAT<        | :3:0>   |        | 215                 |

| MDSRC                 | —                     | —                     | —        | —       |         | MDMS        | s<3:0>  |        | 272                 |

| MDCARH                | —                     | MDCHPOL               | MDCHSYNC | —       |         | MDCH        | <3:0>   |        | 273                 |

| MDCARL                | —                     | MDCLPOL               | MDCLSYNC | —       |         | MDCL        | <3:0>   |        | 274                 |

## TABLE 29-4: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

**Note 1:** PIC16(L)F18346 only.

2: Unimplemented, read as '1'.

## PIC16(L)F18326/18346

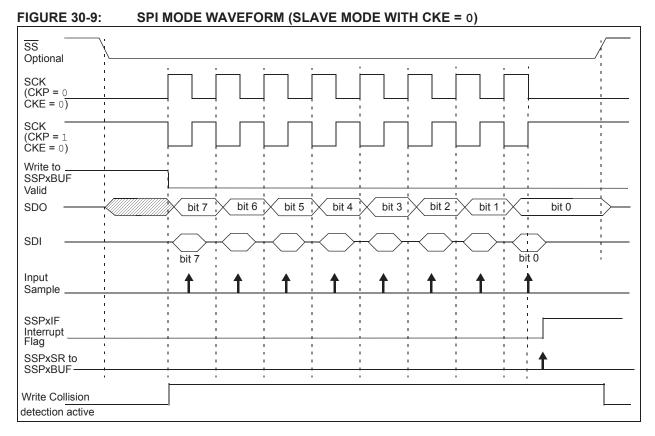

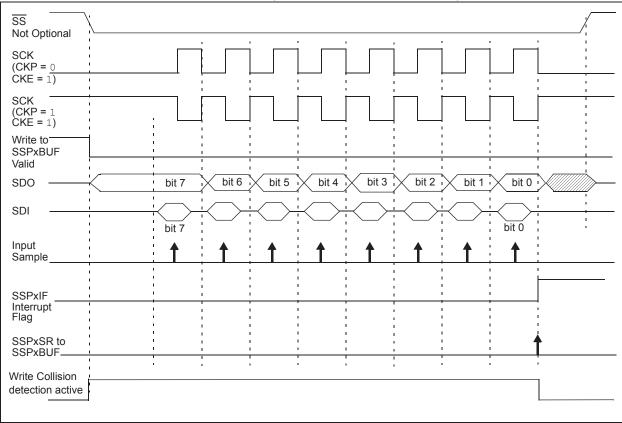

## FIGURE 30-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

DS40001839B-page 322

## 30.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

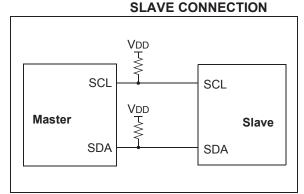

## 30.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Figure 30-11 shows the block diagram of the MSSPx module when operating in  $I^2C$  mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 30-2 and Figure 30-3 show a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

Slave Receive mode (slave is receiving data from the master)

To begin communication, the master device sends out a Start condition followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either transmit or receive data from the slave device.

## FIGURE 30-11: I<sup>2</sup>C MASTER/

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends a NACK in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send a Restart condition in place of the Stop bit or last ACK bit when it is in Receive mode.

The  $I^2C$  bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

## 30.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

<sup>© 2016-2017</sup> Microchip Technology Inc.

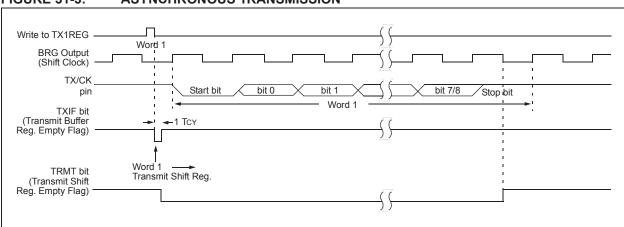

## 31.1.1.5 TSR Status

The TRMT bit of the TX1STA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TX1REG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

## 31.1.1.6 Transmitting 9-bit Characters

The EUSART1 supports 9-bit character transmissions. When the TX9 bit of the TX1STA register is set, the EUSART1 will shift nine bits out for each character transmitted. The TX9D bit of the TX1STA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TX1REG. All nine bits of data will be transferred to the TSR shift register immediately after the TX1REG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 31.1.2.7** "Address **Detection**" for more information on the Address mode.

## 31.1.1.7 Asynchronous Transmission Setup

- Initialize the SP1BRGH, SP1BRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 31.3 "EUSART1 Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TX1REG register. This will start the transmission.

## FIGURE 31-3: ASYNCHRONOUS TRANSMISSION

| R/W-0/0          | U-0                          | U-0               | R/W-1/1        | R/W-0/0                 | R/W-0/0         | R/W-0/0          | R/W-0/0        |

|------------------|------------------------------|-------------------|----------------|-------------------------|-----------------|------------------|----------------|

| CLKREN — — CLK   |                              |                   | CLKRI          | DC<1:0>                 |                 | CLKRDIV<2:0>     |                |

| bit 7            | ·                            |                   |                |                         |                 |                  | bit C          |

| Legend:          |                              |                   |                |                         |                 |                  |                |

| R = Readable     | e bit                        | W = Writable      | bit            | U = Unimpler            | nented bit, rea | d as '0'         |                |

| u = Bit is unc   | hanged                       | x = Bit is unkr   | nown           | -n/n = Value a          | at POR and BC   | R/Value at all o | other Resets   |

| '1' = Bit is set | t                            | '0' = Bit is clea | ared           |                         |                 |                  |                |

|                  |                              |                   |                |                         |                 |                  |                |

| bit 7            | CLKREN: Re                   | eference Clock    | Module Enable  | e bit                   |                 |                  |                |

|                  | 1 = Referer                  | nce clock modu    | le enabled     |                         |                 |                  |                |

|                  | 0 = Referer                  | nce clock modu    | le is disabled |                         |                 |                  |                |

| bit 6-5          | Unimplemen                   | nted: Read as '   | 0'             |                         |                 |                  |                |

| bit 4-3          | CLKRDC<1:                    | 0>: Reference     | Clock Duty Cy  | cle bits <sup>(1)</sup> |                 |                  |                |

|                  |                              | utputs duty cycl  |                |                         |                 |                  |                |

|                  | 10 = Clock of                | utputs duty cycl  | e of 50%       |                         |                 |                  |                |

|                  |                              | utputs duty cycl  |                |                         |                 |                  |                |

|                  | 00 = Clock of                | utputs duty cycl  | e of 0%        |                         |                 |                  |                |

| bit 2-0          | CLKRDIV<2:                   | :0>: Reference    | Clock Divider  | bits                    |                 |                  |                |

|                  |                              | divided by 128    |                |                         |                 |                  |                |

|                  | 110 <b>= Fosc d</b>          |                   |                |                         |                 |                  |                |

|                  | 101 <b>= Fosc d</b>          | •                 |                |                         |                 |                  |                |

|                  | 100 = Fosc (<br>011 = Fosc ( |                   |                |                         |                 |                  |                |

|                  | 010 = Fosc (                 | •                 |                |                         |                 |                  |                |

|                  | 001 = Fosc (                 | •                 |                |                         |                 |                  |                |

|                  | 000 = Fosc                   |                   |                |                         |                 |                  |                |

| Note 1. Bi       | ts are valid for F           | Peference Clock   | divider value  | e of two or larg        | ar the base clo | ock cannot be fi | urther divided |

## **REGISTER 32-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER**

Note 1: Bits are valid for Reference Clock divider values of two or larger, the base clock cannot be further divided.

| Name                 | Bit 7                 | Bit 6                 | Bit 5                | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|----------------------|-----------------------|-----------------------|----------------------|---------------------|---------|--------|---------|--------|---------------------|

| TRISA                | —                     | —                     | TRISA5               | TRISA4              | (2)     | TRISA2 | TRISA1  | TRISA0 | 143                 |

| TRISB <sup>(1)</sup> | TRISB7                | TRISB6                | TRISB5               | TRISB4              | —       | —      | —       | —      | 149                 |

| TRISC                | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5               | TRISC4              | TRISC3  | TRISC2 | TRISC1  | TRISC0 | 155                 |

| CLKRCON              | CLKREN                | —                     | —                    | CLKRE               | )C<1:0> |        | CLKRDIV | <2:0>  | 227                 |

| CLCxSELy             | —                     | —                     |                      | LCxDyS<5:0>         |         |        |         |        |                     |

| MDCARH               | —                     | MDCHPOL               | MDCHSYNC — MDCH<3:0> |                     |         |        |         | 273    |                     |

| MDCARL               | —                     | MDCLPOL               | MDCLSYNC             | DCLSYNC – MDCL<3:0> |         |        |         |        |                     |

## TABLE 32-1: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK REFERENCE OUTPUT

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the CLKR module.

**Note 1:** PIC16(L)F18346 only.

2: Unimplemented, read as '1'.

|               |      |                                      | Standard Oper    | ating C             | onditions          | unless        | otherwise stated)                                                                                                               |

|---------------|------|--------------------------------------|------------------|---------------------|--------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

|               |      |                                      | Standard Open    |                     |                    | uniess        | otherwise statedy                                                                                                               |

| Param.<br>No. | Sym. | Characteristic                       | Min.             | Тур.†               | Max.               | Units         | Conditions                                                                                                                      |

|               | VIL  | Input Low Voltage                    |                  |                     |                    |               |                                                                                                                                 |

|               |      | I/O PORT:                            |                  |                     |                    |               |                                                                                                                                 |

| D300          |      | with TTL buffer                      |                  |                     | 0.8                | V             | $4.5V \le VDD \le 5.5V$                                                                                                         |

| D301          |      |                                      |                  |                     | 0.15 VDD           | V             | $1.8V \leq VDD \leq 4.5V$                                                                                                       |

| D302          |      | with Schmitt Trigger buffer          |                  | —                   | 0.2 Vdd            | V             | 2.0V ≤ VDD ≤ <del>5.5</del> V                                                                                                   |

| D303          |      | with I <sup>2</sup> C levels         | —                | —                   | 0.3 Vdd            | V             | $\frown$                                                                                                                        |

| D304          |      | with SMBus levels                    | —                | —                   | 0.8                | V             | $2.7V \leq VDD \leq 5.5V$                                                                                                       |

| D305          |      | MCLR                                 |                  | _                   | 0.2 VDD            | K             |                                                                                                                                 |

|               | VIH  | Input High Voltage                   |                  |                     |                    |               |                                                                                                                                 |

|               |      | I/O PORT:                            | _                |                     | $\frown$           |               | $\searrow$                                                                                                                      |

| D320          |      | with TTL buffer                      | 2.0              | —                   | _/ _               | ×             | $4.5V \neq VDD \leq 5.5V$                                                                                                       |

| D321          |      |                                      | 0.25 VDD + 0.8   | —                   | $  - \rangle$      | $\mathbb{V}/$ | $1.8V \le VDD \le 4.5V$                                                                                                         |

| D322          |      | with Schmitt Trigger buffer          | 0.8 Vdd          | <                   | <u> </u>           | $\sqrt{}$     | $2.0V \leq V\text{DD} \leq 5.5V$                                                                                                |

| D323          |      | with I <sup>2</sup> C levels         | 0.7 Vdd          |                     | /-/                | $\vee$        |                                                                                                                                 |

| D324          |      | with SMBus levels                    | 2.1 4            | $\langle - \rangle$ |                    | > v           | $2.7V \leq V\text{DD} \leq 5.5V$                                                                                                |

| D325          |      | MCLR                                 | 0.7 VDD          | $\left[ \right]$    |                    | V             |                                                                                                                                 |

|               | lı∟  | Input Leakage Current <sup>(2)</sup> |                  | $\overline{)}$      | $\bigtriangledown$ |               |                                                                                                                                 |

| D340          |      | I/O Ports                            | 7                | ±5                  | ± 125              | nA            | $\label{eq:VSS} \begin{split} &V\text{SS} \leq V\text{PIN} \leq V\text{DD}, \\ &\text{Pin at high-impedance, 85°C} \end{split}$ |

| D341          |      | <                                    | A/               | ₹5                  | ± 1000             | nA            | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 125°C                                                                     |

| D342          |      | MCLR <sup>(2)</sup>                  |                  | ± 50                | ± 200              | nA            | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 85°C                                                                      |

|               | IPUR | Weak Pull-up Current                 |                  | 1                   |                    | 1             |                                                                                                                                 |

| D350          |      | $\land$                              | 25               | 120                 | 200                | μA            | VDD = 3.0V, VPIN = VSS                                                                                                          |

|               | Vol  | Output Low Voltage <sup>(3)</sup>    | >                |                     | •                  | •             |                                                                                                                                 |

| D360          |      | I/O ports                            | _                | _                   | 0.6                | V             | IOL = 10.0 mA, VDD = 3.0V                                                                                                       |

|               | Vон  | Output High Vøltage <sup>(3)</sup>   |                  |                     |                    |               |                                                                                                                                 |

| D370          |      | I/Q ports                            | Vdd - 0.7        | _                   | _                  | V             | ІОН = 6.0 mA, VDD = 3.0V                                                                                                        |

| D380          | CIO  | All VO pins                          | _                | 5                   | 50                 | pF            |                                                                                                                                 |

|               |      |                                      | d but not tootod |                     |                    |               |                                                                                                                                 |

## TABLE 35-4: I/O PORTS<sup>(1)</sup>

These parameters are characterized but not tested. €

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as current sourced by the pin.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages. Excluding OSC2 in CLKOUT mode.

2;

3⁄.

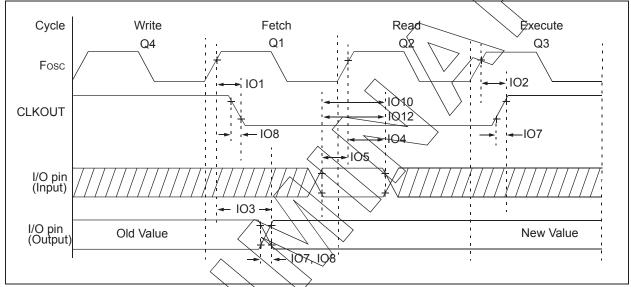

## TABLE 35-5: I/O AND CLOCK TIMING SPECIFICATIONS

| Standard                                           | Standard Operating Conditions (unless otherwise stated) |                                                      |          |       |            |       |                                               |  |  |  |

|----------------------------------------------------|---------------------------------------------------------|------------------------------------------------------|----------|-------|------------|-------|-----------------------------------------------|--|--|--|

| Param.<br>No.                                      | Sym.                                                    | Characteristic                                       | Min.     | Typ.† | Max.       | Units | Conditions                                    |  |  |  |

| High Voltage Entry Programming Mode Specifications |                                                         |                                                      |          |       |            |       |                                               |  |  |  |

| MEM01                                              | Vінн                                                    | Voltage on MCLR/VPP pin to<br>enter Programming mode | 8        | _     | 9          | V     | Note 2                                        |  |  |  |

| MEM02                                              | IPPGM                                                   | Current on MCLR/VPP pin during<br>Programming mode   | —        | _     | 600        | uA    | Note 2                                        |  |  |  |

| Program                                            | ming Mod                                                | de Specifications                                    |          |       |            |       |                                               |  |  |  |

| MEM10                                              | VBE                                                     | VDD for Bulk Erase                                   |          | 2.7   | _          | V     |                                               |  |  |  |

| MEM11                                              | IDDPGM                                                  | Supply Current during<br>Programming Operation       | _        | _     | 3          | mA    |                                               |  |  |  |

| Data EE                                            | PROM Me                                                 | mory Specifications                                  |          |       |            |       |                                               |  |  |  |

| MEM20                                              | ED                                                      | DataEE Byte Endurance                                | 100k     | _     | _          | E/W   | -40°C ≤ TA ≤ 85°C                             |  |  |  |

| MEM21                                              | TD_RET                                                  | Characteristic Retention                             | _        | 40    | - <        | Year  | Provided no other specifications are violated |  |  |  |

| MEM22                                              | ND_REF                                                  | Total Erase/Write Cycles before<br>Refresh           | _        | _     | 100k       | ÉW.   |                                               |  |  |  |

| MEM23                                              | VD_RW                                                   | VDD for Read or Erase/Write<br>Operation             | VDDMIN   |       | VDQMAX     | v     |                                               |  |  |  |

| MEM24                                              | TD_BEW                                                  | Byte Erase and Write Cycle Time                      | _        | 4.0   | 5.0        | ms    |                                               |  |  |  |

| Program                                            | I Flash Me                                              | emory Specifications                                 | $\frown$ |       |            |       |                                               |  |  |  |

| MEM30                                              | Eр                                                      | Flash Memory Cell Endurance                          | 10k      |       | $\searrow$ | E/W   | -40°C ≤ TA ≤ 85°C<br>(Note 1)                 |  |  |  |

| MEM31                                              | EPHEF                                                   | High-Endurance Flash Memory<br>Cell Endurance        | 100K     |       | $\sim_{-}$ | E/W   | TBD                                           |  |  |  |

| MEM32                                              | TP_RET                                                  | Characteristic Retention                             |          | 40    | —          | Year  | Provided no other specifications are violated |  |  |  |

| MEM33                                              | VP_RD                                                   | VDD for Read Operation                               | VODMIN   | —     | VDDMAX     | V     |                                               |  |  |  |

| MEM34                                              | VP_REW                                                  | VDD for Row Erase or Write<br>Operation              | VDDMIN   | _     | VDDMAX     | V     |                                               |  |  |  |

| MEM35                                              | TP_REW                                                  | Self-Timed Row Erase or<br>Self-Timed Write          | _        | 2.0   | 2.5        | ms    |                                               |  |  |  |

+ Data in "Typ." column is at 3.00, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Flash Memory Cell Endurance for the Flash memory is defined as: One Row Erase operation and one Self-Timed Write.

2: Required only if CONFIG3.LVP is disabled.

| TABLE 35-9: | PLL CLOCK TIMING SPECIFICATIONS |

|-------------|---------------------------------|

|-------------|---------------------------------|

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                         |       |       |      |       |            |  |  |  |

|---------------|---------------------------------------------------------|-----------------------------------------|-------|-------|------|-------|------------|--|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                          | Min.  | Тур.† | Max. | Units | Conditions |  |  |  |

| PLL01         | Fpllin                                                  | PLL Input Frequency Range               | 4     |       | 8    | MHz   |            |  |  |  |

| PLL02         | FPLLOUT                                                 | PLL Output Frequency Range              | 16    | —     | 32   | MHz   |            |  |  |  |

| PLL03         | TPLLST                                                  | PLL Lock Time from Start-up             | —     | 200   | —    | μs    | η          |  |  |  |

| PLL04         | Fplljit                                                 | PLL Output Frequency Stability (Jitter) | -0.25 | —     | 0.25 | %     |            |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16(L)F18326/18346

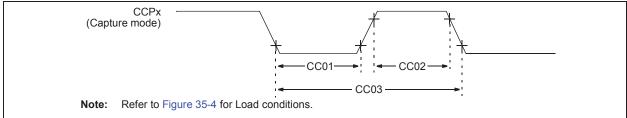

## FIGURE 35-13: CAPTURE/COMPARE/PWM TIMINGS (CCP)

## TABLE 35-18: CAPTURE/COMPARE/PWM CHARACTERISTICS (CCP)

| d Opera | ating Conditions (unles | ss otherwise sta                                                                              | ted)                                                                                                                                                                 |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                |

|---------|-------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sym.    | Character               | istic                                                                                         | Min.                                                                                                                                                                 | Тур.†                                                                                                                                                                                                                                                          | Max.                                                                                                                                                                                                                                                                                                                                                                      | Units                                                                                                                                                                                                                                                           | Conditions                                                                                                                                                                                                                                                     |

| TccL    | CCPx Input Low Time     | No Prescaler                                                                                  | 0.5Tcy +<br>20                                                                                                                                                       | —                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                           | ns                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                |

|         |                         | With Prescaler                                                                                | 20                                                                                                                                                                   | —                                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                         | ns                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                |

| ТссН    | CCPx Input High<br>Time | No Prescaler                                                                                  | 0.5Tcy +<br>20                                                                                                                                                       | —                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                           | ns                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                |

|         |                         | With Prescaler                                                                                | 20                                                                                                                                                                   | —                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                           | ns                                                                                                                                                                                                                                                              | $\sim$                                                                                                                                                                                                                                                         |