Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 014110                   |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18346-i-gz |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|------------|----------------------------------------------------------|

|------------|----------------------------------------------------------|

| Address | Name   | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7   | Bit 6   | Bit 5       | Bit 4           | Bit 3             | Bit 2   | Bit 1   | Bit 0                                 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------------------|---------|---------|-------------|-----------------|-------------------|---------|---------|---------------------------------------|-----------------------|---------------------------------|

| Bank 7  |        |                                  |         |         |             |                 |                   |         |         |                                       |                       |                                 |

|         |        |                                  |         |         | CPU CORE RE | EGISTERS; see 1 | Table 4-2 for spe | cifics  |         |                                       |                       |                                 |

| 38Ch    | INLVLA |                                  | —       | —       | INLVLA5     | INLVLA4         | INLVLA3           | INLVLA2 | INLVLA1 | INLVLA0                               | 11 1111               | 11 111                          |

| 38Dh    | INLVLB | X —                              |         |         |             | Unimple         | mented            |         |         |                                       | -                     | —                               |

|         |        | — X                              | INLVLB7 | INLVLB6 | INLVLB5     | INLVLB4         | —                 | —       | _       | —                                     | 1111                  | 1111                            |

| 38Eh    | INLVLC | X —                              | —       | —       | INLVLC5     | INLVLC4         | INLVLC3           | INLVLC2 | INLVLC1 | INLVLC0                               | 11 1111               | 11 111                          |

|         |        | — X                              | INLVLC7 | INLVLC6 | INLVLC5     | INLVLC4         | INLVLC3           | INLVLC2 | INLVLC1 | INLVLC0                               | 1111 1111             | 1111 111                        |

| 38Fh    | —      | —                                |         |         |             | Unimple         | mented            |         |         |                                       | -                     | —                               |

| 390h    | —      | -                                |         |         |             | Unimple         | mented            |         |         |                                       | -                     | _                               |

| 391h    | IOCAP  |                                  | —       | _       | IOCAP5      | IOCAP4          | IOCAP3            | IOCAP2  | IOCAP1  | IOCAP0                                | 00 0000               | 00 000                          |

| 392h    | IOCAN  |                                  | —       | _       | IOCAN5      | IOCAN4          | IOCAN3            | IOCAN2  | IOCAN1  | IOCAN0                                | 00 0000               | 00 000                          |

| 393h    | IOCAF  |                                  | _       | —       | IOCAF5      | IOCAF4          | IOCAF3            | IOCAF2  | IOCAF1  | IOCAF0                                | 00 0000               | 00 000                          |

| 394h    | IOCBP  | X —                              |         | •       |             | Unimple         | mented            |         |         | •                                     | _                     | _                               |

|         |        | — X                              | IOCBP7  | IOCBP6  | IOCBP5      | IOCBP4          | —                 | —       | —       | _                                     | 0000                  | 0000                            |

| 395h    | IOCBN  | X —                              |         | •       |             | Unimple         | mented            |         |         | •                                     | _                     | _                               |

|         |        | — X                              | IOCBN7  | IOCBN6  | IOCBN5      | IOCBN4          | —                 | —       | —       | _                                     | 0000                  | 0000                            |

| 396h    | IOCBF  | X —                              |         | -       |             | Unimple         | mented            |         |         | · · · · · · · · · · · · · · · · · · · | -                     | —                               |

|         |        | — X                              | IOCBF7  | IOCBF6  | IOCBF5      | IOCBF4          | —                 | _       |         |                                       | 0000                  | 0000                            |

| 397h    | IOCCP  | × —                              | —       | _       | IOCCP5      | IOCCP4          | IOCCP3            | IOCCP2  | IOCCP1  | IOCCP0                                | 00 0000               | 00 000                          |

|         |        | — X                              | IOCCP7  | IOCCP6  | IOCCP5      | IOCCP4          | IOCCP3            | IOCCP2  | IOCCP1  | IOCCP0                                | 0000 0000             | 0000 000                        |

| 398h    | IOCCN  | X —                              | —       | —       | IOCCN5      | IOCCN4          | IOCCN3            | IOCCN2  | IOCCN1  | IOCCN0                                | 00 0000               | 00 000                          |

IOCCN3

IOCCF3

IOCCF3

IOCCN2

IOCCF2

IOCCF2

IOCCN1

IOCCF1

IOCCF1

IOCCN0

IOCCF0

IOCCF0

0000 0000

--00 0000

0000 0000 0000 0000

0000 0000

--00 0000

399h

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

IOCCN4

IOCCF4

IOCCF4

IOCCN5

IOCCF5

IOCCF5

Note 1: Only on PIC16F18326/18346.

IOCCF

2: Register accessible from both User and ICD Debugger.

Х

Х

X —

IOCCN7

\_

IOCCF7

IOCCN6

\_

IOCCF6

#### 7.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 7.3 "Clock Switching" for more information.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- 1. The HFINTOSC (High-Frequency Internal Oscillator) is factory-calibrated and operates up to 32 MHz.

- The LFINTOSC (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

#### 7.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (1 MHz) or '000' (32 MHz) to set the oscillator upon device Power-up or Reset

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time

The HFINTOSC frequency can be selected by setting the HFFRQ<3:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the output of the selected clock source by a range between 1:1 and 1:512.

#### 7.2.2.2 2x PLL

The oscillator module contains a PLL that can be used with the HFINTOSC clock source to provide a system clock source. The input frequency to the PLL is limited to 8, 12, or 16 MHz, which will yield a system clock source of 16, 24, or 32 MHz, respectively.

The PLL may be enabled for use by one of two methods:

- Program the RSTOSC bits in the Configuration Word 1 to '000' to enable the HFINTOSC (32 MHz). This setting configures the HFFRQ<3:0> bits to '110' (16 MHz) and activates the 2x PLL.

- Write '000' to the NOSC<2:0> bits in the OSCCON1 register to enable the 2x PLL, and write the correct value into the HFFRQ<3:0> bits of the OSCFRQ register to select the desired system clock frequency. See Register 6-6 for more information.

| FIGURE 9-2                                                                                                                                                                                                                                                                                                                                               | 2: WAP           | KE-UP FROM       | <b>I SLEEP</b> | THRC    | <b>UGH INTER</b>                      | RUPT                            |                 |                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------|---------|---------------------------------------|---------------------------------|-----------------|------------------|

| CLKIN <sup>(1</sup><br>CLKOUT <sup>(2</sup>                                                                                                                                                                                                                                                                                                              |                  | Q1 Q2 Q3  Q4     |                | Tost(3) |                                       | Q1 Q2 Q3 Q4<br>/~_/~_/~_/<br>// | Q1 Q2 Q3 Q4<br> | Q1 Q2 Q3 Q4<br>~ |

| Interrupt flag                                                                                                                                                                                                                                                                                                                                           |                  |                  | /              | ı<br>I  | Interrupt Laten                       | CV <sup>(4)</sup>               |                 |                  |

| GIE bit<br>(INTCON reg.                                                                                                                                                                                                                                                                                                                                  | ).               | I<br>I<br>I<br>I | Processor in   |         | · · · · · · · · · · · · · · · · · · · | ·                               | ·               |                  |

| nstruction Flow<br>PC                                                                                                                                                                                                                                                                                                                                    | /<br>XPC         | X PC + 1         | ХРС            | + 2     | X PC + 2                              | PC + 2                          | X 0004h         | X 0005h          |

| Instruction {<br>Fetched                                                                                                                                                                                                                                                                                                                                 | Inst(PC) = Sleep | Inst(PC + 1)     | I<br>I         |         | Inst(PC + 2)                          | i<br>i                          | Inst(0004h)     | Inst(0005h)      |

| Instruction {<br>Executed {                                                                                                                                                                                                                                                                                                                              | Inst(PC - 1)     | Sleep            | 1<br>1<br>1    |         | Inst(PC + 1)                          | Forced NOP                      | Forced NOP      | Inst(0004h)      |

| <ol> <li>External clock. High, Medium, Low mode assumed.</li> <li>CLKOUT is shown here for timing reference.</li> <li>Tost = 1024 Tosc. This delay does not apply to EC and INTOSC Oscillator modes.</li> <li>GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.</li> </ol> |                  |                  |                |         |                                       |                                 |                 |                  |

#### 11.4.7 NVMREG EEPROM, USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS

Instead of accessing Program Flash Memory, the EEPROM, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when NVMREGS = 1 in the NVMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-3.

When read access is initiated on an address outside the parameters listed in Table 11-3, the NVMDATH: NVMDATL register pair is cleared, reading back '0's.

### TABLE 11-3:EEPROM, USER ID, DEV/REV ID AND CONFIGURATION WORD ACCESS<br/>(NVMREGS = 1)

| Address     | Function                | Read Access | Write Access |

|-------------|-------------------------|-------------|--------------|

| 8000h-8003h | User IDs                | Yes         | Yes          |

| 8005h-8006h | Device ID/Revision ID   | Yes         | No           |

| 8007h-800Ah | Configuration Words 1-4 | Yes         | No           |

| F000h-F0FFh | EEPROM                  | Yes         | Yes          |

| R/W-0/0                         | R/W-0/0 | R/W-0/0              | R/W-0/0          | U-0            | U-0                                | U-0              | U-0         |  |

|---------------------------------|---------|----------------------|------------------|----------------|------------------------------------|------------------|-------------|--|

| WPUB7                           | WPUB6   | WPUB5                | WPUB4            |                | —                                  | —                | —           |  |

| bit 7                           |         | •                    |                  |                | •                                  |                  | bit 0       |  |

|                                 |         |                      |                  |                |                                    |                  |             |  |

| Legend:                         |         |                      |                  |                |                                    |                  |             |  |

| R = Readable                    | bit     | W = Writable         | N = Writable bit |                | U = Unimplemented bit, read as '0' |                  |             |  |

| u = Bit is unchanged x = Bit is |         | x = Bit is unkn      | iown             | -n/n = Value a | at POR and BO                      | R/Value at all o | ther Resets |  |

| '1' = Bit is set                |         | '0' = Bit is cleared |                  |                |                                    |                  |             |  |

|                                 |         |                      |                  |                |                                    |                  |             |  |

#### REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER

| bit 7-4 | WPUB<7:4>: Weak Pull-up Register bits |

|---------|---------------------------------------|

|         | 1 = Weak Pull-up enabled              |

|         | 0 = Weak Pull-up disabled             |

| bit 3-0 | Unimplemented: Read as '0'            |

#### REGISTER 12-14: ODCONB: PORTB OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| ODCB7   | ODCB6   | ODCB5   | ODCB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 **ODCB<7:4>:** PORTB Open-Drain Configuration bits For RB<7:4> pins, respectively: 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

bit 3-0 Unimplemented: Read as '0'

| U-0                                             | R/W-0/0                               | R/W-0/0           | U-0  | U-0            | R/W-0/0          | R/W-0/0          | U-0         |

|-------------------------------------------------|---------------------------------------|-------------------|------|----------------|------------------|------------------|-------------|

| _                                               | DACMD                                 | ADCMD             |      | _              | CMP2MD           | CMP1MD           |             |

| bit 7                                           | · · · · · · · · · · · · · · · · · · · | ·                 |      | •              |                  | •                | bit 0       |

| Legend:                                         |                                       |                   |      |                |                  |                  |             |

| R = Readal                                      | ble bit                               | W = Writable I    | oit  | U = Unimplem   | nented bit, read | l as '0'         |             |

| u = Bit is ur                                   | nchanged                              | x = Bit is unkn   | own  | -n/n = Value a | t POR and BO     | R/Value at all o | ther Resets |

| '1' = Bit is s                                  | et                                    | '0' = Bit is clea | ared | q = Value dep  | ends on condit   | ion              |             |

|                                                 |                                       |                   |      |                |                  |                  |             |

| bit 7                                           | Unimpleme                             | nted: Read as 'o  | )'   |                |                  |                  |             |

| bit 6                                           | DACMD: Dis                            | able DAC bit      |      |                |                  |                  |             |

|                                                 |                                       | odule disabled    |      |                |                  |                  |             |

|                                                 |                                       | odule enabled     |      |                |                  |                  |             |

| bit 5                                           |                                       | able ADC bit      |      |                |                  |                  |             |

|                                                 |                                       | odule enabled     |      |                |                  |                  |             |

| bit 4-3                                         | Unimpleme                             | nted: Read as '0  | )'   |                |                  |                  |             |

| bit 2                                           | -                                     | isable Compara    |      |                |                  |                  |             |

|                                                 | 1 = C2 module disabled                |                   |      |                |                  |                  |             |

|                                                 | 0 = C2 mod                            | ule enabled       |      |                |                  |                  |             |

| bit 1                                           |                                       |                   |      |                |                  |                  |             |

| 1 = C1 module disabled<br>0 = C1 module enabled |                                       |                   |      |                |                  |                  |             |

| bit 0                                           |                                       | nted: Read as '0  | ,    |                |                  |                  |             |

|                                                 | ommpleme                              | nieu. Redu ds (   | 1    |                |                  |                  |             |

#### REGISTER 14-3: PMD2: PMD CONTROL REGISTER 2

| REGISTER ZU | J-4. CVVGX |     | DATAINFUI | SELECTION | N REGISTER |         |         |

|-------------|------------|-----|-----------|-----------|------------|---------|---------|

| U-0         | U-0        | U-0 | U-0       | R/W-0/0   | R/W-0/0    | R/W-0/0 | R/W-0/0 |

| —           | —          | —   | —         |           | DAT        | <3:0>   |         |

| bit 7       |            |     |           |           |            |         | bit 0   |

|             |            |     |           |           |            |         |         |

| Legend:     |            |     |           |           |            |         |         |

#### REGISTER 20-4: CWGxDAT: CWGx DATA INPUT SELECTION REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 DAT<3:0>: CWG Data Input Selection bits

| DAT  | Data Source |

|------|-------------|

| 0000 | CWGxPPS     |

| 0001 | C1OUT       |

| 0010 | C2OUT       |

| 0011 | CCP1        |

| 0100 | CCP2        |

| 0101 | CCP3        |

| 0110 | CCP4        |

| 0111 | PWM5        |

| 1000 | PWM6        |

| 1001 | NCO1        |

| 1010 | CLC1        |

| 1011 | CLC2        |

| 1100 | CLC3        |

| 1101 | CLC4        |

| 1110 | Reserved    |

| 1111 | Reserved    |

| Name                  | Bit 7                 | Bit 6                 | Bit 5   | Bit 4    | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|---------|----------|--------|----------|----------|--------|---------------------|

| TRISA                 | —                     | —                     | TRISA5  | TRISA4   | (2)    | TRISA2   | TRISA1   | TRISA0 | 143                 |

| ANSELA                | —                     | _                     | ANSA5   | ANSA4    |        | ANSA2    | ANSA1    | ANSA0  | 144                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5  | TRISB4   | _      | _        | _        | _      | 149                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5   | ANSB4    | _      | _        | _        | _      | 150                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4   | TRISC3 | TRISC2   | TRISC1   | TRISC0 | 155                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5   | ANSC4    | ANSC3  | ANSC2    | ANSC1    | ANSC0  | 157                 |

| PIR4                  | CWG2IF                | CWG1IF                | TMR5GIF | TMR5IF   | CCP4IF | CCP3IF   | CCP2IF   | CCP1IF | 110                 |

| PIE4                  | CWG2IE                | CWG1IE                | TMR5GIE | TMR5IE   | CCP4IE | CCP3IE   | CCP2IE   | CCP1IE | 105                 |

| CWG1CON0              | EN                    | LD                    | —       | _        |        | Ν        | 10DE<2:0 | >      | 213                 |

| CWG1CON1              | —                     | _                     | IN      | _        | POLD   | POLC     | POLB     | POLA   | 214                 |

| CWG1CLKCON            | —                     | _                     | —       | _        |        | _        | _        | CS     | 214                 |

| CWG1DAT               | —                     | _                     | —       | _        |        | DAT      | <3:0>    |        | 215                 |

| CWG1STR               | OVRD                  | OVRC                  | OVRB    | OVRA     | STRD   | STRC     | STRB     | STRA   | 216                 |

| CWG1AS0               | SHUTDOWN              | REN                   | LSBD<   | <1:0>    | LSAC   | <1:0>    | —        | —      | 217                 |

| CWG1AS1               | —                     | —                     | _       | AS4E     | AS3E   | AS2E     | AS1E     | AS0E   | 218                 |

| CWG1DBR               | —                     | —                     |         |          | DBR•   | <5:0>    |          |        | 218                 |

| CWG1DBF               | —                     | —                     |         |          | DBF<   | <5:0>    |          |        | 219                 |

| CWG1PPS               | —                     | _                     | —       |          | CV     | VG1PPS<4 | k:0>     |        | 162                 |

| CWG2CON0              | EN                    | LD                    | —       | _        | —      | Ν        | 10DE<2:0 | >      | 213                 |

| CWG2CON1              | —                     | —                     | IN      | —        | POLD   | POLC     | POLB     | POLA   | 214                 |

| CWG2CLKCON            | —                     | —                     | —       | —        | —      | —        | —        | CS     | 214                 |

| CWG2DAT               | —                     | —                     | —       | _        |        | DAT      | <3:0>    |        | 215                 |

| CWG2STR               | OVRD                  | OVRC                  | OVRB    | OVRA     | STRD   | STRC     | STRB     | STRA   | 216                 |

| CWG2AS0               | SHUTDOWN              | REN                   | LSBD<   | <1:0>    | LSAC   | <1:0>    | _        | _      | 217                 |

| CWG2AS1               | —                     | —                     | —       | AS4E     | AS3E   | AS2E     | AS1E     | AS0E   | 218                 |

| CWG2DBR               | —                     | —                     |         | DBR<5:0> |        |          |          |        | 218                 |

| CWG2DBF               |                       |                       |         |          | DBF<   | <5:0>    |          |        | 219                 |

| CWG2PPS               | —                     | _                     | —       |          | CV     | VG2PPS<4 | -0:      |        | 162                 |

#### TABLE 20-2: SUMMARY OF REGISTERS ASSOCIATED WITH CWGx

**Note 1:** PIC16(L)F18346 only.

2: Unimplemented, read as '0'.

| Name                  | Bit 7                 | Bit 6                 | Bit 5     | Bit 4  | Bit 3                       | Bit 2    | Bit 1   | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|-----------|--------|-----------------------------|----------|---------|--------|---------------------|

| INTCON                | GIE                   | PEIE                  |           | —      | —                           | —        |         | INTEDG | 100                 |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE      | TXIE   | SSP1IE                      | BCL1IE   | TMR2IE  | TMR1IE | 102                 |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF      | TXIF   | SSP1IF                      | BCL1IF   | TMR2IF  | TMR1IF | 107                 |

| TRISA                 | —                     | —                     | TRISA5    | TRISA4 | (2)                         | TRISA2   | TRISA1  | TRISA0 | 143                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5    | TRISB4 | —                           | —        | _       | _      | 149                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5    | TRISC4 | TRISC3                      | TRISC2   | TRISC1  | TRISC0 | 155                 |

| ANSELA                | —                     | —                     | ANSA5     | ANSA4  |                             | ANSA2    | ANSA1   | ANSA0  | 144                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5     | ANSB4  |                             | _        | _       |        | 150                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5     | ANSC4  | ANSC3                       | ANSC2    | ANSC1   | ANSC0  | 157                 |

| ADCON0                |                       |                       | CHS<      | 5:0>   |                             |          | GO/DONE | ADON   | 244                 |

| ADCON1                | ADFM                  | A                     | ADCS<2:0> | •      |                             | ADNREF   | ADPRE   | F<1:0> | 245                 |

| ADACT                 | —                     | —                     |           |        |                             | ADACT<4: | )>      |        | 246                 |

| ADRESH                | ADRESH<7:0>           |                       |           |        |                             |          | 247     |        |                     |

| ADRESL                | ADRESL<7:0>           |                       |           |        |                             |          |         | 247    |                     |

| FVRCON                | FVREN                 | FVRRDY                | TSEN      | TSRNG  | SRNG CDAFVR<1:0> ADFVR<1:0> |          |         |        | 180                 |

| DAC1CON1              | —                     | —                     |           |        |                             | DAC1R<4: | 0>      |        | 264                 |

| OSCSTAT1              | EXTOR                 | HFOR                  |           | LFOR   | SOR                         | ADOR     | _       | PLLR   | 91                  |

#### TABLE 22-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** -= unimplemented read as '0'. Shaded cells are not used for the ADC module.

**Note 1:** PIC16(L)F18346 only.

**2:** Unimplemented, read as '1'.

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                        | R/W-0/0                                               | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------|----------------|------------------|------------------|--------------|

|                  | T0CS<2:0>                                                                                                                                                                                                      |                                                       | TOASYNC        |                | TOCKF            | PS<3:0>          |              |

| bit 7            |                                                                                                                                                                                                                |                                                       |                |                |                  |                  | bit          |

|                  |                                                                                                                                                                                                                |                                                       |                |                |                  |                  |              |

| Legend:          |                                                                                                                                                                                                                |                                                       |                |                |                  |                  |              |

| R = Readable     |                                                                                                                                                                                                                | W = Writable                                          |                | •              | mented bit, read |                  |              |

| u = Bit is unch  | anged                                                                                                                                                                                                          | x = Bit is unkr                                       |                | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |                                                                                                                                                                                                                | '0' = Bit is cle                                      | ared           |                |                  |                  |              |

| bit 7-5          | 111 = CLC1<br>110 = SOSC<br>101 = Reserv<br>100 = LFINT<br>011 = HFINT<br>010 = Fosc/4                                                                                                                         | ved<br>OSC<br><sup>-</sup> OSC<br>4<br>PPS (Inverted) | ource Select b | iits           |                  |                  |              |

| bit 4            | 1 = The inpu                                                                                                                                                                                                   | MR0 Input Asy<br>ut to the TMR0 o<br>ut to the TMR0 o | counter is not | synchronized f |                  | S                |              |

| bit 3-0          | <b>TOCKPS&lt;3:0</b><br>1111 = 1:327<br>1110 = 1:163<br>1101 = 1:819<br>1100 = 1:409<br>1011 = 1:202<br>1010 = 1:102<br>1001 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0100 = 1:4<br>0011 = 1:2<br>0000 = 1:1 | 384<br>92<br>96<br>48<br>24<br>2<br>5                 | ate Select bit |                |                  |                  |              |

#### REGISTER 26-4: T0CON1: TIMER0 CONTROL REGISTER 1

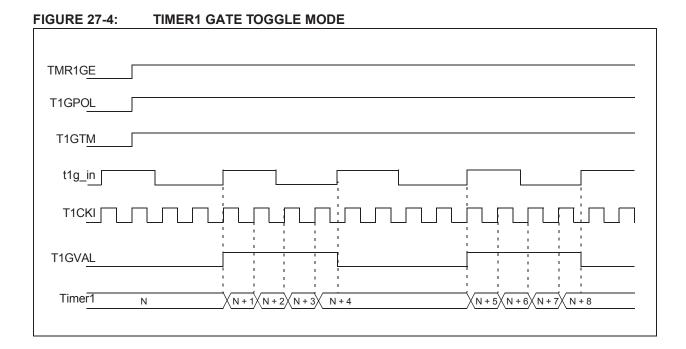

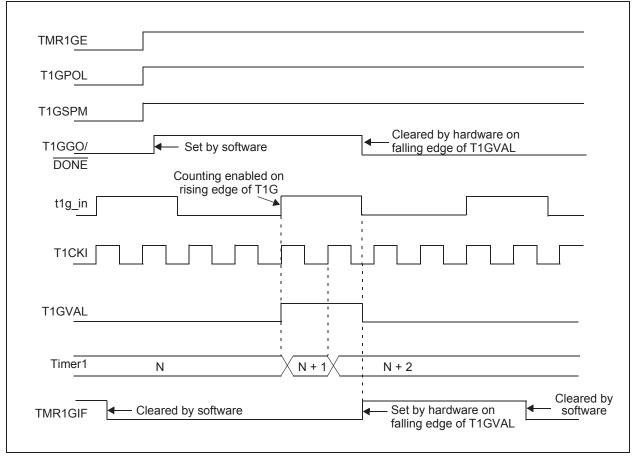

#### FIGURE 27-5: TIMER1 GATE SINGLE-PULSE MODE

#### 28.5 Register Definitions: Timer2/4/6 Control

| U-0           | R/W-0/0                   | R/W-0/0                | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |

|---------------|---------------------------|------------------------|----------------|----------------|------------------|----------------|--------------|--|--|--|

| _             |                           |                        | PS<3:0>        |                | TMRxON           |                | S<1:0>       |  |  |  |

| oit 7         |                           |                        |                |                |                  |                | bit          |  |  |  |

|               |                           |                        |                |                |                  |                |              |  |  |  |

| Legend:       |                           |                        |                |                |                  |                |              |  |  |  |

| R = Readab    | ole bit                   | W = Writable           | bit            | U = Unimple    | mented bit, read | l as '0'       |              |  |  |  |

| u = Bit is un | changed                   | x = Bit is unkr        | nown           | -n/n = Value   | at POR and BO    | R/Value at all | other Resets |  |  |  |

| 1' = Bit is s | et                        | '0' = Bit is clea      | ared           |                |                  |                |              |  |  |  |

| oit 7         | Unimpleme                 | ented: Read as '       | 0'             |                |                  |                |              |  |  |  |

| oit 6-3       | TxOUTPS<                  | 3:0>: Timerx Ou        | tput Postscale | er Select bits |                  |                |              |  |  |  |

|               | 1111 <b>= 1:16</b>        | 6 Postscaler           |                |                |                  |                |              |  |  |  |

|               | 1110 <b>= 1:1</b> 5       | 1110 = 1:15 Postscaler |                |                |                  |                |              |  |  |  |

|               |                           | 1101 = 1:14 Postscaler |                |                |                  |                |              |  |  |  |

|               | 1100 = 1:13 Postscaler    |                        |                |                |                  |                |              |  |  |  |

|               |                           | 1 = 1:12 Postscaler    |                |                |                  |                |              |  |  |  |

|               |                           | l Postscaler           |                |                |                  |                |              |  |  |  |

|               | 1001 = 1:10<br>1000 = 1:9 | ) Postscaler           |                |                |                  |                |              |  |  |  |

|               | 0111 = 1:8                |                        |                |                |                  |                |              |  |  |  |

|               | 0110 = 1:7                |                        |                |                |                  |                |              |  |  |  |

|               | 0101 = 1:6                |                        |                |                |                  |                |              |  |  |  |

|               | 0100 = 1:5                | Postscaler             |                |                |                  |                |              |  |  |  |

|               | 0011 = 1:4 Postscaler     |                        |                |                |                  |                |              |  |  |  |

|               | 0010 <b>= 1:3</b>         | 0010 = 1:3 Postscaler  |                |                |                  |                |              |  |  |  |

|               | 0001 = 1:2 Postscaler     |                        |                |                |                  |                |              |  |  |  |

|               | 0000 = 1:1                | Postscaler             |                |                |                  |                |              |  |  |  |

| oit 2         | TMRxON: 7                 | Timer2 On bit          |                |                |                  |                |              |  |  |  |

|               | 1 = Timerx<br>0 = Timerx  |                        |                |                |                  |                |              |  |  |  |

| oit 1-0       | TxCKPS<1                  | :0>: Timerx Cloc       | k Prescale Se  | elect bits     |                  |                |              |  |  |  |

|               | 11 = Presca               | aler is 64             |                |                |                  |                |              |  |  |  |

|               | 10 = Presca               | aler is 16             |                |                |                  |                |              |  |  |  |

|               | 01 = Presca               |                        |                |                |                  |                |              |  |  |  |

|               | 00 <b>= Presca</b>        | aler is 1              |                |                |                  |                |              |  |  |  |

### **REGISTER 28-1:** TxCON<sup>(1)</sup>: TIMERX CONTROL REGISTER

**Note 1:** 'x' refers to either '2,' 4' or '6' for the respective Timer2/4/6 registers.

### 29.5 Register Definitions: CCP Control

| R/W-0/0      | 0-U                                                                                   | R-x/x                                                                        | R/W-0/0                             | R/W-0/0                         | R/W-0/0         | R/W-0/0        | R/W-0/0     |

|--------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------|---------------------------------|-----------------|----------------|-------------|

| CCPxEI       | м —                                                                                   | CCPxOUT                                                                      | CCPxFMT                             |                                 | CCPxMC          | DDE<3:0>       |             |

| bit 7        |                                                                                       |                                                                              |                                     |                                 |                 |                | bit         |

|              |                                                                                       |                                                                              |                                     |                                 |                 |                |             |

| Legend:      |                                                                                       |                                                                              |                                     |                                 |                 |                |             |

| R = Reada    |                                                                                       | W = Writable                                                                 |                                     | •                               | mented bit, rea |                |             |

| u = Bit is u | inchanged                                                                             | x = Bit is unkr                                                              | nown                                | -n/n = Value a                  | at POR and BC   | R/Value at all | other Reset |

| '1' = Bit is | set                                                                                   | '0' = Bit is cle                                                             | ared                                |                                 |                 |                |             |

| bit 7        | <b>CCPxEN:</b> (<br>1 = CCP is<br>0 = CCP is                                          |                                                                              | ble bit                             |                                 |                 |                |             |

| bit 6        | Unimplem                                                                              | ented: Read as '                                                             | 0'                                  |                                 |                 |                |             |

| bit 5        | CCPxOUT:                                                                              | CCPx Output Da                                                               | ata (read-only)                     | bit                             |                 |                |             |

| bit 4        | <u>CCPxMOD</u><br>Unuse<br><u>CCPxMOD</u><br>Unuse<br><u>CCPxMOD</u><br>1 = Left-alig | E = Compare mo                                                               | le                                  | t bit                           |                 |                |             |

| bit 3-0      | CCPxMOD<br>1111 = PW<br>1110 = Re:<br>1101 = Re:<br>1100 = Re:                        | served<br>served                                                             | lode Select bit                     | s <sup>(1)</sup>                |                 |                |             |

|              | 1010 <b>= Co</b><br>1001 <b>= Co</b>                                                  | mpare mode: out<br>mpare mode: out<br>mpare mode: clea<br>mpare mode: set    | put will pulse (<br>ar output on co | )-1-0<br>ompare match           | MR1/3/5         |                |             |

|              | 0110 <b>= Ca</b><br>0101 <b>= Ca</b>                                                  | pture mode: ever<br>pture mode: ever<br>pture mode: ever<br>pture mode: ever | y 4th rising ed<br>y rising edge o  | ge of CCPx inp<br>of CCPx input |                 |                |             |

|              | 0010 = Co<br>0001 = Co                                                                | pture mode: ever<br>mpare mode: tog<br>mpare mode: tog<br>pture/Compare/P    | gle output on i<br>gle output on i  | natch<br>natch; clear TN        |                 |                |             |

| Note 1:      | All modes will se trigger source.                                                     | et the CCPxIF bit                                                            | and will trigge                     | er an ADC conv                  | ersion if CCPx  | is selected as | the ADC     |

#### REGISTER 29-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-0/0             | R/W-0/0                      | R/W-0/0                                        | R/W-0/0            | R/W-0/0        | R-0/0              | R-0/0            | R-x/x       |

|---------------------|------------------------------|------------------------------------------------|--------------------|----------------|--------------------|------------------|-------------|

| SPEN <sup>(1)</sup> | RX9                          | SREN                                           | CREN               | ADDEN          | FERR               | OERR             | RX9D        |

| bit 7               | ·                            |                                                | ·                  |                |                    | ·                | bit (       |

| Legend:             |                              |                                                |                    |                |                    |                  |             |

| R = Readable        | e bit                        | W = Writable                                   | bit                | U = Unimple    | mented bit, read   | d as '0'         |             |

| u = Bit is uncl     | nanged                       | x = Bit is unk                                 | nown               | •              | at POR and BC      |                  | ther Resets |

| '1' = Bit is set    |                              | '0' = Bit is cle                               | eared              |                |                    |                  |             |

| bit 7               | SPEN: Seria                  | Il Port Enable b                               | it(1)              |                |                    |                  |             |

|                     | 1 = Serial p<br>0 = Serial p | ort enabled<br>ort disabled (he                | eld in Reset)      |                |                    |                  |             |

| bit 6               | <b>RX9:</b> 9-bit R          | eceive Enable                                  | bit                |                |                    |                  |             |

|                     |                              | 9-bit reception<br>8-bit reception             |                    |                |                    |                  |             |

| bit 5               | SREN: Sing                   | le Receive Ena                                 | ble bit            |                |                    |                  |             |

|                     | Asynchrono                   | <u>us mode</u> :                               |                    |                |                    |                  |             |

|                     |                              | iis mode – valu<br><u>s mode – Mast</u> e      | •                  |                |                    |                  |             |

|                     |                              | single receive                                 |                    |                |                    |                  |             |

|                     |                              | s single receive                               |                    |                |                    |                  |             |

|                     |                              | eared after rece<br>s mode – Slave             |                    | ele.           |                    |                  |             |

|                     | -                            | iis mode – valu                                |                    |                |                    |                  |             |

| bit 4               |                              | inuous Receive                                 | •                  |                |                    |                  |             |

|                     | Asynchrono                   | <u>us mode</u> :                               |                    |                |                    |                  |             |

|                     |                              | s continuous ree<br>s continuous re<br>s mode: |                    | ole bit CREN i | s cleared          |                  |             |

|                     | 1 = Enables                  |                                                |                    | ole bit CREN i | s cleared (CREI    | N overrides SR   | EN)         |

| bit 3               | ADDEN: Ad                    | dress Detect E                                 | nable bit          |                |                    |                  |             |

|                     | Asynchrono                   | us mode 9-bit (                                | RX9 = 1 <u>)</u> : |                |                    |                  |             |

|                     | the rece                     | ive buffer is se                               | t                  | -              | bad of the receiv  |                  |             |

|                     | Asynchrono                   | us mode 8-bit (                                | RX9 = 0):          | are received a | and ninth bit can  | i be used as pa  | rity dit    |

|                     |                              | is mode – valu                                 | e ignored          |                |                    |                  |             |

| bit 2               | FERR: Fram                   | -                                              | undeted by rea     |                | Creatister and re  | anivo novt volic | huto)       |

|                     | 1 = Framing<br>0 = No fram   |                                                |                    | IUNING RUTREC  | G register and re  |                  | i byte)     |

| bit 1               | OERR: Over                   | rrun Error bit                                 |                    |                |                    |                  |             |

|                     | 1 = Overrur<br>0 = No over   | error (can be or<br>run error                  | cleared by clea    | ring bit CREN  | 1)                 |                  |             |

| bit 0               | RX9D: Ninth                  | bit of Receive                                 | d Data             |                |                    |                  |             |

|                     | This can be                  | address/data b                                 | it or a parity bit | and must be    | calculated by us   | ser firmware.    |             |

|                     | e EUSART1 m<br>sociated TRIS |                                                |                    |                | i-state to drive a | as needed. Con   | figure the  |

#### . . . . . . .

### FIGURE 34-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                |

|---------------------------------------------------------------------------------------|

| OPCODE d f (FILE #)                                                                   |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |

| Bit-oriented file register operations                                                 |

| OPCODE b (BIT #) f (FILE #)                                                           |

| b = 3-bit bit address<br>f = 7-bit file register address                              |

| Literal and control operations                                                        |

| General                                                                               |

| 13 8 7 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 8-bit immediate value                                                             |

| CALL and GOTO instructions only                                                       |

|                                                                                       |

| OPCODE k (literal)                                                                    |

| k = 11-bit immediate value                                                            |

| 13 7 6 0                                                                              |

| OPCODE k (literal)                                                                    |

| k = 7-bit immediate value                                                             |

| MOVLB instruction only<br>13 54 0                                                     |

| OPCODE k (literal)                                                                    |

| k = 5-bit immediate value                                                             |

| BRA instruction only<br>13 9 8 0                                                      |

| OPCODE k (literal)                                                                    |

| k = 9-bit immediate value                                                             |

| FSR Offset instructions<br>13 7 6 5 0                                                 |

| OPCODE n k (literal)                                                                  |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |

| FSR Increment instructions133210                                                      |

| OPCODE n m (mode)                                                                     |

| n = appropriate FSR<br>m = 2-bit mode value                                           |

| OPCODE only<br>13 0                                                                   |

| OPCODE                                                                                |

|                                                                                       |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                                                 | BTFSS      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Syntax:          | [ <i>label</i> ]BRA label                                                                                                                                                                                                                       | Syntax:    |

|                  | [ <i>label</i> ]BRA \$+k                                                                                                                                                                                                                        | Operands   |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255                                                                                                                                                                                                           |            |

|                  | $-256 \le k \le 255$                                                                                                                                                                                                                            | Operation  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   | Status Aff |

| Status Affected: | None                                                                                                                                                                                                                                            | Descriptio |

| Description:     | Add the signed 9-bit literal 'k' to the<br>PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + k. This instruction is a<br>2-cycle instruction. This branch has a<br>limited range. |            |

| Syntax:          | [ label ] BRW                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BSF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| c         | [ <i>label</i> ]BTFSS f,b                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nds:      | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| tion:     | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Affected: | None                                                                                                                                                                                                            |

| ption:    | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruction<br>is discarded and a NOP is executed<br>instead, making this a 2-cycle<br>instruction. |

Bit Test f, Skip if Set

| CALL             | Call Subroutine                                                                                                                                                                                                                         |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          |                                                                                                                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |  |  |  |  |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<6:3>) → PC<14:11>                                                                                                                                                                             |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |  |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                     |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                                                           |  |  |  |

| Operands:        | None                                                                                                                                                                                                     |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ \text{0} \rightarrow \text{WDT prescaler,} \\ \text{1} \rightarrow \overline{\text{TO}} \\ \text{1} \rightarrow \overline{\text{PD}} \end{array}$ |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                   |  |  |  |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{TO}$ and PD<br>are set.                                                            |  |  |  |

| CALLW            | Subroutine Call With W [ /abe/ ] CALLW                                                                                                                                                                                |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          |                                                                                                                                                                                                                       |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |  |  |  |  |

| COMF             | Complement f                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                   |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |

| CLRF             | Clear f                                                               |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |  |  |  |

| DECF             | Decrement f [ /abe/ ] DECF f,d                                                                                                                    |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|