### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18346-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| I/O <sup>(2)</sup> | 20-Pin PDIP/SOIC/SSOP | 20-Pin UQFN | ADC  | Reference | Comparator       | NCO | DAC      | WSQ                   | Timers                                                                                  | сср                 | MWG | CWG                                            | MSSP                                           | EUSART            | CLC                   | CLKR | Interrupt                 | Pull-up | Basic             |

|--------------------|-----------------------|-------------|------|-----------|------------------|-----|----------|-----------------------|-----------------------------------------------------------------------------------------|---------------------|-----|------------------------------------------------|------------------------------------------------|-------------------|-----------------------|------|---------------------------|---------|-------------------|

| RA0                | 19                    | 16          | ANA0 | _         | C1IN0+           | —   | DAC1OUT  | -                     | -                                                                                       | —                   | —   | -                                              | —                                              | _                 | —                     | _    | IOC                       | Y       | ICDDAT<br>ICSPDAT |

| RA1                | 18                    | 15          | ANA1 | VREF+     | C1IN0-<br>C2IN0- | —   | DAC1REF+ |                       |                                                                                         | —                   | —   | _                                              | SS2                                            | —                 |                       | l    | IOC                       | Y       | ICDCLK<br>ICSPCLK |

| RA2                | 17                    | 14          | ANA2 | VREF-     | _                | _   | DAC1REF- | _                     | T0CKI <sup>(1)</sup>                                                                    | CCP3 <sup>(1)</sup> | _   | CWG1IN <sup>(1)</sup><br>CWG2IN <sup>(1)</sup> | -                                              | _                 | CLCIN0 <sup>(1)</sup> | _    | IOC<br>INT <sup>(1)</sup> | Y       | _                 |

| RA3                | 4                     | 1           | _    | _         | _                | _   | _        | _                     | _                                                                                       | _                   | _   | _                                              | _                                              | _                 | _                     | _    | IOC                       | Y       | MCLR<br>VPP       |

| RA4                | 3                     | 20          | ANA4 | _         | _                | _   | _        | _                     | T1G <sup>(1)</sup><br>T3G <sup>(1)</sup><br>T5G <sup>(1)</sup><br>SOSCO                 | CCP4 <sup>(1)</sup> | _   | _                                              | _                                              | _                 | _                     | _    | IOC                       | Y       | CLKOUT<br>OSC2    |

| RA5                | 2                     | 19          | ANA5 |           | _                |     | _        | _                     | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T5CKI <sup>(1)</sup><br>SOSCIN<br>SOSCI | _                   | _   | _                                              | Ι                                              | _                 | Ι                     | _    | IOC                       | Y       | CLKIN<br>OSC1     |

| RB4                | 13                    | 10          | ANB4 | _         | _                | _   | —        | _                     | _                                                                                       | _                   | _   | _                                              | SDI1 <sup>(1)</sup><br>SDA1 <sup>(1,3,4)</sup> | _                 | CLCIN2 <sup>(1)</sup> | _    | IOC                       | Y       | _                 |

| RB5                | 12                    | 9           | ANB5 | _         | _                | _   | _        | _                     | _                                                                                       | —                   | _   | _                                              | SDI2 <sup>(1)</sup><br>SDA2 <sup>(1,3,4)</sup> | RX <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> | _    | IOC                       | Υ       | _                 |

| RB6                | 11                    | 8           | ANB6 | _         | _                | _   | _        | _                     | _                                                                                       | —                   | _   | _                                              | SCK1 <sup>(1)</sup><br>SCL1 <sup>(1,3,4)</sup> | _                 | _                     | _    | IOC                       | Y       | _                 |

| RB7                | 10                    | 7           | ANB7 | _         | _                | _   | _        | _                     | _                                                                                       | _                   | _   | _                                              | SCK2 <sup>(1)</sup><br>SCL2 <sup>(1,3,4)</sup> | _                 | _                     | _    | IOC                       | Y       | _                 |

| RC0                | 16                    | 13          | ANC0 | _         | C2IN0+           | _   | _        | _                     | _                                                                                       | —                   | _   | _                                              | _                                              | _                 | _                     | —    | IOC                       | Y       | _                 |

| RC1                | 15                    | 12          | ANC1 |           | C1IN1-<br>C2IN1- | _   | _        | _                     | _                                                                                       | —                   | _   | _                                              | _                                              | _                 | _                     |      | IOC                       | Y       | _                 |

| RC2                | 14                    | 11          | ANC2 | _         | C1IN2-<br>C2IN2- | _   | _        | MDCIN1 <sup>(1)</sup> | _                                                                                       | —                   | _   | _                                              | —                                              | _                 | _                     | _    | IOC                       | Y       | _                 |

TABLE 3: 20-PIN ALLOCATION TABLE (PIC16(L)F18346)

All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. 2:

These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections. 3:

These pins are configured for I<sup>2</sup>C logic levels; clock and data signals may be assigned to any of these pins. Assignments to other pins (e.g., RA5) will operate, but logic levels will be standard 4: TTL/ST as selected by the INLVL register.

### TABLE 1-2: PIC16(L)F18326 PINOUT DESCRIPTION

| Name                                                                                                             | Function | Input<br>Type | Output Type | Description                                          |

|------------------------------------------------------------------------------------------------------------------|----------|---------------|-------------|------------------------------------------------------|

| RA0/ANA0/C1IN0+/DAC1OUT/                                                                                         | RA0      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| SS2 <sup>(1)</sup> / ICDDAT/ICSPDAT                                                                              | ANA0     | AN            | _           | ADC Channel A0 input.                                |

|                                                                                                                  | C1IN0+   | AN            | _           | Comparator C1 positive input.                        |

|                                                                                                                  | DAC1OUT  | _             | AN          | Digital-to-Analog Converter output.                  |

|                                                                                                                  | SS2      | TTL/ST        | —           | Slave Select 2 input.                                |

|                                                                                                                  | ICDDAT   | TTL/ST        | CMOS        | In-Circuit Debug Data I/O.                           |

|                                                                                                                  | ICSPDAT  | TTL/ST        | CMOS        | ICSP™ Data I/O.                                      |

| RA1/ANA1/VREF+/C1IN0-/                                                                                           | RA1      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| C2IN0-/DAC1REF+/ ICDCLK/                                                                                         | ANA1     | AN            | —           | ADC Channel A1 input.                                |

| ICSPCLK                                                                                                          | VREF+    | AN            | —           | ADC positive voltage reference input.                |

|                                                                                                                  | C1IN0-   | AN            | _           | Comparator C1 negative input.                        |

|                                                                                                                  | C2IN0-   | AN            | _           | Comparator C2 negative input.                        |

|                                                                                                                  | DAC1REF+ | _             | AN          | Digital-to-Analog Converter positive reference input |

|                                                                                                                  | ICDCLK   | TTL/ST        | CMOS        | In-Circuit Debug Clock I/O.                          |

|                                                                                                                  | ICSPCLK  | TTL/ST        | CMOS        | ICSP Clock I/O.                                      |

| RA2/ANA2/VREF-/ DAC1REF-/                                                                                        | RA2      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| T0CKI <sup>(1)</sup> / CCP3 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /<br>CWG2IN <sup>(1)</sup> /INT <sup>(1)</sup> | ANA2     | AN            | _           | ADC Channel A2 input.                                |

| CWG2IN <sup>(1</sup> /INI <sup>(1)</sup>                                                                         | VREF-    | AN            | —           | ADC negative voltage reference input.                |

|                                                                                                                  | DAC1REF- | —             | AN          | Digital-to-Analog Converter negative reference inpu  |

|                                                                                                                  | TOCKI    | TTL/ST        | _           | TMR0 Clock input.                                    |

|                                                                                                                  | CCP3     | TTL/ST        | CMOS        | Capture/Compare/PWM 3 input.                         |

|                                                                                                                  | CWG1IN   | TTL/ST        | —           | Complementary Waveform Generator 1 input.            |

|                                                                                                                  | CWG2IN   | TTL/ST        | —           | Complementary Waveform Generator 2 input.            |

|                                                                                                                  | INT      | TTL/ST        | —           | External interrupt input.                            |

| RA3/MCLR/Vpp                                                                                                     | RA3      | TTL/ST        | CMOS        | General purpose I/O.                                 |

|                                                                                                                  | MCLR     | TTL/ST        | —           | Master Clear with internal pull-up.                  |

|                                                                                                                  | Vpp      | HV            | _           | Programming voltage.                                 |

| RA4/ANA4/T1G <sup>(1)</sup> / SOSCO/                                                                             | RA4      | TTL/ST        | CMOS        | General purpose I/O.                                 |

| CLKOUT/OSC2                                                                                                      | ANA4     | AN            | _           | ADC Channel A4 input.                                |

|                                                                                                                  | T1G      | ST            | _           | TMR1 gate input.                                     |

|                                                                                                                  | SOSCO    | _             | XTAL        | Secondary Oscillator connection.                     |

|                                                                                                                  | CLKOUT   | —             | CMOS        | Fosc/4 output.                                       |

|                                                                                                                  | OSC2     | _             | XTAL        | Crystal/Resonator (LP, XT, HS modes).                |

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD

= Open-Drain

TTL = TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL

= Crystal levels

I

I

I

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-1.

All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

### TABLE 1-3: PIC16(L)F18346 PINOUT DESCRIPTION

| Name                                                                                                                                     | Function | Input<br>Type | Output<br>Type | Description                                           |

|------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|----------------|-------------------------------------------------------|

| RA0/ANA0/C1IN0+/DAC1OUT/                                                                                                                 | RA0      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| ICDDAT/ICSPDAT                                                                                                                           | ANA0     | AN            | _              | ADC Channel A0 input.                                 |

|                                                                                                                                          | C1IN0+   | AN            | _              | Comparator C1 positive input.                         |

|                                                                                                                                          | DAC10UT  | —             | AN             | Digital-to-Analog Converter output.                   |

|                                                                                                                                          | ICDDAT   | TTL/ST        | CMOS           | In-Circuit Debug Data I/O.                            |

|                                                                                                                                          | ICSPDAT  | TTL/ST        | CMOS           | ICSP™ Data I/O.                                       |

| RA1/ANA1/VREF+/C1IN0-/                                                                                                                   | RA1      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| C2IN0-/ DAC1REF+/SS2 <sup>(1)</sup> )/<br>ICDCLK/ ICSPCLK                                                                                | ANA1     | AN            | _              | ADC Channel A1 input.                                 |

| ICDCLK/ ICSPCLK                                                                                                                          | VREF+    | AN            | _              | ADC positive voltage reference input.                 |

|                                                                                                                                          | C1IN0-   | AN            | _              | Comparator C1 negative input.                         |

|                                                                                                                                          | C2IN0-   | AN            | _              | Comparator C2 negative input.                         |

|                                                                                                                                          | DAC1REF+ | AN            | _              | Digital-to-Analog Converter positive reference input. |

|                                                                                                                                          | SS2      | TTL/ST        | _              | Slave Select 2 input.                                 |

|                                                                                                                                          | ICDCLK   | TTL/ST        | CMOS           | In-Circuit Debug Clock I/O.                           |

|                                                                                                                                          | ICSPCLK  | TTL/ST        | CMOS           | ICSP Clock I/O.                                       |

| RA2/ANA2/VREF-/ DAC1REF-/                                                                                                                | RA2      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| T0CKI <sup>(1)</sup> / CCP3 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /<br>CWG2IN <sup>(1)</sup> /CLCIN0 <sup>(1)</sup> / INT <sup>(1)</sup> | ANA2     | AN            | _              | ADC Channel A2 input.                                 |

|                                                                                                                                          | VREF-    | AN            | _              | ADC negative voltage reference input.                 |

|                                                                                                                                          | DAC1REF- | AN            | _              | Digital-to-Analog Converter negative reference input. |

|                                                                                                                                          | T0CKI    | TTL/ST        | _              | TMR0 Clock input.                                     |

|                                                                                                                                          | CCP3     | TTL/ST        | CMOS           | Capture/Compare/PWM 3 input.                          |

|                                                                                                                                          | CWG1IN   | TTL/ST        | _              | Complementary Waveform Generator 1 input.             |

|                                                                                                                                          | CWG2IN   | TTL/ST        | _              | Complementary Waveform Generator 2 input.             |

|                                                                                                                                          | CLCIN0   | TTL/ST        | —              | Configurable Logic Cell 0 input.                      |

|                                                                                                                                          | INT      | TTL/ST        | —              | External interrupt input.                             |

| RA3/MCLR/Vpp                                                                                                                             | RA3      | TTL/ST        | CMOS           | General purpose I/O.                                  |

|                                                                                                                                          | MCLR     | TTL/ST        | —              | Master Clear with internal pull-up.                   |

|                                                                                                                                          | Vpp      | HV            | —              | Programming voltage.                                  |

| RA4/ANA4/T1G(1)/T3G <sup>(1)</sup> /                                                                                                     | RA4      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| T5G <sup>(1)</sup> /SOSCO/CCP4 <sup>(1)</sup> /<br>CLKOUT/OSC2                                                                           | ANA4     | AN            | _              | ADC Channel A4 input.                                 |

| CEROUT/OSC2                                                                                                                              | T1G      | TTL/ST        | —              | TMR1 gate input.                                      |

|                                                                                                                                          | T3G      | TTL/ST        | —              | TMR3 gate input.                                      |

|                                                                                                                                          | T5G      | TTL/ST        | _              | TMR5 gate input.                                      |

|                                                                                                                                          | SOSCO    | —             | XTAL           | Secondary Oscillator connection.                      |

|                                                                                                                                          | CCP4     | TTL/ST        | CMOS           | Capture/Compare/PWM 4 input.                          |

|                                                                                                                                          | CLKOUT   | —             | CMOS           | Fosc/4 output.                                        |

|                                                                                                                                          | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                 |

Legend:AN= Analog input or outputCMOS= CMOS compatible input or outputOD= Open-DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levelsI<sup>2</sup>C= Schmitt Trigger input with I<sup>2</sup>CHV= High VoltageXTAL= Crystal levelsI<sup>2</sup>C= Schmitt Trigger input with I<sup>2</sup>C

**Note 1:** Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|------------|----------------------------------------------------------|

|------------|----------------------------------------------------------|

| Address | Name   | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7   | Bit 6   | Bit 5       | Bit 4           | Bit 3             | Bit 2   | Bit 1   | Bit 0                                 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------------------|---------|---------|-------------|-----------------|-------------------|---------|---------|---------------------------------------|-----------------------|---------------------------------|

| Bank 7  |        |                                  |         |         |             |                 |                   |         |         |                                       |                       |                                 |

|         |        |                                  |         |         | CPU CORE RE | EGISTERS; see 1 | Table 4-2 for spe | cifics  |         |                                       |                       |                                 |

| 38Ch    | INLVLA |                                  | —       | —       | INLVLA5     | INLVLA4         | INLVLA3           | INLVLA2 | INLVLA1 | INLVLA0                               | 11 1111               | 11 111                          |

| 38Dh    | INLVLB | X —                              |         |         |             | Unimple         | mented            |         |         |                                       | -                     | —                               |

|         |        | — X                              | INLVLB7 | INLVLB6 | INLVLB5     | INLVLB4         | —                 | —       | _       | —                                     | 1111                  | 1111                            |

| 38Eh    | INLVLC | X —                              | —       | —       | INLVLC5     | INLVLC4         | INLVLC3           | INLVLC2 | INLVLC1 | INLVLC0                               | 11 1111               | 11 111                          |

|         |        | — X                              | INLVLC7 | INLVLC6 | INLVLC5     | INLVLC4         | INLVLC3           | INLVLC2 | INLVLC1 | INLVLC0                               | 1111 1111             | 1111 111                        |

| 38Fh    | —      | —                                |         |         |             | Unimple         | mented            |         |         |                                       | -                     | —                               |

| 390h    | —      | -                                |         |         |             | Unimple         | mented            |         |         |                                       | -                     | _                               |

| 391h    | IOCAP  |                                  | —       | —       | IOCAP5      | IOCAP4          | IOCAP3            | IOCAP2  | IOCAP1  | IOCAP0                                | 00 0000               | 00 000                          |

| 392h    | IOCAN  |                                  | —       | _       | IOCAN5      | IOCAN4          | IOCAN3            | IOCAN2  | IOCAN1  | IOCAN0                                | 00 0000               | 00 000                          |

| 393h    | IOCAF  |                                  | _       | —       | IOCAF5      | IOCAF4          | IOCAF3            | IOCAF2  | IOCAF1  | IOCAF0                                | 00 0000               | 00 000                          |

| 394h    | IOCBP  | X —                              |         | •       |             | Unimple         | mented            |         |         | •                                     | _                     | _                               |

|         |        | — X                              | IOCBP7  | IOCBP6  | IOCBP5      | IOCBP4          | —                 | —       | —       | _                                     | 0000                  | 0000                            |

| 395h    | IOCBN  | X —                              |         | •       |             | Unimple         | mented            |         |         | •                                     | _                     | _                               |

|         |        | — X                              | IOCBN7  | IOCBN6  | IOCBN5      | IOCBN4          | —                 | —       | —       | _                                     | 0000                  | 0000                            |

| 396h    | IOCBF  | X —                              |         | -       |             | Unimple         | mented            |         |         | · · · · · · · · · · · · · · · · · · · | -                     | —                               |

|         |        | — X                              | IOCBF7  | IOCBF6  | IOCBF5      | IOCBF4          | —                 | _       |         |                                       | 0000                  | 0000                            |

| 397h    | IOCCP  | × —                              | —       | _       | IOCCP5      | IOCCP4          | IOCCP3            | IOCCP2  | IOCCP1  | IOCCP0                                | 00 0000               | 00 000                          |

|         |        | — X                              | IOCCP7  | IOCCP6  | IOCCP5      | IOCCP4          | IOCCP3            | IOCCP2  | IOCCP1  | IOCCP0                                | 0000 0000             | 0000 000                        |

| 398h    | IOCCN  | X —                              | —       | —       | IOCCN5      | IOCCN4          | IOCCN3            | IOCCN2  | IOCCN1  | IOCCN0                                | 00 0000               | 00 000                          |

IOCCN3

IOCCF3

IOCCF3

IOCCN2

IOCCF2

IOCCF2

IOCCN1

IOCCF1

IOCCF1

IOCCN0

IOCCF0

IOCCF0

0000 0000

--00 0000

0000 0000 0000 0000

0000 0000

--00 0000

399h

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

IOCCN4

IOCCF4

IOCCF4

IOCCN5

IOCCF5

IOCCF5

Note 1: Only on PIC16F18326/18346.

IOCCF

2: Register accessible from both User and ICD Debugger.

Х

Х

X —

IOCCN7

\_

IOCCF7

IOCCN6

\_

IOCCF6

| TABLE           | 4-4: SPE | CIAL F                           | UNCTION RE | EGISTER SI       | UMMARY B    | SANKS 0-31 (  | (CONTINUEI        | <b>D</b> ) |       |       |                       |                                 |  |

|-----------------|----------|----------------------------------|------------|------------------|-------------|---------------|-------------------|------------|-------|-------|-----------------------|---------------------------------|--|

| Address         | Name     | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7      | Bit 6            | Bit 5       | Bit 4         | Bit 3             | Bit 2      | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |  |

| Banks           | 15-16    |                                  |            |                  |             |               |                   |            |       |       |                       |                                 |  |

|                 |          |                                  |            |                  | CPU CORE RI | EGISTERS; see | Table 4-2 for spe | cifics     |       |       |                       |                                 |  |

| 78Ch to<br>79FH | -        | -                                |            |                  |             | Unimple       | emented           |            |       |       | -                     | —                               |  |

| 80Ch to<br>81Fh | _        | -                                |            | Unimplemented    |             |               |                   |            |       |       |                       |                                 |  |

| Bank 1          | 7        |                                  |            |                  |             |               |                   |            |       |       |                       |                                 |  |

| 88Ch            | —        | —                                |            |                  |             | Unimple       | emented           |            |       |       | -                     | —                               |  |

| 88Dh            | —        | —                                |            |                  |             | Unimple       | emented           |            |       |       | —                     | —                               |  |

| 88Eh            | —        | —                                |            |                  |             | Unimple       | emented           |            |       |       | _                     |                                 |  |

| 88Fh            | —        | —                                |            |                  |             | Unimple       | emented           |            |       |       | -                     | _                               |  |

| 890h            | —        | —                                |            |                  |             | Unimple       | emented           |            |       |       | _                     |                                 |  |

| 891h            | NVMADRL  |                                  |            |                  |             | NVMAD         | R<7:0>            |            |       |       | 0000 0000             | 0000 000                        |  |

| 892h            | NVMADRH  |                                  | —          | – NVMADR<14:8>   |             |               |                   |            |       |       |                       |                                 |  |

| 893h            | NVMDATL  |                                  |            | NVMDAT<7:0>      |             |               |                   |            |       |       |                       |                                 |  |

| 894h            | NVMDATH  |                                  | _          | —                |             |               | NVMDA             | T<13:8>    |       |       | 00 0000               | 00 000                          |  |

| 895h            | NVMCON1  |                                  | _          | NVMREGS          | LWLO        | FREE          | WRERR             | WREN       | WR    | RD    | -000 x000             | -000 q00                        |  |

| 896h            | NVMCON2  |                                  |            | NVMCON2 0000 001 |             |               |                   |            |       |       |                       |                                 |  |

Unimplemented

Unimplemented

Unimplemented

Unimplemented

Unimplemented

RMCLR

RI

POR

RWDT

897h

898h

899h

89Ah

89Bh

89Fh

89Ch to

\_

\_

\_

PCON0

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

\_

Only on PIC16F18326/18346. Note 1:

Register accessible from both User and ICD Debugger. 2:

STKOVF

STKUNF

\_

\_

\_

\_

\_

—

\_

—

\_

00-1 110q qq-q qquu

BOR

—

\_

\_

| IADLE   | 4-4. JFE |                                  |         | EGISTER SU |             | ANNO U-DI     | CONTINUE          | )       |           |        |                       |                                 |

|---------|----------|----------------------------------|---------|------------|-------------|---------------|-------------------|---------|-----------|--------|-----------------------|---------------------------------|

| Address | Name     | PIC16(L)F18326<br>PIC16(L)F18346 | Bit 7   | Bit 6      | Bit 5       | Bit 4         | Bit 3             | Bit 2   | Bit 1     | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank 1  | 8        |                                  |         |            |             |               |                   |         |           |        |                       |                                 |

|         |          |                                  |         |            | CPU CORE RE | EGISTERS; see | Table 4-2 for spe | cifics  |           |        |                       |                                 |

| 90Ch    | _        | _                                |         |            |             | Unimple       | mented            |         |           |        | _                     | _                               |

| 90Dh    | —        | -                                |         |            |             | Unimple       | mented            |         |           |        | —                     | —                               |

| 90Eh    | —        | _                                |         |            |             | Unimple       | mented            |         |           |        | —                     | —                               |

| 90Fh    | —        | —                                |         |            |             | Unimple       | Unimplemented     |         |           |        |                       | _                               |

| 910h    | —        | —                                |         |            |             | Unimple       | mented            |         |           |        | —                     | _                               |

| 911h    | PMD0     |                                  | SYSCMD  | FVRMD      | _           | —             | —                 | NVMMD   | CLKRMD    | IOCMD  | 00000                 | 0000                            |

| 912h    | PMD1     |                                  | NCOMD   | TMR6MD     | TMR5MD      | TMR4MD        | TMR3MD            | TMR2MD  | TMR1MD    | TMR0MD | 0000                  | 000                             |

| 913h    | PMD2     |                                  | —       | DACMD      | ADCMD       | —             | —                 | CMP2MD  | CMP1MD    | _      | -000-                 | -00(                            |

| 914h    | PMD3     |                                  | CWG2MD  | CWG1MD     | PWM6MD      | PWM5MD        | CCP4MD            | CCP3MD  | CCP2MD    | CCP1MD | -00000                | -0000                           |

| 915h    | PMD4     |                                  | —       | —          | UART1MD     | —             | —                 | MSSP2MD | MSSP1MD   | —      | 00-                   | 0(                              |

| 916h    | PMD5     |                                  | _       | —          |             | CLC4MD        | CLC3MD            | CLC2MD  | CLC1MD    | DSMMD  | 000                   | 00                              |

| 917h    | —        | —                                |         |            |             | Unimple       | mented            |         |           |        | —                     |                                 |

| 918h    | CPUDOZE  |                                  | IDLEN   | DOZEN      | ROI         | DOE           |                   |         | DOZE<2:0> |        | 000000                | 00000                           |

| 919h    | OSCCON1  |                                  |         |            | NOSC<2:0>   |               |                   | NDIV    | <3:0>     |        | -qqq 0000             | -qqq 000                        |

| 91Ah    | OSCCON2  |                                  | _       |            | COSC<2:0>   | 1             |                   | CDIV    | <3:0>     |        | -qqq 0000             | -qqq 000                        |

| 91Bh    | OSCCON3  |                                  | CSWHOLD | SOSCPWR    | SOSCBE      | ORDY          | NOSCR             | —       | —         | —      | 0000 0                | 0000 0                          |

| 91Ch    | OSCSTAT1 |                                  | EXTOR   | HFOR       | —           | LFOR          | SOR               | ADOR    | —         | PLLR   | dd-d dd-d             | dd-d dd-                        |

| 91Dh    | OSCEN    |                                  | EXTOEN  | HFOEN      | —           | LFOEN         | SOSCEN            | ADOEN   | —         | —      | 00-0 00               | 00-0 00-                        |

| 91Eh    | OSCTUNE  |                                  | _       | _          |             |               | HFTU              |         |           |        | 10 0000               | 10 000                          |

| 91Fh    | OSCFRQ   |                                  | _       | —          | _           | —             |                   | HFFR    | Q<3:0>    |        | qqq                   | qq                              |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Only on PIC16F18326/18346. Legend:

Note 1:

2: Register accessible from both User and ICD Debugger.

| REGISTE      | R 5-3: CON            | FIGURATION                       | WORD 3: IN      | EMORY          |                  |              |            |

|--------------|-----------------------|----------------------------------|-----------------|----------------|------------------|--------------|------------|

|              |                       | R/P-1                            | U-1             | U-1            | U-1              | U-1          | U-1        |

|              |                       | LVP <sup>(1)</sup>               | —               | _              | —                | —            | —          |

|              |                       | bit 13                           |                 |                |                  |              | bit 8      |

|              |                       |                                  |                 |                |                  |              |            |

| U-1          | U-1                   | U-1                              | U-1             | U-1            | U-1              | R/P-1        | R/P-1      |

| —            | —                     | —                                | —               | —              | —                | WRT1         | WRT0       |

| bit 7        |                       |                                  |                 |                |                  |              | bit 0      |

| <u>.</u>     |                       |                                  |                 |                |                  |              |            |

| Legend:      |                       |                                  |                 |                |                  |              |            |

| R = Reada    | able bit              | P = Programn                     | nable bit       | U = Unimplem   | nented bit, read | as '1'       |            |

| '0' = Bit is | cleared               | '1' = Bit is set                 |                 | n = Value whe  | en blank or afte | r Bulk Erase |            |

|              |                       |                                  |                 |                |                  |              |            |

| bit 13       | LVP: Low-Vo           | oltage Programn                  | ning Enable bit | (1)            |                  |              |            |

|              |                       | ow-Voltage Pro                   | • •             | enabled. MC    | LR/VPP pin f     | unction is M | CLR. MCLRE |

|              |                       | Configuration bit                |                 |                | in a             |              |            |

|              |                       | IV on MCLR/VP                    |                 | a for programm | ing.             |              |            |

| bit 12-2     |                       | nted: Read as '1                 |                 |                |                  |              |            |

| bit 1-0      |                       | User NVM Self-                   |                 | n bits         |                  |              |            |

|              | 11 = OFF<br>10 = POOT | Write protectio<br>0000h to 01FF |                 | ed 0200h to 31 | EEEh may be m    | odified      |            |

|              |                       | 0000h to 1FFF                    | •               |                | •                |              |            |

|              | 00 = ALL              | 0000h to 3FFF                    |                 |                |                  |              |            |

|              | WRT applies           | only to the self-                |                 |                |                  |              | protected. |

| Note 1:      | The LVP bit cann      | not be programm                  | ned to '0' wher | Programming    | mode is entere   | ed via LVP.  |            |

### **REGISTER 5-3: CONFIGURATION WORD 3: MEMORY**

# PIC16(L)F18326/18346

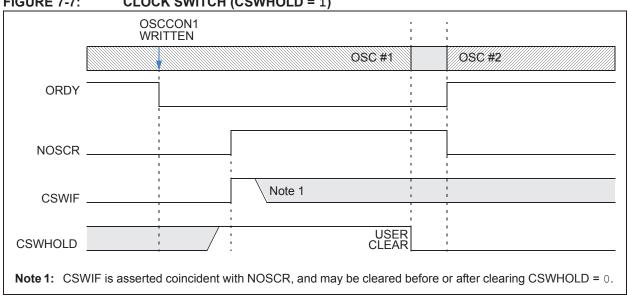

## FIGURE 7-6: CLOCK SWITCH (CSWHOLD = 0) OSCCON1 WRITTEN OSC #1 OSC #2 ORDY Note 2 NOSCR Note '1 CSWIF USER CLEAR **CSWHOLD**

Note 1: CSWIF is asserted coincident with NOSCR; interrupt is serviced at OSC#2 speed. 2: The assertion of NOSCR is hidden from the user because it appears only for the duration of the switch.

### FIGURE 7-7: CLOCK SWITCH (CSWHOLD = 1)

### 9.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0). If the SLEEP instruction is executed while the IDLEN bit is set (IDLEN = 1), the CPU will enter the Idle mode (Section 9.2.3 "Low-Power Sleep Mode").

Upon entering Sleep mode, the following conditions exist:

- 1. Resets other than WDT are not affected by Sleep mode; WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The PD bit of the STATUS register is cleared

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set

- 4. The CPU and System clocks are disabled

- 31 kHz LFINTOSC, HFINTOSC and SOSC will remain enabled if any peripheral has requested them as a clock source or if the HFOEN, LFOEN, or SOSCEN bits of the OSCEN register are set.

- ADC is unaffected if the dedicated ADCRC oscillator is selected. When the ADC clock is something other than ADCRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains active.

- 7. I/O ports maintain the status they had before SLEEP was executed (driving high, low, or high-impedance) only if no peripheral connected to the I/O port is active.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 24.0 "5-bit Digital-to-Analog Converter (DAC1) Module" and Section 16.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 9.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled

- 5. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last two events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to Section 6.11 "Determining the Cause of a Reset".

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

### 9.2.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

U

**S**

F18326/18346

DS40001839B-page 254

Preliminary

### **REGISTER 23-4:** NCO1ACCH: NCO1 ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0        | R/W-0/0         | R/W-0/0           | R/W-0/0    |

|------------------|---------|--------------------|---------|----------------|-----------------|-------------------|------------|

|                  |         |                    | NCO1A   | CC<15:8>       |                 |                   |            |

| bit 7            |         |                    |         |                |                 |                   | bit 0      |

|                  |         |                    |         |                |                 |                   |            |

| Legend:          |         |                    |         |                |                 |                   |            |

| R = Readable     | bit     | W = Writable b     | it      | U = Unimplem   | ented bit, read | as '0'            |            |

| u = Bit is uncha | anged   | x = Bit is unkno   | own     | -n/n = Value a | t POR and BOF   | R/Value at all ot | her Resets |

| '1' = Bit is set |         | '0' = Bit is clear | red     |                |                 |                   |            |

bit 7-0 NCO1ACC<15:8>: NCO1 Accumulator, high byte

### **REGISTER 23-5:** NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-------|-----|-----|-----|----------------|---------|---------|---------|--|--|--|

| —     | —   | —   | —   | NCO1ACC<19:16> |         |         |         |  |  |  |

| bit 7 |     |     |     |                |         |         | bit 0   |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1ACC<19:16>: NCO1 Accumulator, upper byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH:NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real-time, asynchronously to the CPU; there is no provision to ensure atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

### **REGISTER 23-6:** NCO1INCL<sup>(1,2)</sup>: NCO1 INCREMENT REGISTER – LOW BYTE

| R/W-0/0      | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 |  |  |  |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|

| NCO1INC<7:0> |             |         |         |         |         |         |         |  |  |  |

| bit 7        | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 NCO1INC<7:0>: NCO1 Increment, low byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

2: NCO1INC is double-buffered as INCBUF; INCBUF is updated on the next falling edge of NCOCLK after writing to NCO1INCL;NCO1INCU and NCO1INCH should be written prior to writing NCO1INCL.

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|--------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                    | NCO1I   | NC<15:8>       |                  |                  |              |

| bit 7            |         |                    |         |                |                  |                  | bit 0        |

|                  |         |                    |         |                |                  |                  |              |

| Legend:          |         |                    |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable bi    | it      | U = Unimplem   | nented bit, read | l as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unkno   | wn      | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clear | red     |                |                  |                  |              |

## **REGISTER 23-7:** NCO1INCH<sup>(1)</sup>: NCO1 INCREMENT REGISTER – HIGH BYTE

bit 7-0 NCO1INC<15:8>: NCO1 Increment, high byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

### **REGISTER 23-8:** NCO1INCU<sup>(1)</sup>: NCO1 INCREMENT REGISTER – UPPER BYTE

|       |     |     | • • • • • • • • • • • • • • • • • • • • |                |         |         |         |  |

|-------|-----|-----|-----------------------------------------|----------------|---------|---------|---------|--|

| U-0   | U-0 | U-0 | U-0                                     | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

| —     | —   | —   | —                                       | NCO1INC<19:16> |         |         |         |  |

| bit 7 |     |     |                                         |                |         |         | bit 0   |  |

### Legend:

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1INC<19:16>: NCO1 Increment, upper byte

**Note 1:** The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

# PIC16(L)F18326/18346

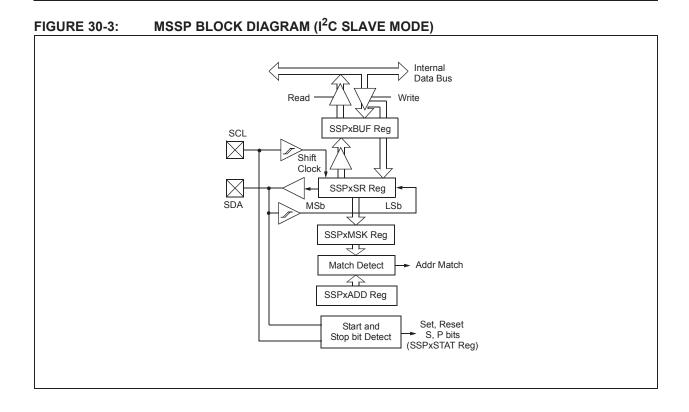

### 30.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see Section 30.5.6 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This  $\overline{ACK}$ value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

### 30.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

### 30.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 30-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- Note 1: If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

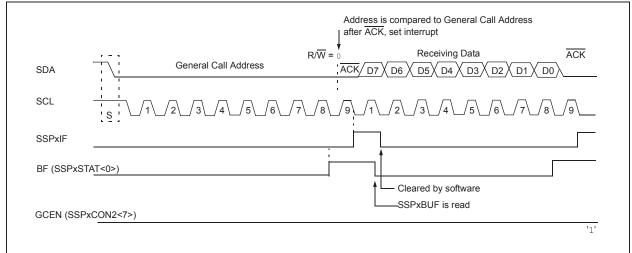

### 30.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^{2}C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with

the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 30-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

### FIGURE 30-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

### 30.5.9 SSP MASK REGISTER

An SSP Mask (SPPxMSK) register (Register 30-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

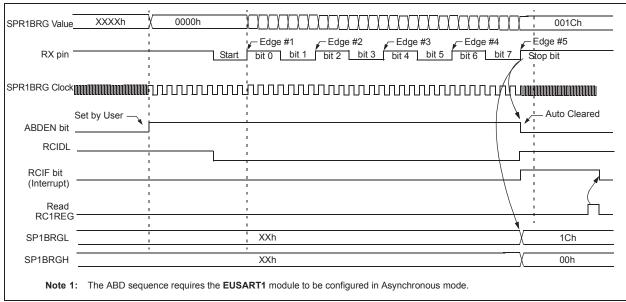

### 31.3.1 AUTO-BAUD DETECT

The EUSART1 module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUD1CON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART1 state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Figure 31-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SP1BRGH, SP1BRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RC1REG needs to be read to clear the RCIF interrupt. RC1REG content should be discarded. When calibrating for modes that do not use the SP1BRGH register the user can verify that the SP1BRGL register did not overflow by checking for 00h in the SP1BRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 31-1. During ABD, both the SP1BRGH and SP1BRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SP1BRGH and SP1BRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 31.3.3 "Auto-Wake-up on Break").

2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART1 baud rates are not possible.

**3:** During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SP1BRGH:SP1BRGL register pair.

| TABLE 31-1: BRG COUNTER CLOCK RATE | TABLE 31-1: | <b>BRG COUNTER CLOCK RATES</b> |

|------------------------------------|-------------|--------------------------------|

|------------------------------------|-------------|--------------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SP1BRGL and SP1BRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

### FIGURE 31-6: AUTOMATIC BAUD RATE CALIBRATION

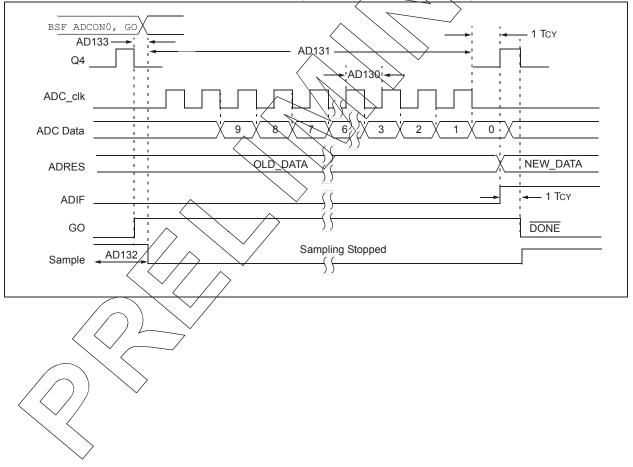

### TABLE 35-13: ANALOG-TO DIGITAL CONVERTER (ADC) CONVERSION TIMING SPECIFICATIONS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                 |            |       |      |       |                                                             |  |  |

|---------------|---------------------------------------------------------|---------------------------------|------------|-------|------|-------|-------------------------------------------------------------|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                  | Min.       | Typ.† | Max. | Units | Conditions                                                  |  |  |

| AD20          | TAD                                                     | ADC Clock Period                | 1          |       | 9    | us    | Using Fosc as the ADC clock source;<br>ADCS $! = \times 11$ |  |  |

| AD21          |                                                         |                                 | 1          | 2     | 6    | us    | Using ADCRC as the<br>ADC clock source,<br>ADCS = 11        |  |  |

| AD22          | TCNV                                                    | Conversion Time                 | _          | 11    | _    | TAD   | Set of GO/DONE bit to<br>Clear of GO/DONE bit               |  |  |

| AD23          | TACQ                                                    | Acquisition Time                | _          | 2     | _    | us    |                                                             |  |  |

| AD24          | THCD                                                    | Sample and Hold Capacitor       |            | _     | _    | us <  | Fosc based clock source                                     |  |  |

|               |                                                         | Disconnect Time                 |            |       | _    | us    | ADCRC based clock source                                    |  |  |

| *             | L<br>These na                                           | arameters are characterized but | not tested | I     | <    |       |                                                             |  |  |

These parameters are characterized but not tested.

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

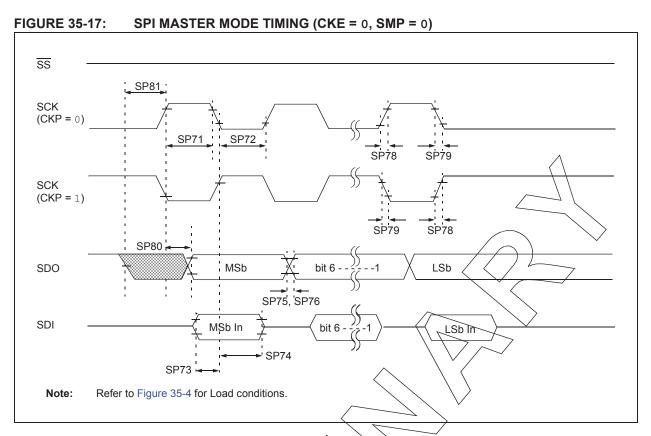

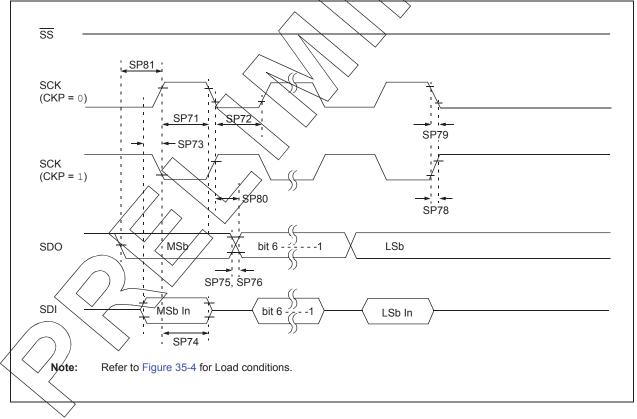

### FIGURE 35-18: SPI MASTER MODE TIMING (CKE = 1, SMR = 1)

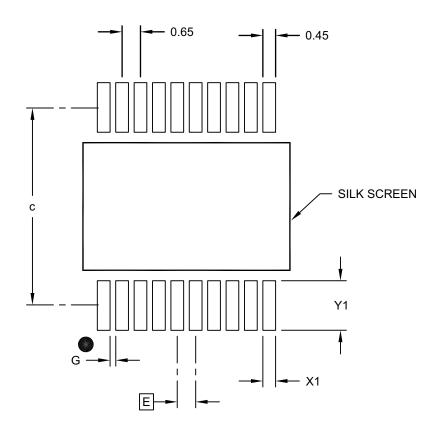

### 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | N                | <b>MILLIMETER</b> | ILLIMETERS<br>NOM MAX<br>0.65 BSC |      |  |

|--------------------------|------------------|-------------------|-----------------------------------|------|--|

| Dimensior                | Dimension Limits |                   |                                   | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC          |                                   |      |  |

| Contact Pad Spacing      | С                |                   | 7.20                              |      |  |

| Contact Pad Width (X20)  | X1               |                   |                                   | 0.45 |  |

| Contact Pad Length (X20) | Y1               |                   |                                   | 1.75 |  |

| Distance Between Pads    | G                | 0.20              |                                   |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072B