Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                 |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 71                                                                               |

| Program Memory Size        | 96KB (96K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 27x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30290fathp-u3a |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

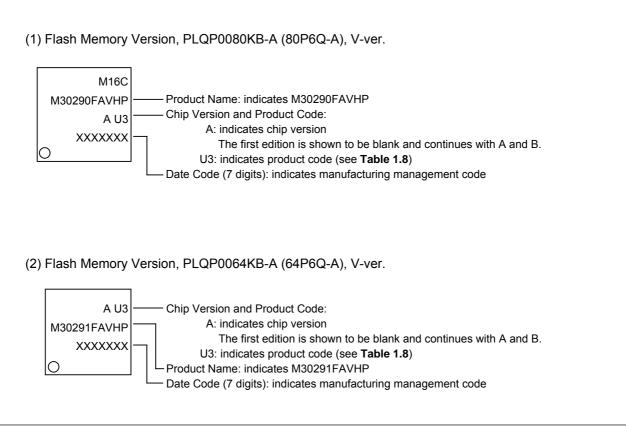

Figure 1.6 Marking Diagrams of Flash Memory Version - M16C/29 Group V-ver. (Top View)

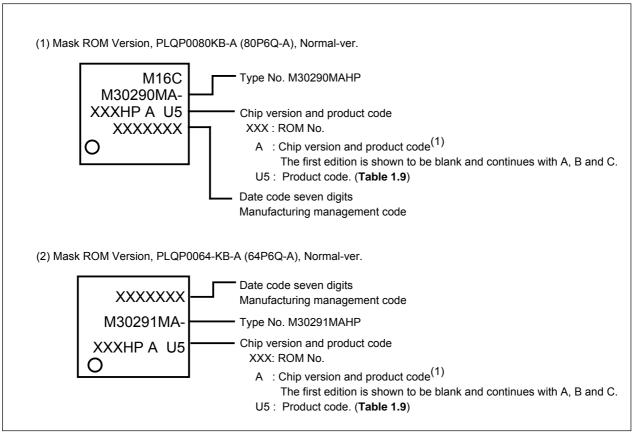

Figure 1.7 Marking Diagrams of Mask ROM Version - M16C/29 Group Normal-ver. (Top View)

### Table 4.2 SFR Information (2)

| Address                                  | Register                                                                                                                                                                           | Symbol                        | After reset            |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------|

| 004016                                   |                                                                                                                                                                                    |                               |                        |

| 004116                                   | CAN0 wakeup interrupt control register                                                                                                                                             | C01WKIC                       | XXXXX0002              |

| 004216                                   | CANO successful reception interrupt control register                                                                                                                               | CORECIC                       | XXXXX0002              |

| 004316                                   | CAN0 successful transmission interrupt control register                                                                                                                            |                               | XXXXX0002              |

| 004416                                   | INT3 interrupt control register                                                                                                                                                    | INT3IC                        | XX00X0002              |

| 004516                                   | ICOC 0 interrupt control register                                                                                                                                                  |                               | XXXXX0002              |

| 004616                                   | ICOC 1 interrupt control register, I <sup>2</sup> C bus interface interrupt control register 1<br>ICOC base timer interrupt control register, ScL/SDA interrupt control register 2 | ICOC1IC,IICIC<br>BTIC,SCLDAIC | XXXXX0002<br>XXXXX0002 |

| 0047 <sub>16</sub><br>0048 <sub>16</sub> | SI/O4 interrupt control register, INT5 interrupt control register                                                                                                                  | S4IC, INT5IC                  | XX00X0002              |

| 004916                                   | SI/O3 interrupt control register, INT4 interrupt control register                                                                                                                  | S3IC, INT4IC                  | XX00X0002              |

| 004A16                                   | UART2 Bus collision detection interrupt control register                                                                                                                           | BCNIC                         | XXXXX0002              |

| 004B16                                   | DMA0 interrupt control register                                                                                                                                                    | DM0IC                         | XXXXX0002              |

| 004C16                                   | DMA1 interrupt control register                                                                                                                                                    | DM1IC                         | XXXXX0002              |

| 004D16                                   | CAN0 error interrupt control register                                                                                                                                              | C01ERRIC                      | XXXXX0002              |

| 004E16                                   | A/D conversion interrupt control register, Key input interrupt control register (Note 2)                                                                                           | ADIC, KUPIC                   | XXXXX0002              |

| 004F16                                   | UART2 transmit interrupt control register                                                                                                                                          | S2TIC                         | XXXXX0002              |

| 005016                                   | UART2 receive interrupt control register                                                                                                                                           | S2RIC                         | XXXXX0002              |

| 005116                                   | UART0 transmit interrupt control register                                                                                                                                          | SOTIC                         | XXXXX0002              |

| 005216                                   | UART0 receive interrupt control register                                                                                                                                           | SORIC                         | XXXXX0002              |

| 005316                                   | UART1 transmit interrupt control register                                                                                                                                          | S1TIC                         | XXXXX0002              |

| 005416                                   | UART1 receive interrupt control register                                                                                                                                           | S1RIC                         | XXXXX0002              |

| 005516                                   | TimerA0 interrupt control register                                                                                                                                                 | TAOIC                         | XXXXX0002              |

| 005616                                   | TimerA1 interrupt control register TimerA2 interrupt control register                                                                                                              | TA1IC<br>TA2IC                | XXXXX0002<br>XXXXX0002 |

| 0057 <sub>16</sub><br>0058 <sub>16</sub> | TimerA2 Interrupt control register                                                                                                                                                 | TA3IC                         | XXXXX0002              |

| 005816                                   | TimerA4 interrupt control register                                                                                                                                                 | TA4IC                         | XXXXX0002              |

| 005A16                                   | TimerB0 interrupt control register                                                                                                                                                 | TBOIC                         | XXXXX0002              |

| 005B16                                   | TimerB1 interrupt control register                                                                                                                                                 | TB1IC                         | XXXXX0002              |

| 005C16                                   | TimerB2 interrupt control register                                                                                                                                                 | TB2IC                         | XXXXX0002              |

| 005D16                                   | INTO interrupt control register                                                                                                                                                    | INTOIC                        | XX00X0002              |

| 005E16                                   | INT1 interrupt control register                                                                                                                                                    | INT1IC                        | XX00X0002              |

| 005F16                                   | INT2 interrupt control register                                                                                                                                                    | INT2IC                        | XX00X0002              |

| 006016                                   | CAN0 message box 0: Identifier/DLC                                                                                                                                                 |                               | XX16                   |

| 006116                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006216                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006316                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006416                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006516                                   | CANO magazara hay 0 : Data field                                                                                                                                                   |                               | XX16<br>XX16           |

| 006616<br>006716                         | CAN0 message box 0 : Data field                                                                                                                                                    |                               | XX16                   |

| 006716<br>006816                         |                                                                                                                                                                                    |                               | XX16                   |

| 006916                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006A16                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006B16                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006C16                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006D16                                   |                                                                                                                                                                                    |                               | XX16                   |

| 006E16                                   | CAN0 message box 0 : Time stamp                                                                                                                                                    |                               | XX16                   |

| 006F16                                   |                                                                                                                                                                                    |                               | XX16                   |

| 007016                                   | CAN0 message box 1 : Identifier/DLC                                                                                                                                                |                               | XX16                   |

| 007116                                   |                                                                                                                                                                                    |                               | XX16                   |

| 007216                                   |                                                                                                                                                                                    |                               | XX16                   |

| 007316                                   |                                                                                                                                                                                    |                               | XX16                   |

| 007416                                   |                                                                                                                                                                                    |                               | XX16                   |

| 007516                                   | CANO mossage hav 1 : Data field                                                                                                                                                    |                               | XX16<br>XX16           |

| 0076 <sub>16</sub><br>0077 <sub>16</sub> | CAN0 message box 1 : Data field                                                                                                                                                    |                               | XX16<br>XX16           |

| 007716<br>007816                         |                                                                                                                                                                                    |                               | XX16                   |

| 007816<br>007916                         |                                                                                                                                                                                    |                               | XX16                   |

| 007916<br>007A16                         |                                                                                                                                                                                    |                               | XX16                   |

| 007B16                                   |                                                                                                                                                                                    |                               | XX16                   |

| 007C16                                   |                                                                                                                                                                                    |                               | XX16                   |

| 007D16                                   |                                                                                                                                                                                    |                               | XX16                   |

|                                          | CAN0 message box 1 : Time stamp                                                                                                                                                    |                               | XX16                   |

| 007E16                                   |                                                                                                                                                                                    |                               |                        |

Note 1: The blank areas are reserved and cannot be used by users. Note 2: A/D conversion interrupt control register is effective when the bit1(Interrupt source select register ( address 35Eh IFSR2A) is set to "0". Key input interrupt control register is effective when the bit1 is set to "1". X : Undefined

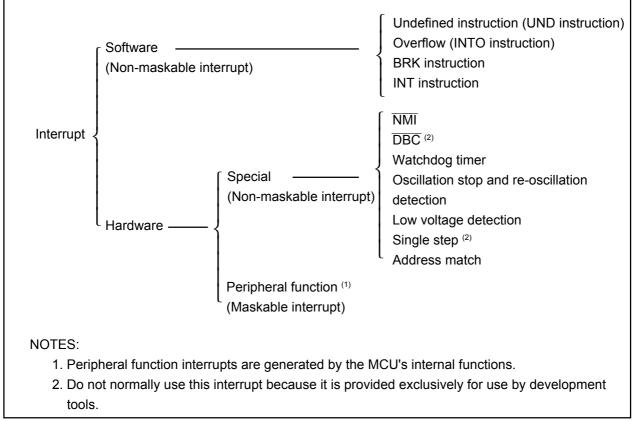

# 9. Interrupts

### Note

The SI/O4 interrupt of peripheral function interrupts is not available in the 64-pin package. The low voltage detection function is not available in M16C/29 T-ver. and V-ver..

## 9.1 Type of Interrupts

Figure 9.1 shows types of interrupts.

#### Figure 9.1 Interrupts

- Maskable Interrupt: An interrupt which can be enabled (disabled) by the interrupt enable flag (I flag) or

whose interrupt priority <u>can be changed</u> by priority level.

- Non-maskable Interrupt: An interrupt which cannot be enabled (disabled) by the interrupt enable flag (I flag) or whose interrupt priority <u>cannot be changed</u> by priority level.

| 7 b6 b5 b4 b3 b2 b |    | Symbol<br>INVC1 | Address<br>034916                                | After Reset<br>0016                                                                                                                                                                  |    |

|--------------------|----|-----------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                    | ļļ | Bit Symbol      | Bit Name                                         | Function                                                                                                                                                                             | RW |

|                    | -  | INV10           | Timer A1, A2, A4 start trigger signal select bit | 0: Timer B2 underflow<br>1: Timer B2 underflow and write to the<br>TB2 register <sup>(2)</sup>                                                                                       | RW |

|                    |    | INV11           | Timer A1-1, A2-1, A4-1<br>control bit (3)        | 0: Three-phase mode 0 (4)<br>1: Three-phase mode 1                                                                                                                                   | RW |

|                    |    | INV12           | Dead time timer count source select bit          | 0: f1 or f2<br>1: f1 divided by 2 or f2 divided by 2                                                                                                                                 | RW |

|                    |    | INV13           | Carrier wave detect flag <sup>(5)</sup>          | 0: Timer Reload control signal is set to 0<br>1: Timer Reload control signal is set to 1                                                                                             | RO |

|                    | [  | INV14           | Output polarity control bit                      | 0 : Output waveform "L" active<br>1 : Output waveform "H" active                                                                                                                     | RW |

|                    |    | INV15           | Dead time invalid bit                            | 0: Dead time timer enabled<br>1: Dead time timer disabled                                                                                                                            | RW |

|                    |    | INV16           | Dead time timer trigger select bit               | <ul> <li>0: Falling edge of timer A4, A1 or A2<br/>one-shot pulse</li> <li>1: Rising edge of three-phase output shift<br/>register (U, V or W phase) output<sup>(6)</sup></li> </ul> | RW |

|                    |    | Reserved bit    | Set to 0                                         | RW                                                                                                                                                                                   |    |

#### NOTES:

- 1. Write to this register after setting the PRC1 bit in the PRCR register to 1 (write enable). Note also that this register can only be rewritten when timers A1, A2, A4 and B2 are idle.

- 2. A start trigger is generated by writing to the TB2 register only while timer B2 stops.

- 3. The effects of the INV11 bit are described in the table below.

| Item                       | INV11=0                                                                                                              | INV11=1                                          |

|----------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Mode                       | Three-phase mode 0                                                                                                   | Three-phase mode 1                               |

| TA11, TA21, TA41 registers | Not Used                                                                                                             | Used                                             |

| INV00 bit, INV01 bit       | Has no effect. ICTB2 counted every time<br>timer B2 underflows regardless of<br>whether bits INV00 and INV01 are set | Effect                                           |

| INV13 bit                  | Has no effect                                                                                                        | Effective when INV11 bit is 1 and INV06 bit is 0 |

4. If the INV06 bit is 1 (sawtooth wave modulation mode), set this bit to 0 (three-phase mode 0). Also, if the INV11 bit is 0, set the PWCON bit to 0 (timer B2 reloaded by a timer B2 underflow).

5. The INV13 bit is effective only when the INV06 bit is set to 0 (triangular wave modulation mode) and the INV11 bit is set to 1 (three-phase mode 1).

6. If all of the following conditions hold true, set the INV16 bit to 1 (dead time timer triggered by the rising edge of threephase output shift register output)

• The INV15 bit is 0 (dead time timer enabled)

• When the INV03 bit is set to 1 (three-phase motor control timer output enabled), the Dij bit and DiBj bit (i:U, V, or W, j: 0 to 1) have always different values (the positive-phase and negative-phase always output different levels during the period other than dead time).

Conversely, if either one of the above conditions holds false, set the INV16 bit to 0 (dead time timer triggered by the falling edge of one-shot pulse).

Figure 12.27 INVC1 Register

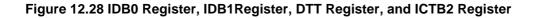

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbol<br>IDB0<br>IDB1 | Address<br>034A16<br>034B16                       | After Reset<br>001111112<br>001111112                                   |    |

|-------------------------|------------------------|---------------------------------------------------|-------------------------------------------------------------------------|----|

|                         | Bit Symbol             | Bit Name                                          | Function                                                                | RW |

|                         | DUi                    | U phase output buffer i                           | Write the output level<br>0: Active level                               | RW |

|                         | DUBi                   | Ū phase output buffer i                           | 1: Inactive level                                                       | RW |

|                         | DVi                    | V phase output buffer i                           | When read, these bits show the three-phase output shift register value. | RW |

|                         | DVBi                   | $\overline{V}$ phase output buffer i              |                                                                         | RW |

|                         | DWi                    | W phase output buffer i                           |                                                                         | RW |

|                         | DWBi                   | $\overline{W}$ phase output buffer i              |                                                                         | RW |

| (b7-b6)                 |                        | Nothing is assigned. If nece these contents are 0 | ssary, set to 0. When read,                                             | RO |

#### NOTE:

1. Registers IDB0 and IDB1 values are transferred to the three-phase shift register by a transfer trigger. The value written to the IDB0 register aftera transfer trigger represents the output signal of each phase, and the next value written to the IDB1 register at the falling edge of the timer A1, A2, or A4 one-shot pulse represents the output signal of each phase.

## Dead Time Timer (1, 2)

| b7 b0 | Symbol<br>DTT                                                     | Address<br>034C16                                                                                                                             | After Re<br>Undefine                                      |               |    |

|-------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|----|

|       |                                                                   | Function                                                                                                                                      |                                                           | Setting Range | RW |

|       | counting the count<br>after counting it n t<br>whichever is going | value = n, upon a start tri,<br>souce selected by the IN<br>imes. The positive or ne<br>from an inactive to an a<br>ne dead time timer stops. | VV12 bit and stops<br>gative phase<br>ctive level changes | 1 to 255      | wo |

#### NOTES:

1. Use MOV instruction to write to this register.

2. Effective when the INV15 bit is set to 0 (dead time timer enable). If the INV15 bit is set to 1, the dead time timer is disabled and has no effect.

#### Timer B2 Interrupt Occurrences Frequency Set Counter

| b7 b6 b5 b4 b3 | -<br>b0 | Symbol<br>ICTB2                                                                                                                        | Address<br>034D16                                                                       | After F<br>Undef                                                                              |                    |    |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------|----|

|                |         |                                                                                                                                        | Function                                                                                |                                                                                               | Setting Range      | RW |

|                |         | time timer B2 unde<br>= n, a timer B2 into<br>occurrence of a tir<br>If the INV01 bit is<br>selected by the IN<br>= n, a timer B2 into | 1 (ICTB2 counter co<br>V00 bit), assuming<br>errupt is generated<br>mer B2 underflow th | the set value<br>at every <i>n</i> th<br>punt timing<br>the set value<br>at every <i>n</i> th | 1 to 15            | WO |

|                |         | Nothing is assigne<br>undefined.                                                                                                       | ed. When write, set                                                                     | to "0". When re                                                                               | ad, the content is |    |

| NOTE           | -       |                                                                                                                                        |                                                                                         |                                                                                               |                    |    |

NOTE

1. Use MOV instruction to write to this register.

If the INV01 bit is set to 1, make sure the TB2S bit also is set to 0 (timer B2 count stopped) when writing to this register. If the INV01 bit is set to 0, although this register can be written even when the TB2S bit is set to 1 (timer B2 count start), do not write synchronously with a timer B2 underflow.

RENESAS

| ') (b                                                                  | 8<br>0)b7                                                                                             | b0                                                                                                                   | G1TM3                                                                                                   | Address<br>to G1TM2 030116-030016,<br>to G1TM5 030716-030616,<br>to G1TM7 030D16-030C16,                                                                                                                                                                            | 030916-030816                                                                                             | 030B16-030A16 Indeter                                                                                                                   | minte<br>minte      |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                                                        |                                                                                                       | Γ                                                                                                                    |                                                                                                         | Function                                                                                                                                                                                                                                                            |                                                                                                           | Setting Range                                                                                                                           | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      |                                                                                                         | e timer value is stored eve<br>ment timing                                                                                                                                                                                                                          | ry                                                                                                        |                                                                                                                                         | RO                  |

|                                                                        |                                                                                                       |                                                                                                                      | Symb<br>G1PC                                                                                            | OCR0 to G1POCR3 03                                                                                                                                                                                                                                                  | ( <b>j=0 to 7</b> )<br>dress<br>1016, 031116, 03<br>1416, 031516, 03                                      | After R<br>31216, 031316 0X00 >                                                                                                         | (X002               |

|                                                                        |                                                                                                       |                                                                                                                      | Bit<br>Symbol                                                                                           | Bit Name                                                                                                                                                                                                                                                            |                                                                                                           | Function                                                                                                                                | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | MOD0                                                                                                    | Operating mode                                                                                                                                                                                                                                                      | 01: SR wav                                                                                                | vaveform output mode<br>eform output mode <sup>(1)</sup>                                                                                | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | MOD1                                                                                                    | select bit                                                                                                                                                                                                                                                          | output r                                                                                                  | delayed waveform<br>node<br>set to this value                                                                                           | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | (b3-b2)                                                                                                 | Nothing is assigned. If I When read, their conten                                                                                                                                                                                                                   |                                                                                                           |                                                                                                                                         | -                   |

|                                                                        |                                                                                                       |                                                                                                                      | IVL                                                                                                     | Output initial value select bit <sup>(4)</sup>                                                                                                                                                                                                                      |                                                                                                           | t as a default value<br>t as a default value                                                                                            | RW                  |

| ·                                                                      |                                                                                                       |                                                                                                                      | RLD                                                                                                     | G1POj register value reload timing select bit                                                                                                                                                                                                                       | value is w<br>1: Reloads t                                                                                | he G1POj register when<br>vritten<br>he G1POj register when<br>timer is reset                                                           | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | (b6)                                                                                                    | Nothing is assigned. If When read, its content i                                                                                                                                                                                                                    |                                                                                                           | t to 0.                                                                                                                                 | -                   |

|                                                                        |                                                                                                       |                                                                                                                      | INV                                                                                                     | Inverse output function select bit <sup>(2)</sup>                                                                                                                                                                                                                   | 0: Output is<br>1: Output is                                                                              | not inversed<br>inversed                                                                                                                | RW                  |

| corr<br>prov<br>2. The<br>to 1<br>prov<br>3. In the<br>char<br>4. To p | s setting<br>respond<br>vide way<br>inverse<br>, and "H<br>vided by<br>he SR v<br>nnel (ne<br>provide | ing odd ch<br>veform out<br>e output fur<br>f" signal is<br>v setting it t<br>vaveform c<br>ext channe<br>either "H" | annel (nex<br>put. Odd<br>nction is th<br>provided<br>to 1.<br>output moo<br>l after the<br>or "L" sign | even channels. In SR way<br>of channel after an even c<br>channels provide no wave<br>le final step in waveform g<br>a default output by setting<br>de, set not only the even c<br>even channel).<br>al output set in the IVL bit<br>inction) and IFEj bit in the 0 | hannel) are ig<br>eform output.<br>generating pro-<br>the IVL bit to<br>channel but als<br>s, set the FSC | nored. Even channels<br>becess. When the INV bit i<br>0, and an "L" signal is<br>so the correspoinding ev<br>j bit in the G1FS register | s set<br>en<br>to 0 |

Figure 13.6 G1TM0 to G1TM7 Registers, and G1POCR0 to G1POCR7 Registers

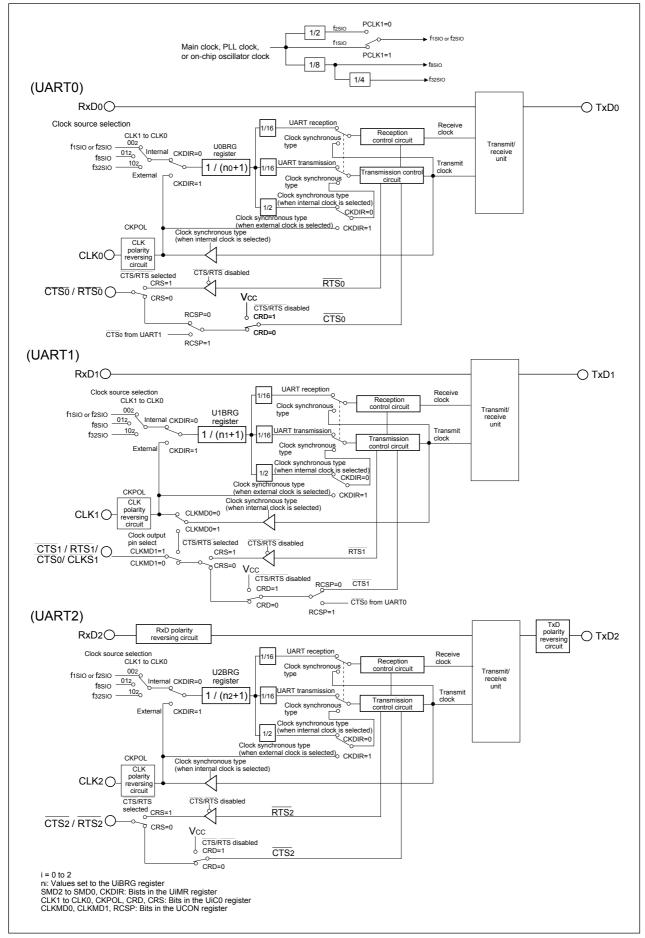

Figure 14.1 Block diagram of UARTi (i = 0 to 2)

RENESAS

## 14.1.1 Clock Synchronous serial I/O Mode

The clock synchronous serial I/O mode uses a transfer clock to transmit and receive data. **Table 14.1** lists the specifications of the clock synchronous serial I/O mode. **Table 14.2** lists the registers used in clock synchronous serial I/O mode and the register values set.

Table 14.1 Clock Synchronous Serial I/O Mode Specifications

| Item                            | Specification                                                                                               |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|

| Transfer data format            | Transfer data length: 8 bits                                                                                |

| Transfer clock                  | • The CKDIR bit in the UiMR(i=0 to 2) register is set to 0 (internal clock) : fj/ (2(n+1))                  |

|                                 | fj = f1SIO, f2SIO, f8SIO, f32SIO. n: Setting value of UiBRG register 0016 to FF16                           |

|                                 | • CKDIR bit is set to 1 (external clock ): Input from CLKi pin                                              |

| Transmission, reception control | Selectable from CTS function, RTS function or CTS/RTS function disable                                      |

| Transmission start condition    | <ul> <li>Before transmission can start, the following requirements must be met <sup>(1)</sup></li> </ul>    |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                        |

|                                 | – The TI bit in the UiC1 register is set to 0 (data present in UiTB register)                               |

|                                 | – If $\overline{\text{CTS}}$ function is selected, input on the $\overline{\text{CTS}}$ i pin is set to "L" |

| Reception start condition       | Before reception can start, the following requirements must be met <sup>(1)</sup>                           |

|                                 | – The RE bit in the UiC1 register is set to 1 (reception enabled)                                           |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                        |

|                                 | - The TI bit in the UiC1 register is set to 0 (data present in the UiTB register)                           |

| Interrupt request               | For transmission, one of the following conditions can be selected                                           |

| generation timing               | – The UiIRS bit <sup>(3)</sup> is set to 0 (transmit buffer empty): when transferring data from the         |

|                                 | UiTB register to the UARTi transmit register (at start of transmission)                                     |

|                                 | - The UiIRS bit is set to 1 (transfer completed): when the serial I/O finished sending                      |

|                                 | data from the UARTi transmit register                                                                       |

|                                 | For reception                                                                                               |

|                                 | When transferring data from the UARTi receive register to the UiRB register (at                             |

|                                 | completion of reception)                                                                                    |

| Error detection                 | Overrun error <sup>(2)</sup>                                                                                |

|                                 | This error occurs if the serial I/O started receiving the next data before reading the                      |

|                                 | UiRB register and received the 7th bit in the the next data                                                 |

| Select function                 | CLK polarity selection                                                                                      |

|                                 | Transfer data input/output can be chosen to occur synchronously with the rising or                          |

|                                 | the falling edge of the transfer clock                                                                      |

|                                 | LSB first, MSB first selection                                                                              |

|                                 | Whether to start sending/receiving data beginning with bit 0 or beginning with bit 7                        |

|                                 | can be selected                                                                                             |

|                                 | Continuous receive mode selection                                                                           |

|                                 | Reception is enabled immediately by reading the UiRB register                                               |

|                                 | Switching serial data logic (UART2)                                                                         |

|                                 | This function reverses the logic value of the transmit/receive data                                         |

|                                 | Transfer clock output from multiple pins selection (UART1)                                                  |

|                                 | The output pin can be selected in a program from two UART1 transfer clock pins that                         |

|                                 | have been set                                                                                               |

|                                 | Separate CTS/RTS pins (UART0)                                                                               |

|                                 | CTS0 and RTS0 are input/output from separate pins                                                           |

|                                 | UART1 pin remapping selection                                                                               |

|                                 | The UART1 pin can be selected from the P67 to P64 or P73 to P70                                             |

| IOTES:                          |                                                                                                             |

1. When an external clock is selected, the conditions must be met while if the CKPOL bit in the UiC0 register is set to 0 (transmit data output at the falling edge and the receive data taken in at the rising edge of the transfer clock), the external clock is in the high state; if the CKPOL bit in the UiC0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the rising edge and the receive data taken in at the set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock), the external clock is in the high state; if the CKPOL bit in the UiC0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock), the external clock is in the low state.

2. If an overrun error occurs, bits 8 to 0 in the UiRB register are undefined. The IR bit in the SiRIC register remains unchanged.

3. The U0IRS and U1IRS bits respectively are the bits 0 and 1 in the UCON register; the U2IRS bit is bit 4 in the U2C1 register.

# 14.1.2 Clock Asynchronous Serial I/O (UART) Mode

The UART mode allows transmitting and receiving data after setting the desired bit rate and transfer data format. **Table 14.5** lists the specifications of the UART mode.

| Item                            | Specification                                                                                                 |

|---------------------------------|---------------------------------------------------------------------------------------------------------------|

| Transfer data format            | <ul> <li>Character bit (transfer data): Selectable from 7, 8 or 9 bits</li> </ul>                             |

|                                 | Start bit: 1 bit                                                                                              |

|                                 | <ul> <li>Parity bit: Selectable from odd, even, or none</li> </ul>                                            |

|                                 | Stop bit: Selectable from 1 or 2 bits                                                                         |

| Transfer clock                  | <ul> <li>The CKDIR bit in the UiMR(i=0 to 2) register is set to 0 (internal clock) : fj/ (16(n+1))</li> </ul> |

|                                 | fj = f1SIO, f2SIO, f8SIO, f32SIO. n: Setting value of UiBRG register 0016 to FF16                             |

|                                 | <ul> <li>CKDIR bit is set to 1 (external clock ): fEXT/16(n+1)</li> </ul>                                     |

|                                 | fEXT: Input from CLKi pin. n :Setting value of UiBRG register 0016 to FF16                                    |

| Transmission, reception control | <ul> <li>Selectable from CTS function, RTS function or CTS/RTS function disable</li> </ul>                    |

| Transmission start condition    | <ul> <li>Before transmission can start, the following requirements must be met</li> </ul>                     |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                          |

|                                 | <ul> <li>The TI bit in the UiC1 register is set to 0 (data present in UiTB register)</li> </ul>               |

|                                 | – If $\overline{CTS}$ function is selected, input on the $\overline{CTS}$ i pin is set to "L"                 |

| Reception start condition       | <ul> <li>Before reception can start, the following requirements must be met"</li> </ul>                       |

|                                 | <ul> <li>The RE bit in the UiC1 register is set to 1 (reception enabled)</li> </ul>                           |

|                                 | - Start bit detection                                                                                         |

|                                 | <ul> <li>For transmission, one of the following conditions can be selected</li> </ul>                         |

| Interrupt request               | – The UiIRS bit <sup>(2)</sup> is set to 0 (transmit buffer empty): when transferring data from the           |

| generation timing               | UiTB register to the UARTi transmit register (at start of transmission)                                       |

| 5                               | – The UiIRS bit is set to1 (transfer completed): when the serial I/O finished sending                         |

|                                 | data from the UARTi transmit register                                                                         |

|                                 | For reception                                                                                                 |

|                                 | When transferring data from the UARTi receive register to the UiRB register (at                               |

|                                 | completion of reception)                                                                                      |

| Error detection                 | Overrun error <sup>(1)</sup>                                                                                  |

|                                 | This error occurs if the serial I/O started receiving the next data before reading the                        |

|                                 | UiRB register and received the bit one before the last stop bit in the the next data                          |

|                                 | Framing error                                                                                                 |

|                                 | This error occurs when the number of stop bits set is not detected                                            |

|                                 | Parity error                                                                                                  |

|                                 | This error occurs when if parity is enabled, the number of 1 in parity and                                    |

|                                 | character bits does not match the number of 1 set                                                             |

|                                 | Error sum flag                                                                                                |

|                                 | This flag is set to 1 when any of the overrun, framing, and parity errors is encountered                      |

| Select function                 | LSB first, MSB first selection                                                                                |

|                                 | Whether to start sending/receiving data beginning with bit 0 or beginning with bit 7                          |

|                                 | can be selected                                                                                               |

|                                 | Serial data logic switch (UART2)                                                                              |

|                                 | This function reverses the logic of the transmit/receive data. The start and stop bits                        |

|                                 | are not reversed.                                                                                             |

|                                 | TxD, RxD I/O polarity switch (UART2)                                                                          |

|                                 | This function reverses the polarities of hte TxD pin output and RxD pin input. The                            |

|                                 | logic levels of all I/O data is reversed.                                                                     |

|                                 | Separate CTS/RTS pins (UART0)                                                                                 |

|                                 | CTS0 and RTS0 are input/output from separate pins                                                             |

|                                 | • UART1 pin remapping selection                                                                               |

|                                 |                                                                                                               |

Table 14.5 UART Mode Specifications

NOTES:

1. If an overrun error occurs, bits 8 to 0 in the UiRB register are undefined. The IR bit in the SiRIC register remains unchange.

2. Bits U0IRS and U1IRS respectively are the UCON register bits 0 and 1; the U2IRS bit is the U2C1 register bit 4.

#### Table 14.6 Registers to Be Used and Settings in UART Mode

| Register | Bit                  | Function                                                                                        |  |  |  |  |

|----------|----------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| UiTB     | 0 to 8               | Set transmission data <sup>(1)</sup>                                                            |  |  |  |  |

| UiRB     | 0 to 8               | Reception data can be read <sup>(1)</sup>                                                       |  |  |  |  |

|          | OER,FER,PER,SUM      | Error flag                                                                                      |  |  |  |  |

| UiBRG    | 0 to 7               | Set bit rate                                                                                    |  |  |  |  |

| UiMR     | SMD2 to SMD0         | Set these bits to 1002 when transfer data is 7 bits long                                        |  |  |  |  |

|          |                      | Set these bits to 1012 when transfer data is 8 bits long                                        |  |  |  |  |

|          |                      | Set these bits to 1102 when transfer data is 9 bits long                                        |  |  |  |  |

|          | CKDIR                | Select the internal clock or external clock                                                     |  |  |  |  |

|          | STPS                 | Select the stop bit                                                                             |  |  |  |  |

|          | PRY, PRYE            | Select whether parity is included and whether odd or even                                       |  |  |  |  |

|          | IOPOL(i=2) (4)       | Select the TxD/RxD input/output polarity                                                        |  |  |  |  |

| UiC0     | CLK0, CLK1           | Select the count source for the UiBRG register                                                  |  |  |  |  |

|          | CRS                  | Select CTS or RTS to use                                                                        |  |  |  |  |

|          | TXEPT                | Transmit register empty flag                                                                    |  |  |  |  |

|          | CRD                  | Enable or disable the $\overline{\text{CTS}}$ or $\overline{\text{RTS}}$ function               |  |  |  |  |

|          | NCH                  | Select TxDi pin output mode                                                                     |  |  |  |  |

|          | CKPOL                | Set to 0                                                                                        |  |  |  |  |

|          | UFORM                | FORM LSB first or MSB first can be selected when transfer data is 8 bits long. Se               |  |  |  |  |

|          |                      | bit to 0 when transfer data is 7 or 9 bits long.                                                |  |  |  |  |

| UiC1     | TE                   | Set this bit to 1 to enable transmission                                                        |  |  |  |  |

|          | TI                   | Transmit buffer empty flag                                                                      |  |  |  |  |

|          | RE                   | Set this bit to 1 to enable reception                                                           |  |  |  |  |

|          | RI                   | Reception complete flag                                                                         |  |  |  |  |

|          | U2IRS <sup>(2)</sup> | Select the source of UART2 transmit interrupt                                                   |  |  |  |  |

|          | U2RRM <sup>(2)</sup> | Set to 0                                                                                        |  |  |  |  |

|          | UiLCH <sup>(3)</sup> | Set this bit to 1 to use UART2 inverted data logic                                              |  |  |  |  |

|          | UiERE <sup>(3)</sup> | Set to 0                                                                                        |  |  |  |  |

| UiSMR    | 0 to 7               | Set to 0                                                                                        |  |  |  |  |

| UiSMR2   | 0 to 7               | Set to 0                                                                                        |  |  |  |  |

| UiSMR3   | 0 to 7               | Set to 0                                                                                        |  |  |  |  |

| UiSMR4   | 0 to 7               | Set to 0                                                                                        |  |  |  |  |

| UCON     | U0IRS, U1IRS         | Select the source of UART0/UART1 transmit interrupt                                             |  |  |  |  |

|          | U0RRM, U1RRM         | Set to 0                                                                                        |  |  |  |  |

|          | CLKMD0               | Invalid because CLKMD1 is set to 0                                                              |  |  |  |  |

|          | CLKMD1               | Set to 0                                                                                        |  |  |  |  |

|          | RCSP                 | Set this bit to 1 to accept as input the UART0 $\overline{\text{CTS0}}$ signal from the P64 pin |  |  |  |  |

|          | 7                    | Set to 0                                                                                        |  |  |  |  |

NOTES:

- 1. The bits used for transmit/receive data are as follows: Bit 0 to bit 6 when transfer data is 7 bits long; bits 7 to 0 when transfer data is 8 bits long; bit 0 to bit 8 when transfer data is 9 bits long.

- 2. Set bits 5 and 4 in registers U0C1 and U1C1 to 0. Bits U0IRS, U1IRS, U0RRM and U1RRM are included in the UCON register.

- 3. Set bits 7 and 6 in registers U0C1 and U1C1 to 0.

- 4. Set the bit 7 in registers U0MR and U1MR to 0.

i=0 to 2

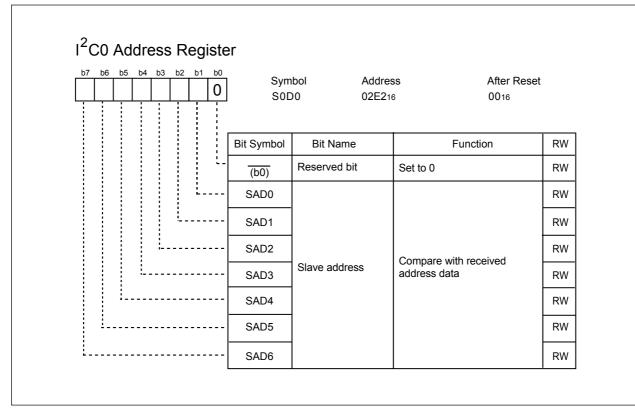

Figure 16.2 S0D0 Register

# 16.7 I<sup>2</sup>C0 Control Register 2 (S4D0 Register)

The S4D0 register controls the error communication detection.

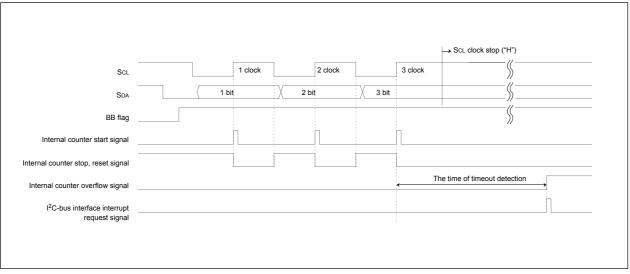

If the SCL clock is stopped counting dring data transfer, each device is stopped, staying online. To avoid the situation, the  $I^2C$  bus interface circuit has a function to detect the time-out when the SCL clock is stopped in high-level ("H") state for a specific period, and to generate an  $I^2C$  bus interface interrupt request. See **Figure 16.13**.

Figure 16.13 The timing of time-out detection

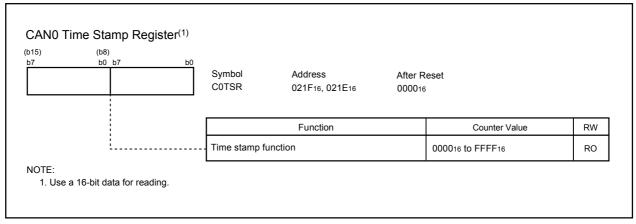

## 17.1.3.10 C0TSR Register

Figure 17.15 shows the C0TSR register.

### Figure 17.15 C0TSR Register

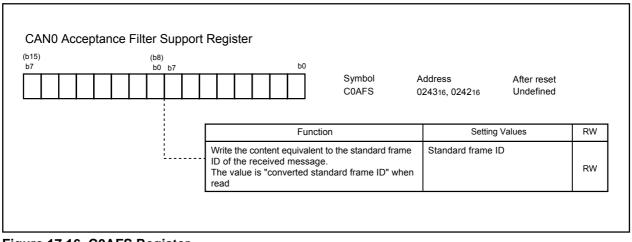

### 17.1.3.11 COAFS Register

Figure 17.16 shows the COAFS register.

Figure 17.16 C0AFS Register

# 20.10 Parallel I/O Mode

In parallel input/output mode, the user ROM can be rewritten by a parallel programmer supporting the M16C/29 group. Contact your parallel programmer manufacturer for more information on the parallel programmer. Refer to the user's manual included with your parallel programmer for instructions.

# 20.10.1 ROM Code Protect Function

The ROM code protect function prevents the flash memory from being read or rewritten. (Refer to **20.3 Functions To Prevent Flash Memory from Rewriting**).

## **Timing Requirements**

# Vcc = 5V

# (VCC = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 21.17 | Timer B Input (Counter Input in Event Counter Mode) |

|-------------|-----------------------------------------------------|

|-------------|-----------------------------------------------------|

| Symbol  | Parameter                                           | Standard | Unit |      |

|---------|-----------------------------------------------------|----------|------|------|

| Symbol  | Parameter                                           | Min.     | Max. | Unit |

| tc(TB)  | TBin input cycle time (counted on one edge)         | 100      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on one edge)   | 40       |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on one edge)    | 40       |      | ns   |

| tc(TB)  | TBin input cycle time (counted on both edges)       | 200      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on both edges) | 80       |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on both edges)  | 80       |      | ns   |

# Table 21.18 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Stan | dard | Unit |