Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                              |

| Number of I/O              | 71                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 27x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-LQFP                                                                         |

| Supplier Device Package    | 80-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30290fchp-u3a |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# RENESAS

M16C/29 Group SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

# 1. Overview

## 1.1 Features

The M16C/29 Group of single-chip control MCU incorporates the M16C/60 series CPU core, employing the high-performance silicon gate CMOS technology and sophisticated instructions for a high level of efficiency. The M16C/29 Group is housed in 64-pin and 80-pin plastic molded LQFP packages. These single-chip MCUs operate using sophisticated instructions featuring a high level of instruction efficiency. This MCU is capable of executing instructions at high speed and it has one CAN module, makes it suitable for control of cars and LAN system of FA. In addition, the CPU core boasts a multiplier and DMAC for high-speed processing to make adequate for office automation, communication devices, and other high-speed processing applications.

## 1.1.1 Applications

Automotive body, car audio, LAN system of FA, etc.

As of March. 2007

#### **1.3 Product List**

Tables 1.3 to 1.5 list the M16C/29 Group products and Figure 1.3 shows the type numbers, memory sizes and packages. Tables 1.6 to 1.8 list the product code of flash memory version for M16C/29 Group. Figure 1.4 to Figure 1.6 show the marking diagram of flash memory version for M16C/29 Group.

|                |                 |                 |                        |         | ai 011, 2007    |

|----------------|-----------------|-----------------|------------------------|---------|-----------------|

| Type Number    | ROM<br>Capacity | RAM<br>Capacity | Package Type           | Remarks | Product<br>Code |

| M30290FAHP     | 96 K + 4 K      | 8 K             | PLQP0080KB-A (80P6Q-A) |         |                 |

| M30290FCHP     | 128 K + 4 K     | 12 K            |                        | Flash   | U3, U5,         |

| M30291FAHP     | 96 K + 4 K      | 8 K             | PLQP0064KB-A (64P6Q-A) | Memory  | U7, U9          |

| M30291FCHP     | 128 K + 4 K     | 12 K            | FLQF0004KB-A (04F0Q-A) |         |                 |

| M30290M8-XXXHP | 64 K            | 4 K             |                        |         |                 |

| M30290MA-XXXHP | 96 K            | 8 K             | PLQP0080KB-A (80P6Q-A) |         |                 |

| M30290MC-XXXHP | 128 K           | 12 K            |                        | Mask    | U3, U5          |

| M30291M8-XXXHP | 64 K            | 4 K             |                        | ROM     | 03, 05          |

| M30291MA-XXXHP | 96 K            | 8 K             | PLQP0064KB-A (64P6Q-A) |         |                 |

| M30291MC-XXXHP | 128 K           | 12 K            |                        |         |                 |

#### Table 1.3 Product List (1) -Normal Version

#### Table 1.4 Product List (2) -T Version

| Table 1.4 Product List (2) |                 | As of M         | arch, 2007               |         |                 |

|----------------------------|-----------------|-----------------|--------------------------|---------|-----------------|

| Type Number                | ROM<br>Capacity | RAM<br>Capacity | Package Type             | Remarks | Product<br>Code |

| M30290FATHP                | 96 K + 4 K      | 8 K             | PLQP0080KB-A (80P6Q-A)   |         |                 |

| M30290FCTHP                | 128 K + 4 K     | 12 K            |                          | Flash   | U3, U5,         |

| M30291FATHP                | 96 K + 4 K      | 8 K             |                          | Memory  | U7, U9          |

| M30291FCTHP                | 128 K + 4 K     | 12 K            | - PLQP0064KB-A (64P6Q-A) |         |                 |

| M30290M8T-XXXHP            | 64 K            | 4 K             |                          |         |                 |

| M30290MAT-XXXHP            | 96 K            | 8 K             | PLQP0080KB-A (80P6Q-A)   |         |                 |

| M30290MCT-XXXHP            | 128 K           | 12 K            |                          | Mask    | UO              |

| M30291M8T-XXXHP            | 64 K            | 4 K             |                          | ROM     | 00              |

| M30291MAT-XXXHP            | 96 K            | 8 K             | PLQP0064KB-A (64P6Q-A)   |         |                 |

| M30291MCT-XXXHP            | 128 K           | 12 K            | 1                        |         |                 |

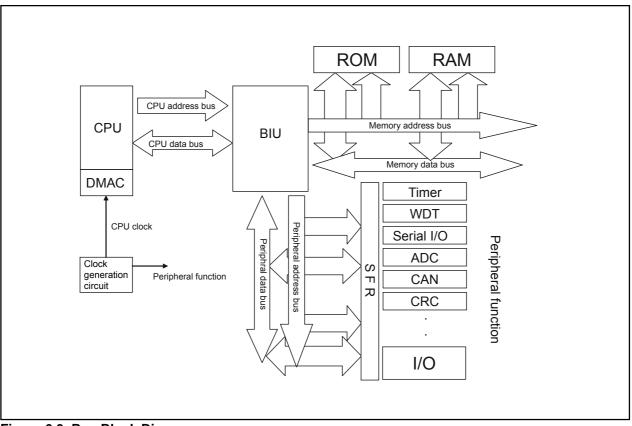

The internal bus consists of CPU bus, memory bus, and peripheral bus. Bus Interface Unit (BIU) is used to interfere with CPU, ROM/RAM, and perpheral functions by controling CPU bus, memory bus, and peripheral bus. **Figure 6.3** shows the block diagram of the internal bus.

Figure 6.3 Bus Block Diagram

The number of bus cycle varies by the internal bus. Table 6.1 lists the accessible area and bus cycle.

| Table 6.1 Ac | cessible Area | and Bus | Cycle |

|--------------|---------------|---------|-------|

|--------------|---------------|---------|-------|

|         | Accessible Area        | Bus Cycle          |

|---------|------------------------|--------------------|

| SFR     | PM20 bit = 0 (2 waits) | 3 CPU clock cycles |

|         | PM20 bit = 1 (1 wait)  | 2 CPU clock cycles |

| ROM/RAM | PM17 bit = 0 (no wait) | 1 CPU clock cycle  |

|         | PM17 bit = 1 (1 wait)  | 2 CPU clock cycles |

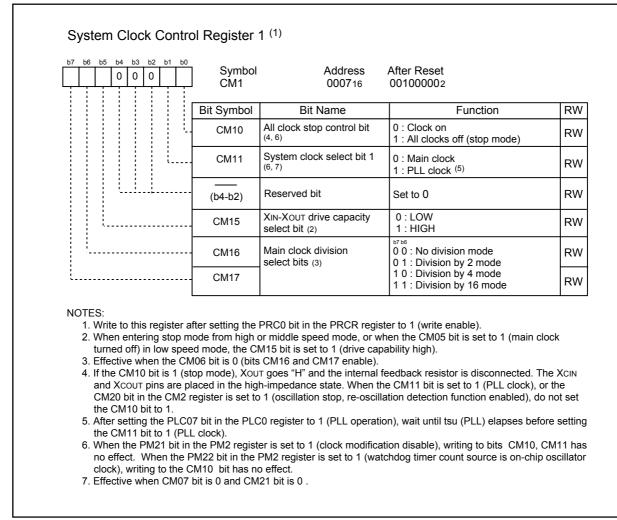

Figure 7.3 CM1 Register

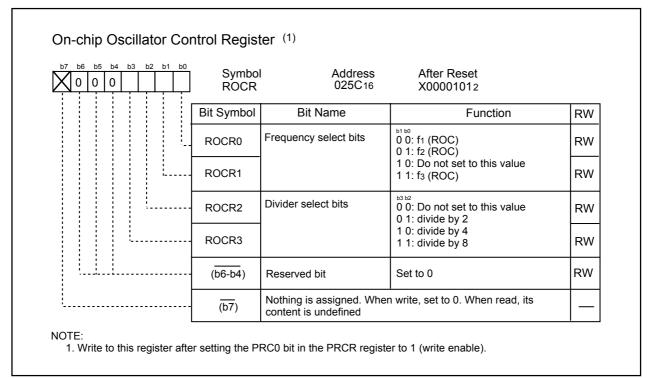

Figure 7.4 ROCR Register

## 12.2 Timer B

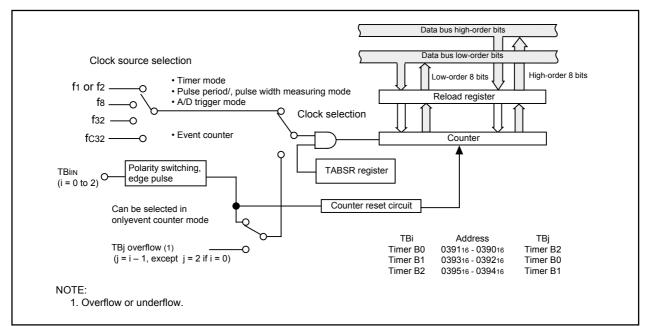

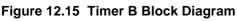

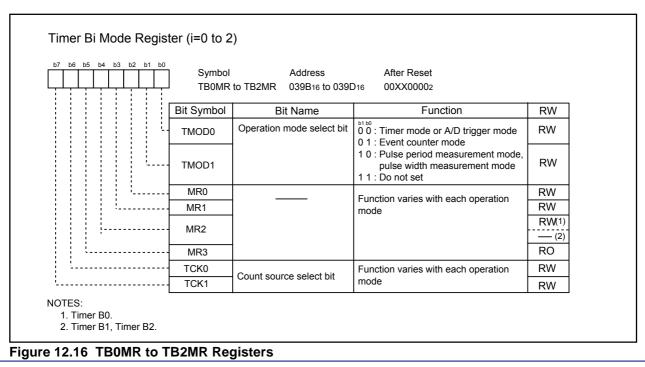

Figure 12.15 shows a block diagram of the timer B. Figures 12.16 and 12.17 show registers related to the timer B.

Timer B supports the following four modes. Use bits TMOD1 and TMOD0 in the TBiMR register (i = 0 to 2) to select the desired mode.

- Timer mode: The timer counts the internal count source.

- Event counter mode: The timer counts the external pulses or overflows and underflows of other timers.

- Pulse period/pulse width measurement mode: The timer measures the pulse period or pulse width of external signal.

- A/D trigger mode: The timer starts counting by one trigger until the count value becomes 000016. This mode is used together with simultaneous sample sweep mode or delayed trigger mode 0 of A/D converter to start A/D conversion.

RENESAS

| b6 b5 b4 b3 b2 b1 b0                  | Symb<br>G1IE                                                   |                                                                                                                                                                                   | After Reset<br>00 <sub>16</sub>                                               |                            |

|---------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------|

|                                       | Bit<br>Symbol                                                  | Bit Name                                                                                                                                                                          | Function                                                                      | RV                         |

|                                       | G1IE00                                                         | Interrupt enable 0, CH0                                                                                                                                                           | 0 : IC/OC interrupt 0 request disable<br>1 : IC/OC interrupt 0 request enable | RV                         |

| · · · · · · · · · · · · · · · · · · · | G1IE01                                                         | Interrupt enable 0, CH1                                                                                                                                                           |                                                                               | RV                         |

| L                                     | G1IE02                                                         | Interrupt enable 0, CH2                                                                                                                                                           |                                                                               | RV                         |

|                                       | G1IE03                                                         | Interrupt enable 0, CH3                                                                                                                                                           |                                                                               | RV                         |

|                                       | G1IE04                                                         | Interrupt enable 0, CH4                                                                                                                                                           |                                                                               | RV                         |

| L                                     | G1IE05                                                         | Interrupt enable 0, CH5                                                                                                                                                           |                                                                               | RV                         |

| L                                     | G1IE06                                                         | Interrupt enable 0, CH6                                                                                                                                                           |                                                                               | RV                         |

|                                       |                                                                |                                                                                                                                                                                   |                                                                               |                            |

| terrupt Enable R                      | G1IE07                                                         | Interrupt enable 0, CH7                                                                                                                                                           |                                                                               | RV                         |

| terrupt Enable R                      |                                                                | r 1<br>pol Address                                                                                                                                                                | After Reset<br>0016                                                           | RV                         |

|                                       | egiste                                                         | r 1<br>pol Address                                                                                                                                                                |                                                                               | RV                         |

|                                       | Symt<br>G1IE                                                   | <b>r 1</b><br>pol Address<br>1 033216                                                                                                                                             | 0016                                                                          | RW                         |

|                                       | Symt<br>G1IE<br>Symbol                                         | r 1<br>pol Address<br>1 033216<br>Bit Name                                                                                                                                        | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     |                            |

|                                       | Symt<br>G1IE<br>Symbol<br>G1IE10                               | r 1<br>pol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0                                                                                                             | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RW<br>RV<br>RV             |

|                                       | Symt<br>G1IE<br>Symbol<br>G1IE10<br>G1IE11                     | r 1<br>pol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1                                                                                  | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RW                         |

|                                       | Symbol<br>G1IE10<br>G1IE11<br>G1IE12                           | r 1<br>pol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1<br>Interrupt enable 1, CH2                                                       | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RV<br>RV<br>RV<br>RV       |

|                                       | Symb<br>G1IE<br>Symbol<br>G1IE10<br>G1IE11<br>G1IE12<br>G1IE13 | r 1<br>bol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1<br>Interrupt enable 1, CH2<br>Interrupt enable 1, CH3                            | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RW<br>RV<br>RV<br>RV<br>RV |

|                                       | Symbol<br>G1IE10<br>G1IE11<br>G1IE12<br>G1IE13<br>G1IE14       | r 1<br>Dol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1<br>Interrupt enable 1, CH2<br>Interrupt enable 1, CH3<br>Interrupt enable 1, CH3 | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RV<br>RV<br>RV             |

Figure 13.10 G1IE0 and G1IE1 Registers

## **13.4 Time Measurement Function**

In synchronization with an external trigger input, the value of the base timer is stored into the G1TMj register (j=0 to 7). **Table 13.5** shows specifications of the time measurement function. **Table 13.6** shows register settings associated with the time measurement function. **Figures 13.19** and **13.20** display operational timing of the time measurement function. **Figure 13.21** shows operational timing of the prescaler function.

| Item                                | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement channel                 | Channels 0 to 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Selecting trigger input polarity    | Rising edge, falling edge, both edges of the INPC1j pin $^{(1)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Measurement start condition         | The IFEj bit in the G1FE register should be set to 1 (channels j function enabled) when the FSCj bit (j=0 to 7) in the G1FS register is set to 1 (time measurement function selected).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Measurement stop condition          | The IFEj bit should be set to 0 (channel j function disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Time measurement timing             | •No prescaler : every time a trigger signal is applied<br>•Prescaler (for channel 6 and channel 7):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                     | every <i>G1TPRk (k=6,7) register value +1</i> times a trigger signal is applied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt request generation timing | The G1IRi bit (i=0 to 7) in the interrupt request register (See Figure 13.9) is set to 1 at time measurement timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INPC1j pin function <sup>(1)</sup>  | Trigger input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Selectable function                 | <ul> <li>Digital filter function The digital filter samples a trigger input signal level every f1, f2 or fBT1 cycles and passes pulse signal matching trigger input signal level three times </li> <li>Prescaler function (for channel 6 and channel 7) Time measurement is executed every <i>G1TPRk register value +1</i> times a trigger signal is applied </li> <li>Cate function (for channel 6 and channel 7)</li> </ul>                                                                                                                                                                                  |

|                                     | <ul> <li>Gate function (for channel 6 and channel 7)<br/>After time measurement by the first trigger input, trigger input cannot be<br/>accepted. However, while the GOC bit in the G1TMCRk register is set to 1<br/>(gate cleared by matching the base timer with the G1POp register (p=4<br/>when k=6, p=5 when k=7)), trigger input can be accepted again by<br/>matching the base timer value with the G1POp register setting</li> <li>Digital Debounce function (for channel7)<br/>See 13.6.2 Digital Debounce Function for P17/INT5/INPC17 and 19.6<br/>Digital Debounce Function for details</li> </ul> |

| Table 13.5 Time | Measurement | Function | Specifications |

|-----------------|-------------|----------|----------------|

|                 |             |          |                |

NOTE:

1. The INPC10 to INPC17 pins

|              | b5 b                    | 04 b3         | b2 b  | b1 b0                      |                                                                                        |                                                                                                                                                                                                                                                                                                                               | dress After Reset<br>716 X0000002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

|--------------|-------------------------|---------------|-------|----------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|              |                         |               |       |                            | Bit<br>Symbol                                                                          | Bit Name                                                                                                                                                                                                                                                                                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R\                                                 |

|              |                         |               |       |                            | IICM                                                                                   | I <sup>2</sup> C bus mode select bit                                                                                                                                                                                                                                                                                          | 0 : Other than I <sup>2</sup> C bus mode<br>1 : I <sup>2</sup> C bus mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                  |

|              |                         |               |       |                            | ABC                                                                                    | Arbitration lost detecting flag control bit                                                                                                                                                                                                                                                                                   | 0 : Update per bit<br>1 : Update per byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R\                                                 |

|              |                         |               |       |                            | BBS                                                                                    | Bus busy flag                                                                                                                                                                                                                                                                                                                 | 0 : STOP condition detected<br>1 : START condition detected (busy)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RV                                                 |

|              |                         |               |       |                            | (b3)                                                                                   | Reserved bit                                                                                                                                                                                                                                                                                                                  | Set to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RV                                                 |

|              |                         |               |       | · ,                        | ABSCS                                                                                  | Bus collision detect sampling clock select bit                                                                                                                                                                                                                                                                                | 0 : Rising edge of transfer clock<br>1 : Underflow signal of timer A0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RV                                                 |

|              |                         |               |       |                            | ACSE                                                                                   | Auto clear function<br>select bit of transmit<br>enable bit                                                                                                                                                                                                                                                                   | 0 : No auto clear function<br>1 : Auto clear at occurrence of bus collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RV                                                 |

|              |                         |               |       |                            | SSS                                                                                    | Transmit start condition select bit                                                                                                                                                                                                                                                                                           | 0 : Not synchronized to RxD2<br>1 : Synchronized to RxD2 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RV                                                 |

|              |                         |               |       |                            |                                                                                        | Nothing is assigned. If p                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

| 2: W         | The BB<br>When a<br>RT2 | a tran<br>Spe | ecial | egins, <sup>5</sup><br>Mod | the SSS t                                                                              | ) by program. (Writing 1 ha                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe | ecial | egins,                     | writing 0<br>the SSS t                                                                 | ) by program. (Writing 1 ha                                                                                                                                                                                                                                                                                                   | is no effect).<br>ized to RxD2).<br>s After Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe | ecial | egins, <sup>5</sup><br>Mod | writing 0<br>the SSS t                                                                 | by program. (Writing 1 ha<br>bit is set to 0 (Not synchron<br>ister 2<br>Symbol Addres<br>J2SMR2 037616<br>Bit Name                                                                                                                                                                                                           | is no effect).<br>ized to RxD2).<br>s After Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RW                                                 |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe | ecial | egins, <sup>5</sup><br>Mod | / writing 0<br>the SSS t<br>e Regi                                                     | by program. (Writing 1 ha<br>bit is set to 0 (Not synchron<br>ister 2<br>Symbol Addres<br>J2SMR2 037616<br>Bit Name                                                                                                                                                                                                           | is no effect).<br>ized to RxD2).<br>s After Reset<br>X00000002<br>Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe | ecial | egins, <sup>5</sup><br>Mod | e Regi                                                                                 | ) by program. (Writing 1 ha<br>bit is set to 0 (Not synchron<br>ister 2<br>Symbol Addres<br>J2SMR2 037616                                                                                                                                                                                                                     | s no effect).<br>ized to RxD2).<br>s After Reset<br>X00000002<br>Function<br>it 2 Refer to Table 14.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RV                                                 |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe |       | egins, <sup>5</sup><br>Mod | y writing 0<br>the SSS to<br>e Regi<br>]                                               | ) by program. (Writing 1 ha<br>bit is set to 0 (Not synchron<br>ister 2<br>Symbol Addres<br>J2SMR2 037616<br>Bit Name<br>I <sup>12</sup> C bus mode select b                                                                                                                                                                  | is no effect).<br>ized to RxD2).<br>s After Reset<br>X00000002<br>Function<br>it 2 Refer to Table 14.13<br>0 : Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RW                                                 |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe |       | Mod                        | writing 0<br>the SSS t<br>e Regi<br>]<br>Bit<br>Symbo<br>IICM2<br>CSC                  | b by program. (Writing 1 ha<br>bit is set to 0 (Not synchron<br>ister 2<br>Symbol Addres<br>J2SMR2 037616<br>Bit Name<br>I <sup>2</sup> C bus mode select to<br>Clock-synchronous bit                                                                                                                                         | s no effect).<br>ized to RxD2).<br>s After Reset<br>X00000002<br>Function<br>it 2 Refer to Table 14.13<br>0 : Disabled<br>1 : Enabled<br>0 : Disabled<br>0 : Disabled                                                                                                                                                                                                                                                                                                                                                                                                                   | RW<br>RW                                           |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe |       | Mod                        | writing 0<br>the SSS t<br>e Regi<br>]<br>Bit<br>Symbo<br>IICM2<br>CSC<br>SWC           | by program. (Writing 1 ha         bit is set to 0 (Not synchron         ister 2         Symbol       Addres         J2SMR2       037616         I       Bit Name         I <sup>2</sup> C bus mode select b         Clock-synchronous bit         SCL2 wait output bit                                                        | s no effect).<br>ized to RxD2).<br>s After Reset<br>X00000002<br>Function<br>it 2 Refer to Table 14.13<br>0 : Disabled<br>1 : Enabled<br>0 : Disabled<br>1 : Enabled<br>0 : Disabled<br>1 : Enabled<br>0 : Disabled<br>1 : Enabled<br>0 : Disabled<br>1 : Enabled                                                                                                                                                                                                                                                                                                                       | RW<br>RW<br>RW                                     |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe |       | Mod                        | writing 0<br>the SSS b<br>e Regi<br>Bit<br>Symbo<br>IICM2<br>CSC<br>SWC<br>ALS         | by program. (Writing 1 happit is set to 0 (Not synchron         ister 2         Symbol       Addres         J2SMR2       037616         I       Bit Name         I <sup>2</sup> C bus mode select b         Clock-synchronous bit         SCL2 wait output bit         UART initialization bit         SCL2 wait output bit 2 | s no effect).<br>ized to RxD2).<br>s After Reset<br>X00000002<br>Function<br>it 2 Refer to Table 14.13<br>0 : Disabled<br>1 : Enabled<br>0 : Disabled<br>1 : Enabled | RW<br>RW<br>RW<br>RW<br>RW                         |

| 1: T<br>2: W | The BB<br>When a<br>RT2 | a tran<br>Spe |       | Mod                        | writing 0<br>the SSS t<br>e Regi<br>Bit<br>Symbo<br>IICM2<br>CSC<br>SWC<br>ALS<br>STAC | b) by program. (Writing 1 ha<br>bit is set to 0 (Not synchron<br>ister 2<br>Symbol Addres<br>J2SMR2 037616<br>I Bit Name<br>I <sup>2</sup> C bus mode select b<br>Clock-synchronous bit<br>SCL2 wait output bit<br>SDA2 output stop bit<br>UART initialization bit                                                            | s no effect).<br>ized to RxD2).<br>s After Reset<br>X00000002<br>Function<br>it 2 Refer to Table 14.13<br>0 : Disabled<br>1 : Enabled<br>0 : Disabled<br>1 : Enabled | RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW |

#### 14.1.1 Clock Synchronous serial I/O Mode

The clock synchronous serial I/O mode uses a transfer clock to transmit and receive data. **Table 14.1** lists the specifications of the clock synchronous serial I/O mode. **Table 14.2** lists the registers used in clock synchronous serial I/O mode and the register values set.

Table 14.1 Clock Synchronous Serial I/O Mode Specifications

| Item                            | Specification                                                                                               |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|

| Transfer data format            | Transfer data length: 8 bits                                                                                |

| Transfer clock                  | • The CKDIR bit in the UiMR(i=0 to 2) register is set to 0 (internal clock) : fj/ (2(n+1))                  |

|                                 | fj = f1SIO, f2SIO, f8SIO, f32SIO. n: Setting value of UiBRG register 0016 to FF16                           |

|                                 | • CKDIR bit is set to 1 (external clock ): Input from CLKi pin                                              |

| Transmission, reception control | Selectable from CTS function, RTS function or CTS/RTS function disable                                      |

| Transmission start condition    | <ul> <li>Before transmission can start, the following requirements must be met <sup>(1)</sup></li> </ul>    |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                        |

|                                 | – The TI bit in the UiC1 register is set to 0 (data present in UiTB register)                               |

|                                 | – If $\overline{\text{CTS}}$ function is selected, input on the $\overline{\text{CTS}}$ i pin is set to "L" |

| Reception start condition       | Before reception can start, the following requirements must be met <sup>(1)</sup>                           |

|                                 | – The RE bit in the UiC1 register is set to 1 (reception enabled)                                           |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                        |

|                                 | - The TI bit in the UiC1 register is set to 0 (data present in the UiTB register)                           |

| Interrupt request               | For transmission, one of the following conditions can be selected                                           |

| generation timing               | – The UiIRS bit <sup>(3)</sup> is set to 0 (transmit buffer empty): when transferring data from the         |

|                                 | UiTB register to the UARTi transmit register (at start of transmission)                                     |

|                                 | - The UiIRS bit is set to 1 (transfer completed): when the serial I/O finished sending                      |

|                                 | data from the UARTi transmit register                                                                       |

|                                 | For reception                                                                                               |

|                                 | When transferring data from the UARTi receive register to the UiRB register (at                             |

|                                 | completion of reception)                                                                                    |

| Error detection                 | Overrun error <sup>(2)</sup>                                                                                |

|                                 | This error occurs if the serial I/O started receiving the next data before reading the                      |

|                                 | UiRB register and received the 7th bit in the the next data                                                 |

| Select function                 | CLK polarity selection                                                                                      |

|                                 | Transfer data input/output can be chosen to occur synchronously with the rising or                          |

|                                 | the falling edge of the transfer clock                                                                      |

|                                 | LSB first, MSB first selection                                                                              |

|                                 | Whether to start sending/receiving data beginning with bit 0 or beginning with bit 7                        |

|                                 | can be selected                                                                                             |

|                                 | Continuous receive mode selection                                                                           |

|                                 | Reception is enabled immediately by reading the UiRB register                                               |

|                                 | Switching serial data logic (UART2)                                                                         |

|                                 | This function reverses the logic value of the transmit/receive data                                         |

|                                 | Transfer clock output from multiple pins selection (UART1)                                                  |

|                                 | The output pin can be selected in a program from two UART1 transfer clock pins that                         |

|                                 | have been set                                                                                               |

|                                 | Separate CTS/RTS pins (UART0)                                                                               |

|                                 | CTS0 and RTS0 are input/output from separate pins                                                           |

|                                 | UART1 pin remapping selection                                                                               |

|                                 | The UART1 pin can be selected from the P67 to P64 or P73 to P70                                             |

| IOTES:                          |                                                                                                             |

1. When an external clock is selected, the conditions must be met while if the CKPOL bit in the UiC0 register is set to 0 (transmit data output at the falling edge and the receive data taken in at the rising edge of the transfer clock), the external clock is in the high state; if the CKPOL bit in the UiC0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the rising edge and the receive data taken in at the set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock), the external clock is in the high state; if the CKPOL bit in the UiC0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock), the external clock is in the low state.

2. If an overrun error occurs, bits 8 to 0 in the UiRB register are undefined. The IR bit in the SiRIC register remains unchanged.

3. The U0IRS and U1IRS bits respectively are the bits 0 and 1 in the UCON register; the U2IRS bit is bit 4 in the U2C1 register.

| Register            | Bit                  | Function                                                                                        |

|---------------------|----------------------|-------------------------------------------------------------------------------------------------|

| UITB <sup>(3)</sup> | 0 to 7               | Set transmission data                                                                           |

| UiRB <sup>(3)</sup> | 0 to 7               | Reception data can be read                                                                      |

|                     | OER                  | Overrun error flag                                                                              |

| UiBRG               | 0 to 7               | Set bit rate                                                                                    |

| UiMR <sup>(3)</sup> | SMD2 to SMD0         | Set to 0012                                                                                     |

|                     | CKDIR                | Select the internal clock or external clock                                                     |

|                     | IOPOL(i=2) (4)       | Set to 0                                                                                        |

| UiC0                | CLK1 to CLK0         | Select the count source for the UiBRG register                                                  |

|                     | CRS                  | Select CTS or RTS to use                                                                        |

|                     | TXEPT                | Transmit register empty flag                                                                    |

|                     | CRD                  | Enable or disable the CTS or RTS function                                                       |

|                     | NCH                  | Select TxDi pin output mode                                                                     |

|                     | CKPOL                | Select the transfer clock polarity                                                              |

|                     | UFORM                | Select the LSB first or MSB first                                                               |

| UiC1                | TE                   | Set this bit to 1 to enable transmission/reception                                              |

|                     | TI                   | Transmit buffer empty flag                                                                      |

|                     | RE                   | Set this bit to 1 to enable reception                                                           |

|                     | RI                   | Reception complete flag                                                                         |

|                     | U2IRS <sup>(1)</sup> | Select the source of UART2 transmit interrupt                                                   |

|                     | U2RRM <sup>(1)</sup> | Set this bit to 1 to use UART2 continuous receive mode                                          |

|                     | U2LCH <sup>(3)</sup> | Set this bit to 1 to use UART2 inverted data logic                                              |

|                     | U2ERE <sup>(3)</sup> | Set to 0                                                                                        |

| U2SMR               | 0 to 7               | Set to 0                                                                                        |

| U2SMR2              | 0 to 7               | Set to 0                                                                                        |

| U2SMR3              | 0 to 2               | Set to 0                                                                                        |

|                     | NODC                 | Select clock output mode                                                                        |

|                     | 4 to 7               | Set to 0                                                                                        |

| U2SMR4              | 0 to 7               | Set to 0                                                                                        |

| UCON                | U0IRS, U1IRS         | Select the source of UART0/UART1 transmit interrupt                                             |

|                     | U0RRM, U1RRM         | Set this bit to 1 to use continuous receive mode                                                |

|                     | CLKMD0               | Select the transfer clock output pin when CLKMD1 is set to 1                                    |

|                     | CLKMD1               | Set this bit to 1 to output UART1 transfer clock from two pins                                  |

|                     | RCSP                 | Set this bit to 1 to accept as input the UART0 $\overline{\text{CTS0}}$ signal from the P64 pin |

|                     | 7                    | Set to 0                                                                                        |

NOTES:

- 1. Set bits 5 and 4 in registers U0C1 and U1C1 to 0. Bits U0IRS, U1IRS, U0RRM, and U1RRM are in the UCON register.

- 2. Not all register bits are described above. Set those bits to 0 when writing to the registers in clock synchronous serial I/O mode.

- 3. Set bits 7 and 6 in registers U0C1 and U1C1 to 0.

- 4. Set the bit 7 in registers U0MR and U1MR to 0.

i=0 to 2

### 14.1.2 Clock Asynchronous Serial I/O (UART) Mode

The UART mode allows transmitting and receiving data after setting the desired bit rate and transfer data format. **Table 14.5** lists the specifications of the UART mode.

| Item                            | Specification                                                                                                 |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Transfer data format            | <ul> <li>Character bit (transfer data): Selectable from 7, 8 or 9 bits</li> </ul>                             |  |  |

|                                 | Start bit: 1 bit                                                                                              |  |  |

|                                 | <ul> <li>Parity bit: Selectable from odd, even, or none</li> </ul>                                            |  |  |

|                                 | Stop bit: Selectable from 1 or 2 bits                                                                         |  |  |

| Transfer clock                  | <ul> <li>The CKDIR bit in the UiMR(i=0 to 2) register is set to 0 (internal clock) : fj/ (16(n+1))</li> </ul> |  |  |

|                                 | fj = f1SIO, f2SIO, f8SIO, f32SIO. n: Setting value of UiBRG register 0016 to FF16                             |  |  |

|                                 | <ul> <li>CKDIR bit is set to 1 (external clock ): fEXT/16(n+1)</li> </ul>                                     |  |  |

|                                 | fEXT: Input from CLKi pin. n :Setting value of UiBRG register 0016 to FF16                                    |  |  |

| Transmission, reception control | <ul> <li>Selectable from CTS function, RTS function or CTS/RTS function disable</li> </ul>                    |  |  |

| Transmission start condition    | <ul> <li>Before transmission can start, the following requirements must be met</li> </ul>                     |  |  |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                          |  |  |

|                                 | <ul> <li>The TI bit in the UiC1 register is set to 0 (data present in UiTB register)</li> </ul>               |  |  |

|                                 | – If $\overline{CTS}$ function is selected, input on the $\overline{CTS}$ i pin is set to "L"                 |  |  |

| Reception start condition       | <ul> <li>Before reception can start, the following requirements must be met"</li> </ul>                       |  |  |

|                                 | - The RE bit in the UiC1 register is set to 1 (reception enabled)                                             |  |  |

|                                 | - Start bit detection                                                                                         |  |  |

|                                 | <ul> <li>For transmission, one of the following conditions can be selected</li> </ul>                         |  |  |

| Interrupt request               | – The UiIRS bit <sup>(2)</sup> is set to 0 (transmit buffer empty): when transferring data from the           |  |  |

| generation timing               | UiTB register to the UARTi transmit register (at start of transmission)                                       |  |  |

| 5                               | – The UiIRS bit is set to1 (transfer completed): when the serial I/O finished sending                         |  |  |

|                                 | data from the UARTi transmit register                                                                         |  |  |

|                                 | For reception                                                                                                 |  |  |

|                                 | When transferring data from the UARTi receive register to the UiRB register (at                               |  |  |

|                                 | completion of reception)                                                                                      |  |  |

| Error detection                 | Overrun error <sup>(1)</sup>                                                                                  |  |  |

|                                 | This error occurs if the serial I/O started receiving the next data before reading the                        |  |  |

|                                 | UiRB register and received the bit one before the last stop bit in the the next data                          |  |  |

|                                 | Framing error                                                                                                 |  |  |

|                                 | This error occurs when the number of stop bits set is not detected                                            |  |  |

|                                 | Parity error                                                                                                  |  |  |

|                                 | This error occurs when if parity is enabled, the number of 1 in parity and                                    |  |  |

|                                 | character bits does not match the number of 1 set                                                             |  |  |

|                                 | Error sum flag                                                                                                |  |  |

|                                 | This flag is set to 1 when any of the overrun, framing, and parity errors is encountered                      |  |  |

| Select function                 | LSB first, MSB first selection                                                                                |  |  |

|                                 | Whether to start sending/receiving data beginning with bit 0 or beginning with bit 7                          |  |  |

|                                 | can be selected                                                                                               |  |  |

|                                 | Serial data logic switch (UART2)                                                                              |  |  |

|                                 | This function reverses the logic of the transmit/receive data. The start and stop bits                        |  |  |

|                                 | are not reversed.                                                                                             |  |  |

|                                 | TxD, RxD I/O polarity switch (UART2)                                                                          |  |  |

|                                 | This function reverses the polarities of hte TxD pin output and RxD pin input. The                            |  |  |

|                                 | logic levels of all I/O data is reversed.                                                                     |  |  |

|                                 | Separate CTS/RTS pins (UART0)                                                                                 |  |  |

|                                 | CTS0 and RTS0 are input/output from separate pins                                                             |  |  |

|                                 | • UART1 pin remapping selection                                                                               |  |  |

|                                 |                                                                                                               |  |  |

Table 14.5 UART Mode Specifications

NOTES:

1. If an overrun error occurs, bits 8 to 0 in the UiRB register are undefined. The IR bit in the SiRIC register remains unchange.

2. Bits U0IRS and U1IRS respectively are the UCON register bits 0 and 1; the U2IRS bit is the U2C1 register bit 4.

**Table 14.7** lists the functions of the input/output pins in UART mode. **Table 14.8** lists the P64 pin functions during UART mode. Note that for a period from when the UARTi operation mode is selected to when transfer starts, the TxDi pin outputs an "H". (If the N-channel open-drain output is selected, this pin is in a high-impedance state.)

| Pin Name                             | Function             | Method of Selection                                                                                                                                                                        |

|--------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxDi (i = 0 to 2)<br>(P63, P67, P70) | Serial data output   | (Outputs "H" when performing reception only)                                                                                                                                               |

| RxDi<br>(P62, P66, P71)              | Serial data input    | PD6_2 bit, PD6_6 bit in the PD6 register and the PD7_1 bit in the PD7 register (Can be used as an input port when performing transmission only)                                            |

| CLKi<br>(P61, P65, P72)              | Input/output port    | Set the CKDIR bit in the UiMR register to 0                                                                                                                                                |

|                                      | Transfer clock input | Set the CKDIR bit in the UiMR register to 1<br>Set the PD6_1 bit and PD6_5 bit in the PD6 register to 0, PD7_2 bit in the PD7<br>register to 0                                             |

| (P60, P64, P73)                      | CTS input            | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 0<br>Set the PD6_0 bit and PD6_4 bit in the PD6 register to 0, the PD7_3 bit in the<br>PD7 register 0 |

|                                      | RTS output           | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 1                                                                                                     |

|                                      | Input/output port    | Set the CRD bit in the UiC0 register 1                                                                                                                                                     |

NOTE:

1. When the U1MAP bit in PACR register is set to 1 (P73 to P70), UART1 pin is assgined to P73 to P70.

|                      | Bit Set Value |     |               |        |                     |  |

|----------------------|---------------|-----|---------------|--------|---------------------|--|

| Pin Function         | U1C0 register |     | UCON register |        | PD6 register        |  |

|                      | CRD           | CRS | RCSP          | CLKMD1 | PD6_4               |  |

| P64                  | 1             |     | 0             | 0      | Input: 0, Output: 1 |  |

| CTS1                 | 0             | 0   | 0             | 0      | 0                   |  |

| RTS1                 | 0             | 1   | 0             | 0      |                     |  |

| CTS <sub>0</sub> (2) | 0             | 0   | 1             | 0      | 0                   |  |

NOTES:

1. When the U1MAP bit in PACR register is 1 (P73 to P70), this table lists the P70 functions.

2. In addition to this, set the CRD bit in the U0C0 register to 0 (CTSo/RTSo enabled) and the CRS bit in the U0C0 register to 1 (RTSo selected).

## 14.1.3 Special Mode 1 (I<sup>2</sup>C bus mode)(UART2)

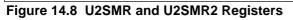

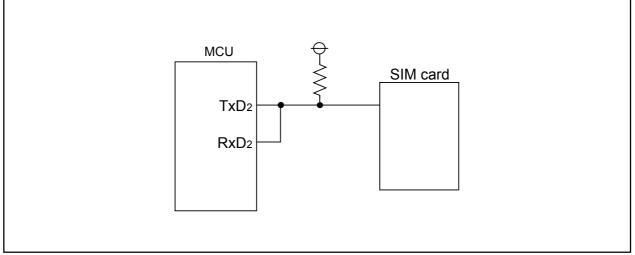

I<sup>2</sup>C bus mode is provided for use as a simplifed I<sup>2</sup>C bus interface compatible mode. **Table 14.10** lists the specifications of the I<sup>2</sup>C bus mode. **Tables 14.11** and **14.12** list the registers used in the I<sup>2</sup>C bus mode and the register values set. **Table 14.13** lists the I<sup>2</sup>C bus mode fuctions. **Figure 14.22** shows the block diagram for I<sup>2</sup>C bus mode. **Figure 14.23** shows SCL2 timing.

As shown in **Table 14.13**, the MCU is placed in I<sup>2</sup>C bus mode by setting bits SMD2 to SMD0 to 0102 and the IICM bit to 1. Because SDA2 transmit output has a delay circuit attached, SDA output does not change state until SCL2 goes low and remains stably low.

| Item                         | Specification                                                                                   |

|------------------------------|-------------------------------------------------------------------------------------------------|

| Transfer data format         | Transfer data length: 8 bits                                                                    |

| Transfer clock               | During master                                                                                   |

|                              | the CKDIR bit in the U2MR register is set to 0 (internal clock) : fj/ (2(n+1))                  |

|                              | fj = f1SIO, f2SIO, f8SIO, f32SIO. n: Setting value in the U2BRG register 0016 to FF16           |

|                              | During slave                                                                                    |

|                              | CKDIR bit is set to 1 (external clock ): Input from SCL2 pin                                    |

| Transmission start condition | Before transmission can start, the following requirements must be met <sup>(1)</sup>            |

|                              | <ul> <li>The TE bit in the U2C1 register is set to 1 (transmission enabled)</li> </ul>          |

|                              | <ul> <li>The TI bit in the U2C1 register is set to 0 (data present in U2TB register)</li> </ul> |

| Reception start condition    | Before reception can start, the following requirements must be met <sup>(1)</sup>               |

|                              | <ul> <li>The RE bit in the U2C1 register is set to 1 (reception enabled)</li> </ul>             |

|                              | <ul> <li>The TE bit in the U2C1 register is set to 1 (transmission enabled)</li> </ul>          |

|                              | – The TI bit in the U2C1 register is set to 0 (data present in the UiTB register)               |

| Interrupt request            | When start or stop condition is detected, acknowledge undetected, and acknowledge               |

| generation timing            | detected                                                                                        |

| Error detection              | Overrun error <sup>(2)</sup>                                                                    |

|                              | This error occurs if the serial I/O started receiving the next data before reading the          |

|                              | U2RB register and received the 8th bit in the the next data                                     |

| Select function              | Arbitration lost                                                                                |

|                              | Timing at which the ABT bit in the U2RB register is updated can be selected                     |

|                              | • SDA digital delay                                                                             |

|                              | No digital delay or a delay of 2 to 8 U2BRG count source clock cycles selectable                |