Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                 |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 71                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 12K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                      |

| Data Converters            | A/D 27x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30290fcvhp-u3a |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin<br>No. | Control<br>Pin | Port | Interrupt<br>Pin | Timer Pin  | Timer S Pin | UART/CAN Pin                                | Multi-master<br>I <sup>2</sup> C bus Pin | Analog Pin |

|------------|----------------|------|------------------|------------|-------------|---------------------------------------------|------------------------------------------|------------|

| 1          |                | P95  |                  |            |             | CLK4                                        |                                          | AN25       |

| 2          |                | P93  |                  |            |             | СТХ                                         |                                          | AN24       |

| 3          |                | P92  |                  | TB2IN      |             | CRX                                         |                                          | AN32       |

| 4          |                | P91  |                  | TB1IN      |             |                                             |                                          | AN31       |

| 5          | CLKOUT         | P90  |                  | ΤΒοιΝ      |             |                                             |                                          | AN30       |

| 6          | CNVss          |      |                  |            |             |                                             |                                          |            |

| 7          | XCIN           | P87  |                  |            |             |                                             |                                          |            |

| 8          | Хсоит          | P86  |                  |            |             |                                             |                                          |            |

| 9          | RESET          |      |                  |            |             |                                             |                                          |            |

| 10         | Хоит           |      |                  |            |             |                                             |                                          |            |

| 11         | Vss            |      |                  |            |             |                                             |                                          |            |

| 12         | Xin            |      |                  |            |             |                                             |                                          |            |

| 13         | Vcc            |      |                  |            |             |                                             |                                          |            |

| 14         |                | P85  | NMI              | SD         |             |                                             |                                          |            |

| 15         |                | P84  | INT <sub>2</sub> | ZP         |             |                                             |                                          |            |

| 16         |                | P83  | INT <sub>1</sub> |            |             |                                             |                                          |            |

| 17         |                | P82  | ĪNT <sub>0</sub> |            |             |                                             |                                          |            |

| 18         |                | P81  |                  | TA4IN / U  |             |                                             |                                          |            |

| 19         |                | P80  |                  | ТА40UT / U |             |                                             |                                          |            |

| 20         |                | P77  |                  | ТАзіл      |             |                                             |                                          |            |

| 21         |                | P76  |                  | ТАзоит     |             |                                             |                                          |            |

| 22         |                | P75  |                  | TA2IN / W  |             |                                             |                                          |            |

| 23         |                | P74  |                  | TA20UT / W |             |                                             |                                          |            |

| 24         |                | P73  |                  | TA1IN / V  |             | CTS2 / RTS2 / TxD1                          |                                          |            |

| 25         |                | P72  |                  | TA10UT / V |             | CLK2 / RxD1                                 |                                          |            |

| 26         |                | P71  |                  | TAOIN      |             | RxD2 / SCL2 / CLK1                          |                                          |            |

| 27         |                | P70  |                  | ΤΑυουτ     |             | TxD2 / SDA2 / RTS1 /<br>CTS1 / CTS0 / CLKS1 |                                          |            |

| 28         |                | P67  |                  |            |             | TxD1                                        |                                          |            |

| 29         |                | P66  |                  |            |             | RxD1                                        |                                          |            |

| 30         |                | P65  |                  |            |             | CLK1                                        |                                          |            |

| 31         |                | P64  |                  |            |             | RTS1 / CTS1/ CTS0 /<br>CLKS1                |                                          |            |

| 32         |                | P37  |                  |            |             |                                             |                                          |            |

| 33         |                | P36  |                  |            |             |                                             |                                          |            |

| 34         |                | P35  |                  |            |             |                                             |                                          |            |

| 35         |                | P34  |                  |            |             |                                             |                                          |            |

| 36         |                | P33  |                  |            |             |                                             |                                          |            |

| 37         |                | P32  |                  |            |             | Sout3                                       |                                          |            |

| 38         |                | P31  |                  |            |             | SIN3                                        |                                          |            |

| 39         |                | P30  |                  |            |             | CLK3                                        |                                          |            |

| 40         |                | P63  |                  |            |             | TxD0                                        |                                          |            |

Table 1 12 Pin Characteristics for 80-Pin Package

The following describes the clocks generated by the clock generation circuit.

### 7.1 Main Clock

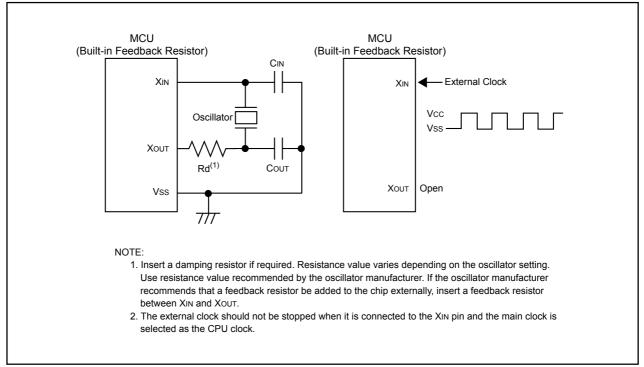

The main clock is generated by the main clock oscillation circuit. This clock is used as the clock source for the CPU and peripheral function clocks. The main clock oscillator circuit is configured by connecting a resonator between the XIN and XOUT pins. The main clock oscillator circuit contains a feedback resistor, which is disconnected from the oscillator circuit during stop mode in order to reduce the amount of power consumed in the chip. The main clock oscillator circuit may also be configured by feeding an exter nally generated clock to the XIN pin. **Figure 7.8** shows the examples of main clock connection circuit.

The power consumption in the chip can be reduced by setting the CM05 bit in the CM0 register to 1 (main clock oscillator circuit turned off) after switching the clock source for the CPU clock to a sub clock or on-chip oscillator clock. In this case, XOUT goes "H". Furthermore, because the internal feedback resistor remains on, XIN is pulled "H" to XOUT via the feedback resistor.

During stop mode, all clocks including the main clock are turned off. Refer to "power control".

If the main clock is not used, it is recommended to connect the XIN pin to VCC to reduce power consumption during reset.

Figure 7.8 Examples of Main Clock Connection Circuit

|                      | Symbol<br>WDC     | Address<br>000F16          | After Reset<br>00XXXXX2                 |    |

|----------------------|-------------------|----------------------------|-----------------------------------------|----|

|                      | Bit Symbol        | Bit Name                   | Function                                | RW |

|                      | (b4-b0)           | High-order bits of watchdo | g timer                                 | RO |

|                      | (b5)              | Reserved bit               | Set to 0                                | RW |

|                      | ( <del>b6</del> ) | Reserved bit               | Set to 0                                | RW |

|                      | WDC7              | Prescaler select bit       | 0 : Divided by 16<br>1 : Divided by 128 | RW |

|                      |                   |                            |                                         |    |

| Watchdog Timer Start | -                 | Address<br>000E16          | After Reset<br>Undefined                |    |

| Watchdog Timer Start | Symbol            |                            | Undefined                               | RW |

Figure 10.2 WDC Register and WDTS Register

### **10.1 Count Source Protective Mode**

In this mode, a on-chip oscillator clock is used for the watchdog timer count source. The watchdog timer can be kept being clocked even when CPU clock stops as a result of run-away.

Before this mode can be used, the following register settings are required:

- (1) Set the PRC1 bit in the PRCR register to 1 (enable writes to PM1 and PM2 registers).

- (2) Set the PM12 bit in the PM1 register to 1 (reset when the watchdog timer underflows).

- (3) Set the PM22 bit in the PM2 register to 1 (on-chip oscillator clock used for the watchdog timer count source).

- (4) Set the PRC1 bit in the PRCR register to 0 (disable writes to PM1 and PM2 registers).

- (5) Write to the WDTS register (watchdog timer starts counting).

Setting the PM22 bit to 1 results in the following conditions

- The on-chip oscillator continues oscillating even if the CM21 bit in the CM2 register is set to "0" (main clock or PLL clock) (system clock of count source selected by the CM21 bit is valid)

- The on-chip oscillator starts oscillating, and the on-chip oscillator clock becomes the watchdog timer count source.

Watchdog timer count (32768)

Watchdog timer period = —

on-chip oscillator clock

- The CM10 bit in the CM1 register is disabled against write. (Writing a 1 has no effect, nor is stop mode entered.)

- The watchdog timer does not stop when in wait mode.

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Symbol<br>TB2SC | Address<br>039E16                                        | After Reset<br>X00000002                                                                                                                                                                            |    |

|-------------------------------------------------------|-----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                       | Bit Symbol      | Bit Name                                                 | Function                                                                                                                                                                                            | RW |

|                                                       | PWCON           | Timer B2 reload timing switch bit (2)                    | 0: Timer B2 underflow<br>1: Timer A output at odd-numbered                                                                                                                                          | RW |

|                                                       | IVPCR1          | Three-phase output port<br>SD control bit 1<br>(3, 4, 7) | <ul> <li>0: Three-phase output forcible cutoff by SD pin input<br/>(high impedance) disabled</li> <li>1: Three-phase output forcible cutoff by SD pin input<br/>(high impedance) enabled</li> </ul> | RW |

|                                                       | TB0EN           | Timer B0 operation mode select bit                       | 0: Other than A/D trigger mode<br>1: A/D trigger mode (5)                                                                                                                                           | RW |

| · · · · · · · · · · · · · · · · · · ·                 | TB1EN           | Timer B1 operation mode select bit                       | 0: Other than A/D trigger mode<br>1: A/D trigger mode (5)                                                                                                                                           | RW |

|                                                       | TB2SEL          | Trigger select bit (6)                                   | 0: TB2 interrupt<br>1: Underflow of TB2 interrupt<br>generation frequency setting counter [ICTB2]                                                                                                   | RW |

| · · · · · · · · · · · · · · · · · · ·                 | (b6-b5)         | Reserved bits                                            | Set to 0                                                                                                                                                                                            | RW |

| L                                                     | (b7)            | Nothing is assigned. If ne<br>When read, the content is  |                                                                                                                                                                                                     | —  |

1. Write to this register after setting the PRC1 bit in the PRCR register to 1 (write enabled).

2. If the INV11 bit is 0 (three-phase mode 0) or the INV06 bit is 1 (triangular wave modulation mode), set this bit to 0 (timer B2 underflow).

3. When setting the IVPCR1 bit to 1 (three-phase output forcible cutoff by SD pin input enabled), Set the PD85 bit to 0 (= input mode).

4. Related pins are U(P8<sub>0</sub>), U(P8<sub>1</sub>), V(P7<sub>2</sub>), V(P7<sub>3</sub>), W(P7<sub>4</sub>), W(P7<sub>5</sub>). When a high-level ("H") signal is applied to the SD pin and set the IVPCR1 bit to 0 after forcible cutoff, pins U, U, V, V, w, and W are exit from the high-impedance state. If a lowlevel ("L") signal is applied to the  $\overline{SD}$  pin, three-phase motor control timer output will be disabled (INV03=0). At this time, when the IVPCR1 bit is 0, pins U, U, V, W, and W become programmable I/O ports. When the IVPCR1 bit is set to 1, pins U, U, V, V, W, and W are placed in a high-impedance state regardless of which function of those pins is used.

5. When this bit is used in delayed trigger mode 0, set bits TB0EN and TB1EN to 1 (A/D trigger mode).

6. When setting the TB2SEL bit to 1 (underflow of TB2 interrupt generation frequency setting counter[ICTB2]), set the INV02 bit to 1 (three-phase motor control timer function).

7. Refer to "19.6 Digital Debounce Function" for the SD input.

The effect of SD pin input is below.

| 1.Case of INV03 = 1(Three-phase motor control timer output enabled) |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| SD pin inputs <sup>(3)</sup> | Status of U/V/W pins             | Remarks                                                                                                        |

|------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|

| Н                            | Three-phase PWM output           |                                                                                                                |

| L <sup>(1)</sup>             | High impedance <sup>(4)</sup>    | Three-phase output<br>forcrible cutoff                                                                         |

| Н                            | Three-phase PWM output           |                                                                                                                |

| L <sup>(1)</sup>             | Input/output port <sup>(2)</sup> |                                                                                                                |

|                              | H<br>L <sup>(1)</sup>            | H     Three-phase PWM output       L <sup>(1)</sup> High impedance <sup>(4)</sup> H     Three-phase PWM output |

NOTES:

1. When "L" is applied to the SD pin, INV03 bit is changed to 0 at the same time.

2. The value of the port register and the port direction register becomes effective.

3. When SD function is not used, set to 0 (Input) in PD85 and pullup to "H" in SD pin from outside.

4. To leave the high-impedance state and restart the three-phase PWM signal output after the three-phase PWM signal output forced cutoff, set the IVPCR1 bit to 0 after the SD pin input level becomes high ("H").

2 Case of INV03 = 0 (Three-phase motor control timer output disabled)

| 2.0436 01 111005 - 0(1116                             |                                   |                                                 |                                                       |

|-------------------------------------------------------|-----------------------------------|-------------------------------------------------|-------------------------------------------------------|

| IVPCR1 bit                                            | $\overline{\text{SD}}$ pin inputs | Status of U/V/W pins                            | Remarks                                               |

| 1<br>(Three-phase output                              | Н                                 | Peripheral input/output<br>or input/output port |                                                       |

| forcrible cutoff enable)                              | L                                 | High impedance                                  | Three-phase output<br>forcrible cutoff <sup>(1)</sup> |

| 0<br>(Three-phase output<br>forcrible cutoff disable) | Н                                 | Peripheral input/output<br>or input/output port |                                                       |

|                                                       | L                                 | Peripheral input/output<br>or input/output port |                                                       |

NOTE:

1. The three-phase output forcrible cutoff function becomes effective if the INPCR1 bit is set to 1 (three-phase output forcrible cutoff function enable) even when the INV03 bit is 0 (three-phase motor control timer output disalbe)

#### Figure 12.30 TB2SC Register

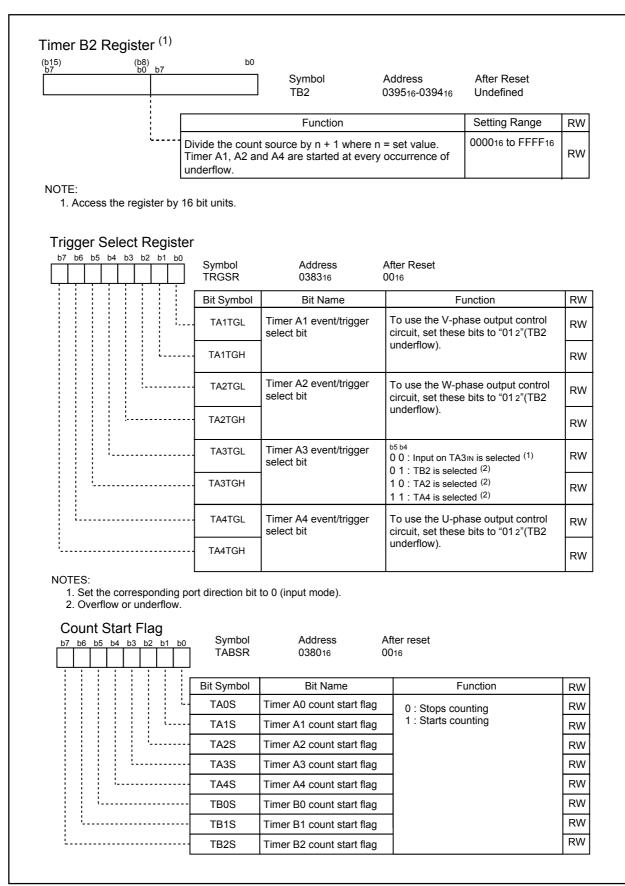

Figure 12.31 TB2 Register, TRGSR Register, and TABSR Register

| ') (b                                                                  | 8<br>0)b7                                                                                             | b0                                                                                                                   | G1TM3                                                                                                   | Address<br>to G1TM2 030116-030016,<br>to G1TM5 030716-030616,<br>to G1TM7 030D16-030C16,                                                                                                                                                                            | 030916-030816                                                                                             | 030B16-030A16 Indeter                                                                                                                   | minte<br>minte      |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                                                        |                                                                                                       | Γ                                                                                                                    |                                                                                                         | Function                                                                                                                                                                                                                                                            |                                                                                                           | Setting Range                                                                                                                           | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      |                                                                                                         | e timer value is stored eve<br>ment timing                                                                                                                                                                                                                          | ry                                                                                                        |                                                                                                                                         | RO                  |

|                                                                        |                                                                                                       |                                                                                                                      | Symb<br>G1PC                                                                                            | OCR0 to G1POCR3 03                                                                                                                                                                                                                                                  | ( <b>j=0 to 7</b> )<br>dress<br>1016, 031116, 03<br>1416, 031516, 03                                      | After R<br>31216, 031316 0X00 >                                                                                                         | (X002               |

|                                                                        |                                                                                                       |                                                                                                                      | Bit<br>Symbol                                                                                           | Bit Name                                                                                                                                                                                                                                                            |                                                                                                           | Function                                                                                                                                | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | MOD0                                                                                                    | Operating mode                                                                                                                                                                                                                                                      | 01: SR wav                                                                                                | vaveform output mode<br>eform output mode <sup>(1)</sup>                                                                                | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | MOD1                                                                                                    | select bit                                                                                                                                                                                                                                                          | output r                                                                                                  | delayed waveform<br>node<br>set to this value                                                                                           | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | (b3-b2)                                                                                                 | Nothing is assigned. If I When read, their conten                                                                                                                                                                                                                   |                                                                                                           |                                                                                                                                         | -                   |

|                                                                        |                                                                                                       |                                                                                                                      | IVL                                                                                                     | Output initial value select bit <sup>(4)</sup>                                                                                                                                                                                                                      |                                                                                                           | t as a default value<br>t as a default value                                                                                            | RW                  |

| ·                                                                      |                                                                                                       |                                                                                                                      | RLD                                                                                                     | G1POj register value reload timing select bit                                                                                                                                                                                                                       | value is w<br>1: Reloads t                                                                                | he G1POj register when<br>vritten<br>he G1POj register when<br>timer is reset                                                           | RW                  |

|                                                                        |                                                                                                       |                                                                                                                      | (b6)                                                                                                    | Nothing is assigned. If When read, its content i                                                                                                                                                                                                                    |                                                                                                           | t to 0.                                                                                                                                 | -                   |

|                                                                        |                                                                                                       |                                                                                                                      | INV                                                                                                     | Inverse output function select bit <sup>(2)</sup>                                                                                                                                                                                                                   | 0: Output is<br>1: Output is                                                                              | not inversed<br>inversed                                                                                                                | RW                  |

| corr<br>prov<br>2. The<br>to 1<br>prov<br>3. In the<br>char<br>4. To p | s setting<br>respond<br>vide way<br>inverse<br>, and "H<br>vided by<br>he SR v<br>nnel (ne<br>provide | ing odd ch<br>veform out<br>e output fur<br>f" signal is<br>v setting it t<br>vaveform c<br>ext channe<br>either "H" | annel (nex<br>put. Odd<br>nction is th<br>provided<br>to 1.<br>output moo<br>l after the<br>or "L" sign | even channels. In SR way<br>of channel after an even c<br>channels provide no wave<br>le final step in waveform g<br>a default output by setting<br>de, set not only the even c<br>even channel).<br>al output set in the IVL bit<br>inction) and IFEj bit in the 0 | hannel) are ig<br>eform output.<br>generating pro-<br>the IVL bit to<br>channel but als<br>c, set the FSC | nored. Even channels<br>becess. When the INV bit i<br>0, and an "L" signal is<br>so the correspoinding ev<br>j bit in the G1FS register | s set<br>en<br>to 0 |

Figure 13.6 G1TM0 to G1TM7 Registers, and G1POCR0 to G1POCR7 Registers

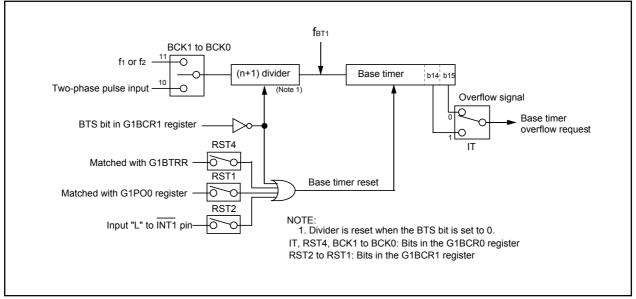

Figure 13.11 Base Timer Block Diagram

| Table 13.3 Base Timer Associated Register Settings (Time Measurement Function, Waveform) |

|------------------------------------------------------------------------------------------|

| Generation Function, Communication Function)                                             |

| Register | Bit          | Function                       |

|----------|--------------|--------------------------------|

| G1BCR0   | BCK1 to BCK0 | Select a count source          |

|          | RST4         | Select base timer reset timing |

|          | IT           | Select the base timer overflow |

| G1BCR1   | RST2 to RST1 | Select base timer reset timing |

|          | BTS          | Used to start the base timer   |

|          | UD1 to UD0   | Select how to count            |

| G1BT     | -            | Read or write base timer value |

| G1DV     | -            | Divide ratio of a count source |

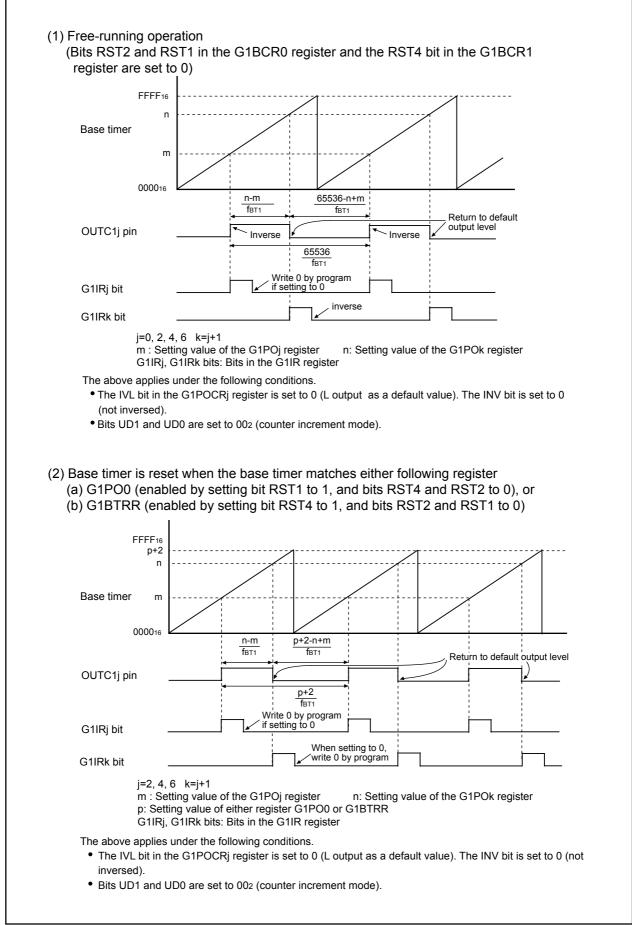

Set the following registers to set the RST1 bit to 1 (base timer reset by matching the base timer with the G1PO0 register)

| G1POCR0 | MOD1 to MOD0 | Set to 002 (single-phase waveform output mode) |

|---------|--------------|------------------------------------------------|

| G1PO0   | -            | Set reset cycle                                |

| G1FS    | FSC0         | Set to 0 (waveform generating function)        |

| G1FE    | IFE0         | Set to 1 (channel operation start)             |

|                                                           | lecting the rising edge as a timer measurement trigger<br>S1 and CTS0 in the G1TMCRj register (j=0 to 7)=012)                                                                                |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fBT1                                                      |                                                                                                                                                                                              |

| Base timer                                                | <u></u>                                                                                                                                                                                      |

| INPC1j pin ir<br>trigger signa<br>passing the o<br>filter | lafter                                                                                                                                                                                       |

| G1IRj bit <sup>(1)</sup>                                  | Delayed by 1 clock write 0 by program if setting to 0                                                                                                                                        |

| G1TMj regis                                               |                                                                                                                                                                                              |

|                                                           | IS :<br>Bits in the G1IR register.<br>nput pulse applied to the INPC1j pin requires 1.5 fBT1 clock cycles or more.                                                                           |

|                                                           | ecting both edges as a timer measurement trigger<br>S1 and CTS0 = 112)                                                                                                                       |

| fBT1                                                      |                                                                                                                                                                                              |

| Base timer                                                | <u> </u>                                                                                                                                                                                     |

| INPC1j pin in<br>trigger signa<br>passing the<br>filter   |                                                                                                                                                                                              |

| G1IRj bit <sup>(1)</sup>                                  | write 0 by progra<br>if setting to 0                                                                                                                                                         |

| G1TMj register (2)                                        | n x n+2 x n+5 x n+8 x n+12                                                                                                                                                                   |

| 2. N                                                      | IS :<br>Bits in the G1IR register.<br>No interrupt is generated if the MCU receives a trigger signal when the G1IRj bit is set to 1.<br>However, the value of the G1TMj register is updated. |

| (c) Trigger si<br>(Bits DF1                               | gnal when using digital filter<br>I to DF0 in the G1TMCRj register =102 or 112)                                                                                                              |

| f1 or f2 or fBT1 <sup>(1)</sup>                           |                                                                                                                                                                                              |

| INPC1j pin                                                | Maximum 3.5 f1 or f2 or fBT1                                                                                                                                                                 |

| Trigger signa<br>passing the<br>filter                    | al after Signals, which do not match 3<br>digital times, are stripped off The trigger signal is delayed                                                                                      |

|                                                           | by the digital filter                                                                                                                                                                        |

| NOTE<br>1. f                                              | :<br>BT1 when bits DF1 to DF0 are set to 10₂, and f1 or f2 when set to 11₂.                                                                                                                  |

Figure 13.24 Set/Reset Waveform Output Mode

RENESAS

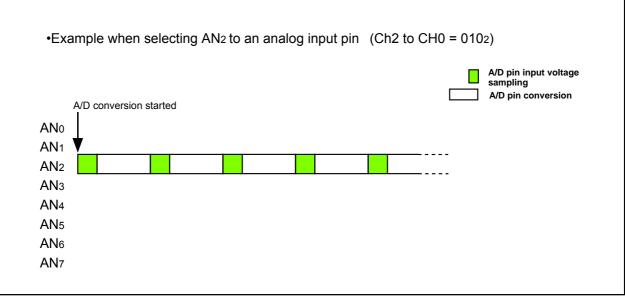

### 15.1.2 Repeat mode

In repeat mode, analog voltage applied to a selected pin is repeatedly converted to a digital code. **Table 15.4** shows the repeat mode specifications. **Figure 15.8** shows the operation example in repeat mode. **Figure 15.9** shows the ADCON0 to ADCON2 registers in repeat mode.

| Item                                | Specification                                                                       |

|-------------------------------------|-------------------------------------------------------------------------------------|

| Function                            | Bits CH2 to CH0 in the ADCON0 register and the ADGSEL1 to ADGSEL0 bits              |

|                                     | in the ADCON2 register select pins. Analog voltage applied to a selected pin        |

|                                     | is repeatedly converted to a digital code                                           |

| A/D Conversion Start                | When the TRG bit in the ADCON0 register is 0 (software trigger)                     |

| Condition                           | Set the ADST bit in the ADCON0 register to 1 (A/D conversion started)               |

|                                     | <ul> <li>When the TRG bit in the ADCON0 register is 1 (hardware trigger)</li> </ul> |

|                                     | The ADTRG pin input changes state from "H" to "L" after setting the ADST bit        |

|                                     | to 1 (A/D conversion started)                                                       |

| A/D Conversion Stop Condition       | Set the ADST bit to 0 (A/D conversion halted)                                       |

| Interrupt Request Generation Timing | None generated                                                                      |

| Analog Input Pin                    | Select one pin from AN0 to AN7, AN00 to AN07, AN20 to AN27, and AN30 to AN32        |

| Readout of A/D Conversion Result    | Readout one of the AD0 to AD7 registers that corresponds to the selected pin        |

### 15.1.8 Delayed Trigger Mode 1

In delayed trigger mode 1, analog voltages applied to the selected pins are converted one-by-one to a digital code. When the input of the  $\overline{ADTRG}$  pin (falling edge) changes state from "H" to "L", a single sweep conversion is started. After completing the ANo pin conversion, the AN1 pin is not sampled and converted until the second  $\overline{ADTRG}$  pin falling edge is generated. When the second  $\overline{ADTRG}$  falling edge is generated, the single sweep conversion of the pins after the AN1 pin is restarted. **Table 15.12** shows the delayed trigger mode 1 specifications. **Figure 15.24** shows the operation example of delayed trigger mode 1. **Figure 15.25** and **15.26** show each flag operation in the ADSTAT0 register that corresponds to the operation example. **Figure 15.27** shows registers ADCON0 to ADCON2 in delayed trigger mode 1. **Figure 15.28** shows the ADTRGCON register in delayed trigger mode 1. **Table 15.13** shows the trigger select bit setting in delayed trigger mode 1.

| Item                             | Specification                                                                            |  |  |

|----------------------------------|------------------------------------------------------------------------------------------|--|--|

| Function                         | Bits SCAN1 and SCAN0 in the ADCON1 register and bits ADGSEL1 and ADGSEL0                 |  |  |

|                                  | in the ADCON2 register select pins. Analog voltages applied to the selected              |  |  |

|                                  | pins are converted one-by-one to a digital code. At this time, the ADTRG pin             |  |  |

|                                  | falling edge starts AN <sub>0</sub> pin conversion and the second ADTRG pin falling edge |  |  |

|                                  | starts conversion of the pins after AN1 pin                                              |  |  |

| A/D Conversion Start             | ANo pin conversion start condition                                                       |  |  |

| Condition                        | The ADTRG pin input changes state from "H" to "L" (falling edge) <sup>(1)</sup>          |  |  |

|                                  | AN1 pin conversion start condition <sup>(2)</sup>                                        |  |  |

|                                  | The ADTRG pin input changes state from "H" to "L" (falling edge)                         |  |  |

|                                  | •When the second ADTRG pin falling edge is generated during A/D conversion of            |  |  |

|                                  | the ANo pin, input voltage of AN1 pin is sampled or after at the time of ADTRG           |  |  |

|                                  | falling edge. The conversion of AN1 and the rest of the sweep starts when AN0            |  |  |

|                                  | conversion is completed.                                                                 |  |  |

|                                  | •When the ADTRG pin falling edge is generated again during single sweep                  |  |  |

|                                  | conversion of pins after the AN1 pin, the conversion is not affected                     |  |  |

| A/D Conversion Stop              | •A/D conversion completed                                                                |  |  |

| Condition                        | •Set the ADST bit to 0 (A/D conversion halted) <sup>(3)</sup>                            |  |  |

| Interrupt Request                | Single sweep conversion completed                                                        |  |  |

| Generation Timing                |                                                                                          |  |  |

| Analog Input Pin                 | Select from AN0 to AN1 (2 pins), AN0 to AN3 (4 pins), AN0 to AN5 (6 pins)                |  |  |

|                                  | and AN₀ to AN⁊ (8 pins) <sup>(4)</sup>                                                   |  |  |

| Readout of A/D Conversion Result | Readout one of registers AN0 to AN7 that corresponds to the selected pins                |  |  |

#### Table 15.12 Delayed Trigger Mode 1 Specifications

NOTES:

- Do not generate the next ADTRG pin falling edge after the AN1 pin conversion is started until all selected pins complete A/D conversion. When an ADTRG pin falling edge is generated again during A/D conversion, its trigger is ignored. The falling edge of ADTRG pin, which was input after all selected pins complete A/D conversion, is considered to be the next AN0 pin conversion start condition.

- 2. The ADTRG pin falling edge is detected synchronized with the operation clock fAD. Therefore, when the ADTRG pin falling edge is generated in shorter periods than fAD, the second ADTRG pin falling edge may not be detected. Do not generate the ADTRG pin falling edge in shorter periods than fAD.

- 3. Do not write 1 (A/D conversion started) to the ADST bit in delayed trigger mode 1. When write 1,unexpected interrupts may be generated.

- 4. AN00 to AN07, AN 20 to AN27, and AN30 to AN32 can be used in the same way as AN0 to AN7. However, all input pins need to belong to the same group.

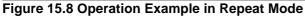

Figure 16.2 S0D0 Register

Г

| b7 b6 b5 t | b4 b3 b2 b1 b0 | Symbo<br>S10 | Address 02E816                                       | After Reset<br>0001000X2                                      |                   |

|------------|----------------|--------------|------------------------------------------------------|---------------------------------------------------------------|-------------------|

|            |                | Bit Symbol   | Bit Name                                             | Function                                                      | RW                |

|            |                | LRB          | Last receive bit                                     | 0: Last bit = 0<br>1: Last bit = 1                            | RO <sup>(1</sup>  |

|            |                | ADR0         | General call detecting flag                          | 0: No general call detected<br>1: General call detected       | RO <sup>(1)</sup> |

|            |                | AAS          | Slave address comparison flag                        | 0: No address matched<br>1: Address matched                   | RO <sup>(1</sup>  |

|            | ·              | AL           | Arbitration lost detection flag                      | 0: Not detected<br>1: Detected                                | RO <sup>(2)</sup> |

|            |                | PIN          | I <sup>2</sup> C bus interface interrupt request bit | 0: Interrupt request issued<br>1: No interrupt request issued | RO <sup>(2)</sup> |

|            |                | BB           | Bus busy flag                                        | 0: Bus free<br>1: Bus busy                                    | RO <sup>(1)</sup> |

|            |                | TRX          | Communication mode select bits 0                     | 0: Receive mode<br>1: Transmit mode                           | RW <sup>(3</sup>  |

|            |                | MST          | Communication mode select bit 1                      | 0: Slave mode<br>1: Master mode                               | RW <sup>(3</sup>  |

Read only. If necessary, set to 0.

To write to these bits, refer to 16.9 START Condition Generation Method and 16.11 STOP Condition Generation Method.

Figure 16.5 S10 Register

# 16.5 I<sup>2</sup>C0 Status Register (S10 register)

The S10 register monitors the  $l^2C$  bus interface status. When using the S10 register to check the status, use the 6 low-order bits for read only.

## 16.5.1 Bit 0: Last Receive Bit (LRB)

The LRB bit stores the last bit value of received data. It can also be used to confirm whether ACK is received. If the ACK-CLK bit in the S20 register is set to 1 (with ACK clock) and ACK is returned when the ACK clock is generated, the LRB bit is set to 0. If ACK is not returned, the LRB bit is set to 1. When the ACK-CLK bit is set to 0 (no ACK clock), the last bit value of received data is input. When writing data to the S00 register, the LRB bit is set to 0.

## 16.5.2 Bit 1: General Call Detection Flag (ADR0)

When the ALS bit in the S1D0 register is set to 0 (addressing format), this ADR0 flag is set to 1 by receiving the general calls<sup>(1)</sup>, whose address data are all 0, in slave mode.

The ADR0 flag is set to 0 when STOP or START conditions is detected or when the IHR bit in the S1D0 register is set to 1 (reset).

NOTE:

1. General call: A master device transmits the general call address 0016 to all slaves. When the master device transmits the general call, all slave devices receive the controlled data after general call.

### 16.5.3 Bit 2: Slave Address Comparison Flag (AAS)

The AAS flag indicates a comparison result of the slave address data after enabled by setting the ALS bit in the S1D0 register to 0 (addressing format).

The AAS flag is set to 1 when the 7 bits of the address data are matched with the slave address stored into the S0D0 register, or when a general call is received, in slave receive mode. The AAS flag is set to 0 by writing data to the S00 register. When the ES0 bit in the S1D0 register is set to 0 ( $I^2C$  bus interface disabled) or when the IHR bit in the S1D0 register is set to 1 (reset), the AAS flag is also set to 0.

## 16.5.4 Bit 3: Arbitration Lost Detection Flag (AL)<sup>(1)</sup>

In master transmit mode, if an "L" signal is applied to the SDA pin by other than the MCU, the AL flag is set to 1 by determining that the arbitration is los and the TRX bit in the S10 register is set to 0 (receive mode) at the same time. The MST bit in the S10 register is set to 0 (slave mode) after transferring the bytes which lost the arbitration.

The arbitration lost can be detected only in master transmit mode. When writing data to the S00 register, the AL flag is set to 0. When the ES0 bit in the S1D0 register is set to 0 ( $I^2C$  bus interface disabled) or when the IHR bit in the S1D0 register is set to 1 (reset), the AL flag is set to 0.

NOTE:

1. Arbitration lost: communication disabled as a master

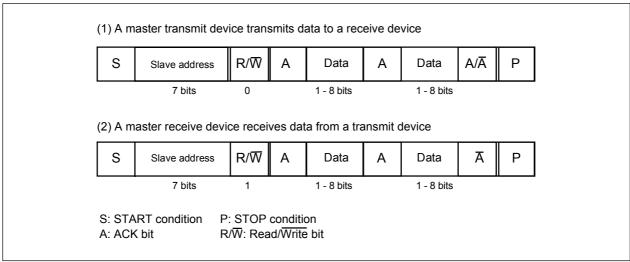

# 16.13 Address Data Communication

This section describes data transmit control when a master transferes data or a slave receives data in 7-bit address format. **Figure 16.20 (1)** shows a master transmit format.

Figure 16.20 Address data communication format

### 16.13.1 Example of Master Transmit

For example, a master transmits data as shown below when following conditions are met: standard clock mode, SCL clock frequency of 100kHz and ACK clock added.

- 1) Set s slave address to the 7 high-order bits in the S0D0 register

- 2) Set 8516 to the S20 register, 0002 to bits ICK4 to ICK2 in the S4D0 register and 0016 to the S3D0 registe to generate an ACK clock and set SCL clock frequency t 100 kHz (f1=8MHz, fIIC=f1)

- 3) Set 0016 to the S10 register to reset transmit/receive

- 4) Set 0816 to the S1D0 register to enable data communication

- 5) Confirm whether the bus is free by BB flag setting in the S10 register

- 6) Set E016 to the S10 register to enter START condition standby mode

- 7) Set the destination address in 7 high-order bits and 0 to a least significant bit in the S00 register to generate START condition. At this time, the first byte consisting of SCL and ACK clock are automatically generated

- 8) Set a transmit data to the S00 register. At this time, SCL and an ACK clock are automatically generated

- 9) When transmitting more than 1-byte control data, repeat the above step 8).

- 10) Set C016 in the S10 register to enter STOP condition standby mode if ACK is not returned from the slave receiver or if the transmit is completed

- 11) Write dummy data to the S00 regiser to generate STOP condition

### 17.1.1 CAN0 Message Box

Table 17.1 shows the memory mapping of the CAN0 message box.

It is possible to access to the message box in byte or word.

Mapping of the message contents differs from byte access to word access. Byte access or word access can be selected by the MsgOrder bit of the C0CTLR register.

| Table 17.1 | Memory Mapping of CAN0 Message Box | K |

|------------|------------------------------------|---|

|------------|------------------------------------|---|

|                                  | Message content (Memory mapping)      |                                       |  |

|----------------------------------|---------------------------------------|---------------------------------------|--|

| Address                          | Byte access (8 bits)                  | Word access (16 bits)                 |  |

| 0060 <sub>16</sub> + n • 16 + 0  | SID <sub>10</sub> to SID <sub>6</sub> | SID₅ to SID₀                          |  |

| 0060 <sub>16</sub> + n • 16 + 1  | SID₅ to SID₀                          | SID <sub>10</sub> to SID <sub>6</sub> |  |

| 0060 <sub>16</sub> + n • 16 + 2  | EID17 to EID14                        | EID <sub>13</sub> to EID <sub>6</sub> |  |

| 0060 <sub>16</sub> + n • 16 + 3  | EID <sub>13</sub> to EID <sub>6</sub> | EID17 to EID14                        |  |

| 0060 <sub>16</sub> + n • 16 + 4  | EID₅ to EID₀                          | Data Length Code (DLC)                |  |

| 0060 <sub>16</sub> + n • 16 + 5  | Data Length Code (DLC)                | EID₅ to EID₀                          |  |

| 0060 <sub>16</sub> + n • 16 + 6  | Data byte 0                           | Data byte 1                           |  |

| 0060 <sub>16</sub> + n • 16 + 7  | Data byte 1                           | Data byte 0                           |  |

|                                  |                                       |                                       |  |

| 0060 <sub>16</sub> + n • 16 + 13 | Data byte 7                           | Data byte 6                           |  |

| 0060 <sub>16</sub> + n • 16 + 14 | Time stamp high-order byte            | Time stamp low-order byte             |  |

| 0060 <sub>16</sub> + n • 16 + 15 | Time stamp low-order byte             | Time stamp high-order byte            |  |

n = 0 to 15: the number of the slot

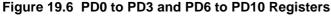

Figure 21.1 Timing Diagram (1)

#### **Timing Requirements**

# Vcc = 5V

(Vcc=5V, Vss=0V, at Topr=-40 to 125°C unless otherwise specified)

| Symbol  | Parameter                             | Standard clock mode |      | High-speed clock mode |      |      |

|---------|---------------------------------------|---------------------|------|-----------------------|------|------|

|         |                                       | Min.                | Max. | Min.                  | Max. | Unit |

| tBUF    | Bus free time                         | 4.7                 |      | 1.3                   |      | μs   |

| tHD;STA | The hold time in start condition      | 4.0                 |      | 0.6                   |      | μs   |

| tLOW    | The hold time in SCL clock "0" status | 4.7                 |      | 1.3                   |      | μs   |

| tR      | SCL, SDA signals' rising time         |                     | 1000 | 20+0.1Cb              | 300  | ns   |

| tHD;DAT | Data hold time                        | 0                   |      | 0                     | 0.9  | μs   |

| tHIGH   | The hold time in SCL clock "1" status | 4.0                 |      | 0.6                   |      | μs   |

| tF      | SCL, SDA signals' falling time        |                     | 300  | 20+0.1Cb              | 300  | ns   |

| tsu;DAT | Data setup time                       | 250                 |      | 100                   |      | ns   |

| tsu;STA | The setup time in restart condition   | 4.7                 |      | 0.6                   |      | μs   |

| tsu;STO | Stop condition setup time             | 4.0                 |      | 0.6                   |      | μs   |

## Table 21.99 Multi-master I<sup>2</sup>C Bus Line

# 22.6 Timers

### 22.6.1 Timer A

### 22.6.1.1 Timer A (Timer Mode)

1. The timer remains idle after reset. Set the mode, count source, counter value, etc. using the TAiMR (i = 0 to 4) register and the TAi register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure the TAiMR register is modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. While counting is in progress, the counter value can be read out at any time by reading the TAi register. However, if the TAi register is read at the same time the counter is reloaded, the read value is always FFFF16. If the TAi register is read after setting a value in it, but before the counter starts counting, the read value is the one that has been set in the register.

- 3. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

#### 22.6.1.2 Timer A (Event Counter Mode)

The timer remains idle after reset. Set the mode, count source, counter value, etc. using the TAiMR (i = 0 to 4) register, the TAi register, the UDF register, bits TAZIE, TA0TGL, and TA0TGH in the ONSF register and the TRGSR register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure bits TAZIE, TA0TGL, and TA0TGH in the TAiMR register, the UDF register, the ONSF register, and the TRGSR register are modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. While counting is in progress, the counter value can be read out at any time by reading the TAi register. However, if the TAi register is read at the same time the counter is reloaded, the read value is always FFFF16 when the timer counter underflows and 000016 when the timer counter overflows. If the TAi register is read after setting a value in it, but before the counter starts counting, the read value is the one that has been set in the register.

- 3. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.