Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 16MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                 |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 71                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 12K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                      |

| Data Converters            | A/D 27x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30290fcvhp-u7a |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

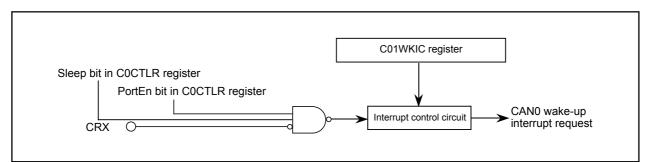

## 9.9 CAN0 Wake-up Interrupt

CAN0 wake-up interrupt occurs when a falling edge is input to CRX. The CAN0 wake-up interrupt is enabled when the PortEn bit is set to 1 (CTX/CRX function) and Sleep bit is set to 1(Sleep mode enabled) in the C0CTLR register. **Figure 9.13** shows the block diagram of the CAN0 wake-up interrupt.

Figure 9.13 CAN0 Wake-up Interrupt Block Diagram

## 9.10 Address Match Interrupt

An address match interrupt request is generated immediately before executing the instruction at the address indicated by the RMADi register (i=0 to 1). Set the start address of any instruction in the RMADi register. Use bits AIER1 and AIER0 in the AIER register to enable or disable the interrupt. Note that the address match interrupt is unaffected by the I flag and IPL. For address match interrupts, the value of the PC that is saved to the stack area varies depending on the instruction being executed (refer to "**Saving Registers**").

(The value of the PC that is saved to the stack area is not the correct return address.) Therefore, follow one of the methods described below to return from the address match interrupt.

• Rewrite the content of the stack and then use the REIT instruction to return.

• Restore the stack to its previous state before the interrupt request was accepted by using the POP or similar other instruction and then use a jump instruction to return.

**Table 9.6** shows the value of the PC that is saved to the stack area when an address match interrupt request is accepted.

aFigure 9.14 shows registers AIER, RMAD0, and RMAD1.

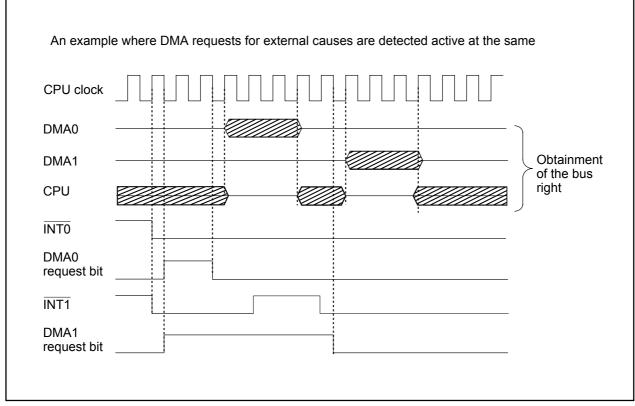

## 11.5 Channel Priority and DMA Transfer Timing

If both DMA0 and DMA1 are enabled and DMA transfer request signals from DMA0 and DMA1 are detected active in the same sampling period (one period from a falling edge to the next falling edge of CPU clock), the DMAS bit on each channel is set to 1 (DMA requested) at the same time. In this case, the DMA requests are arbitrated according to the channel priority, DMA0 > DMA1. The following describes DMAC operation when DMA0 and DMA1 requests are detected active in the same sampling period. **Figure 11.6** shows an example of DMA transfer effected by external factors.

DMA0 request having priority is received first to start a transfer when a DMA0 request and DMA1 request are generated simultaneously. After one DMA0 transfer is completed, a bus arbitration is returned to the CPU. When the CPU has completed one bus access, a DMA1 transfer starts. After one DMA1 transfer is completed, the bus arbitration is again returned to the CPU.

In addition, DMA requests cannot be counted up since each channel has one DMAS bit. Therefore, when DMA requests, as DMA1 in **Figure 11.6** occurs more than one time, the DAMS bit is set to 0 as soon as getting the bus arbitration. The bus arbitration is returned to the CPU when one transfer is completed.

Figure 11.6 DMA Transfer by External Factors

RENESAS

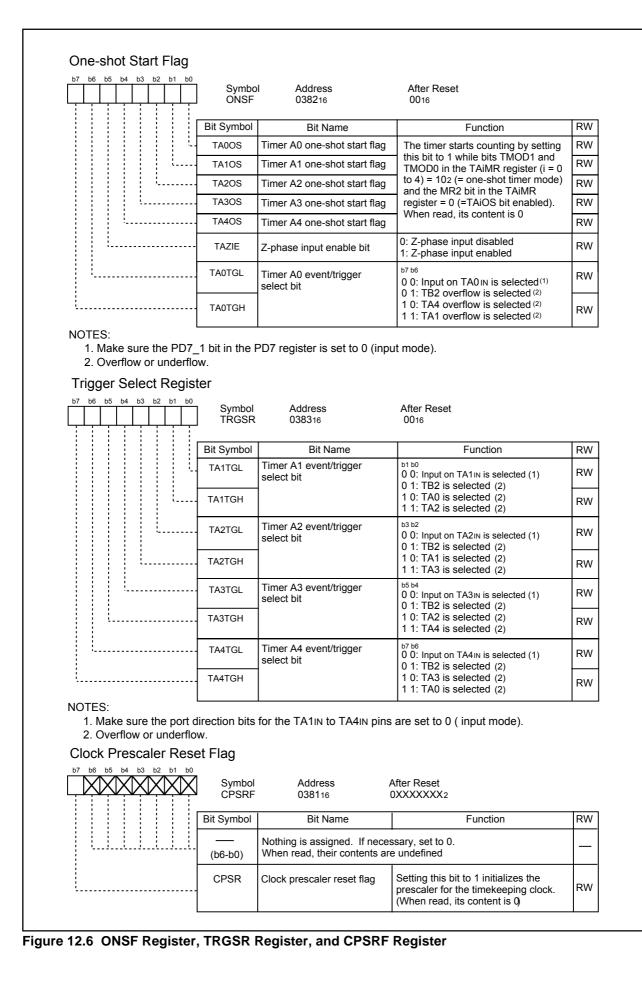

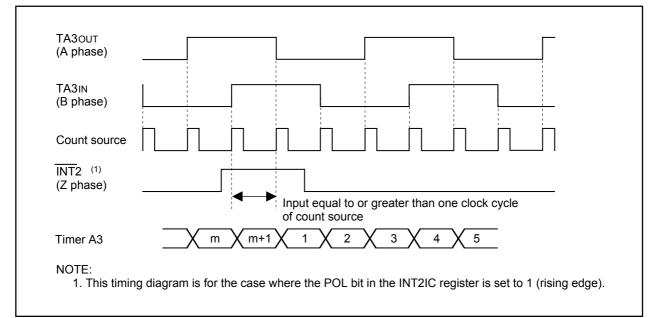

#### 12.1.2.1 Counter Initialization by Two-Phase Pulse Signal Processing

This function initializes the timer count value to 0 by Z-phase (counter initialization) input during twophase pulse signal processing.

This function can only be used in timer A3 event counter mode during two-phase pulse signal processing, free-running type, x4 processing, with Z-phase entered from the INT2 pin.

Counter initialization by Z-phase input is enabled by writing 000016 to the TA3 register and setting the TAZIE bit in ONSF register to 1 (Z-phase input enabled).

Counter initialization is accomplished by detecting Z-phase input edge. The active edge can be chosen to be the rising or falling edge by using the POL bit in the INT2IC register. The Z-phase pulse width applied to the INT2 pin must be equal to or greater than one clock cycle of the timer A3 count source.

The counter is initialized at the next count timing after recognizing Z-phase input. **Figure 12.10** shows the relationship between the two-phase pulse (A phase and B phase) and the Z phase.

If timer A3 overflow or underflow coincides with the counter initialization by Z-phase input, a timer A3 interrupt request is generated twice in succession. Do not use the timer A3 interrupt when using this function.

Figure 12.10 Two-phase Pulse (A phase and B phase) and the Z Phase

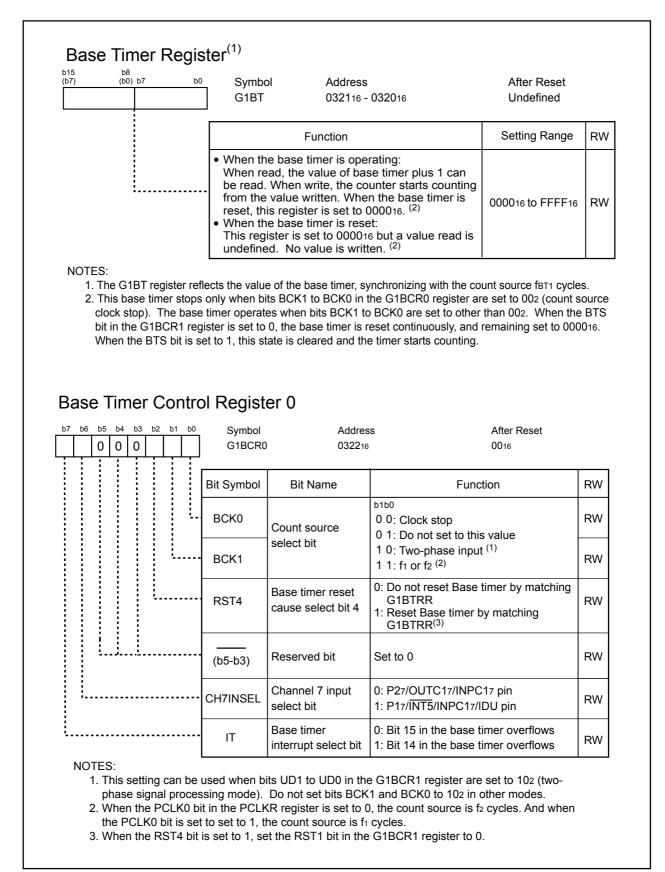

**Figures 13.2** to **13.10** show registers associated with the IC/OC base timer, the time measurement function, and the waveform generating function.

Figure 13.2 G1BT and G1BCR0 Registers

## 13.1 Base Timer

The base timer is a free-running counter that counts an internally generated count source.

Table 13.2 lists specifications of the base timer. Table 13.3 shows registers associated with the base timer. Figure 13.11 shows a block diagram of the base timer. Figure 13.12 shows an example of the base timer in counter increment mode. Figure 13.13 shows an example of the base timer in counter increment/decrement mode. Figure 13.14 shows an example of two-phase pulse signal processing mode.

| Item                       | Specification                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Count source(fBT1)         | f1 or f2 divided by $(n+1)$ , two-phase pulse input divided by $(n+1)$<br>n: determined by the DIV7 to DIV0 bits in the G1DV register. n=0 to 255<br>However, no division when n=0                                                                                                                   |  |  |  |

| Counting operation         | The base timer increments the counter value<br>The base timer increments/decrements the counter value<br>Two-phase pulse signal processing                                                                                                                                                           |  |  |  |

| Count start condition      | The BTS bit in the G1BCR1 register is set to 1 (base timer starts counting)                                                                                                                                                                                                                          |  |  |  |

| Count stop condition       | The BTS bit in the G1BCR1 register is set to 0 (base timer reset)                                                                                                                                                                                                                                    |  |  |  |

| Base timer reset condition | <ul> <li>(1) The value of the base timer matches the value of the G1BTRR register</li> <li>(2) The value of the base timer matches the value of G1PO0 register.</li> <li>(3) Apply a low-level signal ("L") to external interrupt pin, INT1 pin</li> </ul>                                           |  |  |  |

| Value for base timer reset | 000016                                                                                                                                                                                                                                                                                               |  |  |  |

| Interrupt request          | The base timer interrupt request is generated:<br>(1) When the bit 14 or bit 15 in the base timer overflows<br>(2) The value of the base timer value matches the value of the base timer<br>reset register                                                                                           |  |  |  |

| Read from timer            | <ul> <li>The G1BT register indicates a counter value while the base timer is running</li> <li>The G1BT register is undefined when the base timer is reset</li> </ul>                                                                                                                                 |  |  |  |

| Write to timer             | When a value is written while the base timer is running, the timer counter immediately starts counting from this value. No value can be written while the base timer is reset.                                                                                                                       |  |  |  |

| Selectable function        | Counter increment/decrement mode     The base timer starts counting from 000016. After incrementing to FFFF16,     the timer counter is then decremented back to 000016. The base timer     increments the counter value again when the timer counter reaches 000016.     (See <b>Figure 13.13</b> ) |  |  |  |

|                            | <ul> <li>Two-phase pulse processing mode<br/>Two-phase pulse signals from pins P80 and P81 are counted (See Figure<br/>13.14)</li> </ul>                                                                                                                                                             |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                      |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                      |  |  |  |

|                            | The timer increments<br>a counter on all edges The timer decrements<br>a counter on all edges                                                                                                                                                                                                        |  |  |  |

| Table 13.2 | Base Timer | Specifications |

|------------|------------|----------------|

|------------|------------|----------------|

RENESAS

## 14.1.6 Special Mode 4 (SIM Mode) (UART2)

Based on UART mode, this is an SIM interface compatible mode. Direct and inverse formats can be implemented, and this mode allows output of a low from the TxD2 pin when a parity error is detected. **Table 14.18** lists the specifications of SIM mode. **Table 14.19** lists the registers used in the SIM mode and the register values set.

| Item                             | Specification                                                                                   |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| Transfer data format             | Direct format                                                                                   |  |  |  |

|                                  | Inverse format                                                                                  |  |  |  |

| Transfer clock                   | The CKDIR bit in the U2MR register is set to 0 (internal clock) : fi/ (16(n+1))                 |  |  |  |

|                                  | fi = f1SIO, f2SIO, f8SIO, f32SIO. n: Setting value of U2BRG register 0016 to FF16               |  |  |  |

|                                  | • The CKDIR bit is set to 1 (external clock ): fEXT/16(n+1)                                     |  |  |  |

|                                  | fEXT: Input from CLK2 pin. n: Setting value of U2BRG register 0016 to FF16                      |  |  |  |

| Transmission start condition     | Before transmission can start, the following requirements must be met                           |  |  |  |

|                                  | <ul> <li>The TE bit in the U2C1 register is set to 1 (transmission enabled)</li> </ul>          |  |  |  |

|                                  | <ul> <li>The TI bit in the U2C1 register is set to 0 (data present in U2TB register)</li> </ul> |  |  |  |

| Reception start condition        | <ul> <li>Before reception can start, the following requirements must be met</li> </ul>          |  |  |  |

|                                  | <ul> <li>The RE bit in the U2C1 register is set to 1 (reception enabled)</li> </ul>             |  |  |  |

|                                  | - Start bit detection                                                                           |  |  |  |

| Interrupt request                | For transmission                                                                                |  |  |  |

| generation timing <sup>(2)</sup> | When the serial I/O finished sending data from the U2TB transfer register (U2IRS bit =1)        |  |  |  |

|                                  | For reception                                                                                   |  |  |  |

|                                  | When transferring data from the UART2 receive register to the U2RB register (at                 |  |  |  |

|                                  | completion of reception)                                                                        |  |  |  |

| Error detection                  | • Overrun error <sup>(1)</sup>                                                                  |  |  |  |

|                                  | This error occurs if the serial I/O started receiving the next data before reading the          |  |  |  |

|                                  | U2RB register and received the bit one before the last stop bit in the the next data            |  |  |  |

|                                  | Framing error                                                                                   |  |  |  |

|                                  | This error occurs when the number of stop bits set is not detected                              |  |  |  |

|                                  | Parity error                                                                                    |  |  |  |

|                                  | During reception, if a parity error is detected, parity error signal is output from the         |  |  |  |

|                                  | TxD2 pin.                                                                                       |  |  |  |

|                                  | During transmission, a parity error is detected by the level of input to the RxD2 pin           |  |  |  |

|                                  | when a transmission interrupt occurs                                                            |  |  |  |

|                                  | • Error sum flag                                                                                |  |  |  |

|                                  | This flag is set to 1 when any of the overrun, framing, and parity errors is encountered        |  |  |  |

| Table 14.18 | SIM Mode | Specifications |

|-------------|----------|----------------|

|-------------|----------|----------------|

NOTES:

- 1. If an overrun error occurs, bits 8 to 0 in the U2RB register are undefined. The IR bit in the S2RIC register remains unchanged.

- A transmit interrupt request is generated by setting the U2IRS bit in the U2C1 register to 1 (transmission complete) and U2ERE bit to 1 (error signal output) after reset. Therefore, when using SIM mode, be sure to clear the IR bit to 0 (no interrupt request) after setting these bits.

| b7 b6 | 5 b4 b | 3 b2 b | 1 b0 | Symbo<br>ADSTA                                       |                                                                                                                                                                                                                                                            | After res                              | set                                                                                                    |    |

|-------|--------|--------|------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------|----|

|       |        |        |      | Bit Symbol                                           | Bit Name                                                                                                                                                                                                                                                   |                                        | Function I                                                                                             | ٦W |

|       |        |        |      | ADERR0                                               | AN1 trigger status flag                                                                                                                                                                                                                                    | AN0<br>1: AN1                          | trigger did not occur during<br>conversion<br>trigger occured during<br>conversion                     | ٦W |

|       |        |        |      | ADERR1                                               | Conversion termination flag                                                                                                                                                                                                                                | 1: Conv                                | version not terminated<br>version terminated by f<br>er B0 underflow                                   | ٦W |

|       |        | L      |      | (b2)                                                 | Nothing is assigned. If nece When read, its content is 0                                                                                                                                                                                                   | essary, so                             | et to 0.                                                                                               |    |

|       |        |        |      | ADTCSF                                               | Delayed trigger sweep status flag                                                                                                                                                                                                                          |                                        | ep not in progress<br>ep in progress                                                                   | RO |

|       | ·      |        |      | ADSTT0                                               | AN0 conversion status flag                                                                                                                                                                                                                                 |                                        | conversion not in progress<br>conversion in progress                                                   | RO |

|       |        |        |      | ADSTT1                                               | AN1 conversion status flag                                                                                                                                                                                                                                 |                                        | conversion not in progress<br>conversion in progress                                                   | RO |

|       |        |        |      | ADSTRT0                                              | AN0 conversion<br>completion status flag                                                                                                                                                                                                                   |                                        | conversion not completed conversion completed                                                          | RW |

| l     |        |        |      | ADSTRT1                                              | AN1 conversion completion status flag                                                                                                                                                                                                                      |                                        | conversion not completed conversion completed                                                          | ٦W |

| A/D R |        | eri(i= | 0 to | AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7 | Address           03C116 to 03C016           03C316 to 03C216           03C516 to 03C416           03C716 to 03C616           03C916 to 03C816           03CD16 to 03C411           03CD16 to 03C410           03CF16 to 03C410           03CF16 to 03C410 | 5 l<br>5 l<br>5 l<br>5 l<br>6 l<br>6 l | After Reset<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined |    |

|       |        |        |      |                                                      |                                                                                                                                                                                                                                                            | Funct                                  | ion                                                                                                    | R  |

|       |        |        |      |                                                      | When the BITS bit in the Al register is 1 (10-bit mode)                                                                                                                                                                                                    | DCON1                                  | When the BITS bit in the ADCON1 register is 0 (8-bit mode)                                             | R  |

|       |        |        |      | L.                                                   | Eight low-order bits of A/D conversion result                                                                                                                                                                                                              |                                        | A/D conversion result                                                                                  | R  |

|       |        |        |      |                                                      | Two high-order bits of<br>A/D conversion result                                                                                                                                                                                                            |                                        | When read, its content is<br>undefined                                                                 | R  |

|       |        |        |      |                                                      |                                                                                                                                                                                                                                                            |                                        |                                                                                                        |    |

Figure 15.4 ADSTAT0 Register and AD0 to AD7 Registers

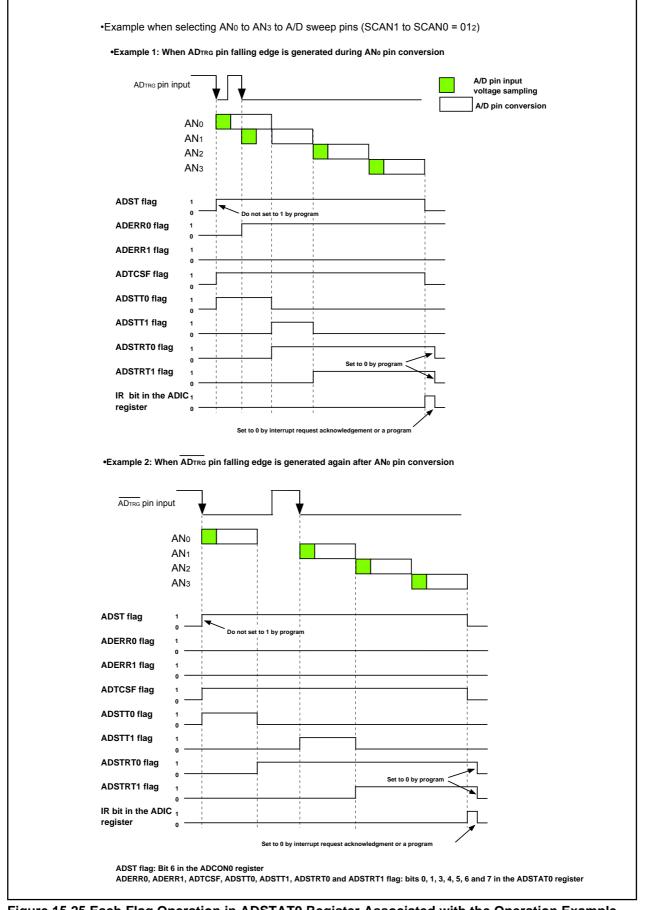

Figure 15.25 Each Flag Operation in ADSTAT0 Register Associated with the Operation Example in Delayed Trigger Mode 1 (1)

RENESAS

## 16.7.1 Bit0: Time-Out Detection Function Enable Bit (TOE)

The TOE bit enables the time-out detection function. When the TOE bit is set to 1, time-out is detected and the  $I^2C$  bus interface interrupt request is generated when the following conditions are met.

1) the BB flag in the S10 register is set to 1 (bus busy)

2) the SCL clock stops for time-out detection period while high-level ("H") signal is maintained (see **Table 16.7**)

The internal counter measures the time-out detection time and the TOSEL bit selects between two modes, long time and short time. When time-out is detected, set the ES0 bit to 0 (I<sup>2</sup>C bus interface disabled) and reset the counter.

## 16.7.2 Bit1: Time-Out Detection Flag (TOF)

The TOF flag indicates the time-out detection. If the internal counter which measures the time-out period overflows, the TOF flag is set to 1 and the  $I^2C$  bus interface interrupt request is generated at the same time.

## 16.7.3 Bit2: Time-Out Detection Period Select Bit (TOSEL)

The TOSEL bit selects time-out detection period from long time mode and short time mode. When the TOSEL bit is set to 0, long time mode is selected. When it is set to 1, short time mode is selected, respectively. The internal counter increments as a 16-bit counter in long time mode, while the counter increments as a 14-bit counter in short time mode, based on the I<sup>2</sup>C system clock (VIIC) as a counter source. **Table 16.7** shows examples of time-out detection period.

|           | Time-out Detection Teriou | (onit: ms)      |

|-----------|---------------------------|-----------------|

| VIIC(MHz) | Long time mode            | Short time mode |

| 4         | 16.4                      | 4.1             |

| 2         | 32.8                      | 8.2             |

| 1         | 65.6                      | 16.4            |

Table 16.7 Examples of Time-out Detection Period (Unit: ms)

## 16.7.4 Bits 3,4,5: I<sup>2</sup>C System Clock Select Bits (ICK2-4)

Bits ICK4 to ICK2, and bits ICK1 and ICK0 in the S3D0 register, and the PCLK0 bit in the PCLKR register select the system clock (VIIC) of the  $I^2$ C bus interface circuit. See **Table 16.6** for the setting values.

## 16.7.5 Bit7: STOP Condition Detection Interrupt Request Bit (SCPIN)

The SCPIN bit monitors the stop condition detection interrupt. The SCPIN bit is set to 1 when the  $I^2C$  bus interface interrupt is generated by detecting the STOP condition. When this bit is set to 0 by program, it becomes 0. However, no change occurs even if it is set to 1.

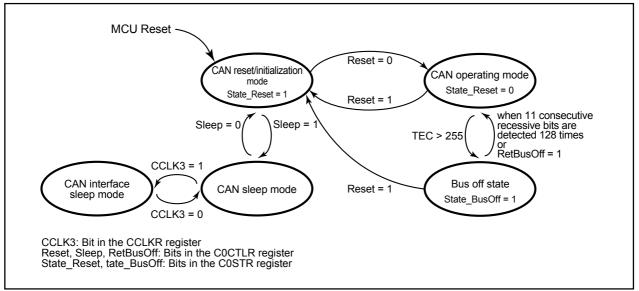

### **17.2 Operating Modes**

The CAN module has the following four operating modes.

- CAN Reset/Initialization Mode

- CAN Operating Mode

- CAN Sleep Mode

- CAN Interface Sleep Mode

Figure 17.17 shows transition between operating modes.

Figure 17.17 Transition Between Operating Modes

### 17.2.1 CAN Reset/Initialization Mode

The CAN reset/initialization mode is activated upon MCU reset or by setting the Reset bit in the C0CTLR register to 1. If the Reset bit is set to 1, check that the State\_Reset bit in the C0STR register is set to 1. Entering the CAN reset/initialization mode initiates the following functions by the module:

- CAN communication is impossible.

- When the CAN reset/initialization mode is activated during an ongoing transmission in operation mode, the module suspends the mode transition until completion of the transmission (successful, arbitration loss, or error detection). Then, the State\_Reset bit is set to 1, and the CAN reset/ initialization mode is activated.

- Registers COMCTLj (j = 0 to 15), COSTR, COICR, COIDR, CORECR, COTECR, and COTSR are initialized. All these registers are locked to prevent CPU modification.

- Registers C0CTLR, C0CONR, C0GMR, C0LMAR, and C0LMBR and the CAN0 message box retain their contents and are available for CPU access.

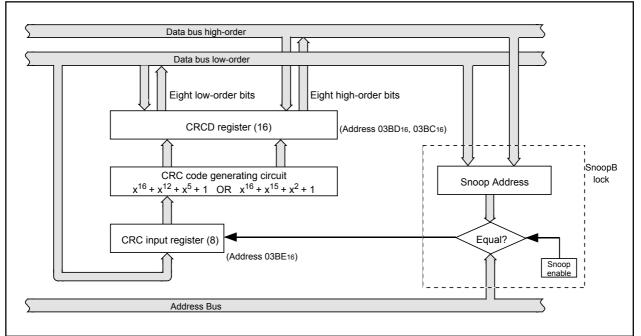

# **18. CRC Calculation Circuit**

The Cyclic Redundancy Check (CRC) calculation detects errors in blocks of data. The MCU uses a generator polynomial of CRC\_CCITT ( $X^{16} + X^{12} + X^5 + 1$ ) or CRC-16 ( $X^{16} + X^{15} + X^2 + 1$ ) to generate CRC code.

The CRC code is a 16-bit code generated for a block of a given data length in multiples of bytes. The code is updated in the CRC data register everytime one byte of data is transferred to a CRC input register. The data register must be initialized before use. Generation of CRC code for one byte of data is completed in two machine cycles.

**Figure 18.1** shows the block diagram of the CRC circuit. **Figure 18.2** shows the CRC-related registers. **Figure 18.3** shows the calculation example using the CRC\_CCITT operation.

## 18.1 CRC Snoop

The CRC circuit includes the ability to snoop reads and writes to certain SFR addresses. This can be used to accumulate the CRC value on a stream of data without using extra bandwidth to explicitly write data into the CRCIN register. All SFR addresses after 002016 are subject to the CRC snoop. The CRC snoop is useful to snoop the writes to a UART TX buffer, or the reads from a UART RX buffer.

To snoop an SFR address, the target address is written to the CRC snoop Address Register (CRCSAR). The two most significant bits of this register enable snooping on reads or writes to the target address. If the target SFR is written to by the CPU or DMA, and the CRC snoop write bit is set (CRCSW=1), the CRC will latch the data into the CRCIN register. The new CRC code will be set in the CRCD register.

Similarly, if the target SFR is read by the CRC or DMA, and the CRC snoop read bit is set (CRCSR=1), the CRC will latch the data from the target into the CRCIN register and calculate the CRC.

The CRC circuit can only calculate CRC codes on data byte at a time. Therefore, if a target SFR is accessed in word (16 bit), only one low-order byte data is stored into the CRCIN register.

Figure 18.1 CRC circuit block diagram

## 19.5 Pin Assignment Control Register (PACR)

**Figure 19.10** shows the PACR register. After reset, set bits PACR2 to PACR0 in the PACR register before a signal is input or output to each pin. When bits PACR2 to PACR0 are not set, some pins do not function as I/O ports.

Bits PACR2 to PACR0: control pins to be used

Value after reset: 0002.

To select the 80-pin package, set the bits to 0112.

To select the 64-pin package, set the bits to 0102.

U1MAP bit: controls pin assignments for the UART1 function.

To assign the UART1 function to P64/CTS1/RTS1, P65/CLK1, P66/RxD1, and P67/TxD1, set the U1MAP bit to 0 (P67 to P64).

To assign the function to P70/CTS1/RTS1, P71/CLK1, P72/RxD1, and P73/TxD1, set the U1MAP bit to 1 (P73 to P70)

The PRC2 bit in the PRCR protects the PACR register. Set the PACR register after setting the PRC2 bit in the PRCR register.

## **19.6 Digital Debounce Function**

Two digital debounce function circuits are provided. Level is determined when level is held, after applying either a falling edge or rising edge to the pin, longer than the programmed filter width time. This enables noise reduction.

This function is assigned to INT5/INPC17 and NMI/SD. Digital filter width is set in the NDDR register and the P17DDR register respectively. **Figure 19.11** shows the NDDR register and the P17DDR register. Additionally, a digital debounce function is disabled to the port P17 input and the port P85 input.

Filter width : (n+1) x 1/f8 n: count value set in the NDDR register and P17DDR register

The NDDR register and the P17DDR register decrement count value with f8 as the count source. The NDDR register and the P17DDR register indicate count time. Count value is reloaded if a falling edge or a rising edge is applied to the pin.

The NDDR register and the P17DDR register can be set 0016 to FF16 when using the digital debounce function. Setting to FF16 disables the digital filter. See **Figure 19.12** for details.

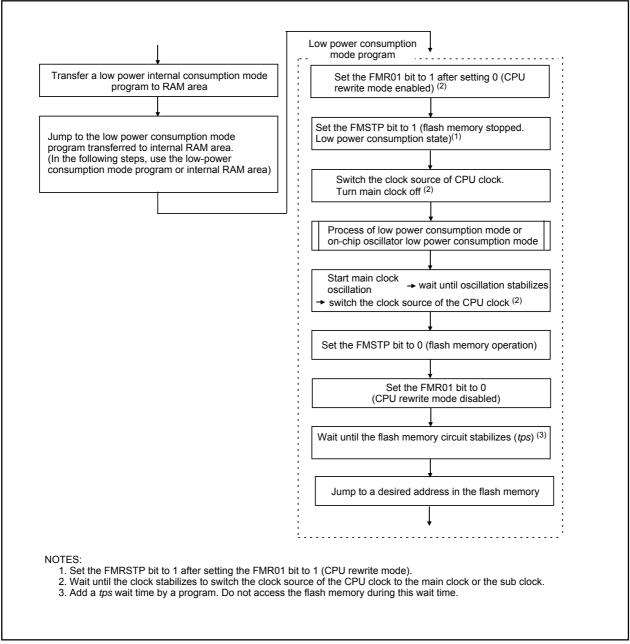

Figure 20.10 Processing Before and After Low Power Dissipation Mode

| Symbol  |                             | Parameter                                                                                                                                        |                                                                                                                             | Condition                                                 | Standard        |         |      | Unit |          |

|---------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|---------|------|------|----------|

| Symbol  |                             | Fala                                                                                                                                             | netei                                                                                                                       |                                                           | Condition       | Min.    | Тур. | Max. | - 0mit   |

| Vон     |                             | P00 to P07, P10 to P17, F<br>P70 to P77, P80 to P87, F                                                                                           |                                                                                                                             | 7, P30 to P37, P60 to P67,<br>3, P95 to P97, P100 to P107 | lон= -1 mA      | Vcc-0.5 |      | Vcc  | V        |

|         | Output High (               |                                                                                                                                                  | Хол                                                                                                                         | High Power                                                | Iон= -0.1 mA    | Vcc-0.5 |      | Vcc  | v        |

| Vон     | Output High (               | п) voltage                                                                                                                                       | <b>N</b> 001                                                                                                                | Low Power                                                 | Іон= -50 μА     | Vcc-0.5 |      | Vcc  |          |

| VOH     | Outrout Librah (            |                                                                                                                                                  | N                                                                                                                           | High Power                                                | No load applied |         | 2.5  |      |          |

|         | Output High (               | "H") Voltage                                                                                                                                     | Xcour                                                                                                                       | Low Power                                                 | No load applied |         | 1.6  |      | V        |

| Val     | Output Low<br>("L") Voltage | P00 to P07, P10 to P17, F<br>P70 to P77, P80 to P87, F                                                                                           |                                                                                                                             | r, P30 to P37, P60 to P67,<br>3, P95 to P97, P100 to P107 | lo∟= 1 mA       |         |      | 0.5  | V        |

|         |                             |                                                                                                                                                  |                                                                                                                             | High Power                                                | lo∟= 0.1 mA     |         |      | 0.5  | <b>.</b> |

|         | Output Low ('               | "L") Voltage                                                                                                                                     | Xour                                                                                                                        | Low Power                                                 | IoL = 50 μA     |         |      | 0.5  | V        |

| Vol     |                             |                                                                                                                                                  |                                                                                                                             | High Power                                                | No load applied |         | 0    |      | <u> </u> |

|         | Output Low ('               | 'L") Voltage                                                                                                                                     | Xcour                                                                                                                       | Low Power                                                 | No load applied |         | 0    |      | - V      |

| Vt+-Vt- | Hysteresis                  | TAOIN-TA4IN, TBOIN-TB2IN, INTO-INT5, NMI, ADTRG, CTS0-<br>CTS2, SCL, SDA, CLK0-CLK2, TA20JT-TA40JT, KI0-KI3, RX00-<br>RX02, SIN3, SIN4           |                                                                                                                             |                                                           |                 |         |      | 0.8  | V        |

| Vt+-Vt- | Hysteresis                  | RESET                                                                                                                                            |                                                                                                                             |                                                           |                 |         |      | 1.8  | V        |

| Vt+-Vt- | Hysteresis                  | XIN                                                                                                                                              |                                                                                                                             |                                                           |                 |         |      | 0.8  | V        |

| Іін     | Input High<br>("H") Current | P00 to P07, P10 to P17, F<br>P70 to P77, P80 to P87, F<br>XIN, RESET, CNVss                                                                      | VI= 3 V                                                                                                                     |                                                           |                 | 4.0     | μA   |      |          |

| lı.     | Input Low<br>("L") Current  | P00 to P07, P10 to P17, P20 to P27, P30 to P37, P60 to P67,<br>P70 to P77, P80 to P87, P90 to P93, P95 to P97, P100 to P107<br>XIN, RESET, CNVss |                                                                                                                             |                                                           | V1= 0 V         |         |      | -4.0 | μA       |

| Rpullup | Pull-up<br>Resistance       |                                                                                                                                                  | P00 to P07, P10 to P17, P20 to P27, P30 to P37, P60 to P67,<br>P70 to P77, P80 to P87, P90 to P93, P95 to P97, P100 to P107 |                                                           | V1= 0 V         | 50      | 100  | 500  | kΩ       |

| Rfxin   | Feedback Re                 | sistance                                                                                                                                         | Xin                                                                                                                         |                                                           |                 |         | 3.0  |      | MΩ       |

| Rfxcin  | Feedback Re                 | sistance                                                                                                                                         | XCIN                                                                                                                        |                                                           |                 |         | 25   |      | MΩ       |

| VRAM    | RAM Standby                 | / Voltage                                                                                                                                        | I.                                                                                                                          |                                                           | In stop mode    | 2.0     |      |      | V        |

#### Table 21.24 Electrical Characteristics (Note 1)

# Vcc = 3V

NOTE:

1. Referenced to V $\infty$  = 2.7 to 3.6 V, V $\otimes$  = 0 V at Topr = -20 to 85 ° C / -40 to 85 ° C, f(BCLK) = 10MHz unless otherwise specified.

#### **Timing Requirements**

# Vcc = 3V

(VCC = 3V, VSS = 0V, at Topr = -20 to  $85^{\circ}$ C / -40 to  $85^{\circ}$ C unless otherwise specified)

| Table 21.26 External Clock Input (XIN input) |

|----------------------------------------------|

|----------------------------------------------|

| Symbol | Baramatar                             |      | Standard |      |  |

|--------|---------------------------------------|------|----------|------|--|

| Symbol | Parameter                             | Min. | Max.     | Unit |  |

| tc     | External clock input cycle time       | 100  |          | ns   |  |

| tw(H)  | External clock input HIGH pulse width | 40   |          | ns   |  |

| tw(L)  | External clock input LOW pulse width  | 40   |          | ns   |  |

| tr     | External clock rise time              |      | 18       | ns   |  |

| tf     | External clock fall time              |      | 18       | ns   |  |

#### **Timing Requirements**

## Vcc = 3V

#### (VCC = 3V, VSS = 0V, at Topr = - 20 to 85°C / - 40 to 85°C unless otherwise specified)

| Table 21.33 | 3 Timer B Input (Counter Input in Event Counter Mod | e) |

|-------------|-----------------------------------------------------|----|

|-------------|-----------------------------------------------------|----|

| Symbol  | Parameter                                           | Stan | Unit |      |

|---------|-----------------------------------------------------|------|------|------|

|         | Parameter                                           | Min. | Max. | Unit |

| tc(TB)  | TBin input cycle time (counted on one edge)         | 150  |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on one edge)   | 60   |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on one edge)    | 60   |      | ns   |

| tc(TB)  | TBin input cycle time (counted on both edges)       | 300  |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on both edges) | 120  |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on both edges)  | 120  |      | ns   |

#### Table 21.34 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                   | Standard |      | Unit |

|---------|-----------------------------|----------|------|------|

| Symbol  | Falameter                   | Min.     | Max. | Unit |

| tc(TB)  | TBin input cycle time       | 600      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width | 300      |      | ns   |

| tw(TBL) | TBin input LOW pulse width  | 300      |      | ns   |

#### Table 21.35 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Symbol Parameter             | Standard |      | Unit |

|---------|------------------------------|----------|------|------|

| Gymbol  |                              | Min.     | Max. | Unit |

| tc(TB)  | TBin input cycle time        | 600      |      | ns   |

| tw(TBH) | TBiin input HIGH pulse width | 300      |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 300      |      | ns   |

#### Table 21.36 A/D Trigger Input

| Symbol  | Parameter                                     | Standard |      | Unit |

|---------|-----------------------------------------------|----------|------|------|

| Symbol  |                                               | Min.     | Max. |      |

| tc(AD)  | ADTRG input cycle time (trigger able minimum) | 1500     |      | ns   |

| tw(ADL) | ADTRG input LOW pulse width                   | 200      |      | ns   |

#### Table 21.37 Serial I/O

| Symbol   | Parameter                   | Standard |      | Unit |

|----------|-----------------------------|----------|------|------|

|          | Falanielei                  | Min.     | Max. | Unit |

| tc(CK)   | CLKi input cycle time       | 300      |      | ns   |

| tw(CKH)  | CLKi input HIGH pulse width | 150      |      | ns   |

| tw(CKL)  | CLKi input LOW pulse width  | 150      |      | ns   |

| td(C-Q)  | TxDi output delay time      |          | 160  | ns   |

| th(C-Q)  | TxDi hold time              | 0        |      | ns   |

| tsu(D-C) | RxDi input setup time       | 100      |      | ns   |

| th(C-D)  | RxDi input hold time        | 90       |      | ns   |

#### Table 21.38 External Interrupt INTi Input

| Symbol  | Symbol Parameter            | Standard |      | Unit |

|---------|-----------------------------|----------|------|------|

| Gymbol  |                             | Min.     | Max. | Unit |

| tw(INH) | INTi input HIGH pulse width | 380      |      | ns   |

| tw(INL) | INTi input LOW pulse width  | 380      |      | ns   |

Vcc = 3V

#### **Timing Requirements**

#### (VCC = 3V, VSS = 0V, at Topr = - 40 to 85°C unless otherwise specified)

#### Table 21.71 Timer B Input (Counter Input in Event Counter Mode)

| Symbol  | Deremeter                                           | Standard |      | Linit |

|---------|-----------------------------------------------------|----------|------|-------|

| Symbol  | Parameter                                           | Min.     | Max. | Unit  |

| tc(TB)  | TBin input cycle time (counted on one edge)         | 150      |      | ns    |

| tw(TBH) | TBin input HIGH pulse width (counted on one edge)   | 60       |      | ns    |

| tw(TBL) | TBin input LOW pulse width (counted on one edge)    | 60       |      | ns    |

| tc(TB)  | TBin input cycle time (counted on both edges)       | 300      |      | ns    |

| tw(TBH) | TBin input HIGH pulse width (counted on both edges) | 120      |      | ns    |

| tw(TBL) | TBin input LOW pulse width (counted on both edges)  | 120      |      | ns    |

#### Table 21.72 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Standard |      | Unit |

|---------|------------------------------|----------|------|------|

| Symbol  | Falameter                    | Min.     | Max. |      |

| tc(TB)  | TBin input cycle time        | 600      |      | ns   |

| tw(TBH) | TBilN input HIGH pulse width | 300      |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 300      |      | ns   |

#### Table 21.73 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                    | Standard |      | Unit |

|---------|------------------------------|----------|------|------|

| Symbol  |                              | Min.     | Max. | Unit |

| tc(TB)  | TBiin input cycle time       | 600      |      | ns   |

| tw(TBH) | TBiin input HIGH pulse width | 300      |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 300      |      | ns   |

#### Table 21.74 A/D Trigger Input

| Symbol  | Parameter                                     | Standard |      | Unit |

|---------|-----------------------------------------------|----------|------|------|

| Gymbol  | i didificici                                  | Min.     | Max. | Unit |

| tc(AD)  | ADTRG input cycle time (trigger able minimum) | 1500     |      | ns   |

| tw(ADL) | ADTRG input LOW pulse width                   | 200      |      | ns   |

#### Table 21.75 Serial I/O

| Symbol   | Parameter                   | Standard |      | Unit |

|----------|-----------------------------|----------|------|------|

| Symbol   | Falameter                   | Min.     | Max. | Unit |

| tc(CK)   | CLKi input cycle time       | 300      |      | ns   |

| tw(CKH)  | CLKi input HIGH pulse width | 150      |      | ns   |

| tw(CKL)  | CLKi input LOW pulse width  | 150      |      | ns   |

| td(C-Q)  | TxDi output delay time      |          | 160  | ns   |

| th(C-Q)  | TxDi hold time              | 0        |      | ns   |

| tsu(D-C) | RxDi input setup time       | 100      |      | ns   |

| th(C-D)  | RxDi input hold time        | 90       |      | ns   |

#### Table 21.76 External Interrupt INTi Input

| Symbol Parameter | Parameter                   | Standard |      | Unit |

|------------------|-----------------------------|----------|------|------|

| Symbol           |                             | Min.     | Max. |      |

| tw(INH)          | INTi input HIGH pulse width | 380      |      | ns   |

| tw(INL)          | INTi input LOW pulse width  | 380      |      | ns   |

## 22.12 Programmable I/O Ports

- 1. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the P72 to P75, P80 and P81 pins go to a high-impedance state.

- 2. The input threshold voltage of pins differs between programmable input/output ports and peripheral functions.

Therefore, if any pin is shared by a programmable input/output port and a peripheral function and the input level at this pin is outside the range of recommended operating conditions VIH and VIL (neither "high" nor "low"), the input level may be determined differently depending on which side—the programmable input/output port or the peripheral function—is currently selected.

- 3.When the SM32 bit in the S3C register is set to 1, the P32 pin goes to high-impedance state. When the SM42 bit in the S4C register is set to 1, the P96 pin goes to high-impedance state.

- 4. When the INV03 bit in the INVC0 register is 1(three-phase motor control timer output enabled), an "L" input on the P85 /NMI/SD pin, has the following effect.

- •When the TB2SC register IVPCR1 bit is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the U/  $\overline{U}$ / V/  $\overline{V}$ / W/  $\overline{W}$  pins go to a high-impedance state.

- •When the TB2SC register IVPCR1 bit is set to 0 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin disabled), the U/  $\overline{U}$ / V/  $\overline{V}$ / W/  $\overline{W}$  pins go to a normal port.

Therefore, the P85 pin can not be used as programmable I/O port when the INV03 bit is set to 1. When the  $\overline{SD}$  function isn't used, set to 0 (Input) in PD85 and pullup to H in the P85  $\overline{\text{/NMI/SD}}$  pin from outside.