#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                              |

| Number of I/O              | 55                                                                              |

| Program Memory Size        | 96KB (96K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fahp-u5a |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Quick Reference to Pages Classified by Address

| Address                                                                                | Register                                                             | Symbol | Page       | Address                                                                      | Register                                                             | Symbol | Page       |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|------------|

| 008016<br>008116<br>008216<br>008316<br>008416<br>008516                               | CAN0 message box 2: Identifier/DLC                                   |        | 289        | 00C016<br>00C116<br>00C216<br>00C316<br>00C416<br>00C516                     | CAN0 message box 6: Identifier/DLC                                   |        | 289        |

| 008616<br>008716<br>008816<br>008916<br>008A16<br>008B16<br>008C16<br>008D16           | CAN0 message box 2: Data field                                       |        | 289        | 00C616<br>00C716<br>00C816<br>00C916<br>00CA16<br>00CB16<br>00CC16<br>00CC16 | CAN0 message box 6: Data field                                       |        | 289        |

| 008E16<br>008F16                                                                       | CAN0 message box 2: time stamp                                       |        | 289        | 00CE16<br>00CF16                                                             | CAN0 message box 6: time stamp                                       |        | 289        |

| 009016<br>009116<br>009216<br>009316<br>009416<br>009516                               | CAN0 message box 3: Identifier/DLC                                   |        | 289        | 00D016<br>00D116<br>00D216<br>00D316<br>00D416<br>00D516                     | CAN0 message box 7: Identifier/DLC                                   |        | 289        |

| 009616<br>009716<br>009816<br>009916<br>009A16<br>009B16<br>009C16<br>009D16           | CAN0 message box 3: Data field                                       |        | 289        | 00D616<br>00D716<br>00D816<br>00D916<br>00DA16<br>00DB16<br>00DC16<br>00DD16 | CAN0 message box 7: Data field                                       |        | 289        |

| 009E16<br>009F16<br>00A016<br>00A116<br>00A216<br>00A316<br>00A416                     | CAN0 message box 3: time stamp<br>CAN0 message box 4: Identifier/DLC |        | 289<br>289 | 00DE16<br>00DF16<br>00E016<br>00E116<br>00E216<br>00E316<br>00E416           | CAN0 message box 7: time stamp<br>CAN0 message box 8: Identifier/DLC |        | 289<br>289 |

| 00A516<br>00A616<br>00A716<br>00A816<br>00A916<br>00AA16<br>00AB16<br>00AC16<br>00AD16 | CAN0 message box 4: Data field                                       |        | 289        | 00E516<br>00E616<br>00E716<br>00E816<br>00E916<br>00EA16<br>00EB16<br>00EC16 | CAN0 message box 8: Data field                                       |        | 289        |

| 00AE16<br>00AF16                                                                       | CAN0 message box 4: time stamp                                       |        | 289        | 00EE16<br>00EF16                                                             | CAN0 message box 8: time stamp                                       |        | 289        |

| 00B016<br>00B116<br>00B216<br>00B316<br>00B416<br>00B516                               | CAN0 message box 5: Identifier/DLC                                   |        | 289        | 00F016<br>00F116<br>00F216<br>00F316<br>00F416<br>00F516                     | CAN0 message box 9: Identifier/DLC                                   |        | 289        |

| 008616<br>008716<br>008816<br>008916<br>008A16<br>008A16<br>008B16<br>008C16           | CAN0 message box 5: Data field                                       |        | 289        | 00F616<br>00F716<br>00F816<br>00F916<br>00FA16<br>00FB16<br>00FC16<br>00FC16 | CAN0 message box 9: Data field                                       |        | 289        |

| 00BE16<br>00BF16                                                                       | CAN0 message box 5: time stamp                                       |        | 289        | 00FE16<br>00FF16                                                             | CAN0 message box 9: time stamp                                       |        | 289        |

Note: The blank areas are reserved and cannot be accessed by users.

As of March. 2007

### **1.3 Product List**

Tables 1.3 to 1.5 list the M16C/29 Group products and Figure 1.3 shows the type numbers, memory sizes and packages. Tables 1.6 to 1.8 list the product code of flash memory version for M16C/29 Group. Figure 1.4 to Figure 1.6 show the marking diagram of flash memory version for M16C/29 Group.

|                |                 |                 |                        |         | ai 011, 2007    |

|----------------|-----------------|-----------------|------------------------|---------|-----------------|

| Type Number    | ROM<br>Capacity | RAM<br>Capacity | Package Type           | Remarks | Product<br>Code |

| M30290FAHP     | 96 K + 4 K      | 8 K             | PLQP0080KB-A (80P6Q-A) |         |                 |

| M30290FCHP     | 128 K + 4 K     | 12 K            |                        | Flash   | U3, U5,         |

| M30291FAHP     | 96 K + 4 K      | 8 K             | PLQP0064KB-A (64P6Q-A) | Memory  | U7, U9          |

| M30291FCHP     | 128 K + 4 K     | 12 K            | FLQF0004KB-A (04F0Q-A) |         |                 |

| M30290M8-XXXHP | 64 K            | 4 K             |                        |         |                 |

| M30290MA-XXXHP | 96 K            | 8 K             | PLQP0080KB-A (80P6Q-A) |         |                 |

| M30290MC-XXXHP | 128 K           | 12 K            |                        | Flash   | U3, U5          |

| M30291M8-XXXHP | 64 K            | 4 K             |                        | ROM     | 03, 05          |

| M30291MA-XXXHP | 96 K            | 8 K             | PLQP0064KB-A (64P6Q-A) |         |                 |

| M30291MC-XXXHP | 128 K           | 12 K            |                        |         |                 |

### Table 1.3 Product List (1) -Normal Version

### Table 1.4 Product List (2) -T Version

| Table 1.4 Product List (2) | T Version       |                 |                          | As of M | arch, 2007      |

|----------------------------|-----------------|-----------------|--------------------------|---------|-----------------|

| Type Number                | ROM<br>Capacity | RAM<br>Capacity | Package Type             | Remarks | Product<br>Code |

| M30290FATHP                | 96 K + 4 K      | 8 K             | PLQP0080KB-A (80P6Q-A)   |         |                 |

| M30290FCTHP                | 128 K + 4 K     | 12 K            |                          | Flash   | U3, U5,         |

| M30291FATHP                | 96 K + 4 K      | 8 K             |                          | Memory  | U7, U9          |

| M30291FCTHP                | 128 K + 4 K     | 12 K            | - PLQP0064KB-A (64P6Q-A) |         |                 |

| M30290M8T-XXXHP            | 64 K            | 4 K             |                          |         |                 |

| M30290MAT-XXXHP            | 96 K            | 8 K             | PLQP0080KB-A (80P6Q-A)   |         |                 |

| M30290MCT-XXXHP            | 128 K           | 12 K            |                          | Mask    | UO              |

| M30291M8T-XXXHP            | 64 K            | 4 K             |                          | ROM     | 00              |

| M30291MAT-XXXHP            | 96 K            | 8 K             | PLQP0064KB-A (64P6Q-A)   |         |                 |

| M30291MCT-XXXHP            | 128 K           | 12 K            | 1                        |         |                 |

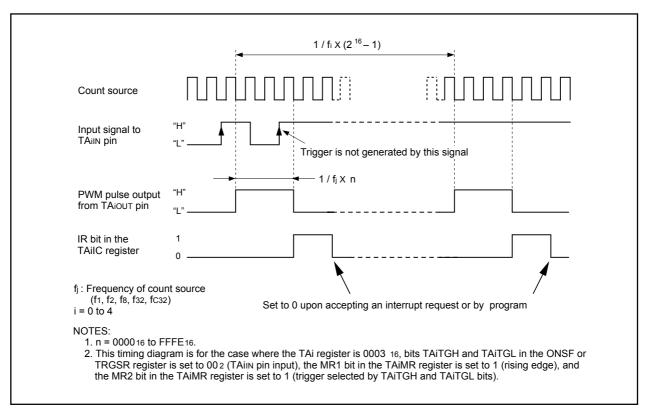

Figure 12.13 Example of 16-bit Pulse Width Modulator Operation

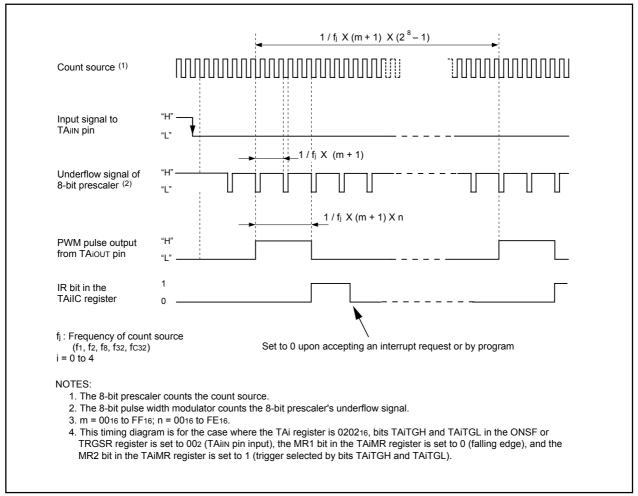

Figure 12.14 Example of 8-bit Pulse Width Modulator Operation

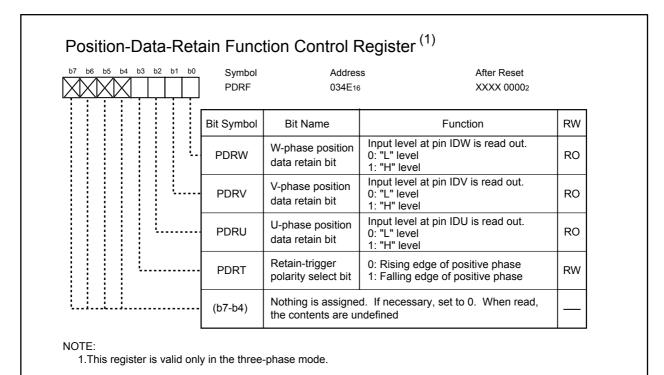

### 12.3.1.2 Position-data-retain Function Control Register

Figure 12.36 shows the structure of the position-data-retain function contol register.

Figure 12.36 PDRF Register

### 12.3.1.2.1 W-phase Position Data Retain Bit (PDRW)

This bit is used to retain the input level at pin IDW.

### 12.3.1.2.2 V-phase Position Data Retain Bit (PDRV)

This bit is used to retain the input level at pin IDV.

### 12.3.1.2.3 U-phase Position Data Retain Bit (PDRU)

This bit is used to retain the input level at pin IDU.

### 12.3.1.2.4 Retain-trigger Polarity Select Bit (PDRT)

This bit is used to select the trigger polarity to retain the position data. When this bit is set to 0, the rising edge of each positive phase selected. When this bit is set to 1, the falling edge of each pocitive phase selected.

### 14.1.1 Clock Synchronous serial I/O Mode

The clock synchronous serial I/O mode uses a transfer clock to transmit and receive data. **Table 14.1** lists the specifications of the clock synchronous serial I/O mode. **Table 14.2** lists the registers used in clock synchronous serial I/O mode and the register values set.

Table 14.1 Clock Synchronous Serial I/O Mode Specifications

| Item                            | Specification                                                                                               |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|

| Transfer data format            | Transfer data length: 8 bits                                                                                |

| Transfer clock                  | • The CKDIR bit in the UiMR(i=0 to 2) register is set to 0 (internal clock) : fj/ (2(n+1))                  |

|                                 | fj = f1SIO, f2SIO, f8SIO, f32SIO. n: Setting value of UiBRG register 0016 to FF16                           |

|                                 | • CKDIR bit is set to 1 (external clock ): Input from CLKi pin                                              |

| Transmission, reception control | Selectable from CTS function, RTS function or CTS/RTS function disable                                      |

| Transmission start condition    | <ul> <li>Before transmission can start, the following requirements must be met <sup>(1)</sup></li> </ul>    |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                        |

|                                 | – The TI bit in the UiC1 register is set to 0 (data present in UiTB register)                               |

|                                 | – If $\overline{\text{CTS}}$ function is selected, input on the $\overline{\text{CTS}}$ i pin is set to "L" |

| Reception start condition       | Before reception can start, the following requirements must be met <sup>(1)</sup>                           |

|                                 | – The RE bit in the UiC1 register is set to 1 (reception enabled)                                           |

|                                 | – The TE bit in the UiC1 register is set to 1 (transmission enabled)                                        |

|                                 | - The TI bit in the UiC1 register is set to 0 (data present in the UiTB register)                           |

| Interrupt request               | For transmission, one of the following conditions can be selected                                           |

| generation timing               | – The UiIRS bit <sup>(3)</sup> is set to 0 (transmit buffer empty): when transferring data from the         |

|                                 | UiTB register to the UARTi transmit register (at start of transmission)                                     |

|                                 | - The UiIRS bit is set to 1 (transfer completed): when the serial I/O finished sending                      |

|                                 | data from the UARTi transmit register                                                                       |

|                                 | For reception                                                                                               |

|                                 | When transferring data from the UARTi receive register to the UiRB register (at                             |

|                                 | completion of reception)                                                                                    |

| Error detection                 | Overrun error <sup>(2)</sup>                                                                                |

|                                 | This error occurs if the serial I/O started receiving the next data before reading the                      |

|                                 | UiRB register and received the 7th bit in the the next data                                                 |

| Select function                 | CLK polarity selection                                                                                      |

|                                 | Transfer data input/output can be chosen to occur synchronously with the rising or                          |

|                                 | the falling edge of the transfer clock                                                                      |

|                                 | LSB first, MSB first selection                                                                              |

|                                 | Whether to start sending/receiving data beginning with bit 0 or beginning with bit 7                        |

|                                 | can be selected                                                                                             |

|                                 | Continuous receive mode selection                                                                           |

|                                 | Reception is enabled immediately by reading the UiRB register                                               |

|                                 | Switching serial data logic (UART2)                                                                         |

|                                 | This function reverses the logic value of the transmit/receive data                                         |

|                                 | Transfer clock output from multiple pins selection (UART1)                                                  |

|                                 | The output pin can be selected in a program from two UART1 transfer clock pins that                         |

|                                 | have been set                                                                                               |

|                                 | Separate CTS/RTS pins (UART0)                                                                               |

|                                 | CTS0 and RTS0 are input/output from separate pins                                                           |

|                                 | UART1 pin remapping selection                                                                               |

|                                 | The UART1 pin can be selected from the P67 to P64 or P73 to P70                                             |

| IOTES:                          |                                                                                                             |

1. When an external clock is selected, the conditions must be met while if the CKPOL bit in the UiC0 register is set to 0 (transmit data output at the falling edge and the receive data taken in at the rising edge of the transfer clock), the external clock is in the high state; if the CKPOL bit in the UiC0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the rising edge and the receive data taken in at the set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock), the external clock is in the high state; if the CKPOL bit in the UiC0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock), the external clock is in the low state.

2. If an overrun error occurs, bits 8 to 0 in the UiRB register are undefined. The IR bit in the SiRIC register remains unchanged.

3. The U0IRS and U1IRS bits respectively are the bits 0 and 1 in the UCON register; the U2IRS bit is bit 4 in the U2C1 register.

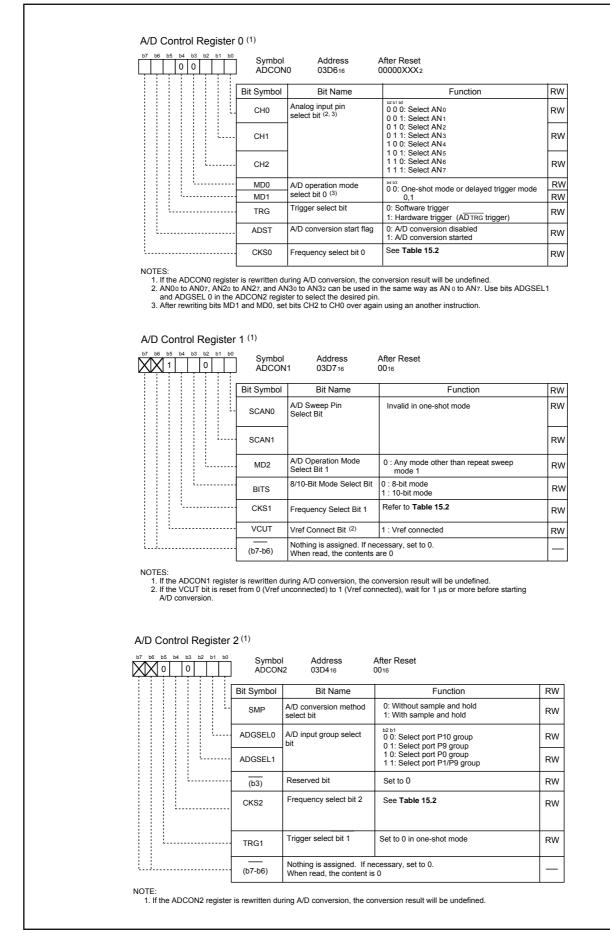

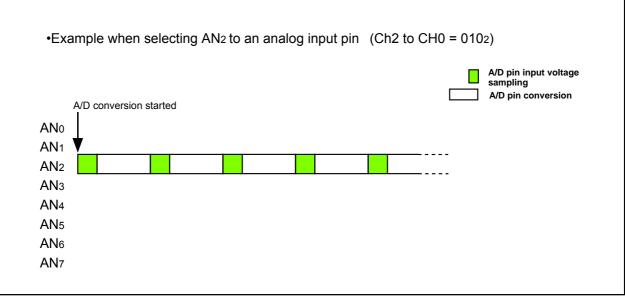

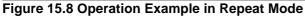

### 15.1.2 Repeat mode

In repeat mode, analog voltage applied to a selected pin is repeatedly converted to a digital code. **Table 15.4** shows the repeat mode specifications. **Figure 15.8** shows the operation example in repeat mode. **Figure 15.9** shows the ADCON0 to ADCON2 registers in repeat mode.

| Item                                | Specification                                                                       |

|-------------------------------------|-------------------------------------------------------------------------------------|

| Function                            | Bits CH2 to CH0 in the ADCON0 register and the ADGSEL1 to ADGSEL0 bits              |

|                                     | in the ADCON2 register select pins. Analog voltage applied to a selected pin        |

|                                     | is repeatedly converted to a digital code                                           |

| A/D Conversion Start                | When the TRG bit in the ADCON0 register is 0 (software trigger)                     |

| Condition                           | Set the ADST bit in the ADCON0 register to 1 (A/D conversion started)               |

|                                     | <ul> <li>When the TRG bit in the ADCON0 register is 1 (hardware trigger)</li> </ul> |

|                                     | The ADTRG pin input changes state from "H" to "L" after setting the ADST bit        |

|                                     | to 1 (A/D conversion started)                                                       |

| A/D Conversion Stop Condition       | Set the ADST bit to 0 (A/D conversion halted)                                       |

| Interrupt Request Generation Timing | None generated                                                                      |

| Analog Input Pin                    | Select one pin from AN0 to AN7, AN00 to AN07, AN20 to AN27, and AN30 to AN32        |

| Readout of A/D Conversion Result    | Readout one of the AD0 to AD7 registers that corresponds to the selected pin        |

|                                                                               | Function RV                                |

|-------------------------------------------------------------------------------|--------------------------------------------|

|                                                                               | 1 diffetion                                |

|                                                                               | bus sample sweep mode or RV gger mode 0, 1 |

| DTE A/D operation mode select 0: Other than bit 3                             | delayed trigger mode 0, 1 RV               |

| HPTRG0 AN0 trigger select bit See Table 1                                     | 5.9 RV                                     |

| HPTRG1 AN1 trigger select bit Set to 0 in simode                              | nultaneous sample sweep RV                 |

| (b7-b4) Nothing is assigned. If necessary, set to When read, the content is 0 | 0                                          |

Figure 15.18 ADTRGCON Register in Simultaneous Sample Sweep Mode

| Table 15.9 Trigger Select Bit Setting in Simultaneous Sample Sweep Mode |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

|   | TRG | TRG1 | HPTRG0 | TRIGGER                                                     |

|---|-----|------|--------|-------------------------------------------------------------|

|   | 0   | -    | -      | Software trigger                                            |

|   | 1   | -    | 1      | Timer B0 underflow <sup>(1)</sup>                           |

| Γ | 1   | 0    | 0      | ADTRG                                                       |

| Γ | 1   | 1    | 0      | Timer B2 or Timer B2 interrupt generation frequency setting |

|   |     | •    | 5      | counter underflow <sup>(2)</sup>                            |

NOTES:

1. A count can be started for Timer <u>B2</u>, Timer B2 interrupt generation frequency setting counter underflow or the INT5 pin falling edge as count start conditions of Timer B0.

Select Timer B2 or Timer B2 interrupt generation frequency setting counter using the TB2SEL bit in the TB2SC register.

Figure 15.20 Each Flag Operation in ADSTAT0 Register Associated with the Operation Example in Delayed Trigger Mode 0 (1)

RENESAS

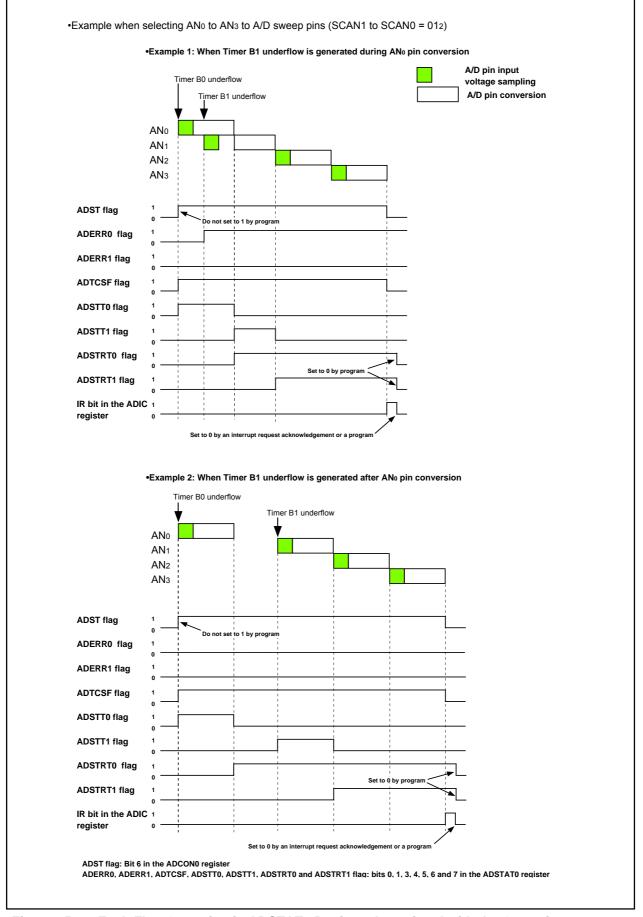

Figure 16.3 S00 and S20 Registers

Г

| b7 b6 b5 | b4 b3 b2 b1 b0 | ] Symbo<br>S10 | Address 02E816                                       | After Reset<br>0001000X2                                      |                   |

|----------|----------------|----------------|------------------------------------------------------|---------------------------------------------------------------|-------------------|

|          |                | Bit Symbol     | Bit Name                                             | Function                                                      | RW                |

|          |                | LRB            | Last receive bit                                     | 0: Last bit = 0<br>1: Last bit = 1                            | RO <sup>(1</sup>  |

|          |                | ADR0           | General call detecting flag                          | 0: No general call detected<br>1: General call detected       | RO <sup>(1)</sup> |

|          |                | AAS            | Slave address comparison flag                        | 0: No address matched<br>1: Address matched                   | RO <sup>(1</sup>  |

|          | l              | AL             | Arbitration lost detection flag                      | 0: Not detected<br>1: Detected                                | RO <sup>(2)</sup> |

|          | ,              | PIN            | I <sup>2</sup> C bus interface interrupt request bit | 0: Interrupt request issued<br>1: No interrupt request issued | R0 <sup>(2)</sup> |

|          |                | BB             | Bus busy flag                                        | 0: Bus free<br>1: Bus busy                                    | RO <sup>(1)</sup> |

|          |                | TRX            | Communication mode select bits 0                     | 0: Receive mode<br>1: Transmit mode                           | RW <sup>(3</sup>  |

|          |                | MST            | Communication mode select bit 1                      | 0: Slave mode<br>1: Master mode                               | RW <sup>(3</sup>  |

Read only. If necessary, set to 0.

To write to these bits, refer to 16.9 START Condition Generation Method and 16.11 STOP Condition Generation Method.

Figure 16.5 S10 Register

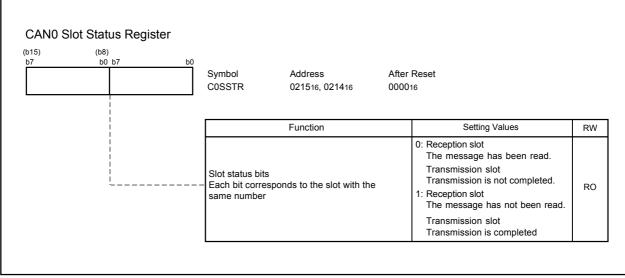

### 17.1.3.4 C0SSTR Register

Figure 17.9 shows the COSSTR register.

Figure 17.9 C0SSTR Register

Γ

| 0<br>0 | 6 b5<br>0 |   |            | 0 | b1 b0 | Sym<br>FMR |                        | Address<br>01B316                  | After Reset<br>010000002                                                     |    |

|--------|-----------|---|------------|---|-------|------------|------------------------|------------------------------------|------------------------------------------------------------------------------|----|

|        |           |   |            |   |       | Bit Symbol | Bit                    | Name                               | Function                                                                     | RW |

|        |           |   |            |   | ļ.    | FMR40      | Erase sus<br>enable b  | pend function<br>it <sup>(1)</sup> | 0: Disabled<br>1: Enabled                                                    | RW |

|        |           |   |            |   | i     | FMR41      | Erase sus<br>request b |                                    | 0: Erase restart<br>1: Suspend request                                       | RW |

|        | <u>.</u>  | ! | . <u>.</u> |   |       | (b5-b2)    | Reserved               | bit                                | Set to 0                                                                     | RO |

|        |           |   |            |   |       | FMR46      | Erase stat             | us                                 | 0: During auto-erase operation<br>1: Auto-erase stop<br>(erase suspend mode) | RO |

|        |           |   |            |   |       | (b7)       | Reserved               | bit                                | Set to 0                                                                     | RW |

- memory in EW mode 0.

- 2. The FMR41 bit is valid only when the FMR40 bit is set to 1. The FMR41 bit can be written only between executing an erase command and completing erase (this bit is set to 0 other than the above duration). The FMR41 bit can be set to 0 or 1 by program in EW mode 0. In EW mode 1, the FMR41 bit is automatically set to 1 when the FMR40 bit is 1 and a maskable interrupt is generated during erasing. The FMR41 bit cannot be set to 1 by program (it can be set to 0 by program).

Figure 20.7 FMR4 Register

# 20.6 Precautions in CPU Rewrite Mode

Described below are the precautions to be observed when rewriting the flash memory in CPU rewrite mode.

## 20.6.1 Operation Speed

When the CPU clock source is the main clock, set the CPU clock frequency at 10 MHz or less with the CM06 bit in the CM0 register and bits CM17 and CM16 in the CM1 register, before entering CPU rewrite mode (EW mode 0 or EW mode 1). Also, when selecting f3(ROC) of a on-chip oscillator as a CPU clock source, set bits ROCR3 and ROCR2 in the ROCR register to the CPU clock division rate at "divide-by-4" or "divide-by-8", before entering CPU rewrite mode (EW mode 0 or EW mode 1). In both cases, set the PM17 bit in the PM1 register to 1 (with wait state).

## 20.6.2 Prohibited Instructions

The following instructions cannot be used in EW mode 0 because the CPU tries to read data in the flash memory: UND instruction, INTO instruction, JMPS instruction, JSRS instruction, and BRK instruction

## 20.6.3 Interrupts

EW Mode 0

- To use interrupts having vectors in a relocatable vector table, the vectors must be relocated to the RAM area.

- The NMI and watchdog timer interrupts are available since registers FMR0 and FMR1 are forcibly reset when either interrupt occurs. However, the interrupt program, which allocates the jump addresses for each interrupt routine to the fixed vector table, is needed. Flash memory rewrite operation is aborted when the NMI or watchdog timer interrupt occurs. Set the FMR01 bit to 1 and execute the rewrite and erase program again after exiting the interrupt routine.

• The address match interrupt can not be used since the CPU tries to read data in the flash memory. EW Mode 1

• Do not acknowledge any interrupts with vectors in the relocatable vector table or the address match interrupt during the auto program period or auto erase period with erase-suspend function disabled.

### 20.6.4 How to Access

To set bit FMR01, FMR02, FMR11 or FMR16 to 1, write 1 immediately after setting to 0. Do not generate an interrupt or a DMA transfer between the instruction to set the bit to 0 and the instruction to set it to 1. When the  $\overline{\text{NMI}}$  function is selected, set the bit while an "H" signal is applied to the P85/ $\overline{\text{NMI}}$ /SD pin.

## 20.6.5 Writing in the User ROM Area

### 20.6.5.1 EW Mode 0

If the supply voltage drops while rewriting the block where the rewrite control program is stored, the flash memory can not be rewritten, because the rewrite control program is not correctly rewritten. If this error occurs, rewrite the user ROM area in standard serial I/O mode or parallel I/O mode.

### 20.6.5.2 EW Mode 1

• Do not rewrite the block where the rewrite control program is stored.

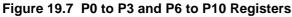

## 20.11.2 Example of Circuit Application in CAN I/O Mode

**Figure 20.21** shows example of circuit application in CAN I/O mode. Refer to the user's manual for CAN programmer to handle pins controlled by a CAN programmer.

Figure 20.21 Circuit Application in CAN I/O Mode

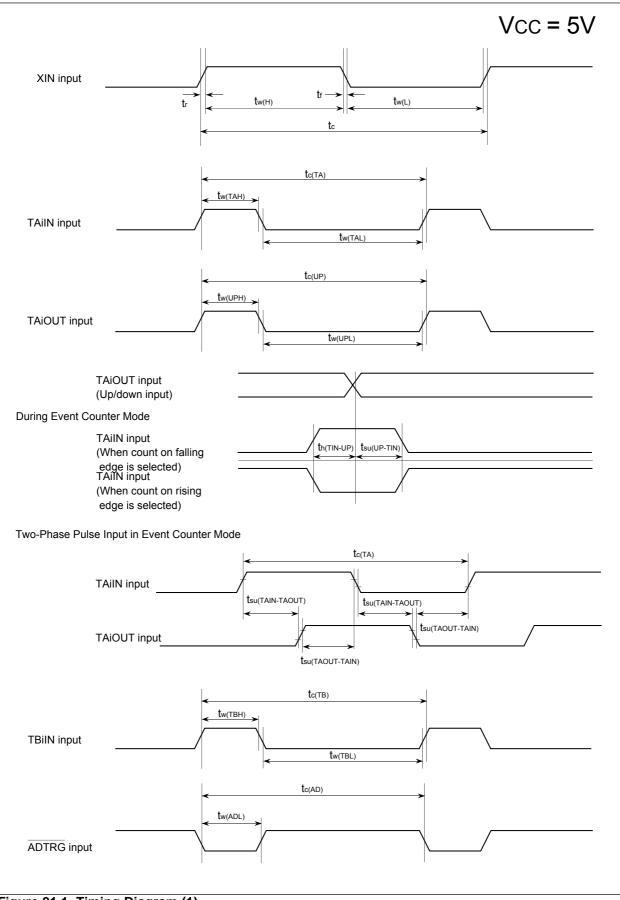

Figure 21.1 Timing Diagram (1)

### **Timing Requirements**

# Vcc = 3V

(VCC = 3V, VSS = 0V, at Topr = -20 to  $85^{\circ}$ C / -40 to  $85^{\circ}$ C unless otherwise specified)

| Table 21.26 External Clock Input (XIN input) |

|----------------------------------------------|

|----------------------------------------------|

| Symbol | Parameter                             | Standa | ldard | Unit |

|--------|---------------------------------------|--------|-------|------|

|        | Falanielei                            | Min.   | Max.  | Unit |

| tc     | External clock input cycle time       | 100    |       | ns   |

| tw(H)  | External clock input HIGH pulse width | 40     |       | ns   |

| tw(L)  | External clock input LOW pulse width  | 40     |       | ns   |

| tr     | External clock rise time              |        | 18    | ns   |

| tr     | External clock fall time              |        | 18    | ns   |

Vcc = 3V

### **Timing Requirements**

### (VCC = 3V, VSS = 0V, at Topr = - 40 to 85°C unless otherwise specified)

#### Table 21.71 Timer B Input (Counter Input in Event Counter Mode)

| Symbol  | Decomptor                                           | Standard | dard | Unit |

|---------|-----------------------------------------------------|----------|------|------|

|         | Parameter                                           | Min.     | Max. |      |

| tc(TB)  | TBin input cycle time (counted on one edge)         | 150      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on one edge)   | 60       |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on one edge)    | 60       |      | ns   |

| tc(TB)  | TBin input cycle time (counted on both edges)       | 300      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on both edges) | 120      |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on both edges)  | 120      |      | ns   |

#### Table 21.72 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Standard | dard | Unit |

|---------|------------------------------|----------|------|------|

| Symbol  |                              | Min.     | Max. | Unit |

| tc(TB)  | TBin input cycle time        | 600      |      | ns   |

| tw(TBH) | TBilN input HIGH pulse width | 300      |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 300      |      | ns   |

#### Table 21.73 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                    | Standard | dard | Unit |

|---------|------------------------------|----------|------|------|

| Symbol  |                              | Min.     | Max. |      |

| tc(TB)  | TBiin input cycle time       | 600      |      | ns   |

| tw(TBH) | TBiin input HIGH pulse width | 300      |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 300      |      | ns   |

#### Table 21.74 A/D Trigger Input

| Symbol  | Parameter                                     | Standard | Unit     |      |

|---------|-----------------------------------------------|----------|----------|------|

|         | i didificici                                  | Min.     | in. Max. | Onit |

| tc(AD)  | ADTRG input cycle time (trigger able minimum) | 1500     |          | ns   |

| tw(ADL) | ADTRG input LOW pulse width                   | 200      |          | ns   |

#### Table 21.75 Serial I/O

| Symbol   | Parameter                   | Standar | dard | – Unit |

|----------|-----------------------------|---------|------|--------|

|          | Falameter                   | Min.    | Max. | Unit   |

| tc(CK)   | CLKi input cycle time       | 300     |      | ns     |

| tw(CKH)  | CLKi input HIGH pulse width | 150     |      | ns     |

| tw(CKL)  | CLKi input LOW pulse width  | 150     |      | ns     |

| td(C-Q)  | TxDi output delay time      |         | 160  | ns     |

| th(C-Q)  | TxDi hold time              | 0       |      | ns     |

| tsu(D-C) | RxDi input setup time       | 100     |      | ns     |

| th(C-D)  | RxDi input hold time        | 90      |      | ns     |

#### Table 21.76 External Interrupt INTi Input

| Symbol  | Parameter                   | Standard | Unit      |       |

|---------|-----------------------------|----------|-----------|-------|

|         | i didireter                 | Min.     | Min. Max. | Offic |

| tw(INH) | INTi input HIGH pulse width | 380      |           | ns    |

| tw(INL) | INTi input LOW pulse width  | 380      |           | ns    |

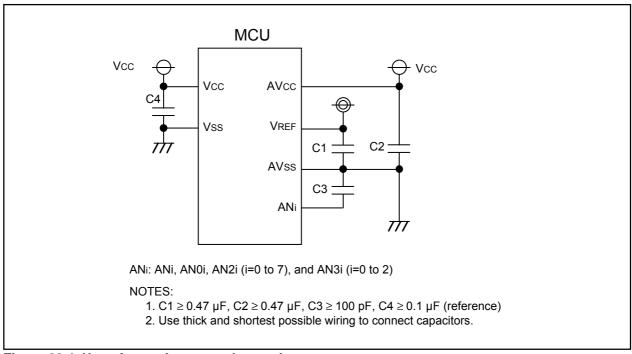

## 22.9 A/D Converter

- 1. Set registers ADCON0 (except bit 6), ADCON1, ADCON2 and ADTRGCON when A/D conversion is stopped (before a trigger occurs).

- 2. When the VCUT bit in ADCON1 register is changed from 0 (Vref not connected) to 1 (Vref connected), start A/D conversion after passing 1  $\mu$ s or longer.

- To prevent noise-induced device malfunction or latchup, as well as to reduce conversion errors, insert capacitors between the AVcc, VREF, and analog input pins (ANi, AN0i, AN2i(i=0 to 7), and AN3i(i=0 to 2)) each and the AVss pin. Similarly, insert a capacitor between the Vcc1 pin and the Vss pin. Figure 22.4 is an example connection of each pin.

- 4. Make sure the port direction bits for those pins that are used as analog inputs are set to 0 (input mode). Also, if the TGR bit in the ADCON0 register is set to 1 (external trigger), make sure the port direction bit for the ADTRG pin is set to 0 (input mode).

- **5.** When using key input interrupts, do not use any of the four AN4 to AN7 pins as analog inputs. (A key input interrupt request is generated when the A/D input voltage goes low.)

- 6. The φAD frequency must be 10 MHz or less. Without sample-and-hold function, limit the φAD frequency to 250kHz or more. With the sample and hold function, limit the φAD frequency to 1MHz or more.

- 7. When changing an A/D operation mode, select analog input pin again in bits CH2 to CH0 in the ADCON0 register and bits SCAN1 to SCAN0 in the ADCON1 register.

Figure 22.4 Use of capacitors to reduce noise

RENESAS