# E. Renesas Electronics America Inc - M30291FATHP#U3AAE9 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                   |

| Core Size                  | -                                                                                   |

| Speed                      | -                                                                                   |

| Connectivity               | -                                                                                   |

| Peripherals                | -                                                                                   |

| Number of I/O              | -                                                                                   |

| Program Memory Size        | -                                                                                   |

| Program Memory Type        | -                                                                                   |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | -                                                                                   |

| Voltage - Supply (Vcc/Vdd) | -                                                                                   |

| Data Converters            | -                                                                                   |

| Oscillator Type            | -                                                                                   |

| Operating Temperature      | -                                                                                   |

| Mounting Type              | -                                                                                   |

| Package / Case             | -                                                                                   |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fathp-u3aae9 |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification | Symbol           | I/O Type | Function                                                                      |  |  |  |  |  |

|----------------|------------------|----------|-------------------------------------------------------------------------------|--|--|--|--|--|

| Timer S        | INPC10 to INPC17 | I        | Input pins for the time measurement function                                  |  |  |  |  |  |

|                | OUTC10 to OUTC17 | 0        | output pins for the waveform generating function                              |  |  |  |  |  |

| CAN            | CRX              | I        | Input pin for the CAN communication function                                  |  |  |  |  |  |

|                | СТХ              | 0        | Output pin for the CAN communication function                                 |  |  |  |  |  |

| I/O Ports      | P00 to P03       | I/O      | CMOS I/O ports which have a direction register determines an individual       |  |  |  |  |  |

|                | P15 to P17       |          | pin is used as an input port or an output port. A pull-up resistor is select- |  |  |  |  |  |

|                | P20 to P27       |          | able for every 4 input ports.                                                 |  |  |  |  |  |

|                | P30 to P33       |          |                                                                               |  |  |  |  |  |

|                | P60 to P67       |          |                                                                               |  |  |  |  |  |

|                | P70 to P77       |          |                                                                               |  |  |  |  |  |

|                | P80 to P87       |          |                                                                               |  |  |  |  |  |

|                | P90 to P93       |          |                                                                               |  |  |  |  |  |

|                | P100 to P107     |          |                                                                               |  |  |  |  |  |

#### Table 1.14 Pin Description (64-pin and 80-pin packages) (Continued)

I: Input O: Output I/O: Input and output

# 7.7 System Clock Protective Function

When the main clock is selected for the CPU clock source, this function protects the clock from modifications in order to prevent the CPU clock from becoming halted by run-away.

If the PM21 bit in the PM2 register is set to 1 (clock modification disabled), the following bits are protected against writes:

- Bits CM02, CM05, and CM07 in CM0 register

- Bits CM10 and CM11 in CM1 register

- CM20 bit in CM2 register

- All bits in the PLC0 register

Before the system clock protective function can be used, the following register settings must be made while the CM05 bit in the CM0 register is 0 (main clock oscillating) and CM07 bit is 0 (main clock selected for the CPU clock source):

(1) Set the PRC1 bit in the PRCR register to 1 (enable writes to PM2 register).

(2) Set the PM21 bit in the PM2 register to 1 (disable clock modification).

(3) Set the PRC1 bit in the PRCR register to 0 (disable writes to PM2 register).

Do not execute the WAIT instruction when the PM21 bit is 1.

## 7.8 Oscillation Stop and Re-oscillation Detect Function

The oscillation stop and re-oscillation detect function detects the re-oscillation after stop of main clock oscillation circuit. When the oscillation stop and re-oscillation detection occurs, the oscillation stop detect function is reset or oscillation stop and re-oscillation detection interrupt is generated, depending on the CM27 bit set in the CM2 register. The oscillation stop detect function is enabled or disabled by the CM20 bit in the CM2 register. **Table 7.8** lists a specification overview of the oscillation stop and re-oscillation detect function.

| Item                                     | Specification                                                                  |

|------------------------------------------|--------------------------------------------------------------------------------|

| Oscillation stop detectable clock and    | $f(X_{IN}) \ge 2 MHz$                                                          |

| frequency bandwidth                      |                                                                                |

| Enabling condition for oscillation stop, | Set CM20 bit to 1(enable)                                                      |

| re-oscillation detection function        |                                                                                |

| Operation at oscillation stop,           | •Reset occurs (when CM27 bit =0)                                               |

| re-oscillation detection                 | •Oscillation stop, re-oscillation detection interrupt occurs(when CM27 bit =1) |

# 9.2 Interrupts and Interrupt Vector

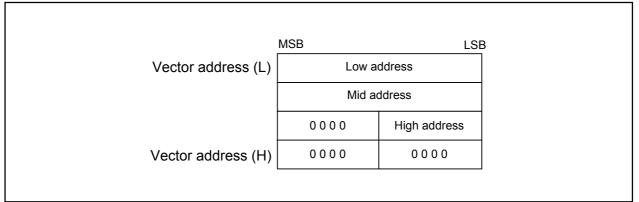

One interrupt vector consists of 4 bytes. Set the start address of each interrupt routine in the respective interrupt vectors. When an interrupt request is accepted, the CPU branches to the address set in the corresponding interrupt vector. **Figure 9.2** shows the interrupt vector.

Figure 9.2 Interrupt Vector

# 9.2.1 Fixed Vector Tables

The fixed vector tables are allocated to the addresses from FFFDC16 to FFFF16. **Table 9.1** lists the fixed vector tables. In the flash memory version of MCU, the vector addresses (H) of fixed vectors are used by the ID code check function. For details, refer to the section "flash memory rewrite disabling function".

Table 9.1 Fixed Vector Tables

| Interrupt source                                                                             | Vector table addresses     | Remarks                                                                                                                                                 | Reference                                                                 |

|----------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                                                                                              | Address (L) to address (H) |                                                                                                                                                         |                                                                           |

| Undefined instruction                                                                        | FFFDC16 to FFFDF16         | Interrupt on UND instruction                                                                                                                            | M16C/60, M16C/20                                                          |

| Overflow                                                                                     | FFFE016 to FFFE316         | Interrupt on INTO instruction                                                                                                                           | serise software                                                           |

| BRK instruction                                                                              | FFFE416 to FFFE716         | If the contents of address<br>FFFE716 is FF16, program ex-<br>ecution starts from the address<br>shown by the vector in the<br>relocatable vector table | maual                                                                     |

| Address match                                                                                | FFFE816 to FFFEB16         |                                                                                                                                                         | Address match interrupt                                                   |

| Single step (1)                                                                              | FFFEC16 to FFFEF16         |                                                                                                                                                         |                                                                           |

| Watchdog timer<br>Oscillation stop and<br>re-oscillation detection,<br>low voltage detection | FFFF016 to FFFF316         |                                                                                                                                                         | Watchdog timer,<br>clock generating circuit,<br>voltage detection circuit |

| DBC (1)                                                                                      | FFFF416 to FFFF716         |                                                                                                                                                         |                                                                           |

| NMI                                                                                          | FFFF816 to FFFFB16         |                                                                                                                                                         | NMI interrupt                                                             |

| Reset(2)                                                                                     | FFFFC16 to FFFFF16         |                                                                                                                                                         | Reset                                                                     |

NOTE:

1. Do not normally use this interrupt because it is provided exclusively for use by development tools.

3. When the two-phase pulse signal processing function is not used, set the corresponding bit to 0.

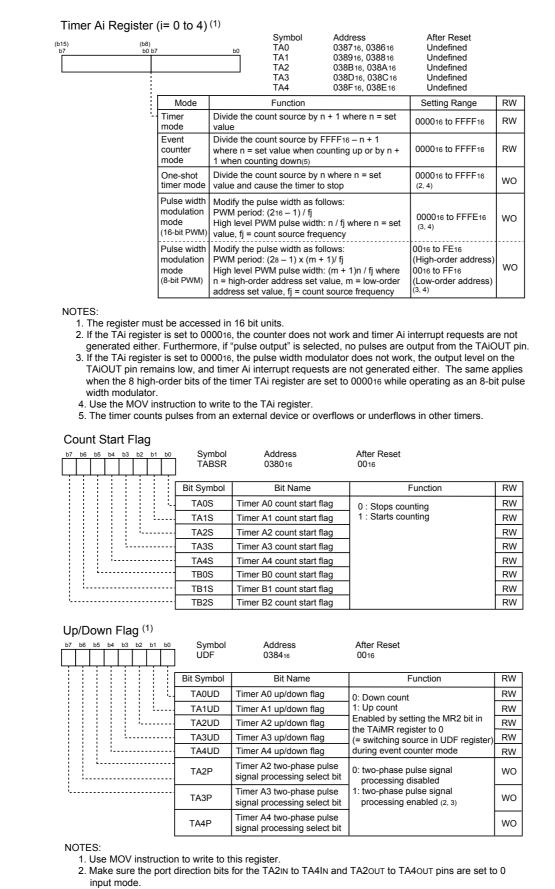

#### Figure 12.5 TA0 to TA4 Registers, TABSR Register, and UDF Register

|   | 0 b4 b | b3 b2 b1 b0<br>0 1 |            | nbol Address<br>DMR to TA4MR 039616 to  | After Reset<br>0 039A16 0016                                                                                                     |    |

|---|--------|--------------------|------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----|

|   |        |                    | Bit Symbol | Bit Name                                | Function                                                                                                                         | RW |

|   |        |                    | TMOD0      | Operation mode select bit               | b1 b0                                                                                                                            | RW |

|   |        |                    | TMOD1      |                                         | 0 1 : Event counter mode <sup>(1)</sup>                                                                                          | RW |

|   |        |                    | MR0        | Pulse output function select bit        | 0: Pulse is not output<br>(TAioUT pin functions as I/O port)<br>1: Pulse is output<br>(TAioUT pin functions as pulse output pin) | RW |

|   |        |                    | MR1        | Count polarityselect bit <sup>(2)</sup> | 0: Counts external signal's falling edge<br>1: Counts external signal's rising edge                                              | RW |

|   |        |                    | MR2        | Up/down switching<br>cause select bit   | 0: UDF register<br>1: Input signal to TAio∪⊤ pin <sup>(3)</sup>                                                                  | RW |

|   | L      |                    | MR3        | Set to 0 in event counter me            | ode                                                                                                                              | RW |

|   |        |                    | TCK0       | Count operation type select bit         | 0: Reload type<br>1: Free-run type                                                                                               | RW |

| l |        |                    | TCK1       | Can be 0 or 1 when not usi              | ng two-phase pulse signal processing                                                                                             | RW |

- 1. During event counter mode, the count source can be selected using registers ONSF and TRGSR.

- Effective when bits TAiTGH and TAiTGL in the ONSF or TRGSR register are 002 (TAiIN pin input).

Decrement when input on TAiOUT pin is low or increment when input on that pin is high. The port direction bit for TAiOUT pin must be set to 0 (input mode).

Figure 12.8 TAiMR Register in Event Counter Mode (when not using two-phase pulse signal processing)

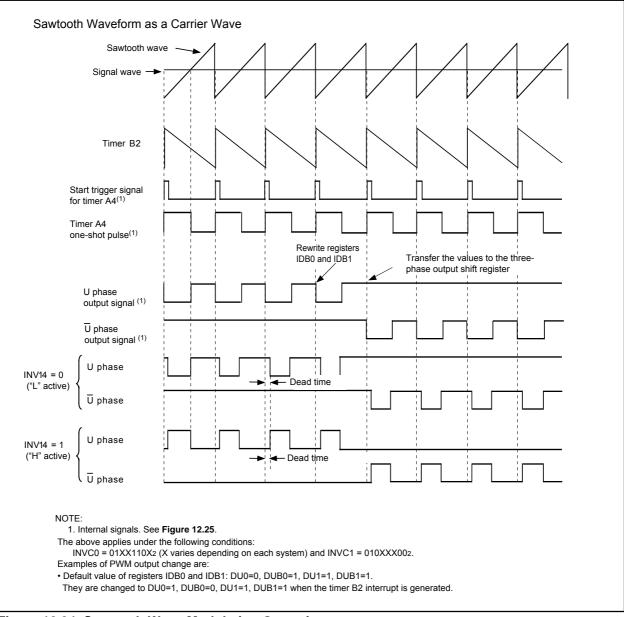

Figure 12.34 Sawtooth Wave Modulation Operation

| b6 b5 b4 b3 b2 b1 b0                  | Symb<br>G1IE                                                   |                                                                                                                                                                                   | After Reset<br>00 <sub>16</sub>                                               |                            |

|---------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------|

|                                       | Bit<br>Symbol                                                  | Bit Name                                                                                                                                                                          | Function                                                                      | RV                         |

|                                       | G1IE00                                                         | Interrupt enable 0, CH0                                                                                                                                                           | 0 : IC/OC interrupt 0 request disable<br>1 : IC/OC interrupt 0 request enable | RV                         |

| · · · · · · · · · · · · · · · · · · · | G1IE01                                                         | Interrupt enable 0, CH1                                                                                                                                                           |                                                                               | RV                         |

| L                                     | G1IE02                                                         | Interrupt enable 0, CH2                                                                                                                                                           |                                                                               | RV                         |

|                                       | G1IE03                                                         | Interrupt enable 0, CH3                                                                                                                                                           |                                                                               | RV                         |

|                                       | G1IE04                                                         | Interrupt enable 0, CH4                                                                                                                                                           |                                                                               | RV                         |

| L                                     | G1IE05                                                         | Interrupt enable 0, CH5                                                                                                                                                           |                                                                               | RV                         |

| L                                     | G1IE06                                                         | Interrupt enable 0, CH6                                                                                                                                                           |                                                                               | RV                         |

|                                       |                                                                |                                                                                                                                                                                   |                                                                               |                            |

| terrupt Enable R                      | G1IE07                                                         | Interrupt enable 0, CH7                                                                                                                                                           |                                                                               | RV                         |

| terrupt Enable R                      |                                                                | r 1<br>pol Address                                                                                                                                                                | After Reset<br>0016                                                           | RV                         |

|                                       | egiste                                                         | r 1<br>pol Address                                                                                                                                                                |                                                                               | RV                         |

|                                       | Symt<br>G1IE                                                   | <b>r 1</b><br>pol Address<br>1 033216                                                                                                                                             | 0016                                                                          | RW                         |

|                                       | Symt<br>G1IE<br>Symbol                                         | r 1<br>pol Address<br>1 033216<br>Bit Name                                                                                                                                        | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     |                            |

|                                       | Symt<br>G1IE<br>Symbol<br>G1IE10                               | r 1<br>pol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0                                                                                                             | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RW<br>RV<br>RV             |

|                                       | Symt<br>G1IE<br>Symbol<br>G1IE10<br>G1IE11                     | r 1<br>pol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1                                                                                  | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RW                         |

|                                       | Symbol<br>G1IE10<br>G1IE11<br>G1IE12                           | r 1<br>pol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1<br>Interrupt enable 1, CH2                                                       | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RV<br>RV<br>RV<br>RV       |

|                                       | Symb<br>G1IE<br>Symbol<br>G1IE10<br>G1IE11<br>G1IE12<br>G1IE13 | r 1<br>bol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1<br>Interrupt enable 1, CH2<br>Interrupt enable 1, CH3                            | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RW<br>RV<br>RV<br>RV<br>RV |

|                                       | Symbol<br>G1IE10<br>G1IE11<br>G1IE12<br>G1IE13<br>G1IE14       | r 1<br>Dol Address<br>1 033216<br>Bit Name<br>Interrupt enable 1, CH0<br>Interrupt enable 1, CH1<br>Interrupt enable 1, CH2<br>Interrupt enable 1, CH3<br>Interrupt enable 1, CH3 | 0016<br>Function<br>0 : IC/OC interrupt 1 request disable                     | RV<br>RV<br>RV             |

Figure 13.10 G1IE0 and G1IE1 Registers

#### 14.1.1.2 CLK Polarity Select Function

Use the CKPOL bit in the UiC0 register (i=0 to 2) to select the transfer clock polarity. **Figure 14.11** shows the polarity of the transfer clock.

| (1) When the CKPOL bit in the UiC0 register is set to 0 (transmit data output at the falling edge<br>and the receive data taken in at the rising edge of the transfer clock)                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                          |

| TxDi $D0 \neq D1 D2$ D3 D4 D5 D6 D7                                                                                                                                                                                                                                      |

| RXDi D0 \ D1 \ D2 \ D3 \ D4 \ D5 \ D6 \ D7                                                                                                                                                                                                                               |

| (2) When the CKPOL bit in the UiC0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock)                                                                                                |

|                                                                                                                                                                                                                                                                          |

| TxDi $\underline{D0 \ 0 \ D1 \ D2} \ \underline{D3 \ D4 \ D5 \ D6 \ D7}$                                                                                                                                                                                                 |

| RXDi D0 D1 D2 D3 D4 D5 D6 D7                                                                                                                                                                                                                                             |

| i = 0 to 2                                                                                                                                                                                                                                                               |

| <ul> <li>NOTES:</li> <li>1. This applies to the case where the UFORM bit in the UiC0 register is set to 0 (LSB first) and the UiLCH bit in the UiC1 register is set to 0 (no reverse).</li> <li>2. When not transferring, the CLKi pin outputs a high signal.</li> </ul> |

|                                                                                                                                                                                                                                                                          |

#### Figure 14.11 Polarity of transfer clock

#### 14.1.1.3 LSB First/MSB First Select Function

Use the UFORM bit in the UiC0 register (i=0 to 2) to select the transfer format. **Figure 14.12** shows the transfer format.

| (1) When the UFORM bit in the UiC0 register 0 (LSB first)                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                          |

| TxDi D0 X D1 X D2 X D3 X D4 X D5 X D6 X D7                                                                                                                                                                                                                               |

| RxDi D0 \ D1 \ D2 \ D3 \ D4 \ D5 \ D6 \ D7                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                          |

| (2) When the UFORM bit in the UiC0 register is set to 1 (MSB first)                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                          |

| TxDi D7 X D6 X D5 X D4 X D3 X D2 X D1 X D0                                                                                                                                                                                                                               |

| RxDi D7 X D6 X D5 X D4 X D3 X D2 X D1 X D0                                                                                                                                                                                                                               |

| i = 0 to 2                                                                                                                                                                                                                                                               |

| NOTE:<br>1. This applies to the case where the CKPOL bit in the UiC0 register is set to 0 (transmit data output at<br>the falling edge and the receive data taken in at the rising edge of the transfer clock) and the<br>UiLCH bit in the UiC1 register 0 (no reverse). |

Figure 14.12 Transfer format

#### 14.1.1.4 Continuous receive mode

When the UiRRM bit (i=0 to 2) is set to 1 (continuous receive mode), the TI bit in the UiC1 register is set to 0 (data present in the UiTB register) by reading the UiRB register. In this case, i.e., UiRRM bit is set to 1, do not write dummy data to the UiTB register in a program. The U0RRM and U1RRM bits are the bit 2 and bit 3 in the UCON register, respectively, and the U2RRM bit is the bit 5 in the U2C1 register.

#### 14.1.1.5 Serial data logic switch function (UART2)

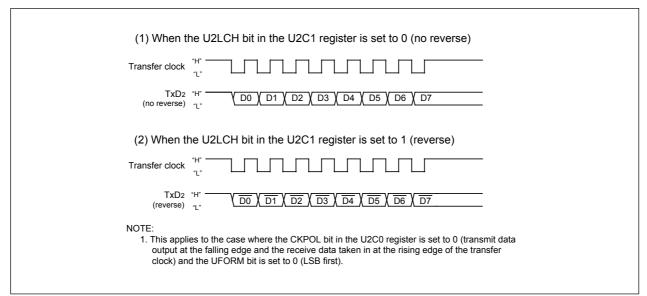

When the U2LCH bit in the U2C1 register is set to 1 (reverse), the data written to the U2TB register has its logic reversed before being transmitted. Similarly, the received data has its logic reversed when read from the U2RB register. **Figure 14.13** shows serial data logic.

Figure 14.13 Serial data logic switch timing

#### 14.1.1.6 Transfer clock output from multiple pins function (UART1)

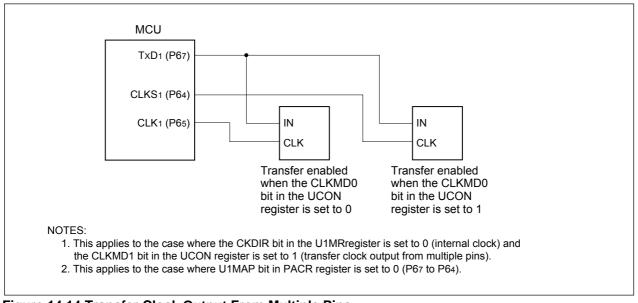

The CLKMD1 to CLKMD0 bits in the UCON register can choose one from two transfer clock output pins. (See **Figure 14.14**) This function is valid when the internal clock is selected for UART1.

Figure 14.14 Transfer Clock Output From Multiple Pins

#### 14.1.3.7 ACK and NACK

If the STSPSEL bit in the U2SMR4 register is set to 0 (start and stop conditions not generated) and the ACKC bit in the U2SMR4 register is set to 1 (ACK data output), the value of the ACKD bit in the U2SMR4 register is output from the SDA2 pin.

If the IICM2 bit is set to 0, a NACK interrupt request is generated if the SDA2 pin remains high at the rising edge of the 9th bit of transmit clock pulse. An ACK interrupt request is generated if the SDA2 pin is low at the rising edge of the 9th bit of transmit clock pulse.

If ACK2 is selected for the cause of DMA1 request, a DMA transfer can be activated by detection of an acknowledge.

#### 14.1.3.8 Initialization of Transmission/Reception

If a start condition is detected while the STAC bit is set to 1 (UART2 initialization enabled), the serial I/ O operates as described below.

- The transmit shift register is initialized, and the content of the U2TB register is transferred to the transmit shift register. In this way, the serial I/O starts sending data synchronously with the next clock pulse applied. However, the UART2 output value does not change state and remains the same as when a start condition was detected until the first bit in the data is output synchronously with the input clock.

- The receive shift register is initialized, and the serial I/O starts receiving data synchronously with the next clock pulse applied.

- The SWC bit is set to 1 (SCL2 wait output enabled). Consequently, the SCL2 pin is pulled low at the falling edge of the ninth clock pulse.

Note that when UART2 transmission/reception is started using this function, the TI does not change state. Note also that when using this function, the selected transfer clock should be an external clock.

| b7 b6 | 5 b4 b | 3 b2 b | 1 b0 | Symbo<br>ADSTA                                       |                                                                                                                                                                                                                                                            | After res                              | set                                                                                                    |    |

|-------|--------|--------|------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------|----|

|       |        |        |      | Bit Symbol                                           | Bit Name                                                                                                                                                                                                                                                   |                                        | Function I                                                                                             | ٦W |

|       |        |        |      | ADERR0                                               | AN1 trigger status flag                                                                                                                                                                                                                                    | AN0<br>1: AN1                          | trigger did not occur during<br>conversion<br>trigger occured during<br>conversion                     | ٦W |

|       |        |        |      | ADERR1                                               | Conversion termination flag                                                                                                                                                                                                                                | 1: Conv                                | version not terminated<br>version terminated by f<br>er B0 underflow                                   | ٦W |

|       |        | L      |      | (b2)                                                 | Nothing is assigned. If nece When read, its content is 0                                                                                                                                                                                                   | essary, so                             | et to 0.                                                                                               |    |

|       |        |        |      | ADTCSF                                               | Delayed trigger sweep status flag                                                                                                                                                                                                                          |                                        | ep not in progress<br>ep in progress                                                                   | RO |

|       | ·      |        |      | ADSTT0                                               | AN0 conversion status flag                                                                                                                                                                                                                                 |                                        | conversion not in progress<br>conversion in progress                                                   | RO |

|       |        |        |      | ADSTT1                                               | AN1 conversion status flag                                                                                                                                                                                                                                 |                                        | conversion not in progress<br>conversion in progress                                                   | RO |

|       |        |        |      | ADSTRT0                                              | AN0 conversion<br>completion status flag                                                                                                                                                                                                                   |                                        | conversion not completed conversion completed                                                          | RW |

| l     |        |        |      | ADSTRT1                                              | AN1 conversion completion status flag                                                                                                                                                                                                                      |                                        | conversion not completed conversion completed                                                          | ٦W |

| A/D R |        | eri(i= | 0 to | AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7 | Address           03C116 to 03C016           03C316 to 03C216           03C516 to 03C416           03C716 to 03C616           03C916 to 03C816           03CD16 to 03C410           03CD16 to 03C410           03CF16 to 03C410           03CF16 to 03C410 | 5 l<br>5 l<br>5 l<br>5 l<br>6 l<br>6 l | After Reset<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined<br>Jndefined |    |

|       |        |        |      |                                                      |                                                                                                                                                                                                                                                            | Funct                                  | ion                                                                                                    | R  |

|       |        |        |      |                                                      | When the BITS bit in the Al register is 1 (10-bit mode)                                                                                                                                                                                                    | DCON1                                  | When the BITS bit in the ADCON1 register is 0 (8-bit mode)                                             | R  |

|       |        |        |      | L.                                                   | Eight low-order bits of A/D conversion result                                                                                                                                                                                                              |                                        | A/D conversion result                                                                                  | R  |

|       |        |        |      |                                                      | Two high-order bits of<br>A/D conversion result                                                                                                                                                                                                            |                                        | When read, its content is<br>undefined                                                                 | R  |

|       |        |        |      |                                                      |                                                                                                                                                                                                                                                            |                                        |                                                                                                        |    |

Figure 15.4 ADSTAT0 Register and AD0 to AD7 Registers

# 16.1 I<sup>2</sup>C0 Data Shift Register (S00 register)

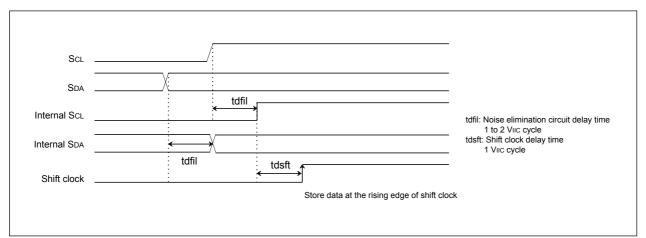

The S00 register is an 8-bit data shift register to store a received data and to write a transmit data. When a transmit data is written to the S00 register, the transmit data is synchronized with a SCL clock and the data is transferred from bit 7. Then, every one bit of the data is transmitted, the register's content is shifted for one bit to the left. When the SCL clock and the data is imported into the S00 register from bit 0. Every one bit of the data is shifted for one bit to the left. When the SCL clock and the data is shifted for one bit to the left. Figure 16.9 shows the timing to store the receive data to the S00 register.

The S00 register can be written when the ES0 bit in the S1D0 register is set to 1 (I<sup>2</sup>C0 bus interface enabled). If the S00 register is written when the ES0 bit is set to 1 and the MST bit in the S10 register is set to 1 (master mode), the bit counter is reset and the SCL clock is output. Write to the S00 register when the START condition is generatedor when an "L" signal is applied to the SCL pin. The S00 register can be read anytime regardless of the ES0 bit value.

Figure 16.9 The Receive Data Storing Timing of S00 Register

# 16.2 I<sup>2</sup>C0 Address Register (S0D0 register)

The S0D0 register consists of bits SAD6 to SAD0, total of 7. At the addressing is formatted, slave address is detected automatically and the 7-bit received address data is compared with the contents of bits SAD6 to SAD0.

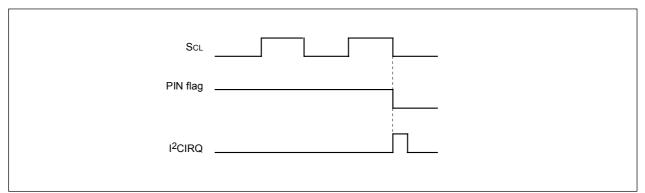

## 16.5.5 Bit 4: I<sup>2</sup>C bus Interface Interrupt Request Bit (PIN)

The PIN bit generates an  $I^2C$  bus interface interrupt request signal. Every one byte data is ransferred, the PIN bit is changed from 1 to 0. At the same time, an  $I^2C$  bus interface interrupt request is generated. The PIN bit is synchronized with the last clock of the internal transfer clock (when ACK-CLK=1, the last clock is the ACK clock: when the ACK-CLK=0, the last clock is the 8th clock) and it becomes 0. The interrupt request is generated on the falling edge of the PIN bit. When the PIN bit is set to 0, the clock applied to SCL maintains "L" and further clock generation is disabled. When the ACK-CLK bit is set to 1 and the WIT bit in the S3D0 register is set to 1 (enable the  $I^2C$  bus interface interrupt of data receive completion). The PIN bit is synchronized with the last clock and the falling edge of the ACK clock. Then, the PIN bit is set to 0 and  $I^2C$  bus interface interrupt request is generated. Figure 16.11 shows the timing of the  $I^2C$  bus interface interrupt request generation.

The PIN bit is set to 1 in one of the following conditions:

•When data is written to the S00 register

•When data is written to the S20 register (when the WIT bit is set to 1 and the internal WAIT flag is set to 1)

•When the ES0 bit in the S1D0 register is set to 0 (I<sup>2</sup>C bus interface disabled)

•When the IHR bit in the S1D0 register is set to 1(reset)

The PIN bit is set to 0 in one of the following conditions:

•With completion of 1-byte data transmit (including a case when arbitration lost is detected)

•With completion of 1-byte data receive

•When the ALS bit in the S1D0 register is set to 0 (addressing format) and slave address is matched or general call address is received successfully in slave receive mode

•When the ALS bit is set to 1 (free format) and the address data is received successfully in slave receive mode

## 16.5.6 Bit 5: Bus Busy Flag (BB)

The BB flag indicates the operating conditions of the bus system. When the BB flag is set to 0, a bus system is not in use and a START condition can be generated. The BB flag is set and reset based on an input signal of the SCL and SDA pins either in master mode or in slave mode. When the START condition is detected, the BB flag is set to 1. On the other hand, when the STOP condition is detected, the BB flag is set to 0. Bits SSC4 to SSC0 in the S2D0 register decide to detect between the START condition and the STOP condition. When the ES0 bit in the S1D0 register is set to 0 (I<sup>2</sup>C bus interface disabled) or when the IHR bit in the S1D0 register is set to 1 (reset), the BB flag is set to 0. Refer to **16.9 START Condition Generation Method and 16.11 STOP Condition Generation Method**.

Figure 16.11 Interrupt request signal generation timing

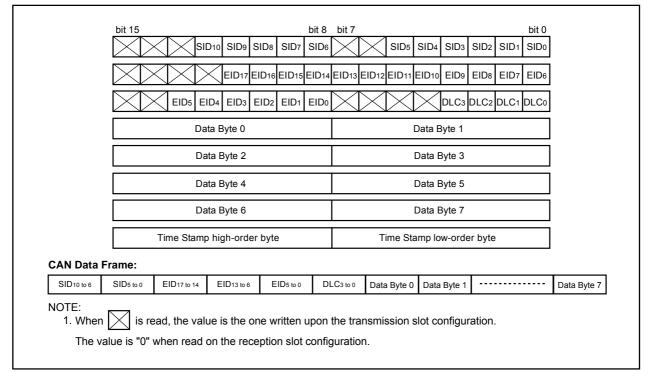

bit 0 bit 7 SID10 SID9 SID8 SID7 SID6 SID4 SID5 SID3 SID<sub>2</sub> SID1 SID<sub>0</sub> EID<sub>14</sub> EID<sub>17</sub> EID<sub>16</sub> EID<sub>15</sub> EID13 EID12 EID11 EID10 EID9 EID8 EID7 EID6 FID4 EID2 EID5 EID3 EID1 EID<sub>0</sub> DLC3 DLC2 DLC1 DLC<sub>0</sub> Data Byte 0 Data Byte 1 Data Byte 7 Time Stamp high-order byte Time Stamp low-order byte **CAN Data Frame:** SID 10 to 6 SID5 to 0 EID17 to 14 EID13 to 6 EID5 to 0 DLC3 to 0 Data Byte 0 Data Byte 1 -----Data Byte 7 NOTE: 1. When |X| is read, the value is the one written upon the transmission slot configuration. The value is 0 when read on the reception slot configuration.

**Figures 17.2** and **17.3** show the bit mapping in each slot in byte access and word access. The content of each slot remains unchanged unless transmission or reception of a new message is performed.

Figure 17.2 Bit Mapping in Byte Access

Figure 17.3 Bit Mapping in Word Access

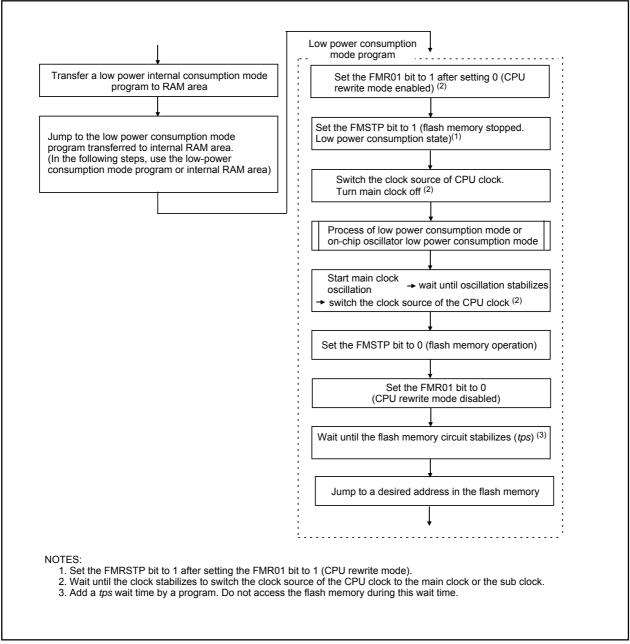

Figure 20.10 Processing Before and After Low Power Dissipation Mode

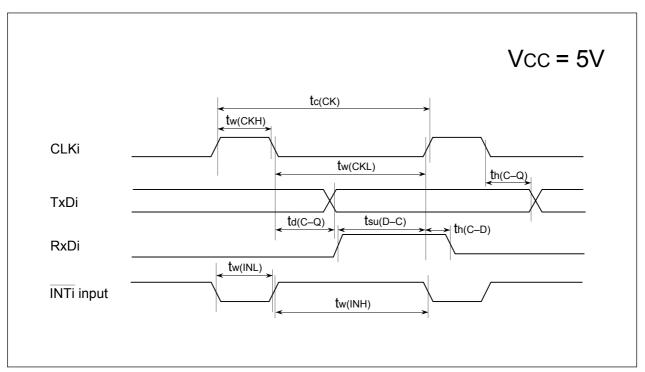

Figure 21.2 Timing Diagram (2)

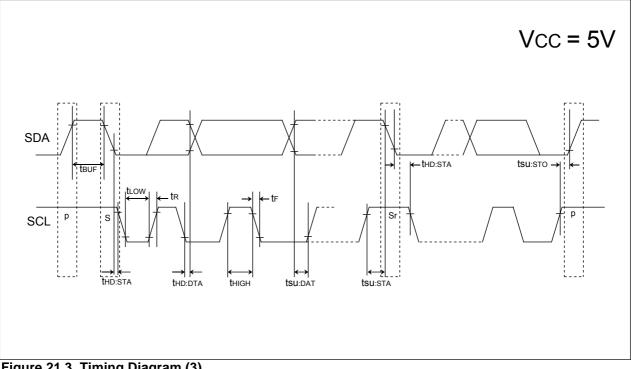

Figure 21.3 Timing Diagram (3)

#### **Timing Requirements**

# Vcc = 5V

(VCC = 5V, VSS = 0V, at Topr = - 40 to 85°C unless otherwise specified)

| O week al | Deveryeter                          | Standard | clock mode | High-speed | Unit |      |  |

|-----------|-------------------------------------|----------|------------|------------|------|------|--|

| Symbol    | Parameter                           | Min.     | Max.       | Min. Max.  |      | Unit |  |

| tBUF      | Bus free time                       | 4.7      |            | 1.3        |      | μs   |  |

| tHD;STA   | The hold time in start condition    | 4.0      |            | 0.6        |      | μs   |  |

| tLOW      | The hold time in SCL clock 0 status | 4.7      |            | 1.3        |      | μs   |  |

| tR        | SCL, SDA signals' rising time       |          | 1000       | 20+0.1Cb   | 300  | ns   |  |

| tHD;DAT   | Data hold time                      | 0        |            | 0          | 0.9  | μs   |  |

| tHIGH     | The hold time in SCL clock 1 status | 4.0      |            | 0.6        |      | μs   |  |

| tF        | SCL, SDA signals' falling time      |          | 300        | 20+0.1Cb   | 300  | ns   |  |

| tsu;DAT   | Data setup time                     | 250      |            | 100        |      | ns   |  |

| tsu;STA   | The setup time in restart condition | 4.7      |            | 0.6        |      | μs   |  |

| tsu;STO   | Stop condition setup time           | 4.0      |            | 0.6        |      | μs   |  |

#### Table 21.61 Multi-master I<sup>2</sup>C bus Line

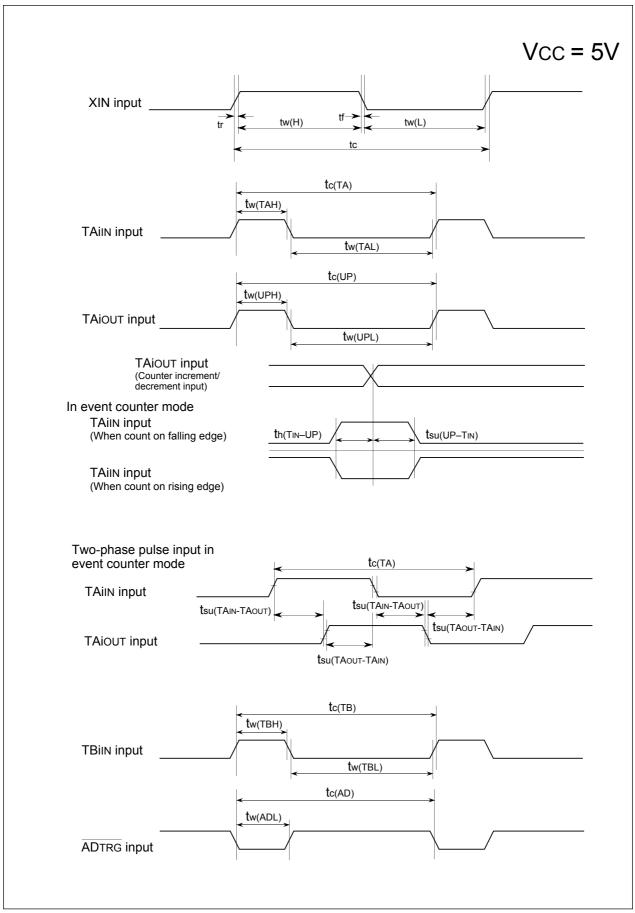

Figure 21.13 Timing Diagram (1)

# 22.6 Timers

## 22.6.1 Timer A

#### 22.6.1.1 Timer A (Timer Mode)

1. The timer remains idle after reset. Set the mode, count source, counter value, etc. using the TAiMR (i = 0 to 4) register and the TAi register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure the TAiMR register is modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. While counting is in progress, the counter value can be read out at any time by reading the TAi register. However, if the TAi register is read at the same time the counter is reloaded, the read value is always FFFF16. If the TAi register is read after setting a value in it, but before the counter starts counting, the read value is the one that has been set in the register.

- 3. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

#### 22.6.1.2 Timer A (Event Counter Mode)

The timer remains idle after reset. Set the mode, count source, counter value, etc. using the TAiMR (i = 0 to 4) register, the TAi register, the UDF register, bits TAZIE, TA0TGL, and TA0TGH in the ONSF register and the TRGSR register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure bits TAZIE, TA0TGL, and TA0TGH in the TAiMR register, the UDF register, the ONSF register, and the TRGSR register are modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. While counting is in progress, the counter value can be read out at any time by reading the TAi register. However, if the TAi register is read at the same time the counter is reloaded, the read value is always FFFF16 when the timer counter underflows and 000016 when the timer counter overflows. If the TAi register is read after setting a value in it, but before the counter starts counting, the read value is the one that has been set in the register.

- 3. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

# **REVISION HISTORY**

# M16C/29 Hardware Manual

| Rev. | Date |         | Description                                                                                         |

|------|------|---------|-----------------------------------------------------------------------------------------------------|

|      |      | Page    | Summary                                                                                             |

|      |      | 63      | • Figure 7.11 State Transition to Stop Mode and Wait Mode modified, Note 7 is added                 |

|      |      | 64      | • Figure 7.12 State Transition in Normal Mode modified, note 5 deleted, note 6                      |

|      |      |         | and 7 are simplified                                                                                |

|      |      | 65      | Table 7.7 Allowed Transition and Setting note 2 partially modified, table con                       |

|      |      |         | tents are partially modified                                                                        |

|      |      | 68      | Figure 7.13 Procedure to Switch Clock Source From On-chip Oscillator                                |

|      |      |         | Clock to Main Clock is modified                                                                     |

|      |      |         | Interrupt                                                                                           |

|      |      | 70      | Note is newly added                                                                                 |

|      |      | 73      | Table 9.1 Fixed Vector Tables Note 2 is added                                                       |

|      |      |         | Watchdog Timer                                                                                      |

|      |      | 89      | <ul> <li>Additional information of the WDTS register is inserted</li> </ul>                         |

|      |      | 90      | Figure 10.1 Watchdog Timer Block Diagram modified                                                   |

|      |      |         | • Figure 10.2 WDC Register and WDTS Register All notes are deleted                                  |

|      |      | -       | 10.2 Cold Start/Warm Start Section is deleted                                                       |

|      |      |         | DMAC                                                                                                |

|      |      | 96      | Note is added                                                                                       |

|      |      |         | Timer                                                                                               |

|      |      | 105     | Figure 12.6 TRGSR Register Note 2 added                                                             |

|      |      | 117     | • 12.2 Timer B Description of A/D trigger mode modified                                             |

|      |      |         | Figure 12.15 Timer B Block Diagram "A/D trigger mode" is added                                      |

|      |      | 123     | 12.2.4 A/D Trigger Mode Description modified                                                        |

|      |      | 129     | Figure 12.28 IDB0 Register, IDB1 Register, DTT Register, and ICTB2 Regis-                           |

|      |      |         | ter Information of bit 7 and 6 modified                                                             |

|      |      | 131     | Figure 12.30 TB2SC Register Note 4 added, contents modified                                         |

|      |      | 133     | • Figure 12.32 TA1MR Register, TA2MR Register, TA4MR Register MR0 bit is                            |

|      |      |         | modified                                                                                            |

|      |      | 134     | • Figure 12.33 Triangular Wave Modulation Operation Description modified                            |

|      |      | 135     | Figure 12.34 Sawtooth Wave Modulation Operation Description modified                                |

|      |      | 139     | Figure 12.38 TPRC Register Bit map is modified                                                      |

|      |      |         | Timer S                                                                                             |

|      |      | 142     | • Figure 13.2 G1BT and G1BCR0 Registers Function of G1BT register modified,                         |

|      |      |         | note 3 is added, function of bits 5 to 3 modified, description patially modified                    |

|      |      | 143     | Figure 13.3 G1BCR1 Register Note 1 is partially added                                               |

|      |      | 146     | • Figure 13.6 G1TM0 to G1TM7 Registers Note 3 and 4 are added                                       |

|      |      | 151-166 | • Table 13.2, 13.5, 13,8, 13.9 and 13.10 Output wave form and Selectable func-<br>tion are modified |

|      |      | 155     | <ul> <li>Figure 13.15 Base Timer Reset Operation by Base Timer Reset Register</li> </ul>            |

|      |      |         | Base timer overflow request line is added, base timer interrupt line is mod                         |