# E. Renesas Electronics America Inc - M30291FATHP#U3AAI1 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                   |

| Core Size                  | -                                                                                   |

| Speed                      | -                                                                                   |

| Connectivity               | -                                                                                   |

| Peripherals                | -                                                                                   |

| Number of I/O              | -                                                                                   |

| Program Memory Size        | -                                                                                   |

| Program Memory Type        | -                                                                                   |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | -                                                                                   |

| Voltage - Supply (Vcc/Vdd) | -                                                                                   |

| Data Converters            | -                                                                                   |

| Oscillator Type            | -                                                                                   |

| Operating Temperature      | -                                                                                   |

| Mounting Type              | -                                                                                   |

| Package / Case             | -                                                                                   |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fathp-u3aai1 |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Quick Reference to Pages Classified by Address

| Address            | Register                                 | Symbol   | Page | Address | Register                                                | Symbol | Page   |

|--------------------|------------------------------------------|----------|------|---------|---------------------------------------------------------|--------|--------|

| 018016             |                                          |          |      | 024016  |                                                         |        |        |

| 018116             |                                          |          |      | 024116  |                                                         |        |        |

| 018216             |                                          |          |      | 024216  | CAN0 acceptance filter support register                 | C0AFS  | 299    |

| 018316             |                                          |          |      | 024316  |                                                         |        |        |

| 018416             |                                          |          |      | 024416  |                                                         |        |        |

| 018516             |                                          |          |      | 024516  |                                                         |        |        |

| 018616             |                                          |          |      | 024616  |                                                         |        |        |

|                    |                                          |          |      | 024716  |                                                         |        |        |

|                    |                                          |          | I.   | 024816  |                                                         |        |        |

|                    |                                          |          |      | 024916  |                                                         |        |        |

| 01B016             |                                          |          |      | 024A16  |                                                         |        |        |

| 01B116             |                                          |          |      | 024C16  |                                                         |        |        |

| 01B216             |                                          |          |      | 024D16  |                                                         |        |        |

| 01B316             | Flash memory control register 4 (Note 2) | FMR4     | 342  | 024E16  |                                                         |        |        |

| 01B4 <sub>16</sub> |                                          |          |      | 024F16  |                                                         |        |        |

| 01B516             | Flash memory control register 1 (Note 2) | FMR1     | 341  | 025016  |                                                         |        |        |

| 01B616             |                                          |          |      | 025116  |                                                         |        |        |

| 01B7 <sub>16</sub> | Flash memory control register 0 (Note 2) | FMR0     | 341  | 025216  |                                                         |        |        |

| 01B816             |                                          |          |      | 025316  |                                                         |        |        |

| 01B916             |                                          |          |      | 025416  |                                                         |        |        |

| 01BA16             |                                          |          |      | 025516  |                                                         |        |        |

| 01BB16             |                                          |          |      | 025616  |                                                         |        | +      |

| 01BC16             |                                          |          |      | 025716  |                                                         |        |        |

|                    |                                          |          |      | 025816  |                                                         |        |        |

|                    |                                          |          | 1    | 025916  |                                                         |        |        |

|                    |                                          |          |      | 025A16  | Three-phase protect control register                    | TPRC   | 139    |

|                    |                                          | COMCTLO  | 292  | 025B16  |                                                         |        |        |

| 020116             | CAN0 message control register 1          | C0MCTL1  | 292  |         | On-chip oscillator control register                     | ROCR   | 50     |

|                    | CAN0 message control register 2          | C0MCTL2  | 292  |         | Pin assignment control register                         | PACR   | 177, 3 |

| 020316             | CAN0 message control register 3          | COMCTL3  | 292  |         | Peripheral clock select register                        | PCLKR  | 52     |

|                    | CAN0 message control register 4          | COMCTL4  | 292  | 025F16  | CAN0 clock select register                              | CCLKR  | 53     |

| 020516             | CAN0 message control register 5          | C0MCTL5  | 292  |         |                                                         |        |        |

| 020616             | CAN0 message control register 6          | COMCTL6  | 292  |         |                                                         |        |        |

| 020716             | CAN0 message control register 7          | C0MCTL7  | 292  |         |                                                         |        |        |

| 020816             | CAN0 message control register 8          | COMCTL8  | 292  |         |                                                         |        |        |

| 020916             | CAN0 message control register 9          | C0MCTL9  | 292  |         |                                                         |        |        |

| 020A16             | CAN0 message control register 10         | C0MCTL10 | 292  |         |                                                         |        |        |

| 020B16             | CAN0 message control register 11         | C0MCTL11 | 292  |         |                                                         |        |        |

| 020C16             | CAN0 message control register 12         | C0MCTL12 | 292  |         |                                                         |        |        |

| 020D16             | CAN0 message control register 13         | C0MCTL13 | 292  |         |                                                         |        |        |

| 020E16             | CAN0 message control register 14         | C0MCTL14 | 292  |         |                                                         |        |        |

| 020F16             | CAN0 message control register 15         | C0MCTL15 | 292  |         |                                                         |        |        |

| 021016             |                                          |          | 202  |         |                                                         |        |        |

| 021116             | CAN0 control register                    | C0CTLR   | 293  |         |                                                         |        |        |

| 021216             | CAN0 status register                     | COSTR    | 294  |         |                                                         |        |        |

| 021316             |                                          |          |      |         |                                                         |        |        |

| 021416             | CAN0 slot status register                | COSSTR   | 295  |         |                                                         |        |        |

| 021516             |                                          |          |      | 0       | 1200 data abiti na siat                                 | 000    | 0.50   |

| 021616             | CAN 0 interrupt control register         | COICR    | 296  |         | I <sup>2</sup> C0 data shift register                   | S00    | 258    |

| 021716             |                                          |          |      | 02E116  | 1200                                                    | 0000   |        |

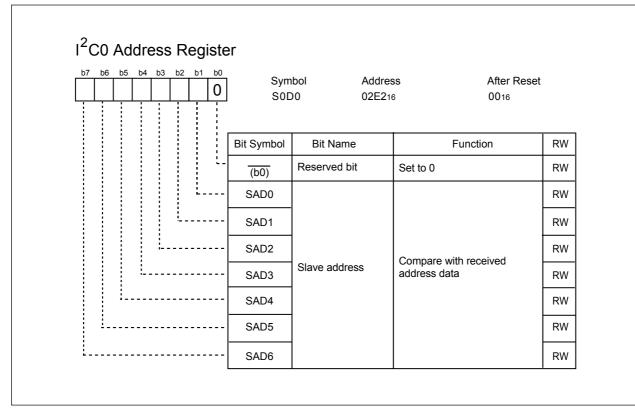

| 021816             | CAN0 extended ID register                | COIDR    | 296  |         | I <sup>2</sup> C0 address register                      | S0D0   | 257    |

| 021916             |                                          |          | •    |         | I <sup>2</sup> C0 control register 0                    | S1D0   | 259    |

| 021A16             | CAN0 configuration register              | C0CONR   | 297  |         | I <sup>2</sup> C0 clock control register                | S20    | 258    |

| 021B16             |                                          |          |      |         | I <sup>2</sup> C0 start/stop condition control register | S2D0   | 263    |

| 021C16             | CAN0 receive error count register        | CORECR   | 298  |         | I <sup>2</sup> C0 control register 1                    | S3D0   | 261    |

| 021D16             | CAN0 transmit error count register       | COTECR   | 298  |         | I <sup>2</sup> C0 control register 2                    | S4D0   | 262    |

| 021E16             | CAN0 time stamp register                 | COTSR    | 299  | 02E816  | I <sup>2</sup> C0 status register                       | S10    | 260    |

| 021F16             | יראיט נווויב אמוויף ובטואנבו             | SUISK    | 233  | 02E916  |                                                         |        |        |

| 021016             |                                          |          |      | 02EA16  |                                                         |        |        |

|                    |                                          |          |      |         |                                                         |        |        |

|                    |                                          |          |      |         |                                                         |        |        |

|                    |                                          |          |      |         |                                                         |        |        |

| 02FE16             |                                          |          |      | 02FE16  |                                                         |        |        |

|                    |                                          |          | 7    | 02FF16  |                                                         |        | 1      |

Note 1: The blank areas are reserved and cannot be accessed by users. Note 2: This register is included in the flash memory version.

## Table 1.5 Product List (3) -V Version

#### As of March, 2007

| Type Number     | ROM<br>Capacity | RAM<br>Capacity | Package Type           | Remarks         | Product<br>Code |

|-----------------|-----------------|-----------------|------------------------|-----------------|-----------------|

| M30290FAVHP     | 96 K + 4 K      | 8 K             | PLQP0080KB-A (80P6Q-A) | Flash<br>Memory |                 |

| M30290FCVHP     | 128 K + 4 K     | 12 K            |                        |                 | U3, U5,         |

| M30291FAVHP     | 96 K + 4 K      | 8 K             | PLQP0064KB-A (64P6Q-A) |                 | U7, U9          |

| M30291FCVHP     | 128 K + 4 K     | 12 K            | FLQF0004RD-A(04F0Q-A)  |                 |                 |

| M30290M8V-XXXHP | 64 K            | 4 K             |                        |                 |                 |

| M30290MAV-XXXHP | 96 K            | 8 K             | PLQP0080KB-A (80P6Q-A) |                 |                 |

| M30290MCV-XXXHP | 128 K           | 12 K            | -                      | Mask            | UO              |

| M30291M8V-XXXHP | 64 K            | 4 K             |                        | ROM             | 00              |

| M30291MAV-XXXHP | 96 K            | 8 K             | PLQP0064KB-A (64P6Q-A) |                 |                 |

| M30291MCV-XXXHP | 128 K           | 12 K            |                        |                 |                 |

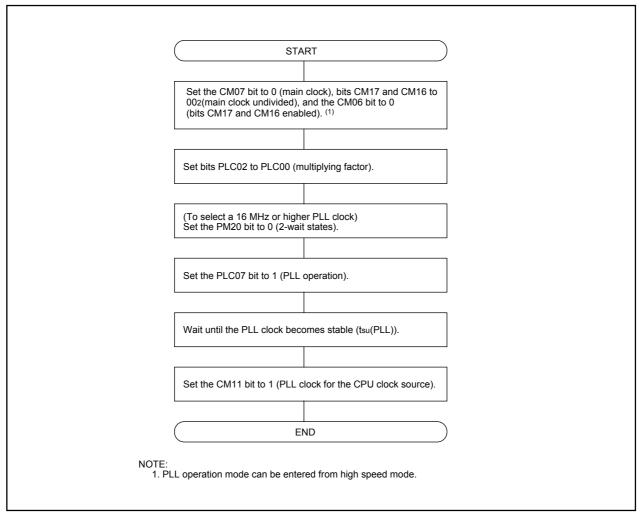

Figure 7.10 Procedure to Use PLL Clock as CPU Clock Source

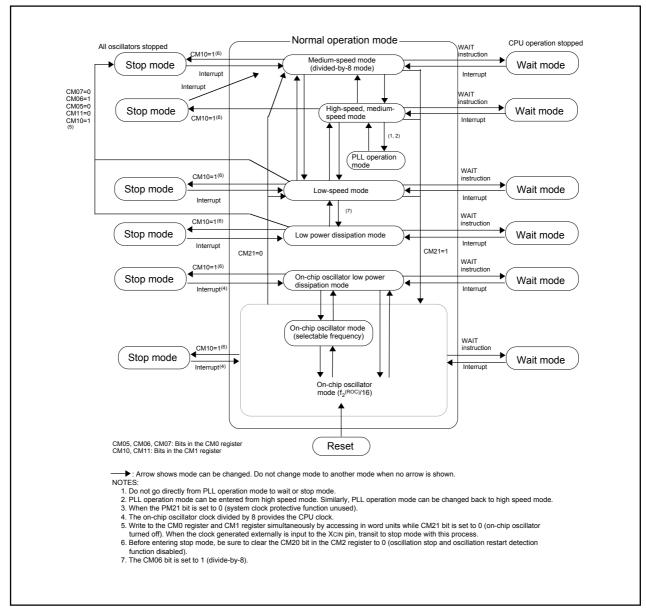

Figure 7.11 shows the state transition from normal operation mode to stop mode and wait mode. Figure 7.12 shows the state transition in normal operation mode.

**Table 7.7** shows a state transition matrix describing allowed transition and setting. The vertical line shows current state and horizontal line shows state after transition.

Figure 7.11 State Transition to Stop Mode and Wait Mode

#### 9.3.1 I Flag

The I flag enables or disables the maskable interrupt. Setting the I flag to 1 (= enabled) enables the maskable interrupt. Setting the I flag to 0 (= disabled) disables all maskable interrupts.

### 9.3.2 IR Bit

The IR bit is set to 1 (= interrupt requested) when an interrupt request is generated. Then, when the interrupt request is accepted and the CPU branches to the corresponding interrupt vector, the IR bit is cleared to 0 (= interrupt not requested).

The IR bit can be cleared to 0 in a program. Note that do not write 1 to this bit.

#### 9.3.3 ILVL2 to ILVL0 Bits and IPL

Interrupt priority levels can be set using bits ILVL2 to ILVL0.

**Table 9.3** shows the settings of interrupt priority levels and **Table 9.4** shows the interrupt priority levels enabled by the IPL.

The following are conditions under which an interrupt is accepted:

- · I flag = 1

- · IR bit = 1

- · interrupt priority level > IPL

The I flag, IR bit, bits ILVL2 to ILVL0, and IPL are independent of each other. In no case do they affect one another.

| ILVL2 to ILVL0 bits | Interrupt priority<br>level  | Priority<br>order |

|---------------------|------------------------------|-------------------|

| 0002                | Level 0 (interrupt disabled) |                   |

| 0012                | Level 1                      | Low               |

| 0102                | Level 2                      |                   |

| 0112                | Level 3                      |                   |

| 1002                | Level 4                      |                   |

| 1012                | Level 5                      |                   |

| 1102                | Level 6                      | ↓                 |

| 1112                | Level 7                      | High              |

#### Table 9.3 Settings of Interrupt Priority Levels

#### Table 9.4 Interrupt Priority Levels Enabled by IPL

| IPL  | Enabled interrupt priority levels        |

|------|------------------------------------------|

| 0002 | Interrupt levels 1 and above are enabled |

| 0012 | Interrupt levels 2 and above are enabled |

| 0102 | Interrupt levels 3 and above are enabled |

| 0112 | Interrupt levels 4 and above are enabled |

| 1002 | Interrupt levels 5 and above are enabled |

| 1012 | Interrupt levels 6 and above are enabled |

| 1102 | Interrupt levels 7 and above are enabled |

| 1112 | All maskable interrupts are disabled     |

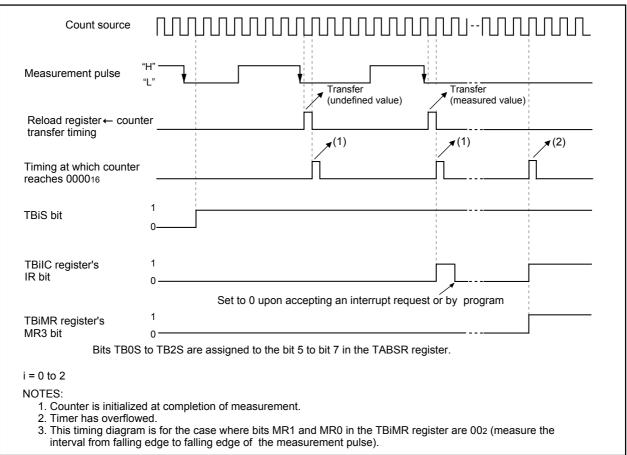

Figure 12.21 Operation timing when measuring a pulse period

| Count source                                                       |                                                                                                                                                                                         |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement pulse                                                  | "H"<br>"L" Transfer Transfer Transfer                                                                                                                                                   |

| Reload register ← coun<br>transfer timing                          |                                                                                                                                                                                         |

| Timing at which counter reaches 000016                             |                                                                                                                                                                                         |

| TBiS bit                                                           |                                                                                                                                                                                         |

| TBilC register's<br>IR bit                                         |                                                                                                                                                                                         |

|                                                                    | Set to 0 upon accepting an interrupt request or by program                                                                                                                              |

| The MR3 bit in the<br>TBiMR register                               | 0                                                                                                                                                                                       |

| Bits T                                                             | B0S to TB2S are assigned to the bit 5 to bit 7 in the TABSR register.                                                                                                                   |

| i = 0 to 2                                                         |                                                                                                                                                                                         |

| <ol> <li>Timer has overflow</li> <li>This timing diagra</li> </ol> | m is for the case where bits MR1 to MR0 in the TBiMR register are 102 (measure the interval to the next rising edge and the interval from a rising edge to the next falling edge of the |

Figure 12.22 Operation timing when measuring a pulse width

RENESAS

| b6 b5 b4 b3 b2 b1 b0 | Symbol<br>INVC0 | Address<br>034816                                                | After Reset<br>0016                                                                                                                                                                                                               |    |

|----------------------|-----------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                      | Bit Symbol      | Bit Name                                                         | Function                                                                                                                                                                                                                          | RW |

|                      | INV00           | Effective interrupt output polarity select bit <sup>(3)</sup>    | <ul> <li>0: ICTB2 counter is incremented by 1 on<br/>the rising edge of timer A1 reload control<br/>signal</li> <li>1: ICTB2 counter is incremented by 1 on<br/>the falling edge of timer A1 reload control<br/>signal</li> </ul> | RW |

|                      | INV01           | Effective interrupt output specification bit <sup>(2, 3)</sup>   | 0: ICTB2 counter incremented by 1 at a<br>timer B2 underflow<br>1: Selected by INV00 bit                                                                                                                                          | RW |

|                      | INV02           | Mode select bit <sup>(4)</sup>                                   | 0: Three-phase motor control timer<br>function unused<br>1: Three-phase motor control timer<br>function (5)                                                                                                                       | RW |

|                      | INV03           | Output control bit <sup>(6)</sup>                                | 0: Three-phase motor control timer output<br>disabled (5)<br>1: Three-phase motor control timer output<br>enabled                                                                                                                 | RW |

|                      | INV04           | Positive and negative<br>phases concurrent output<br>disable bit | 0: Simultaneous active output enabled<br>1: Simultaneous active output disabled                                                                                                                                                   | RW |

|                      | INV05           | Positive and negative<br>phases concurrent output<br>detect flag | 0: Not detected yet<br>1: Already detected <sup>(7)</sup>                                                                                                                                                                         | RW |

|                      | INV06           | Modulation mode select bit <sup>(8)</sup>                        | 0: Triangular wave modulation mode<br>1: Sawtooth wave modulation mode <sup>(9)</sup>                                                                                                                                             | RW |

|                      | INV07           | Software trigger select bit                                      | Setting this bit to 1 generates a transfer<br>trigger. If the INV06 bit is 1, a trigger for the<br>dead time timer is also generated. The<br>value of this bit when read is 0                                                     | RW |

NOTES:

1. Write to this register after setting the PRC1 bit in the PRCR register to 1 (write enable). Note also that bits INV00 to INV02, bits INV04 and INV06 can only be rewritten when timers A1, A2, A4 and B2 are idle.

2. If this bit needs to be set to 1, set any value in the ICTB2 register before writing to it.

3. Effective when the INV11 bit in the INV1 register is 1 (three-phase mode 1). If INV11 is set to 0 (three-phase mode 0), the ICTB2 counter is incremented by 1 each time the timer B2 underflows, regardless of whether the INV00 and INV01 bits are set. When setting the INV01 bit to 1, the first interrupt is generated when the timer B2 underflows n-1 times, if n is the value set in the ICTB2 counter. Subsequent interrupts are generated every n times the timer B2 underflow.

4. Setting the INV02 bit to 1 activates the dead time timer, U/V/W-phase output control circuits and ICTB2 counter.

5. When the INV02 bit is set to 1 and the INV03 bit is set to 0, Ū, U, ∇, V, ₩, W pins, including pins shared with other output functions, enter a high-impedance state. When INV03 is set to 1, U/V/W corresponding pins generate the three-phase PWM output.

6. The INV03 bit is set to 0 in the following cases:

When reset

• When positive and negative go active (INV05 = 1) simultaneously while INV04 bit is 1

• When set to 0 by program

• When input on the SD pin changes state from "H" to "L" regardless of the value of the INVCR1 bit. (The INV03 bit cannot be set to 1 when SD input is "L".) INV03 is set to 0 when both bits INV05 and INV04 are set to 1.

| Item                                                                                               | INV06=0                                                                                                     | INV06=1                                                                                                |  |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Mode                                                                                               | Triangular wave modulation mode                                                                             | Sawtooth wave modulation mode                                                                          |  |

| Timing at which transferred from registers<br>IDB0 to IDB1 to three-phase output shift<br>register | Transferred only once synchronously<br>with the transfer trigger after writing to<br>registers IDB0 to IDB1 | Transferred every transfer trigger                                                                     |  |

| Timing at which dead time timer trigger is generated when INV16 bit is 0                           | Synchronous with the falling edge of timer A1, A2, or A4 one-shot pulse                                     | Synchronous with the transfer<br>trigger and the falling edge of timer<br>A1, A2, or A4 one-shot pulse |  |

| INV13 bit                                                                                          | Effective when INV11 is set to 1 and INV06 is set to 0                                                      | No effect                                                                                              |  |

Transfer trigger: Timer B2 underflow, write to the INV07 bit or write to the TB2 register when the INV10 bit is set to 1.

9: If the INV06 bit is set to 1, set the INV11 bit to 0 (three-phase mode 0) and set the PWCON bit to 0 (timer B2 reloaded by a timer B2 underflow)

10. When the PFCi (i = 0 to 5) bit in the PFCR register is set to 1 (three-phase PWM output), individual pins are enabled to output.

#### Figure 12.26 INVC0 Register

## 12.3.2 Three-phase/Port Output Switch Function

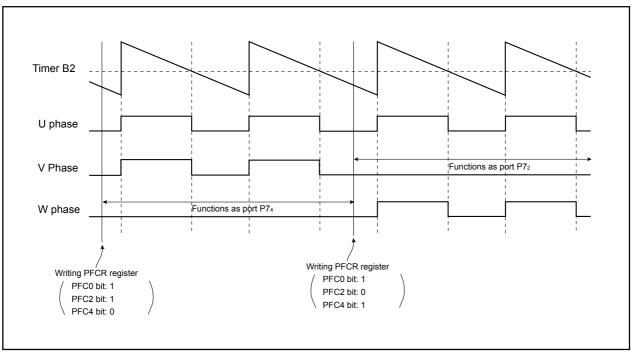

When the INVC03 bit in the INVC0 register set to 1 (Timer output enabled for three-phase motor control) and setting the PFCi (i=0 to 5) in the PFCR register to 0 (I/O port), the three-phase PWM output pin (U,  $\overline{U}$ , V,  $\overline{V}$ , W and  $\overline{W}$ ) functions as I/O port. Each bit of the PFCi bits (i=0 to 5) is applicable for each one of three-phase PWM output pins. **Figure 12.37** shows the example of three-phase/port output switch function. **Figure 12.38** shows the PFCR register and the three-phase protect control register.

Figure 12.37 Usage Example of Three-phse/Port Output Switch Function

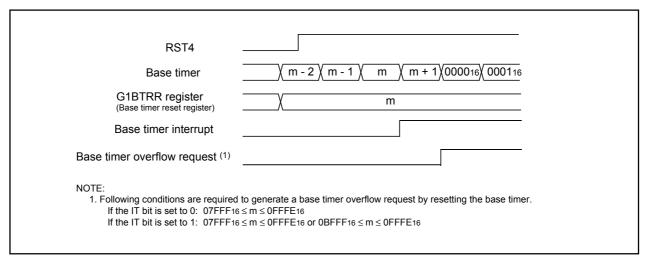

## 13.1.1 Base Timer Reset Register(G1BTRR)

The G1BTRR register provides the capability to reset the base timer when the base timer count value matches the value stored in the G1BTRR register. The G1BTRR register is enabled by the RST4 bit in the G1BCR0 register. This function is identical in operation to the G1PO0 base timer reset that is enabled by the RST1 bit in the G1BCR0 register. If the free-running operation is not selected, the channel 0 can be used for a waveform generation when the base timer is reset by the G1BTRR register. Do not enable bits RST1 and RST4 simultaneously.

Figure 13.15 Base Timer Reset operation by Base Timer Reset Register

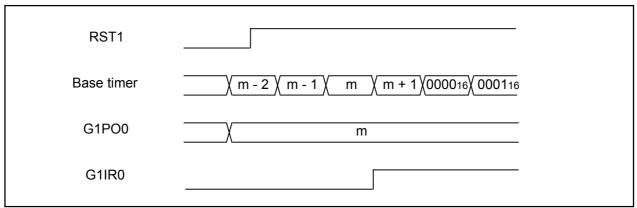

Figure 13.16 Base Timer Reset operation by G1PO0 register

| RST2                                   |                                                                                   |

|----------------------------------------|-----------------------------------------------------------------------------------|

| Base timer                             | <u> m - 2 m - 1 m m m + 1 000016 000116</u>                                       |

| P83/INT1                               |                                                                                   |

| NOTE:<br>1. INT1 Base Timer reset does | s not generate a Base Timer interrupt. INT1 may generate an interrupt if enabled. |

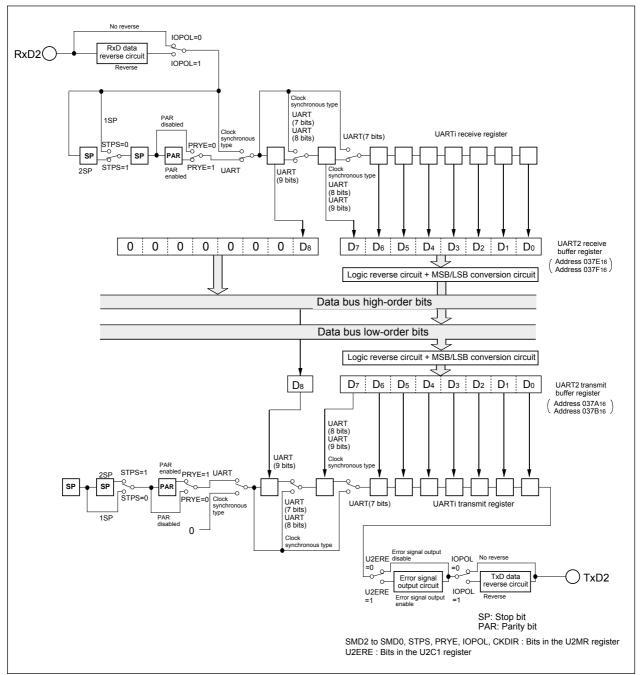

Figure 14.3 Block diagram of UART2 transmit/receive unit

#### 14.1.2.4 Serial Data Logic Switching Function (UART2)

The data written to the U2TB register has its logic reversed before being transmitted. Similarly, the received data has its logic reversed when read from the U2RB register. **Figure 14.19** shows serial data logic.

| (1) When the          | U2LCH bit in the U2C1 register is set to 0 (no reverse)                                                                                                                                                                                                                                                                          |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Transfer clock        |                                                                                                                                                                                                                                                                                                                                  |  |

| TxD2<br>(no reverse)  | "H"                                                                                                                                                                                                                                                                                                                              |  |

| (2) When the          | U2LCH bit in the U2C1 register is set 1 (reverse)                                                                                                                                                                                                                                                                                |  |

| Transfer clock        |                                                                                                                                                                                                                                                                                                                                  |  |

| TxD2<br>(reverse)     | "H" <u>ST ( D0 ) D1 ) D2 ( D3 ) D4 ) D5 ) D6 ( D7 ) P</u> SP                                                                                                                                                                                                                                                                     |  |

| (transmit<br>the U2C0 | ies to the case where the CKPOL bit in the U2C0 register is set to 0 P: Parity bit<br>data output at the falling edge of the transfer clock), the UFORM bit in SP: Stop bit<br>0 register is set to 0 (LSB first), the STPS bit in the U2MR register is set<br>op bit) and the PRYE bit in the U2MR register is set to 1 (parity |  |

Figure 14.19 Serial Data Logic Switching

#### 14.1.2.5 TxD and RxD I/O Polarity Inverse Function (UART2)

This function inverses the polarities of the TxD2 pin output and RxD2 pin input. The logic levels of all input/output data (including the start, stop and parity bits) are inversed. **Figure 14.20** shows the TxD pin output and RxD pin input polarity inverse.

| (1) When the IOPOL bit in the U2MR register is set to 0 (no reverse)                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                               |

| TxD2 "H" ST / D0 / D1 / D2 / D3 / D4 / D5 / D6 / D7 / P / SP                                                                                                                                                                                                                                  |

| RxD2 "H" ST ( D0 ) D1 ) D2 ) D3 ) D4 ) D5 ) D6 ) D7 ) P ) SP<br>(no reverse) "L"                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                               |

| (2) When the IOPOL bit in the U2MR register is set to 1 (reverse)                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                               |

| ТхD2 "H"<br>(reverse) "L" ST <u>V D0 V D1 V D2 V D3 V D4 V D5 V D6 V D7 V</u> P V SP                                                                                                                                                                                                          |

| RxD2         "H"         ST         D0         D1         D2         D3         D4         D5         D6         D7         P         SP           (reverse)                                                                                                                                  |

| NOTE:<br>1. This applies to the case where the UFORM bit in the U2C0 register is set<br>to 0 (LSB first), the STPS bit in the U2MR register is set to 0 (1 stop bit)<br>and the PRYE bit in the U2MR register is set to 1 (parity enabled).<br>ST: Start bit<br>P: Parity bit<br>SP: Stop bit |

Figure 14.20 TxD and RxD I/O Polarity Inverse

#### 15.1.7 Delayed Trigger Mode 0

In delayed trigger mode 0, analog voltages applied to the selected pins are converted one-by-one to a digital code. The delayed trigger mode 0 used in combination with A/D trigger mode of Timer B. The Timer B0 underflow starts a single sweep conversion. After completing the ANo pin conversion, the AN1 pin is not sampled and converted until the Timer B1 underflow is generated. When the Timer B1 underflow is generated, the single sweep conversion is restarted with the AN1 pin. **Table 15.10** shows the delayed trigger mode 0 specifications. **Figure 15.19** shows the operation example in delayed trigger mode 0. **Figures 15.20** and **15.21** show each flag operation in the ADSTAT0 register that corresponds to the operation example. **Figure 15.22** shows registers ADCON0 to ADCON2 in delayed trigger mode 0. **Figure 15.23** shows the ADTRGCON register in delayed trigger mode 0 and **Table 15.11** shows the trigger select bit setting in delayed trigger mode 0.

| Item                      | Specification                                                                          |

|---------------------------|----------------------------------------------------------------------------------------|

| Function                  | Bits SCAN1 and SCAN0 in the ADCON1 register and bits ADGSEL1 and ADGSEL0               |

|                           | in the ADCON2 register select pins. Analog voltage applied to the input voltage of     |

|                           | the selected pins are converted one-by-one to the digital code. At this time, timer B0 |

|                           | underflow generation starts ANo pin conversion. Timer B1 underflow generation          |

|                           | starts conversion after the AN1 pin. <sup>(1)</sup>                                    |

| A/D Conversion Start      | ANo pin conversion start condition                                                     |

|                           | •When Timer B0 underflow is generated if Timer B0 underflow is generated again         |

|                           | before Timer B1 underflow is generated , the conversion is not affected                |

|                           | •When Timer B0 underflow is generated during A/D conversion of pins after the          |

|                           | AN1 pin, conversion is halted and the sweep is restarted from the AN0 pin again        |

|                           | AN1 pin conversion start condition                                                     |

|                           | •When Timer B1 underflow is generated during A/D conversion of the ANo pin, the        |

|                           | input voltage of the AN1 pin is sampled. The AN1 conversion and the rest of the        |

|                           | sweep start when AN <sub>0</sub> conversion is completed.                              |

| A/D Conversion Stop       | •When single sweep conversion from the AN0 pin is completed                            |

| Condition                 | •Set the ADST bit to 0 (A/D conversion halted) <sup>(2)</sup>                          |

| Interrupt request         | A/D conversion completed                                                               |

| generation timing         |                                                                                        |

| Analog input pin          | Select from AN0 to AN1 (2 pins), AN0 to AN3 (4 pins), AN0 to AN5 (6 pins)              |

|                           | and AN₀ to AN⁊ (8 pins) <sup>(3)</sup>                                                 |

| Readout of A/D conversion | Readout one of registers AN0 to AN7 that corresponds to the selected pins              |

| result                    |                                                                                        |

#### Table 15.10 Delayed Trigger Mode 0 Specifications

NOTES:

- 1. Set the larger value than the value of the timer B0 register to the timer B1 register. The count source for timer B0 and timer B1 must be the same.

- 2. Do not write 1 (A/D conversion started) to the ADST bit in delayed trigger mode 0. When write 1, unexpected interrupts may be generated.

- 3. AN00 to AN07, AN 20 to AN27, and AN30 to AN32 can be used in the same way as AN0 to AN7. However, all input pins need to belong to the same group.

Figure 16.2 S0D0 Register

| SCL                            | 7 clock     | 8 clock               | ACI     |              | 1 c    | ock |       |        |

|--------------------------------|-------------|-----------------------|---------|--------------|--------|-----|-------|--------|

| SDA                            | 7 bit       | 8 bit                 | Даск в  |              | ) 1 bi | : X |       |        |

| ACKBIT bit                     | ,           |                       |         |              | / \    |     |       |        |

| -                              |             |                       |         |              |        |     |       |        |

| PIN flag                       |             |                       |         |              |        |     |       |        |

| Internal WAIT flag             |             |                       |         |              |        |     |       |        |

| I <sup>2</sup> C bus interface |             |                       |         |              |        |     |       |        |

| The writing signal of          |             |                       |         |              |        |     |       |        |

|                                |             |                       |         |              |        |     |       |        |

| the S00 register               |             | <b>L</b> H _ <b>d</b> |         |              |        |     |       |        |

| receive mode, ACK              | bit = 1 WIT | bit = 1<br>8 clock    |         | ACK<br>clock |        |     |       |        |

| receive mode, ACK              |             |                       |         |              |        |     | 1 bit | <br>X  |

| receive mode, ACK              | 7 clock     | 8 clock               | ]<br>_X |              |        |     | 1 bit | X      |

| receive mode, ACK              | 7 clock     | 8 clock               |         |              |        |     | 1 bit | X<br>X |

| receive mode, ACK              | 7 clock     | 8 clock               |         |              |        |     | 1 bit | X<br>X |

| receive mode, ACK              | 7 clock     | 8 clock               | 1)      |              | 2)     |     |       | X<br>X |

| receive mode, ACK              | 7 clock     | 8 clock               | 1)      |              | 2)     |     | 1 bit | X      |

Figure 16.12 The timing of the interrupt generation at the completion of the data receive

#### 16.6.3 Bits 2,3 : Port Function Select Bits PED, PEC

If the ES0 bit in the S1D0 register is set to 1 (I<sup>2</sup>C bus interface enabled), the SDAMM functions as an output port. When the PED bit is set to 1 and the SCLMM functions as an output port when the PEC bit is set to 1. Then the setting values of bits P2\_0 and P2\_1 in the port P2 register are output to the I<sup>2</sup>C bus, regardless of he internal SCL/SDA output signals. (SCL/SDA pins are onnected to I<sup>2</sup>C bus interface circuit)

The bus data can be read by reading the port pi direction register in input mode, regardless of the setting values of the PED and PEC bits. **Table 16.5** shows the port specification.

| Pin Name | ES9 Bit | PED Bit | P20 Port Direction<br>Register | Function                                 |

|----------|---------|---------|--------------------------------|------------------------------------------|

|          | 0       | -       | 0/1                            | Port I/O function                        |

| P20      | 1       | 0       | -                              | SDA I/O function                         |

|          | 1       | 1       | -                              | SDA input function, port output function |

| Pin Name | ES0 Bit | PEC Bit | P21 Port Direction<br>Register | Function                                 |

|          | 0       | -       | 0/1                            | Port I/O function                        |

| P21      | 1       | 0       | -                              | ScL I/O function                         |

|          | 1       | 1       | -                              | ScL input function, port output funcion  |

#### **Table 16.5 Port specifications**

## 20.7 Software Commands

Read or write 16-bit commands and data from or to even addresses in the user ROM area. When writing a command code, 8 high-order bits (D15–D8) are ignored.

#### **Table 20.5 Software Commands**

|                       |       | First bus cycle | e                   | Se    | econd bus cy | cle                 |

|-----------------------|-------|-----------------|---------------------|-------|--------------|---------------------|

| Command               | Mode  | Address         | Data<br>(D15 to D0) | Mode  | Address      | Data<br>(D15 to D0) |

| Read array            | Write | Х               | xxFF16              |       |              |                     |

| Read status register  | Write | Х               | <b>xx70</b> 16      | Read  | Х            | SRD                 |

| Clear status register | Write | Х               | <b>xx50</b> 16      |       |              |                     |

| Program               | Write | WA              | <b>xx40</b> 16      | Write | WA           | WD                  |

| Block erase           | Write | Х               | <b>xx20</b> 16      | Write | BA           | xxD016              |

SRD: Status register data (D7 to D0)

WA : Write address (However, even address)

WD : Write data (16 bits)

BA : Highest-order block address (However, even address)

$X\,$  : Any even address in the user ROM area

xx : 8 high-order bits of command code (ignored)

## 20.7.1 Read Array Command (FF16)

The read array command reads the flash memory.

Read array mode is entered by writing command code xxFF16 in the first bus cycle. Content of a specified address can be read in 16-bit unit after the next bus cycle. The MCU remains in read array mode until an another command is written. Therefore, contents of multiple addresses can be read consecutively.

### 20.7.2 Read Status Register Command (7016)

The read status register command reads the status register.

By writing command code xx7016 in the first bus cycle, the status register can be read in the second bus cycle (Refer to **20.8 Status Register**). Read an even address in the user ROM area. Do not execute this command in EW mode 1.

### 20.7.3 Clear Status Register Command (5016)

The clear status register command clears the status register to 0.

By writing xx5016 in the first bus cycle, and bits FMR06 to FMR07 in the FMR0 register and bits SR4 to SR5 in the status register are set to 0.

#### **Timing Requirements**

# Vcc = 5V

## (VCC = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 21.17 | Timer B Input (Counter Input in Event Counter Mode) |

|-------------|-----------------------------------------------------|

|-------------|-----------------------------------------------------|

| Symbol  | Parameter                                           | Standard |      | Unit |

|---------|-----------------------------------------------------|----------|------|------|

| Symbol  | Parameter                                           | Min.     | Max. | Unit |

| tc(TB)  | TBin input cycle time (counted on one edge)         | 100      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on one edge)   | 40       |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on one edge)    | 40       |      | ns   |

| tc(TB)  | TBin input cycle time (counted on both edges)       | 200      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width (counted on both edges) | 80       |      | ns   |

| tw(TBL) | TBin input LOW pulse width (counted on both edges)  | 80       |      | ns   |

### Table 21.18 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    |     | dard | Unit |

|---------|------------------------------|-----|------|------|

| Symbol  |                              |     | Max. | Unit |

| tc(TB)  | TBin input cycle time        | 400 |      | ns   |

| tw(TBH) | TBilN input HIGH pulse width | 200 |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 200 |      | ns   |

#### Table 21.19 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                    |      | dard | Unit |

|---------|------------------------------|------|------|------|

| Gynibol | Falditieter                  | Min. | Max. | Unit |

| tc(TB)  | TBin input cycle time        | 400  |      | ns   |

| tw(TBH) | TBiin input HIGH pulse width | 200  |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 200  |      | ns   |

### Table 21.20 A /D Trigger Input

| Symbol  | Parameter                                     | Stan | dard | Unit  |

|---------|-----------------------------------------------|------|------|-------|

| Gymbol  | i didificici                                  | Min. | Max. | Offic |

| tc(AD)  | ADTRG input cycle time (trigger able minimum) | 1000 |      | ns    |

| tw(ADL) | ADTRG input LOW pulse width                   | 125  |      | ns    |

### Table 21.21 Serial I/O

| Symbol   | Parameter                   | Standard |      | Unit |

|----------|-----------------------------|----------|------|------|

| Symbol   | Falameter                   | Min.     | Max. | Unit |

| tc(CK)   | CLKi input cycle time       | 200      |      | ns   |

| tw(CKH)  | CLKi input HIGH pulse width | 100      |      | ns   |

| tw(CKL)  | CLKi input LOW pulse width  | 100      |      | ns   |

| td(C-Q)  | TxDi output delay time      |          | 80   | ns   |

| th(C-Q)  | TxDi hold time              | 0        |      | ns   |

| tsu(D-C) | RxDi input setup time       | 70       |      | ns   |

| th(C-D)  | RxDi input hold time        | 90       |      | ns   |

### Table 21.22 External Interrupt INTi Input

| Symbol  | Parameter                   |     | Standard |      |

|---------|-----------------------------|-----|----------|------|

| Gymbol  |                             |     | Max.     | Unit |

| tw(INH) | INTi input HIGH pulse width | 250 |          | ns   |

| tw(INL) | INTi input LOW pulse width  | 250 |          | ns   |

#### 22.6.1.4 Timer A (Pulse Width Modulation Mode)

- The timer remains idle after reset. Set the mode, count source, counter value, etc. using bits TA0TGL and TA0TGH in the TAiMR (i = 0 to 4) register, the TAi register, the ONSF register and the TRGSR register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure bits TA0TGL and TA0TGH in the TAiMR register, the ONSF register and the TRGSR register are modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. The IR bit is set to 1 when setting a timer operation mode with any of the following procedures:

- Select the PWM mode after reset.

- Change an operation mode from timer mode to PWM mode.

- Change an operation mode from event counter mode to PWM mode.

To use the timer Ai interrupt (interrupt request bit), set the IR bit to 0 by program after the above listed changes have been made.

- 3. When setting TAiS register to 0 (count stop) during PWM pulse output, the following action occurs:Stop counting.

- When TAiout pin is output "H", output level is set to "L" and the IR bit is set to 1.

- When TAiout pin is output "L", both output level and the IR bit remains unchanged.

- 4. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

## 22.7.2 Rewrite the ICOCiIC Register

When the interrupt request to the ICOCiIC register is generated during the instruction process, the IR bit may not be set to 1 (interrupt requested) and the interrupt request may not be acknowledged. At that time, when the bit in the G1IR register is held to 1 (interrupt requested), the following IC/OC interrupt request will not be generated. When changing the ICOCiIC register settiing, use the following instruction.

Subject instructions: AND, OR, BCLR, BSET

When initializing Timer S, change the ICOCiIC register setting with the request again after setting registers IOCiIC and G1IR to 0016.

### 22.7.3 Waveform Generating Function

1. If the BTS bit in the G1BCR1 register is set to 0 (base timer is reset) when the waveform is generating and the base timer is stopped counting, the waveform output pin keeps the same output level. The output level will be changed when the base timer and the G1POj register match the setting value next time after the base timer starts counting again.

2. If the G1POCRj register is set when the waveform is generated, the same setting value of the IVL bit is applied to the waveform generating pin. Do not set the G1POCRj register when the waveform is generating.

3. When the RST1 bit in the G1BCR1 register is set to 1 (the base timer is reset by matching the G1PO0 register), the base timer is reset after two clock cycles of fBT1 when the base timer value matches the G1PO0 register value. A high-level ("H") signal is applied to the OUTC10 pin between the base timer value match to the base timer reset.

## 22.7.4 IC/OC Base Timer Interrupt

If the MCU is operated in the combination selected from **Table 22.1** for use when the RST4 bit in the G1BCR0 register is set to 1 (reset the base timer that matches the G1BTRR register) to reset the base timer, an IC/OC base timer interrupt request is generated twice.

| IT Bit in the G1BCR0 Register          | G1BTRR Register                             |

|----------------------------------------|---------------------------------------------|

| 0 (bit 15 in the base timer overflows) | 07FFF16 to 0FFFE16                          |

| 1 (bit 14 in the base timer overflows) | 03FFF16 to 0FFFE16 or<br>0BFFF16 to 0FFFE16 |

The second IC/OC base timer interrupt request is generated because the base timer overflow request is generated after one fBT1 clock cycle as soon as the base timer is reset.

One of the following conditions must be met in order not to generate the IC/OC base timer interrupt request twice:

- 1) When the RST4 bit is set to 1, set the G1BTRR register with a combination other than what is listed in **Table 22.1**.

- 2) Do not reset the base timer by matching the G1BTRR register. Reset the base timer by matching the G1P00 register. In other words, do not set the RST4 bit to 1 to reset the base timer. Set the RST1 bit in the G1BCR1 register to 1 (reset the base timer that matches the G1P00 register).

## **REVISION HISTORY**

## M16C/29 Hardware Manual

| Rev. | Date       | Description |                                                                                |

|------|------------|-------------|--------------------------------------------------------------------------------|

|      |            | Page        | Summary                                                                        |

|      |            | 360         | Table 21.1 is partly revised.                                                  |

|      |            | 368         | Section "21.4.2 EW1 Mode" is partly revised.                                   |

| 0.80 | Sep/03/Y04 | 2,3         | Table 1.2.1 and Table 1.2.2 are partly revised.                                |

|      |            | 6,7         | Table 1.4.1 to Table 1.4.3 are partly revised.                                 |

|      |            | 7           | Figure 1.4.1 is partly revised.                                                |

|      |            | 8,9         | Figure 1.5.1 and Figure 1.5.2 are partly revised.                              |

|      |            | 21          | Figure 4.7 is partly revised.                                                  |

|      |            | 24          | Figure 4.10 is partly revised.                                                 |

|      |            | 26          | Section "5.1.2 Hardware Reset 2" is partly revised.                            |

|      |            | 29 to 34    | Section "5.5 Voltage Detection Circuit" is revised.                            |

|      |            | 80          | Section "10.2 Cold start / Warm start" is added.                               |

|      |            | 322         | Table 20.2 is partly revised.                                                  |

|      |            | 323         | Table 20.3 is partly revised.                                                  |

|      |            | 325         | Table 20.6 and Table 20.7 are partly revised.                                  |

|      |            | 327         | Table 20.9 is partly revised.                                                  |

|      |            | 331         | Title of Table 20.23 is partly revised.                                        |

|      |            | 335         | Table 20.25 is partly revised.                                                 |

|      |            | 339         | Title of Table 20.39 is partly revised.                                        |

|      |            | 343         | Table 20.41 is partly revised.                                                 |

|      |            | 344         | Table 20.42 is partly revised.                                                 |

|      |            | 346         | "Low Voltage Detection Circuit Electrical Characteristics" is deleted.         |

|      |            |             | Talbe 20.45 is partly revised.                                                 |

|      |            | 348         | Table 20.47 is partly revised.                                                 |

|      |            | 352         | Title of Table 20.61 is partly revised.                                        |

|      |            | 356         | Talbe 20.63 is partly revised.                                                 |

|      |            | 360         | Title of Table 20.77 is partly revised.                                        |

|      |            | 398         | 64P6Q-A package is revised.                                                    |

| 1.00 | Nov/01/Y04 | All pages   | Words standardized (on-chip oscillator, A/D)                                   |

|      |            | 2, 3        | Table1.2.1 and Table 1.2.2 are partly revised.                                 |

|      |            | 8, 9        | Table 1.4.4 to 1.4.6 and figure 1.4.2 to 1.4.6 are added.                      |

|      |            | 28          | "5.1.2 Hardware Reset 2" is partly revised.                                    |

|      |            | 29          | "5.4 Oscillation Stop Detection Reset" is partly revised.                      |

|      |            | 38          | Table 7.1 is partly revised.                                                   |

|      |            | 41          | Note 6 in Figure 7.3 is partly revised. b7 to b4 bit in Figure 7.4 is revised. |

|      |            | 42          | Figure 7.5 is partly revised.                                                  |

|      |            | 43          | "PCLKR register" in Figure 7.6 is partly revised.                              |

|      |            | 50          | "7.6.1 Normal Operation Mode" is partly revised.                               |

|      |            | 51          | Note 1 in Table 7.6.1.1 is partly revised.                                     |

|      |            | 57          | "7.8 Oscillation Stop and Re-oscillation Detect Function" is partly revised.   |

## **REVISION HISTORY**

## M16C/29 Hardware Manual

| Rev. | Date | Description |                                                                                                                                                       |

|------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      | Page        | Summary                                                                                                                                               |

|      |      | 9           | Tables 1.6 to 1.8 Product Codes modified                                                                                                              |

|      |      | 19, 20      | Table 1.14 Pin Description pin description on I/O ports modified                                                                                      |

|      |      |             | Reset                                                                                                                                                 |

|      |      | 37          | Figure 5.2 Reset Sequence Vcc and ROC timings modified                                                                                                |

|      |      |             | Processor Mode                                                                                                                                        |

|      |      | 45          | • Figure 6.2 PM2 Register Description on notes 5 and 6 modified                                                                                       |

|      |      |             | Clock Generation Circuit                                                                                                                              |

|      |      | 52          | Figure 7.6 PM2 Register Description on notes 5 and 6 modified                                                                                         |

|      |      | 64          | Figure 7.12 State Transition in Normal Mode note 2 modified                                                                                           |

|      |      |             | Protection                                                                                                                                            |

|      |      | 69          | Description on protection modified                                                                                                                    |

|      |      |             | Figure 8.1 PRCR Register note 1 modified                                                                                                              |

|      |      |             | Interrupts                                                                                                                                            |

|      |      | 88          | Table 9.6 PC Value Saved in Stack Area When Address Match Interrupt                                                                                   |

|      |      |             | Request I Acknowledged instruction modified                                                                                                           |

|      |      |             | Watchdog Timer                                                                                                                                        |

|      |      | 90          | Figure10.2 WDTS Register modified                                                                                                                     |

|      |      |             | 10.1 Count Source Protective Mode description modified                                                                                                |

|      |      |             | Timer                                                                                                                                                 |

|      |      | 129         | Figure 12.28 ICTB2 Register modified                                                                                                                  |

|      |      |             | Multi-Master I <sup>2</sup> C bus Interface                                                                                                           |

|      |      | 256         | • Figure 16.1 Block Diagram of Multi-Master I <sup>2</sup> C bus Interface modified                                                                   |

|      |      | 005         | Flash Memory Version                                                                                                                                  |

|      |      | 335         | • 20.3.1 ROM Code Protect Function register name modified                                                                                             |

|      |      | 340         | • 20.5.2 Flash Memory Control Register 1 description on FMR17 bit modified                                                                            |

|      |      | 341         | Figure 20.6 FMR1 Register note 2 modified                                                                                                             |

|      |      | 343         | Figure 20.9 Setting and Resetting of EW Mode 1 modified     Electrical Characteristics                                                                |

|      |      | 369         |                                                                                                                                                       |

|      |      | 309         | • Table 21.5 Flash Memory Version Electrical Characteristics note 10 modi-                                                                            |

|      |      | 370         | fied                                                                                                                                                  |

|      |      | 370         | <ul> <li>Timing figure for td(P-R) and td(ROC) modified</li> <li>Table 21.9 Electrical Characteristics parameter and measurement condition</li> </ul> |

|      |      | 572         | modified, note 5 deleted                                                                                                                              |

|      |      | 380         | • Table 21.25 Electrical Characteristics measurement condition modified, note                                                                         |

|      |      | 500         | 5 deleted                                                                                                                                             |

|      |      | 390         | • Tables 21.43 and 44 Flash Memory Version Electrical Characteristics note                                                                            |

|      |      | 000         | 10 modified                                                                                                                                           |

|      |      | 391         | Timing figure for td(P-R) and td(ROC) modified                                                                                                        |

|      |      | 393         | • Table 21.47 Electrical Characteristics parameter and condition modified, note                                                                       |

|      |      | 293         | - Table 21.47 Electrical characteristics parameter and condition modified, note                                                                       |