# E. Renesas Electronics America Inc - M30291FATHP#U3AAU3 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                   |

| Core Size                  | -                                                                                   |

| Speed                      | -                                                                                   |

| Connectivity               | -                                                                                   |

| Peripherals                | -                                                                                   |

| Number of I/O              | -                                                                                   |

| Program Memory Size        | -                                                                                   |

| Program Memory Type        | -                                                                                   |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | -                                                                                   |

| Voltage - Supply (Vcc/Vdd) | -                                                                                   |

| Data Converters            | -                                                                                   |

| Oscillator Type            | -                                                                                   |

| Operating Temperature      | -                                                                                   |

| Mounting Type              | -                                                                                   |

| Package / Case             | -                                                                                   |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fathp-u3aau3 |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

| (1) | Register Names, Bit Names, and Pin Names<br>Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word<br>"register," "bit," or "pin" to distinguish the three categories.<br>Examples the PM03 bit in the PM0 register<br>P3_5 pin, VCC pin                                                                                      |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (2) | Notation of Numbers<br>The indication "2" is appended to numeric values given in binary format. However, nothing is appended to the<br>values of single bits. The indication "16" is appended to numeric values given in hexadecimal format. Nothing<br>is appended to numeric values given in decimal format.<br>Examples Binary: 112<br>Hexadecimal: EFA016<br>Decimal: 1234 |  |

#### Table 4.3 SFR Information (3)

| Table            | 4.3 SFR Information (3)             |        |              |

|------------------|-------------------------------------|--------|--------------|

| Address          | Register                            | Symbol | After reset  |

| 008016           | CAN0 message box 2: Identifier/DLC  |        | XX16         |

| 008116           |                                     |        | XX16         |

| 008216           |                                     |        | XX16         |

| 008316           |                                     |        | XX16         |

| 008416           |                                     |        | XX16         |

| 008516           |                                     |        | XX16         |

| 008616           | CAN0 message box 2 : Data field     |        | XX16         |

| 008716           |                                     |        | XX16         |

| 008816           |                                     |        | XX16         |

| 008916           |                                     |        | XX16         |

| 008A16           |                                     |        | XX16         |

| 008B16           |                                     |        | XX16         |

| 008C16           |                                     |        | XX16         |

| 008D16           |                                     |        | XX16         |

| 008E16           | CAN0 message box 2 : Time stamp     |        | XX16         |

| 008E16           | Orivo message box 2 . Time stamp    |        | XX16         |

| 009016           | CAN0 message box 3 : Identifier/DLC |        | XX16         |

| 009016           | CANO message box 3 . Identifiended  |        | XX16<br>XX16 |

|                  |                                     |        | XX16         |

| 009216           |                                     |        | XX16         |

| 009316           |                                     |        | XX16         |

| 009416           |                                     |        |              |

| 009516           | CANO massage have 2 - Data field    |        | XX16<br>XX16 |

| 009616           | CAN0 message box 3 : Data field     |        |              |

| 009716           |                                     |        | XX16         |

| 009816           |                                     |        | XX16         |

| 009916           |                                     |        | XX16         |

| 009A16           |                                     |        | XX16         |

| 009B16           |                                     |        | XX16         |

| 009C16           |                                     |        | XX16         |

| 009D16           |                                     |        | XX16         |

| 009E16           | CAN0 message box 3 : Time stamp     |        | XX16         |

| 009F16           |                                     |        | XX16         |

| 00A016           | CAN0 message box 4: Identifier/DLC  |        | XX16         |

| 00A116           |                                     |        | XX16         |

| 00A216           |                                     |        | XX16         |

| 00A316           |                                     |        | XX16         |

| 00A416           |                                     |        | XX16         |

| 00A516           |                                     |        | XX16         |

| 00A616           | CAN0 message box 4 : Data field     |        | XX16         |

| 00A716           |                                     |        | XX16         |

| 00A816           |                                     |        | XX16         |

| 00A916           |                                     |        | XX16         |

| 00AA16           |                                     |        | XX16         |

| 00AB16           |                                     |        | XX16         |

| 00AC16           |                                     |        | <b>XX</b> 16 |

| 00AD16           |                                     |        | XX16         |

| 00AE16           | CAN0 message box 4 : Time stamp     |        | XX16         |

| 00AF16           |                                     |        | XX16         |

| 00B016           | CAN0 message box 5 : Identifier/DLC |        | XX16         |

| 00B116           | -                                   |        | XX16         |

| 00B216           |                                     |        | XX16         |

| 00B316           |                                     |        | XX16         |

| 00B416           |                                     |        | XX16         |

| 00B516           |                                     |        | XX16         |

| 00B616           | CAN0 message box 5 : Data field     |        | XX16         |

| 00B716           |                                     |        | XX16         |

| 00B816           |                                     |        | XX16         |

| 00B916           |                                     |        | XX16         |

| 00B916<br>00BA16 |                                     |        | XX16         |

| 00BA16           |                                     |        | XX16         |

| 00BB16<br>00BC16 |                                     |        | XX16         |

|                  |                                     |        | XX16         |

| 00BD16           | CAN0 message box 5 : Time stamp     |        | XX16<br>XX16 |

| 00BE16           | Onno message box o . Time stamp     |        | XX16<br>XX16 |

| 00BF16           |                                     |        | 01 ^^        |

Note 1: The blank areas are reserved and cannot be used by users.

X : Undefined

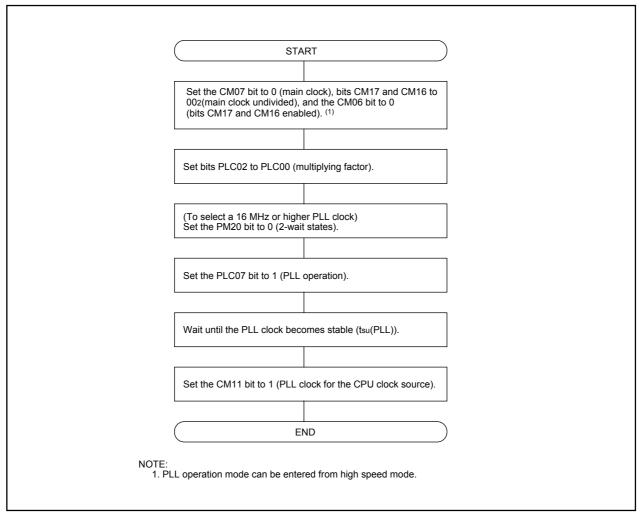

Figure 7.10 Procedure to Use PLL Clock as CPU Clock Source

|   | 0 b4 b | b3 b2 b1 b0<br>0 1 |            | nbol Address<br>DMR to TA4MR 039616 to  | After Reset<br>0 039A16 0016                                                                                                     |    |

|---|--------|--------------------|------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----|

|   |        |                    | Bit Symbol | Bit Name                                | Function                                                                                                                         | RW |

|   |        |                    | TMOD0      | Operation mode select bit               | b1 b0                                                                                                                            | RW |

|   |        |                    | TMOD1      |                                         | 0 1 : Event counter mode <sup>(1)</sup>                                                                                          | RW |

|   |        |                    | MR0        | Pulse output function select bit        | 0: Pulse is not output<br>(TAioUT pin functions as I/O port)<br>1: Pulse is output<br>(TAioUT pin functions as pulse output pin) | RW |

|   |        |                    | MR1        | Count polarityselect bit <sup>(2)</sup> | 0: Counts external signal's falling edge<br>1: Counts external signal's rising edge                                              | RW |

|   |        |                    | MR2        | Up/down switching<br>cause select bit   | 0: UDF register<br>1: Input signal to TAio∪⊤ pin <sup>(3)</sup>                                                                  | RW |

|   | L      |                    | MR3        | Set to 0 in event counter me            | ode                                                                                                                              | RW |

|   |        |                    | TCK0       | Count operation type select bit         | 0: Reload type<br>1: Free-run type                                                                                               | RW |

| l |        |                    | TCK1       | Can be 0 or 1 when not usi              | ng two-phase pulse signal processing                                                                                             | RW |

- 1. During event counter mode, the count source can be selected using registers ONSF and TRGSR.

- Effective when bits TAiTGH and TAiTGL in the ONSF or TRGSR register are 002 (TAiIN pin input).

Decrement when input on TAiOUT pin is low or increment when input on that pin is high. The port direction bit for TAiOUT pin must be set to 0 (input mode).

Figure 12.8 TAiMR Register in Event Counter Mode (when not using two-phase pulse signal processing)

#### 12.1.4 Pulse Width Modulation (PWM) Mode

In PWM mode, the timer outputs pulses of a given width in succession (see **Table 12.5**). The counter functions as either 16-bit pulse width modulator or 8-bit pulse width modulator. **Figure 12.12** shows TAiMR register in pulse width modulation mode. **Figures 12.13** and **12.14** show examples of how a 16-bit pulse width modulator operates and how an 8-bit pulse width modulator operates.

| Item                                | Specification                                                                                   |

|-------------------------------------|-------------------------------------------------------------------------------------------------|

| Count source                        | f1, f2, f8, f32, fC32                                                                           |

| Count operation                     | Decrement (operating as an 8-bit or a 16-bit pulse width modulator)                             |

|                                     | The timer reloads a new value at a rising edge of PWM pulse and continues counting              |

|                                     | <ul> <li>The timer is not affected by a trigger that occurs during counting</li> </ul>          |

| 16-bit PWM                          | High level width n / fj n : set value of TAi register (i=o to 4)                                |

|                                     | • Cycle time (2 <sup>16</sup> -1) / fj fixed fj: count source frequency (f1, f2, f8, f32, fC32) |

| 8-bit PWM                           | High level width n x (m+1) / fj n : set value of TAi register high-order address                |

|                                     | Cycle time (2 <sup>8</sup> -1) x (m+1) / fj m : set value of TAi register low-order address     |

| Count start condition               | <ul> <li>TAiS bit in the TABSR register is set to 1 (= start counting)</li> </ul>               |

|                                     | <ul> <li>The TAiS bit = 1 and external trigger input from the TAiN pin</li> </ul>               |

|                                     | <ul> <li>The TAiS bit = 1 and one of the following external triggers occurs</li> </ul>          |

|                                     | Timer B2 overflow or underflow,                                                                 |

|                                     | timer Aj (j=i-1, except j=4 if i=0) overflow or underflow,                                      |

|                                     | timer Ak (k=i+1, except k=0 if i=4) overflow or underflow                                       |

| Count stop condition                | TAiS bit is set to 0 (stop counting)                                                            |

| Interrupt request generation timing | PWM pulse goes "L"                                                                              |

| TAilN pin function                  | I/O port or trigger input                                                                       |

| TAiout pin function                 | Pulse output                                                                                    |

| Read from timer                     | An undefined value is read by reading TAi register                                              |

| Write to timer                      | When not counting and until the 1st count source is input after counting start                  |

|                                     | Value written to TAi register is written to both reload register and counter                    |

|                                     | <ul> <li>When counting (after 1st count source input)</li> </ul>                                |

|                                     | Value written to TAi register is written to only reload register                                |

|                                     | (Transferred to counter when reloaded next)                                                     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Symbol<br>TB2SC | Address<br>039E16                                        | After Reset<br>X00000002                                                                                                                                                                            |    |

|-------------------------------------------------------|-----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                       | Bit Symbol      | Bit Name                                                 | Function                                                                                                                                                                                            | RW |

|                                                       | PWCON           | Timer B2 reload timing switch bit (2)                    | 0: Timer B2 underflow<br>1: Timer A output at odd-numbered                                                                                                                                          | RW |

|                                                       | IVPCR1          | Three-phase output port<br>SD control bit 1<br>(3, 4, 7) | <ul> <li>0: Three-phase output forcible cutoff by SD pin input<br/>(high impedance) disabled</li> <li>1: Three-phase output forcible cutoff by SD pin input<br/>(high impedance) enabled</li> </ul> | RW |

|                                                       | TB0EN           | Timer B0 operation mode select bit                       | 0: Other than A/D trigger mode<br>1: A/D trigger mode (5)                                                                                                                                           | RW |

| · · · · · · · · · · · · · · · · · · ·                 | TB1EN           | Timer B1 operation mode select bit                       | 0: Other than A/D trigger mode<br>1: A/D trigger mode (5)                                                                                                                                           | RW |

|                                                       | TB2SEL          | Trigger select bit (6)                                   | 0: TB2 interrupt<br>1: Underflow of TB2 interrupt<br>generation frequency setting counter [ICTB2]                                                                                                   | RW |

| · · · · · · · · · · · · · · · · · · ·                 | (b6-b5)         | Reserved bits                                            | Set to 0                                                                                                                                                                                            | RW |

| L                                                     | (b7)            | Nothing is assigned. If ne<br>When read, the content is  |                                                                                                                                                                                                     | —  |

1. Write to this register after setting the PRC1 bit in the PRCR register to 1 (write enabled).

2. If the INV11 bit is 0 (three-phase mode 0) or the INV06 bit is 1 (triangular wave modulation mode), set this bit to 0 (timer B2 underflow).

3. When setting the IVPCR1 bit to 1 (three-phase output forcible cutoff by SD pin input enabled), Set the PD85 bit to 0 (= input mode).

4. Related pins are U(P8<sub>0</sub>), U(P8<sub>1</sub>), V(P7<sub>2</sub>), V(P7<sub>3</sub>), W(P7<sub>4</sub>), W(P7<sub>5</sub>). When a high-level ("H") signal is applied to the SD pin and set the IVPCR1 bit to 0 after forcible cutoff, pins U, U, V, V, w, and W are exit from the high-impedance state. If a lowlevel ("L") signal is applied to the  $\overline{SD}$  pin, three-phase motor control timer output will be disabled (INV03=0). At this time, when the IVPCR1 bit is 0, pins U, U, V, W, and W become programmable I/O ports. When the IVPCR1 bit is set to 1, pins U, U, V, V, W, and W are placed in a high-impedance state regardless of which function of those pins is used.

5. When this bit is used in delayed trigger mode 0, set bits TB0EN and TB1EN to 1 (A/D trigger mode).

6. When setting the TB2SEL bit to 1 (underflow of TB2 interrupt generation frequency setting counter[ICTB2]), set the INV02 bit to 1 (three-phase motor control timer function).

7. Refer to "19.6 Digital Debounce Function" for the SD input.

The effect of SD pin input is below.

| 1.Case of INV03 = 1(Three-phase motor control timer output enabled) |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| SD pin inputs <sup>(3)</sup> | Status of U/V/W pins             | Remarks                                                                                                        |

|------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|

| Н                            | Three-phase PWM output           |                                                                                                                |

| L <sup>(1)</sup>             | High impedance <sup>(4)</sup>    | Three-phase output<br>forcrible cutoff                                                                         |

| Н                            | Three-phase PWM output           |                                                                                                                |

| L <sup>(1)</sup>             | Input/output port <sup>(2)</sup> |                                                                                                                |

|                              | H<br>L <sup>(1)</sup>            | H     Three-phase PWM output       L <sup>(1)</sup> High impedance <sup>(4)</sup> H     Three-phase PWM output |

NOTES:

1. When "L" is applied to the SD pin, INV03 bit is changed to 0 at the same time.

2. The value of the port register and the port direction register becomes effective.

3. When SD function is not used, set to 0 (Input) in PD85 and pullup to "H" in SD pin from outside.

4. To leave the high-impedance state and restart the three-phase PWM signal output after the three-phase PWM signal output forced cutoff, set the IVPCR1 bit to 0 after the SD pin input level becomes high ("H").

2 Case of INV03 = 0 (Three-phase motor control timer output disabled)

| 2.0436 01 111005 - 0(1116 |                                   |                                                 |                                                       |

|---------------------------|-----------------------------------|-------------------------------------------------|-------------------------------------------------------|

| IVPCR1 bit                | $\overline{\text{SD}}$ pin inputs | Status of U/V/W pins                            | Remarks                                               |

| 1<br>(Three-phase output  | Н                                 | Peripheral input/output<br>or input/output port |                                                       |

| forcrible cutoff enable)  | L                                 | High impedance                                  | Three-phase output<br>forcrible cutoff <sup>(1)</sup> |

| 0<br>(Three-phase output  | Н                                 | Peripheral input/output<br>or input/output port |                                                       |

| forcrible cutoff disable) | L                                 | Peripheral input/output<br>or input/output port |                                                       |

NOTE:

1. The three-phase output forcrible cutoff function becomes effective if the INPCR1 bit is set to 1 (three-phase output forcrible cutoff function enable) even when the INV03 bit is 0 (three-phase motor control timer output disalbe)

#### Figure 12.30 TB2SC Register

#### Time Measurement Control Register j (j=0 to 7) b6 b5 b4 b3 b2 b1 b0 b7 Symbol Address After Reset G1TMCR0 to G1TMCR3 031816, 031916, 031A16, 031B16 0016 G1TMCR4 to G1TMCR7 031C16, 031D16, 031E16, 031F16 0016 Bit RW Bit Name Function Symbol b1 b0 CTS0 RW 0 0: No time measurement Time measurement 0 1: Rising edge trigger select bit 1 0: Falling edge CTS1 RW 1 1: Both edges b3 b2 DF0 RW 0 0: No digital filter Digital filter function 0 1: Do not set to this value select bit 1 0: fbt1 DF1 RW 1 1: f1 or f2<sup>(1)</sup> Gate function 0: Gate function is not used GT RW select bit (2) 1: Gate function is used 0: Not cleared Gate function clear GOC 1: The gate is cleared when the base RW select bit (2, 3, 4) timer matches the G1POk register The gate is cleared by setting the Gate function clear GSC RW bit (2, 3) GSC bit to 1 Prescaler function 0: Not used ...... PR RW select bit (2) 1: Used NOTES: 1. When the PCLK0 bit in the PCLKR register is set to 0, the count source is f2 cycles. And when the PCLK0 bit is set to 1, the count source is f1 cycles. 2. These bits are in registers G1TMCR6 and G1TMCR7. Set all bits 4 to 7 in registers G1TMCR0 to G1TMCR5 to 0. 3. These bits are enabled when the GT bit is set to 1. 4. The GOC bit is set to 0 after the gate function is cleared. See Figure 13.7 for details on the G1POk register (k=4 when j=6 and k=5 when j=7). Time Measurement Prescale Register j (j=6,7)<sup>(1)</sup> Symbol Address After Reset G1TPR6 to G1TPR7 032416, 032516 0016 Function Setting Range RW As the setting value is n, time is measured when-RW 0016 to FF16 ever a trigger input is counted by n+1 <sup>(2)</sup> NOTES: 1. The G1TPR6 to G1TPR7 registers reflect the base timer value, synchronizing with the count source fBT1 cycles. 2. The first prescaler, after the PR bit in the G1TMCRj register is changed from 0 (not used) to 1 (used), may be divided by n, rather than n+1. The subsequent prescaler is divided by n+1.

Figure 13.5 G1TMCR0 to G1TMCR7 Registers, and G1TPR6 to G1TPR7 Registers

RENESAS

|                                                           | lecting the rising edge as a timer measurement trigger<br>S1 and CTS0 in the G1TMCRj register (j=0 to 7)=012)                                                                                |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fBT1                                                      |                                                                                                                                                                                              |

| Base timer                                                | <u></u>                                                                                                                                                                                      |

| INPC1j pin ir<br>trigger signa<br>passing the o<br>filter | lafter                                                                                                                                                                                       |

| G1IRj bit <sup>(1)</sup>                                  | Delayed by 1 clock write 0 by program if setting to 0                                                                                                                                        |

| G1TMj regis                                               |                                                                                                                                                                                              |

|                                                           | IS :<br>Bits in the G1IR register.<br>nput pulse applied to the INPC1j pin requires 1.5 fBT1 clock cycles or more.                                                                           |

|                                                           | ecting both edges as a timer measurement trigger<br>S1 and CTS0 = 112)                                                                                                                       |

| fBT1                                                      |                                                                                                                                                                                              |

| Base timer                                                | <u> </u>                                                                                                                                                                                     |

| INPC1j pin in<br>trigger signa<br>passing the<br>filter   |                                                                                                                                                                                              |

| G1IRj bit <sup>(1)</sup>                                  | write 0 by progra<br>if setting to 0                                                                                                                                                         |

| G1TMj register (2)                                        | n x n+2 x n+5 x n+8 x n+12                                                                                                                                                                   |

| 2. N                                                      | IS :<br>Bits in the G1IR register.<br>No interrupt is generated if the MCU receives a trigger signal when the G1IRj bit is set to 1.<br>However, the value of the G1TMj register is updated. |

| (c) Trigger si<br>(Bits DF1                               | gnal when using digital filter<br>I to DF0 in the G1TMCRj register =102 or 112)                                                                                                              |

| f1 or f2 or fBT1 <sup>(1)</sup>                           |                                                                                                                                                                                              |

| INPC1j pin                                                | Maximum 3.5 f1 or f2 or fBT1                                                                                                                                                                 |

| Trigger signa<br>passing the<br>filter                    | al after Signals, which do not match 3<br>digital times, are stripped off The trigger signal is delayed                                                                                      |

|                                                           | by the digital filter                                                                                                                                                                        |

| NOTE<br>1. f                                              | :<br>BT1 when bits DF1 to DF0 are set to 10₂, and f1 or f2 when set to 11₂.                                                                                                                  |

| Register            | Bit                              | Func                                                                                                                                                                                                                                                                                                                         | ction                                                                                                                                                                                                                                                                                |

|---------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                                  | Master                                                                                                                                                                                                                                                                                                                       | Slave                                                                                                                                                                                                                                                                                |

| U2TB                | 0 to 7                           | Set transmission data                                                                                                                                                                                                                                                                                                        | Set transmission data                                                                                                                                                                                                                                                                |

| U2RB <sup>(1)</sup> | 0 to 7                           | Reception data can be read                                                                                                                                                                                                                                                                                                   | Reception data can be read                                                                                                                                                                                                                                                           |

|                     | 8                                | ACK or NACK is set in this bit                                                                                                                                                                                                                                                                                               | ACK or NACK is set in this bit                                                                                                                                                                                                                                                       |

|                     | ABT                              | Arbitration lost detection flag                                                                                                                                                                                                                                                                                              | Invalid                                                                                                                                                                                                                                                                              |

|                     | OER                              | Overrun error flag                                                                                                                                                                                                                                                                                                           | Overrun error flag                                                                                                                                                                                                                                                                   |

| U2BRG               | 0 to 7                           | Set bit rate                                                                                                                                                                                                                                                                                                                 | Invalid                                                                                                                                                                                                                                                                              |

| U2MR <sup>(1)</sup> | SMD2 to SMD0                     | Set to 0102                                                                                                                                                                                                                                                                                                                  | Set to 0102                                                                                                                                                                                                                                                                          |

|                     | CKDIR                            | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |

|                     | IOPOL                            | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |

| U2C0                | CLK1, CLK0                       | Select the count source for the U2BRG register                                                                                                                                                                                                                                                                               | Invalid                                                                                                                                                                                                                                                                              |

|                     | CRS                              | Invalid because CRD = 1                                                                                                                                                                                                                                                                                                      | Invalid because CRD = 1                                                                                                                                                                                                                                                              |

|                     | TXEPT                            | Transmit buffer empty flag                                                                                                                                                                                                                                                                                                   | Transmit buffer empty flag                                                                                                                                                                                                                                                           |

|                     | CRD                              | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |

|                     | NCH                              | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |

|                     | CKPOL                            | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |

|                     | UFORM                            | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |

| U2C1                | TE                               | Set this bit to 1 to enable transmission                                                                                                                                                                                                                                                                                     | Set this bit to 1 to enable transmission                                                                                                                                                                                                                                             |

|                     | ТІ                               | Transmit buffer empty flag                                                                                                                                                                                                                                                                                                   | Transmit buffer empty flag                                                                                                                                                                                                                                                           |

|                     | RE                               | Set this bit to 1 to enable reception                                                                                                                                                                                                                                                                                        | Set this bit to 1 to enable reception                                                                                                                                                                                                                                                |

|                     | RI                               | Reception complete flag                                                                                                                                                                                                                                                                                                      | Reception complete flag                                                                                                                                                                                                                                                              |

|                     | U2IRS                            | Invalid                                                                                                                                                                                                                                                                                                                      | Invalid                                                                                                                                                                                                                                                                              |

|                     | U2RRM,<br>U2LCH, U2ERE           | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |

| U2SMR               | IICM                             | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |

|                     | ABC                              | Select the timing at which arbitration-lost is detected                                                                                                                                                                                                                                                                      | Invalid                                                                                                                                                                                                                                                                              |

|                     | BBS                              | Bus busy flag                                                                                                                                                                                                                                                                                                                | Bus busy flag                                                                                                                                                                                                                                                                        |

|                     | 3 to 7                           | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |

| U2SMR2              | IICM2                            | Refer to Table 14.13                                                                                                                                                                                                                                                                                                         | Refer to Table 14.13                                                                                                                                                                                                                                                                 |

|                     | CSC                              | Set this bit to 1 to enable clock                                                                                                                                                                                                                                                                                            | Set to 0                                                                                                                                                                                                                                                                             |

|                     |                                  | synchronization                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                      |

|                     | SWC                              | synchronization<br>Set this bit to 1 to have SCL2 output                                                                                                                                                                                                                                                                     | Set this bit to 1 to have SCL2 output                                                                                                                                                                                                                                                |

|                     | SWC                              | 5                                                                                                                                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                |

|                     | SWC                              | Set this bit to 1 to have SCL2 output                                                                                                                                                                                                                                                                                        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                |

|                     | SWC<br>ALS                       | Set this bit to 1 to have SCL2 output fixed to L at the falling edge of the 9th                                                                                                                                                                                                                                              | fixed to "L" at the falling edge of the 9 <sup>th</sup>                                                                                                                                                                                                                              |

|                     |                                  | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output                                                                                                                                                                                  | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock                                                                                                                                                                                                              |

|                     | ALS                              | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output                                                                                | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output                                                                                |

|                     | ALS<br>STAC<br>SWC2              | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low                                                         | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low                                                         |

|                     | ALS                              | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             |

| U2SMR3              | ALS<br>STAC<br>SWC2<br>SDHI<br>7 | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output<br>Set to 0 | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output<br>Set to 0 |

| U2SMR3              | ALS<br>STAC<br>SWC2<br>SDHI      | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             |

### Table 14.11 Registers to Be Used and Settings in I<sup>2</sup>C bus mode (1) (Continued)

NOTE:

1. Not all bits in the register are described above. Set those bits to 0 when writing to the registers in I<sup>2</sup>C bus mode.

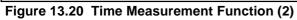

Figure 15.11 ADCON0 to ADCON2 Registers in Single Sweep Mode

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbol S2D0 |                                                     | After Reset 000110102                                                                |    |

|-------------------------|-------------|-----------------------------------------------------|--------------------------------------------------------------------------------------|----|

|                         | Bit Symbol  | Bit Name                                            | Function                                                                             | RV |

|                         | - SSC0      |                                                     |                                                                                      | RV |

|                         | - SSC1      | START/STOP condition<br>setting bits <sup>(1)</sup> | Setting for detection condition<br>of START/STOP condition.<br>See <b>Table 16.2</b> | RV |

|                         | SSC2        |                                                     |                                                                                      | RV |

|                         | - SSC3      |                                                     |                                                                                      | RV |

|                         | SSC4        |                                                     |                                                                                      | RV |

|                         | SIP         | ScL/SDA interrupt pin<br>polarity select bit        | 0: Active in falling edge<br>1: Active in rising edge                                | RV |

| sis                     |             | ScL/SDA interrupt pin select bit                    | 0: SDA enabled<br>1: ScL enabled                                                     | RV |

|                         | STSPSEL     | START/STOP condition generation select bit          | 0: Short setup/hold time mode<br>1: Long setup/hold time mode                        | RV |

#### Figure 16.8 S2D0 Register

#### Table 16.2 Recommended setting (SSC4-SSC0) start/stop condition at each oscillation frequency

|             |                             |                             | ,                        |              |              |             |

|-------------|-----------------------------|-----------------------------|--------------------------|--------------|--------------|-------------|

| Oscillation | I <sup>2</sup> C bus system | I <sup>2</sup> C bus system | SSC4-SSC0 <sup>(1)</sup> | SCL release  | Setup time   | Hold time   |

| f1 (MHz)    | clock select                | clock(MHz)                  |                          | time (cycle) | (cycle)      | (cycle)     |

| 10          | 1 / 2 <sub>f1</sub> (2)     | 5                           | XXX11110                 | 6.2 μs (31)  | 3.2 μs (16)  | 3.0 µs (15) |

| 8           | 1 / 2f1 <sup>(2)</sup>      | 4                           | XXX11010                 | 6.75 μs(27)  | 3.5 µs (14)  | 3.25 μs(13) |

|             |                             |                             | XXX11000                 | 6.25 μs(25)  | 3.25 µs (13) | 3.0 μs (12) |

| 8           | 1 / 8f1 <sup>(2)</sup>      | 1                           | XXX00100                 | 5.0 μs (5)   | 3.0 µs (3)   | 2.0 μs (2)  |

| 4           | 1 / 2f1 <sup>(2)</sup>      | 2                           | XXX01100                 | 6.5 μs (13)  | 3.5 μs (7)   | 3.0 µs (6)  |

|             |                             |                             | XXX01010                 | 5.5 μs (11)  | 3.0 µs (6)   | 2.5 μs (5)  |

| 2           | 1 / 2f1 <sup>(2)</sup>      | 1                           | XXX00100                 | 5.0 μs (5)   | 3.0 µs (3)   | 2.0 µs (2)  |

NOTES:

1. Do not set odd values or 000002 to START/STOP condition setting bits (SSC4 to SSC0)

2. When the PCLK0 bit in the PCLKR register is set to 1.

### 16.4.5 Bit 7: I<sup>2</sup>C bus Interface Pin Input Level Select Bit (TISS)

The TISS bit selects the input level of the SCL and SDA pins for the multi-master  $I^2C$  bus interface. When the TISS bit is set to 1, the P20 and P21 become the SMBus input level.

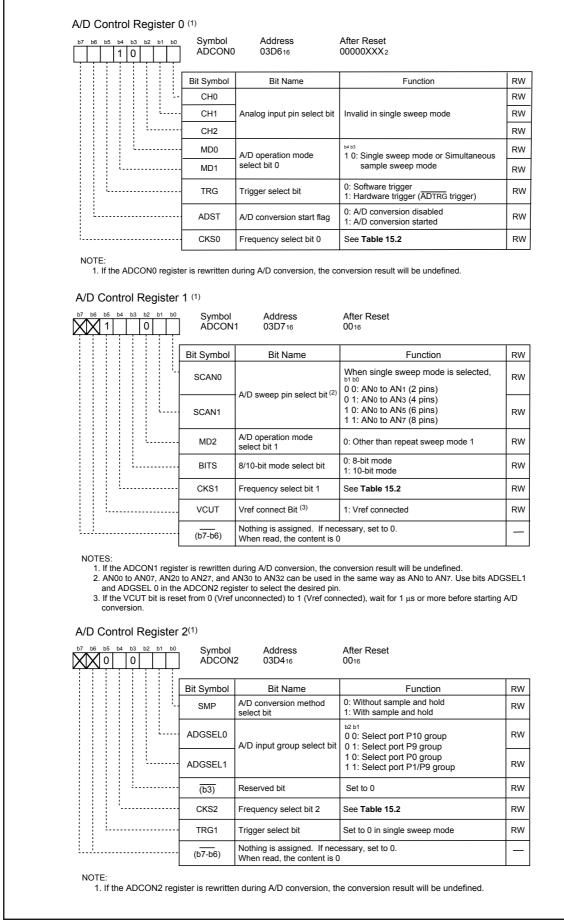

Figure 16.10 The timing of reset to the I<sup>2</sup>C bus interface circuit

| b7         b6         b5         b4         b3         b2         b1         b0           1         1         1         1         1         1         1         1 | Symbol<br>ROMCP | Address<br>0FFFFF16                              | Factory Setting<br>FF16 <sup>(4)</sup> |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------|----------------------------------------|----|

|                                                                                                                                                                   | Bit Symbol      | Bit Name                                         | Function                               | RW |

|                                                                                                                                                                   | (b5-b0)         | Reserved Bit                                     | Set to 1                               | RW |

|                                                                                                                                                                   | ROMCP1          | ROM Code Protect Level<br>1 Set Bit (1, 2, 3, 4) | 00:<br>01:<br>01:<br>Enables protect   | RW |

|                                                                                                                                                                   |                 |                                                  | 10: <b>J</b> Linables protect          | RW |

- 1. When the ROM code protect is active by the ROMCP1 bit setting, the flash memory is protected against reading or rewriting in parallel I/O mode.

- 2. Set the bit 5 to bit 0 to 1111112 when the ROMCP1 bit is set to a value other than 112. When the bit 5 to bit 0 are set to values other than 1111112, the ROM code protection may not become active by setting the ROMCP1 bit to a value other than 112.

- 3. To make the ROM code protection inactive, erase a block including the ROMCP address in standard serial I/O mode or CPU rewrite mode.

- 4. The ROMCP address is set to FF16 when a block, including the ROMCP address, is erased.

- 5. When a value of the ROMCP address is 0016 or FF16, the ROM code protect function is disabled.

#### Figure 20.4 ROMCP Address

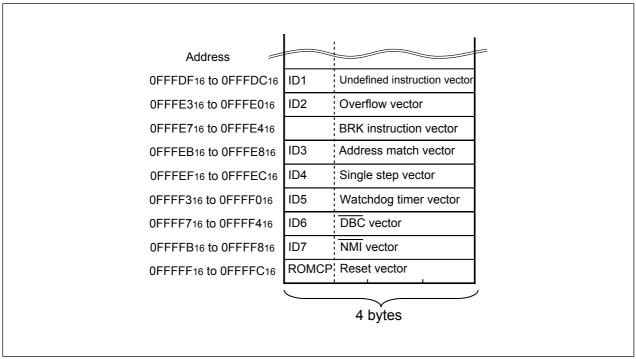

Figure 20.5 Address for ID Code Stored

#### 20.8.4 Full Status Check

If an error occurs, bits FMR06 to FMR07 in the FMR0 register are set to 1, indicating a specific error. Therefore, execution results can be comfirmed by verifying these status bits (full status check). **Table 20.7** lists errors and FMR0 register state. **Figure 20.14** shows a flow chart of the full status check and handling procedure for each error.

| FMR0    | register |                |                                                                    |

|---------|----------|----------------|--------------------------------------------------------------------|

| (SRD re | egister) |                |                                                                    |

| status  |          | Error          | Error occurrence condition                                         |

| FMR07   | FMR06    |                |                                                                    |

| (SR5)   | (SR4)    |                |                                                                    |

| 1       | 1        | Command        | An incorrect commands is written                                   |

|         |          | sequence error | • A value other than xxD016 or xxFF16 is written in the second bus |

|         |          |                | cycle of the block erase command <sup>(1)</sup>                    |

|         |          |                | When the block erase command is executed on an protected block     |

|         |          |                | When the program command is executed on protected blocks           |

| 1       | 0        | Erase error    | The block erase command is executed on an unprotected block        |

|         |          |                | but the program operation is not successfully completed            |

| 0       | 1        | Program error  | The program command is executed on an unprotected block but        |

|         |          |                | the program operation is not successfully completed                |

|         |          |                |                                                                    |

Note 1: The flash memory enters read array mode by writing command code xxFF16 in the second bus cycle of these commands. The command code written in the first bus cycle becomes invalid.

#### Pin Name Descriptio I/O Apply the voltage guaranteed for Program and Erase to Vcc pin and 0 Vcc,Vss Power input V to Vss pin. **CNVss CNVs** T Connect to Vcc pin. RESET Reset input I Reset input pin. While RESET pin is "L", wait for td(ROC). Connect a ceramic resonator or crystal oscillator between XIN and XIN Clock input 1 XOUT pins. To input an externally generated clock, input it to XIN pin XOUT Clock output 0 and open XOUT pin. AVcc, AVss Connect AVss to Vss and AVcc to Vcc, respectively. Analog power supply input VREF Reference voltage input Т Enter the reference voltage for AD conversion. P00 to P07 Input port P0 I Input "H" or "L" signal or leave open. P10 to P15, P17 Input port P1 Т Input "H" or "L" signal or leave open. P16 Input port P1 T Connect this pin to Vcc while RESET pin is "L". (2) P20 to P27 Input port P2 I Input "H" or "L" level signal or leave open. Input "H" or "L" level signal or leave open. P30 to P37 Input port P3 Т P60 to P63 Input "H" or "L" level signal or leave open. Input port P6 T Standard serial I/O mode 1: BUSY signal output pin P64 **BUSY** output 0 Standard serial I/O mode 2: Monitor signal output pin for boot program operation check Standard serial I/O mode 1: Serial clock input pin T P65 SCLK input Standard serial I/O mode 2: Input "L" P66 RxD input T Serial data input pin Serial data output pin (1) P67 $\cap$ TxD output P70 to P77 Input "H" or "L" signal or leave open. Input port P7 1 P80 to P84, Input port P8 Т Input "H" or "L" signal or leave open. P87 Connect this pin to Vss while RESET pin is "L". (2) P85 **RP** input T P86 CE input T Connect this pin to Vcc while RESET pin is "L". (2)

#### Table 20.8 Pin Descriptions (Flash Memory Standard Serial I/O Mode)

NOTES:

P100 to P107

P90 to P92,

P95 to P97 P93

> 1. When using standard serial I/O mode 1, to input "H" to the TxD pin is necessary while the RESET pin is held "L". Therefore, connect this pin to VCC via a resistor. Adjust the pull-up resistor value on a system not to affect a data transfer after reset, because this pin changes to a data-output pin

Input "H" or "L" signal or leave open.

Input "H" or "L" signal or leave open.

Input "H" or "L" signal or leave open.

"H" signal is output for specific time. Input "H" signal or leave open.

T

I/O

Т

I

2. Set the following, either or both.

Input port P9

Input port P10

-Connect the CE pin to Vcc.

-Connect the RP pin to VSS and P16 pin to Vcc.

Input port P93 Normal-ver.

T-ver./V-ver

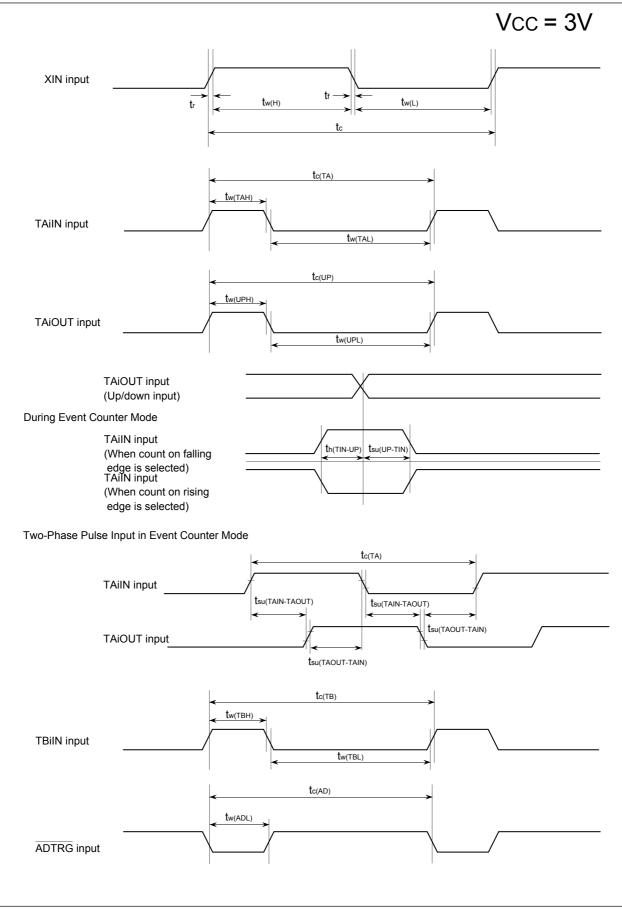

Figure 21.10 Timing Diagram (1)

### 22.5 DMAC

#### 22.5.1 Write to DMAE Bit in DMiCON Register

When both of the conditions below are met, follow the steps below.

- (a) Conditions

- The DMAE bit is set to 1 again while it remains set (DMAi is in an active state).

• A DMA request may occur simultaneously when the DMAE bit is being written.

- (b) Procedure

- (1) Write 1 to the DMAE bit and DMAS bit in DMiCON register simultaneously<sup>(1)</sup>.

- (2) Make sure that the DMAi is in an initial state<sup>(2)</sup> in a program.

If the DMAi is not in an initial state, the above steps should be repeated.

#### NOTES:

The DMAS bit remains unchanged even if 1 is written. However, if 0 is written to this bit, it is set to 0 (DMA not requested). In order to prevent the DMAS bit from being modified to 0, 1 should be written to the DMAS bit when 1 is written to the DMAE bit. In this way the state of the DMAS bit immediately before being written can be maintained.

Similarly, when writing to the DMAE bit with a read-modify-write instruction, 1 should be written to the DMAS bit in order to maintain a DMA request which is generated during execution.

2. Read the TCRi register to verify whether the DMAi is in an initial state. If the read value is equal to a value which was written to the TCRi register before DMA transfer start, the DMAi is in an initial state. (If a DMA request occurs after writing to the DMAE bit, the value written to the TCRi register is 1.) If the read value is a value in the middle of transfer, the DMAi is not in an initial state.

### 22.14 Mask ROM Version

#### 22.14.1 Internal ROM Area

In the masked ROM version, do not write to internal ROM area. Writing to the area may increase power consumption.

#### 22.14.2 Reserved Bit

The b3 to b0 in addresses 0FFFF16 are reserved bits. Set these bits to 11112.

### 22.15 Flash Memory Version

### 22.15.1 Functions to Inhibit Rewriting Flash Memory Rewrite

ID codes are stored in addresses 0FFFDF16, 0FFFE316, 0FFFEB16, 0FFFEF16, 0FFFF316, 0FFFF716, and 0FFFFB16. If wrong data are written to theses addresses, the flash memory cannot be read or written in standard serial I/O mode.

The ROMCP register is mapped in address 0FFFF16. If wrong data is written to this address, the flash memory cannot be read or written in parallel I/O mode.

In the flash memory version of MCU, these addresses are allocated to the vector addresses ("H") of fixed vectors. The b3 to b0 in address 0FFFF16 are reserved bits. Set these bits to 11112.

### 22.15.2 Stop Mode

When the MCU enters stop mode, execute the instruction which sets the CM10 bit to 1 (stop mode) after setting the FMR01 bit to 0 (CPU rewrite mode disabled) and disabling the DMA transfer.

### 22.15.3 Wait Mode

When the MCU enters wait mode, excute the WAIT instruction after setting the FMR01 bit to 0 (CPU rewrite mode disabled).

### 22.15.4 Low PowerDissipation Mode, On-Chip Oscillator Low Power Dissipation Mode

If the CM05 bit is set to 1 (main clock stop), the following commands must not be executed.

- Program

- Block erase

#### 22.15.5 Writing Command and Data

Write the command code and data at even addresses.

#### 22.15.6 Program Command

Write xx4016 in the first bus cycle and write data to the write address in the second bus cycle, and an auto program operation (data program and verify) will start. Make sure the address value specified in the first bus cycle is the same even address as the write address specified in the second bus cycle.

#### 22.15.7 Operation Speed

When CPU clock source is main clock, before entering CPU rewrite mode (EW mode 0 or 1), select 10 MHz or less for BCLK using the CM06 bit in the CM0 register and bits CM17 to CM16 in the CM1 register. Also, when CPU clock is f3(ROC) on-chip oscillator clock, before entering CPU rewrite mode (EW mode 0 or 1), set the ROCR3 to ROCR2 bits in the ROCR register to "divide by 4" or "divide by 8". On both cases, set the PM17 bit in the PM1 register to 1 (with wait state).

#### 22.15.8 Instructions Inhibited Against Use

The following instructions cannot be used in EW mode 0 because the flash memory's internal data is referenced: UND instruction, INTO instruction, JMPS instruction, JSRS instruction, and BRK instruction

### Κ

KUPIC 76

### Ν

NDDR 327

### 0

ONSF 105

#### Ρ

P0 to P3 324 P17DDR 327 P6 to P10 324 PACR 177, 326 PCLKR 52 PCR 326 PD0 to PD3 323 PD6 to PD10 323 PDRF 137 PFCR 139 PLC0 53 PM0 44 PM1 44 PM2 45, 52 PRCR 69 PUR0 to PUR2 325

## R

RMAD0

88

RMAD1

88

ROCR

50

ROMCP

336

### S

S00 258 S0D0 257 S0RIC to S2RIC 76 S0TIC to S2TIC 76 S10 260 S1D0 259 S20 258 S2D0 263 S31C 76 S3BRG 218 S3C 218 S3D0 261 S3TRR 218 S4BRG 218 S4C 218 S4D0 262 S4IC 76 S4TRR 218 SAR0 95 SAR1 95 SCLDAIC 76

### Т

TA0 to TA4 104 TA0IC to TA4IC 76 TA0MR to TA4MR 103 TA11 130 TA1MR 133 TA2 130 TA21 130 TA2MR 133 TA4 130 TA41 130 TA4MR 133 TABSR 104, 118, 132 TB0 to TB2 118 TB0IC to TB2IC 76 TB0MR to TB2MR 117 TB2 132 TB2MR 133 TB2SC 131, 227 TCR0 95 TCR1 95 **TPRC** 139 TRGSR 105, 132

### U