#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                              |

| Number of I/O              | 55                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fchp-u5a |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### 9.3.1 I Flag

The I flag enables or disables the maskable interrupt. Setting the I flag to 1 (= enabled) enables the maskable interrupt. Setting the I flag to 0 (= disabled) disables all maskable interrupts.

# 9.3.2 IR Bit

The IR bit is set to 1 (= interrupt requested) when an interrupt request is generated. Then, when the interrupt request is accepted and the CPU branches to the corresponding interrupt vector, the IR bit is cleared to 0 (= interrupt not requested).

The IR bit can be cleared to 0 in a program. Note that do not write 1 to this bit.

### 9.3.3 ILVL2 to ILVL0 Bits and IPL

Interrupt priority levels can be set using bits ILVL2 to ILVL0.

**Table 9.3** shows the settings of interrupt priority levels and **Table 9.4** shows the interrupt priority levels enabled by the IPL.

The following are conditions under which an interrupt is accepted:

- · I flag = 1

- · IR bit = 1

- · interrupt priority level > IPL

The I flag, IR bit, bits ILVL2 to ILVL0, and IPL are independent of each other. In no case do they affect one another.

| ILVL2 to ILVL0 bits | Interrupt priority<br>level  | Priority<br>order |

|---------------------|------------------------------|-------------------|

| 0002                | Level 0 (interrupt disabled) |                   |

| 0012                | Level 1                      | Low               |

| 0102                | Level 2                      |                   |

| 0112                | Level 3                      |                   |

| 1002                | Level 4                      |                   |

| 1012                | Level 5                      |                   |

| 1102                | Level 6                      | ↓                 |

| 1112                | Level 7                      | High              |

#### Table 9.3 Settings of Interrupt Priority Levels

#### Table 9.4 Interrupt Priority Levels Enabled by IPL

| IPL  | Enabled interrupt priority levels        |

|------|------------------------------------------|

| 0002 | Interrupt levels 1 and above are enabled |

| 0012 | Interrupt levels 2 and above are enabled |

| 0102 | Interrupt levels 3 and above are enabled |

| 0112 | Interrupt levels 4 and above are enabled |

| 1002 | Interrupt levels 5 and above are enabled |

| 1012 | Interrupt levels 6 and above are enabled |

| 1102 | Interrupt levels 7 and above are enabled |

| 1112 | All maskable interrupts are disabled     |

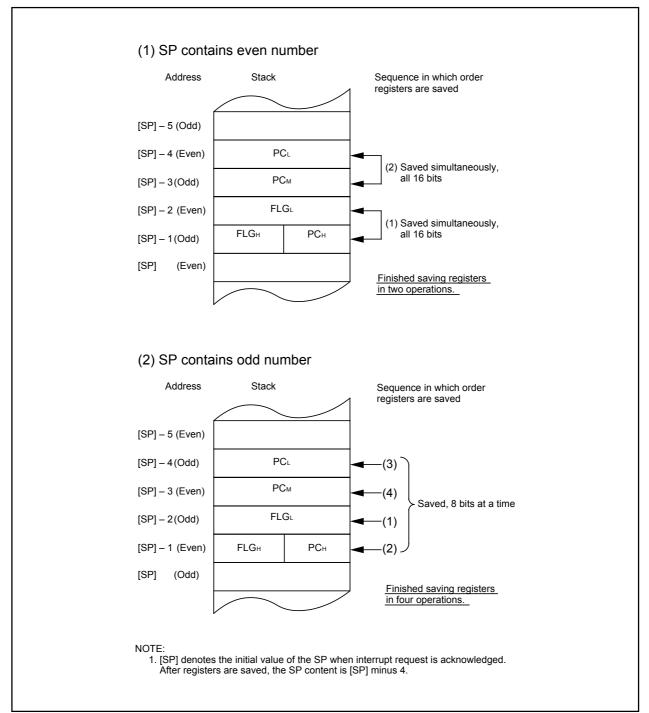

The operation of saving registers carried out in the interrupt sequence is dependent on whether the  $SP^{(1)}$ , at the time of acceptance of an interrupt request, is even or odd. If the stack pointer <sup>(1)</sup> is even, the FLG register and the PC are saved, 16 bits at a time. If odd, they are saved in two steps, 8 bits at a time. **Figure 9.8** shows the operation of the saving registers.

NOTE:

1. When any INT instruction in software numbers 32 to 63 has been executed, this is the SP indicated by the U flag. Otherwise, it is the ISP.

Figure 9.8 Operation of Saving Register

### 12.1.2 Event Counter Mode

In event counter mode, the timer counts pulses from an external device or overflows and underflows of other timers. Timers A2, A3, and A4 can count two-phase external signals. **Table 12.2** lists specifications in event counter mode (when not processing two-phase pulse signal). **Table 12.3** lists specifications in event counter mode (when processing two-phase pulse signal with the timers A2, A3 and A4). **Figure 12.8** shows TAiMR register in event counter mode (when <u>not</u> processing two-phase pulse signal with the timers A2, A3 and A4). **Figure 12.9** shows TA2MR to TA4MR registers in event counter mode (when processing two-phase pulse signal with the timers A2, A3 and A4).

| Item                                | Specification                                                                    |  |  |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Count source                        | • External signals input to TAiIN pin (i=0 to 4) (effective edge can be selected |  |  |  |  |  |  |

|                                     | in program)                                                                      |  |  |  |  |  |  |

|                                     | Timer B2 overflows or underflows,                                                |  |  |  |  |  |  |

|                                     | timer Aj (j=i-1, except j=4 if i=0) overflows or underflows,                     |  |  |  |  |  |  |

|                                     | timer Ak (k=i+1, except k=0 if i=4) overflows or underflows                      |  |  |  |  |  |  |

| Count operation                     | Increment or decrement can be selected by external signal or program             |  |  |  |  |  |  |

|                                     | • When the timer overflows or underflows, it reloads the reload register con-    |  |  |  |  |  |  |

|                                     | tents and continues counting. When operating in free-running mode, the           |  |  |  |  |  |  |

|                                     | timer continues counting without reloading.                                      |  |  |  |  |  |  |

| Divided ratio                       | 1/ (FFFF16 - n + 1) for increment                                                |  |  |  |  |  |  |

|                                     | 1/ (n + 1) for down-count n : set value of TAi register 000016 to FFF16          |  |  |  |  |  |  |

| Count start condition               | Set TAiS bit in the TABSR register to 1 (start counting)                         |  |  |  |  |  |  |

| Count stop condition                | Set TAiS bit to 0 (stop counting)                                                |  |  |  |  |  |  |

| Interrupt request generation timing | Timer overflow or underflow                                                      |  |  |  |  |  |  |

| TAilN pin function                  | I/O port or count source input                                                   |  |  |  |  |  |  |

| TAIOUT pin function                 | I/O port, pulse output, or up/down-count select input                            |  |  |  |  |  |  |

| Read from timer                     | Count value can be read by reading TAi register                                  |  |  |  |  |  |  |

| Write to timer                      | When not counting and until the 1st count source is input after counting start   |  |  |  |  |  |  |

|                                     | Value written to TAi register is written to both reload register and counter     |  |  |  |  |  |  |

|                                     | <ul> <li>When counting (after 1st count source input)</li> </ul>                 |  |  |  |  |  |  |

|                                     | Value written to TAi register is written to only reload register                 |  |  |  |  |  |  |

|                                     | (Transferred to counter when reloaded next)                                      |  |  |  |  |  |  |

| Select function                     | Free-run count function                                                          |  |  |  |  |  |  |

|                                     | Even when the timer overflows or underflows, the reload register content is      |  |  |  |  |  |  |

|                                     | not reloaded to it                                                               |  |  |  |  |  |  |

|                                     | Pulse output function                                                            |  |  |  |  |  |  |

|                                     | Whenever the timer underflows or underflows, the output polarity of TAiOUT       |  |  |  |  |  |  |

|                                     | pin is inverted . When not counting, the pin outputs a low.                      |  |  |  |  |  |  |

Table 12.2 Specifications in Event Counter Mode (when not processing two-phase pulse signal)

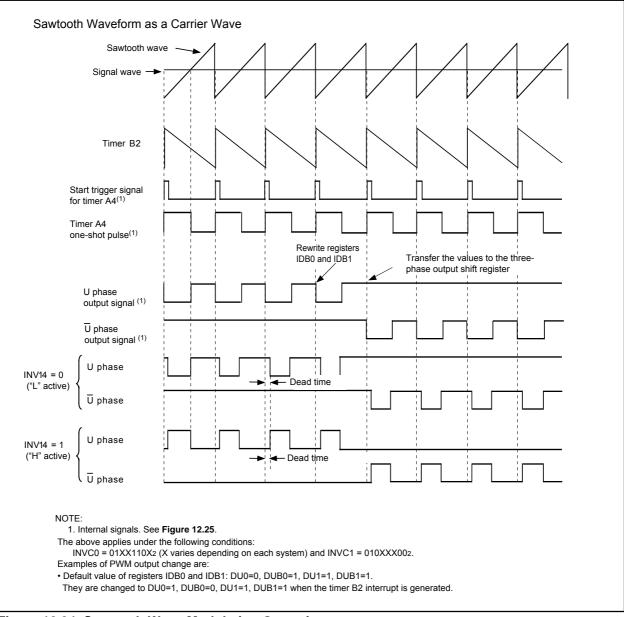

Figure 12.34 Sawtooth Wave Modulation Operation

**Table 14.3** lists pin functions for the case where the multiple transfer clock output pin select function is deselected. **Table 14.4** lists the P64 pin functions during clock synchronous serial I/O mode. Note that for a period from when the UARTi operation mode is selected to when transfer starts, the TxDi pin outputs an "H". (If the N-channel open-drain output is selected, this pin is in a high-impedance state.)

| Pin Name                             | Function              | Method of Selection                                                                                                                                                                                  |

|--------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxDi (i = 0 to 2)<br>(P63, P67, P70) |                       | (Outputs dummy data when performing reception only)                                                                                                                                                  |

| RxDi<br>(P62, P66, P71)              | Serial data input     | Set the PD6_2 bit and PD6_6 bit in the PD6 register, and PD7_1 bit in the PD7 register to 0 (Can be used as an input port when performing transmission only)                                         |

| CLKi                                 | Transfer clock output | Set the CKDIR bit in the UiMR register to 0                                                                                                                                                          |

| (P61, P65, P72)                      | Transfer clock input  | Set the CKDIR bit in the UiMR register to 1<br>Set the PD6_1 bit and PD6_5 bit in the PD6 register, and the PD7_2 bit in the<br>PD7 register to 0                                                    |

| CTSi/RTSi<br>(P60, P64, P73)         | CTS input             | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 0<br>Set the PD6_0 bit and PD6_4 bit in the PD6 register is set to 0, the PD7_3 bit<br>in the PD7 register to 0 |

|                                      | RTS output            | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 1                                                                                                               |

|                                      | I/O port              | Set the CRD bit in the UiC0 register to 1                                                                                                                                                            |

NOTE:

1: When the U1MAP bit in PACR register is 1 (P73 to P70), UART1 pin is assgined to P73 to P70.

#### Table 14.4 P64 Pin Functions<sup>(1)</sup>

|                                 |      |                             | Bit Se | et Value         |       |                     |

|---------------------------------|------|-----------------------------|--------|------------------|-------|---------------------|

| Pin Function                    | U1C0 | U1C0 register UCON register |        |                  |       | PD6 register        |

|                                 | CRD  | CRS                         | RCSP   | CLKMD1           | PD6_4 |                     |

| P64                             | 1    |                             | 0      | 0                |       | Input: 0, Output: 1 |

| CTS1                            | 0    | 0                           | 0      | 0                |       | 0                   |

| RTS <sub>1</sub>                | 0    | 1                           | 0      | 0                | —     | —                   |

| CTS <sub>0</sub> <sup>(2)</sup> | 0    | 0                           | 1      | 0                |       | 0                   |

| CLKS1                           |      | _                           |        | 1 <sup>(3)</sup> | 1     |                     |

NOTES:

1. When the U1MAP bit in PACR register is 1 (P73 to P70), this table lists the P70 functions.

2. In addition to this, set the CRD bit in the U0C0 register to 0 (CT00/RT00 enabled) and the CRS bit in the U0C0 register to 1 (RTS0 selected).

3. When the CLKMD1 bit is set to 1 and the CLKMD0 bit is set to 0, the following logic levels are output:

High if the CLKPOL bit in the U1C0 register is set to 0

. Low if the CLKPOL bit in the U1C0 register is set to 1

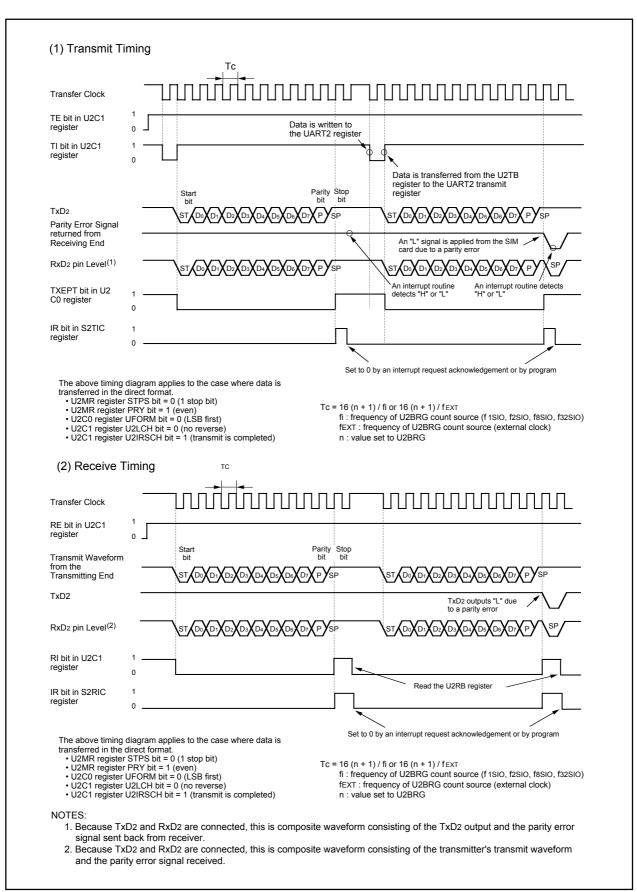

Figure 14.31 Transmit and Receive Timing in SIM Mode

RENESAS

# **15.1 Operating Modes**

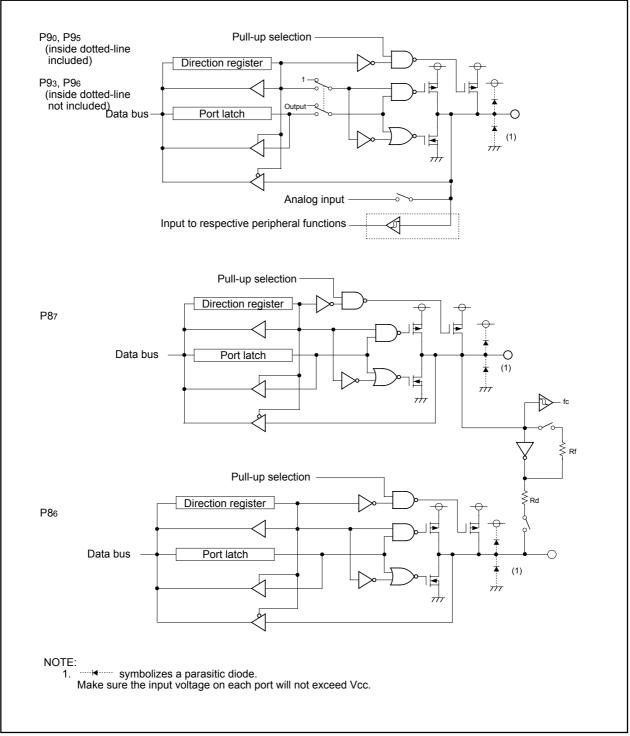

### 15.1.1 One-Shot Mode

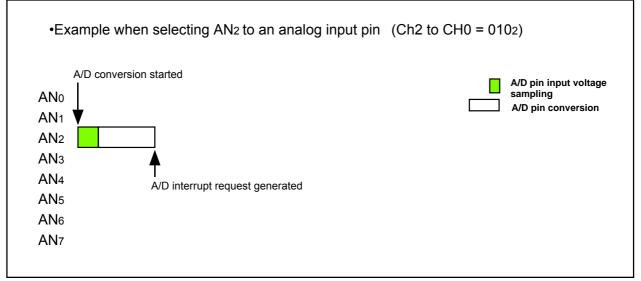

In one-shot mode, analog voltage applied to a selected pin is once converted to a digital code. **Table 15.3** shows the one-shot mode specifications. **Figure 15.6** shows the operation example in one-shot mode. **Figure 15.7** shows registers ADCON0 to ADCON2 in one-shot mode.

| Table 15.3 | One-shot | Mode | Specifications |

|------------|----------|------|----------------|

|------------|----------|------|----------------|

| Item                                | Specification                                                                |  |  |  |  |  |

|-------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| Function                            | Bits CH2 to CH0 in the ADCON0 register and registers ADGSEL1 and             |  |  |  |  |  |

|                                     | ADGSEL0 in the ADCON2 register select pins. Analog voltage applied to a      |  |  |  |  |  |

|                                     | selected pin is once converted to a digital code                             |  |  |  |  |  |

| A/D Conversion Start                | When the TRG bit in the ADCON0 register is 0 (software trigger)              |  |  |  |  |  |

| Condition                           | Set the ADST bit in the ADCON0 register to 1 (A/D conversion started)        |  |  |  |  |  |

|                                     | When the TRG bit in the ADCON0 register is 1 (hardware trigger)              |  |  |  |  |  |

|                                     | The ADTRG pin input changes state from "H" to "L" after setting the          |  |  |  |  |  |

|                                     | ADST bit to 1 (A/D conversion started)                                       |  |  |  |  |  |

| A/D Conversion Stop                 | A/D conversion completed (If a software trigger is selected, the ADST bit is |  |  |  |  |  |

| Condition                           | set to 0 (A/D conversion halted)).                                           |  |  |  |  |  |

|                                     | Set the ADST bit to 0                                                        |  |  |  |  |  |

| Interrupt Request Generation Timing | A/D conversion completed                                                     |  |  |  |  |  |

| Analog Input Pin                    | Select one pin from AN0 to AN7, AN00 to AN07, AN20 to AN27, AN30 to AN32     |  |  |  |  |  |

| Readout of A/D Conversion Result    | Readout one of registers AD0 to AD7 that corresponds to the selected pin     |  |  |  |  |  |

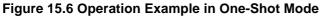

Figure 16.2 S0D0 Register

# 16.13 Address Data Communication

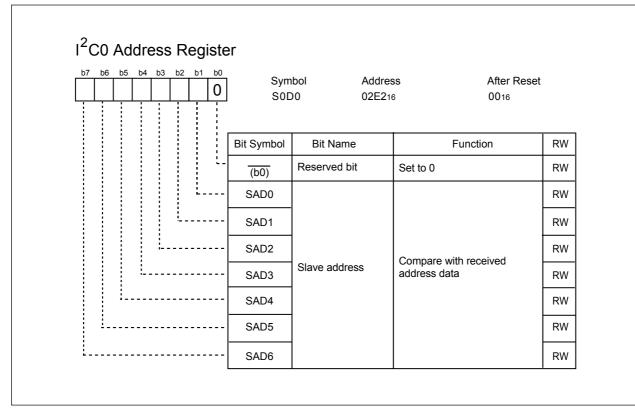

This section describes data transmit control when a master transferes data or a slave receives data in 7-bit address format. **Figure 16.20 (1)** shows a master transmit format.

Figure 16.20 Address data communication format

# 16.13.1 Example of Master Transmit

For example, a master transmits data as shown below when following conditions are met: standard clock mode, SCL clock frequency of 100kHz and ACK clock added.

- 1) Set s slave address to the 7 high-order bits in the S0D0 register

- 2) Set 8516 to the S20 register, 0002 to bits ICK4 to ICK2 in the S4D0 register and 0016 to the S3D0 registe to generate an ACK clock and set SCL clock frequency t 100 kHz (f1=8MHz, fIIC=f1)

- 3) Set 0016 to the S10 register to reset transmit/receive

- 4) Set 0816 to the S1D0 register to enable data communication

- 5) Confirm whether the bus is free by BB flag setting in the S10 register

- 6) Set E016 to the S10 register to enter START condition standby mode

- 7) Set the destination address in 7 high-order bits and 0 to a least significant bit in the S00 register to generate START condition. At this time, the first byte consisting of SCL and ACK clock are automatically generated

- 8) Set a transmit data to the S00 register. At this time, SCL and an ACK clock are automatically generated

- 9) When transmitting more than 1-byte control data, repeat the above step 8).

- 10) Set C016 in the S10 register to enter STOP condition standby mode if ACK is not returned from the slave receiver or if the transmit is completed

- 11) Write dummy data to the S00 regiser to generate STOP condition

### 17.7 Return from Bus off Function

When the protocol controller enters bus off state, it is possible to make it forced return from bus off state by setting the RetBusOff bit in the COCTLR register to 1 (Force return from bus off). At this time, the error state changes from bus off state to error active state. If the RetBusOff bit is set to 1, registers CORECR and COTECR are initialized and the State\_Reset bit in the COSTR register is set to 0 (The CAN module is not in error bus off state). However, registers of the CAN module such as COCONR register and the content of each slot are not initialized.

### **17.8 Time Stamp Counter and Time Stamp Function**

When the C0TSR register is read, the value of the time stamp counter at the moment is read. The period of the time stamp counter reference clock is the same as that of 1 bit time that is configured by the C0CONR register. The time stamp counter functions as a free run counter.

The 1 bit time period can be divided by 1 (undivided), 2, 4 or 8 to produce the time stamp counter reference clock. Use the TSPreScale bit in the COCTLR register to select the divide-by-n value.

The time stamp counter is equipped with a register that captures the counter value when the protocol controller regards it as a successful reception. The captured value is stored when a time stamp value is stored in a reception slot.

### 17.9 Listen-Only Mode

When the RXOnly bit in the COCTLR register is set to 1, the module enters listen-only mode.

In listen-only mode, no transmission -- data frames, error frames, and ACK response -- is performed to bus. When listen-only mode is selected, do not request the transmission.

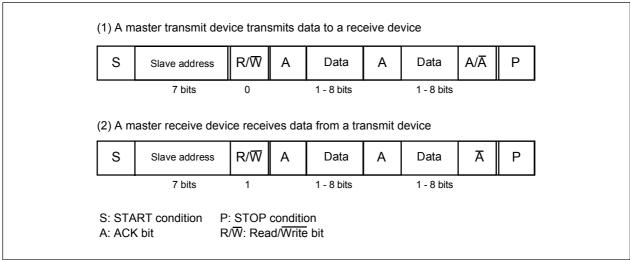

Figure 19.4 I/O Ports (4)

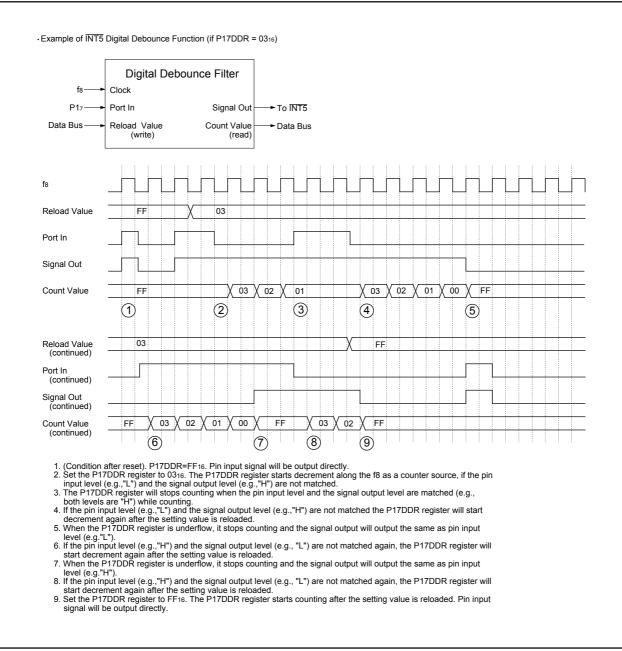

Figure 19.12 Functioning of Digital Debounce Filter

| Flash Memory Cont       | 0             | er O                                       |                                                                                                                                       |    |

|-------------------------|---------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbo<br>FMR0 |                                            | After Reset<br>000000012                                                                                                              |    |

|                         | Bit Symbol    | Bit Name                                   | Function                                                                                                                              | RW |

|                         | FMR00         | RY/BY status flag                          | 0: Busy (during writing or erasing)<br>1: Ready                                                                                       | RO |

|                         | FMR01         | CPU rewrite mode select bit <sup>(1)</sup> | 0: Disables CPU rewrite mode<br>(Disables software command)<br>1: Enables CPU rewrite mode<br>(Enables software commands)             | RW |

|                         | FMR02         | Block 0, 1 rewrite enable bit (2)          | Set write protection for user ROM area (see <b>Table 20.4</b> )                                                                       | RW |

|                         | FMSTP         | Flash memory stop bit (3, 5)               | 0: Starts flash memory operation<br>1: Stops flash memory operation<br>(Enters low-power consumption state<br>and flash memory reset) | RW |

|                         | (b5-b4)       | Reserved bit                               | Set to 0                                                                                                                              | RW |

|                         | FMR06         | Program status flag (4)                    | 0: Successfully completed<br>1: Completion error                                                                                      | RO |

| L                       | FMR07         | Erase status flag (4)                      | 0: Successfully completed<br>1: Completion error                                                                                      | RO |

NOTES:

Set the FMR01 bit to 1 immediately after setting it first to 0. Do not generate an interrupt or a DMA transfer between setting the bit to 0 and setting it to 1. Set this bit while the P85/NMI/SD pin is held "H" when selecting the NMI function. Set by program in a space other than the flash memory in EW mode 0. Set this bit to read alley mode and 0.

2. Set this bit to 1 immediately after setting it first to 0 while the FMR01 bit is set to 1. Do not generate an interrupt or a DMA transfer between setting this bit to 0 and setting it to 1.

3. Set this bit in a space other than the flash memory by program. When this bit is set to 1, access to flash memory will be denied. To set this bit to 0 after setting it to 1, wait for 10 usec. or more after setting it to 1. To read data from flash memory after setting this bit to 0, maintain tps wait time before accessing flash memory.

4. This bit is set to 0 by executing the clear status command.

5. This bit is enabled when the FMR01 bit is set to 1 (CPU rewrite mode). If the FMR01 bit is set to 0, this bit can be set to 1 by writing 1 to the FMR01 bit. However, the flash memory does not enter low-power consumption status and it is not initialized.

#### Flash Memory Control Register 1

| b7 b6 b5 b4 b3 b2 b1 b0               | Symbo<br>FMR1 |                                                                  | After Reset<br>000XXX0X2                                                                       |    |

|---------------------------------------|---------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----|

|                                       | Bit Symbol    | Bit Name                                                         | Function                                                                                       | RW |

|                                       | (b0)          | Reserved bit                                                     | When read, the content is undefined                                                            | RO |

| L                                     | FMR11         | EW mode 1 select bit <sup>(1)</sup>                              | 0: EW mode 0<br>1: EW mode 1                                                                   | RW |

|                                       | (b3-b2)       | Reserved bit                                                     | When read, the content is undefined                                                            | RO |

| · · · · · · · · · · · · · · · · · · · | (b4)          | Nothing is assigned. If necessar When read, the content is under |                                                                                                | —  |

|                                       | (b5)          | Reserved bit                                                     | Set to 0                                                                                       | RW |

| L                                     | FMR16         | Block 0 to 5 rewrite enable bit <sup>(2)</sup>                   | Set write protection for user ROM<br>space (see <b>Table 20.4</b> )<br>0: Disable<br>1: Enable | RW |

| l                                     | FMR17         | Block A, B access wait bit <sup>(3)</sup>                        | 0: PM17 enabled<br>1: With wait state (1 wait)                                                 | RW |

NOTES:

1. Set the FMR11 bit to 1 immediately after setting it first to 0 while the FMR01 bit is set to 1. Do not generate an interrupt or a DMA transfer between setting the bit to 0 and setting it to 1. Set this bit while the P85/NMI/SD pin is held "H" when the NMI function is selected. If the FMR01 bit is set to 0, the FMR01 bit and FMR11 bit are both set to 0.

2. Set this bit to 1 immediately after setting it first to 0 while the FMR01 bit is set to 1. Do not generate an interrupt or a DMA transfer between setting this bit to 0 and setting it to 1.

3. When rewriting more than 100 times, set this bit to 1 (with wait state). When the FMR17 bit is set to1(with wait state), regardless of the PM17 bit setting, 1 wait state is inserted when accessing to blocks A and B. The PM17 bit setting is enabled, regardless of the FMR17 bit setting, as to the access to other block and the internal RAM.

#### Figure 20.6 FMR0 and FMR1 Registers

#### **Timing Requirements**

# Vcc = 5V

# (VCC = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Symbol  | Parameter                           | Standard clock mode |      | High-speed clock mode |      | Unit |

|---------|-------------------------------------|---------------------|------|-----------------------|------|------|

| Symbol  | Parameter                           | Min.                | Max. | Min.                  | Max. | Unit |

| tBUF    | Bus free time                       | 4.7                 |      | 1.3                   |      | μs   |

| tHD;STA | The hold time in start condition    | 4.0                 |      | 0.6                   |      | μs   |

| tLOW    | The hold time in SCL clock 0 status | 4.7                 |      | 1.3                   |      | μs   |

| tR      | SCL, SDA signals' rising time       |                     | 1000 | 20+0.1Cb              | 300  | ns   |

| tHD;DAT | Data hold time                      | 0                   |      | 0                     | 0.9  | μs   |

| tHIGH   | The hold time in SCL clock 1 status | 4.0                 |      | 0.6                   |      | μs   |

| tF      | SCL, SDA signals' falling time      |                     | 300  | 20+0.1Cb              | 300  | ns   |

| tsu;DAT | Data setup time                     | 250                 |      | 100                   |      | ns   |

| tsu;STA | The setup time in restart condition | 4.7                 |      | 0.6                   |      | μs   |

| tsu;STO | Stop condition setup time           | 4.0                 |      | 0.6                   |      | μs   |

# Table 21.23 Multi-master I<sup>2</sup>C bus Line

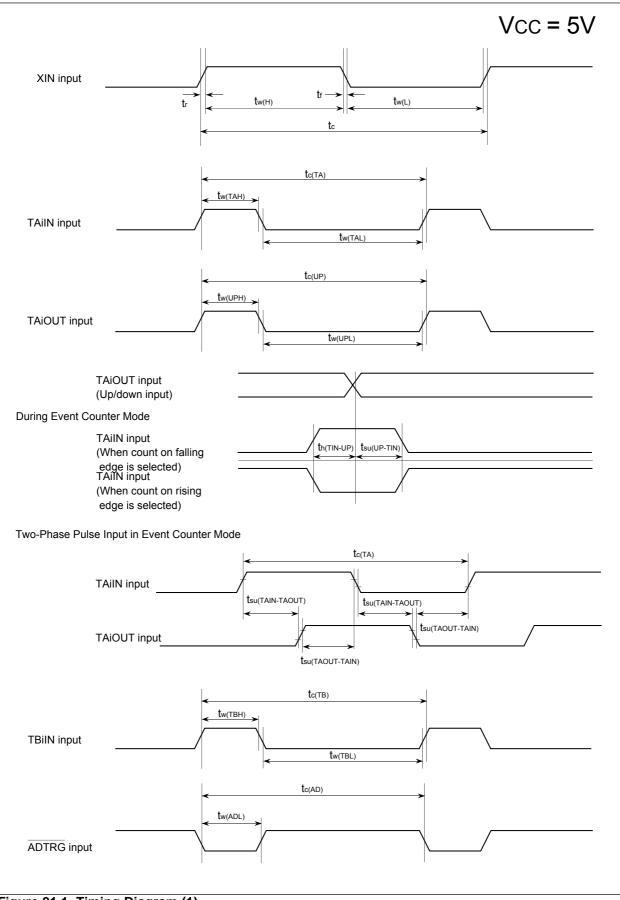

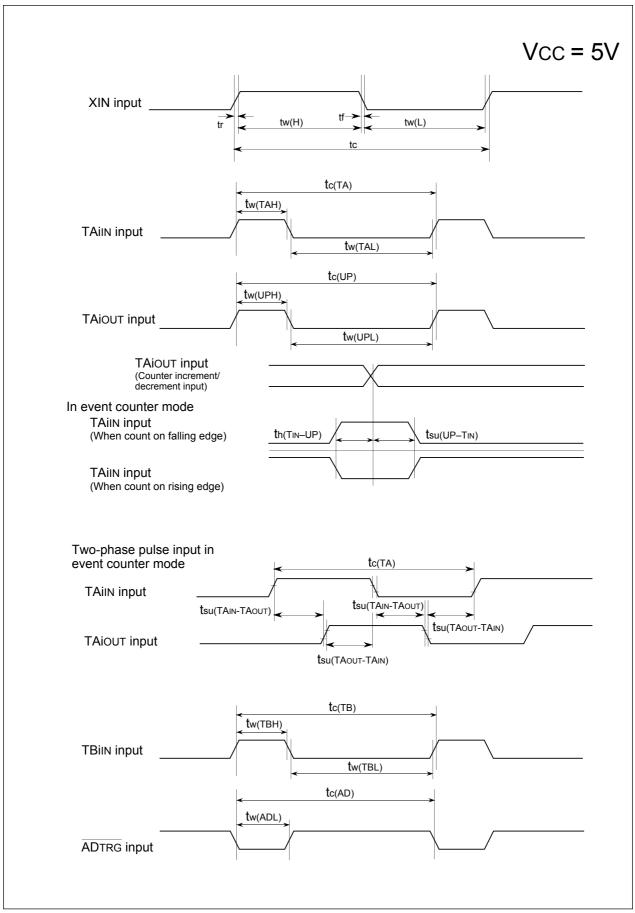

Figure 21.1 Timing Diagram (1)

#### **Timing Requirements**

Vcc = 5V

# (Vcc=5V, Vss=0V, at Topr=-40 to 125°C unless otherwise specified)

| Symbol | Deremeter                             |                       | Standard |      | Linit  |

|--------|---------------------------------------|-----------------------|----------|------|--------|

|        | Parameter                             |                       | Min.     | Max. | – Unit |

| tc     | External Clock Input Cycle Time       | Topr=-40° C to 105° C | 50       |      | ns     |

|        |                                       | Topr=-40° C to 125° C | 62.5     |      | ns     |

| tw(H)  | External Clock Input High ("H") Width | Topr=-40° C to 105° C | 20       |      | ns     |

|        |                                       | Topr=-40° C to 125° C | 25       |      | ns     |

| tw(∟)  | External Clock Input Low ("L") Width  | Topr=-40° C to 105° C | 20       |      | ns     |

|        |                                       | Topr=-40° C to 125° C | 25       |      | ns     |

| tr     | External Clock Rise Time              | Topr=-40° C to 105° C |          | 9    | ns     |

|        |                                       | Topr=-40° C to 125° C |          | 15   | ns     |

| tf     | External Clock Fall Time              | Topr=-40° C to 105° C |          | 9    | ns     |

|        |                                       | Topr=-40° C to 125° C |          | 15   | ns     |

### Table 21.86 External Clock Input (XIN input)

Figure 21.13 Timing Diagram (1)

# **REVISION HISTORY**

# M16C/29 Hardware Manual

| Rev. | Date |      | Description                                                                    |  |

|------|------|------|--------------------------------------------------------------------------------|--|

|      |      | Page | e Summary                                                                      |  |

|      |      |      | 4 deleted                                                                      |  |

|      |      | 401  | • Table 21.63 Elctrical Characteristics measurement condition modified, note 4 |  |

|      |      |      | deleted                                                                        |  |

|      |      | 411  | •Tables 21.81 and 21.82 Flash Memory Version Electrical Characteristics        |  |

|      |      |      | note 10 modified                                                               |  |

|      |      | 412  | •Timing figure for td(P-R) and td(ROC) modified                                |  |

|      |      | 414  | •Table 21.85 Electrical Characteristics measurment condition modified, note 4  |  |

|      |      |      | deleted                                                                        |  |

|      |      |      | Usage Notes                                                                    |  |

|      |      | 439  | •Figure 22.4 Use of Capacitors to Reduce Noise note 1 modified                 |  |

|      |      | 449  | •22.15.10 How to Access description modified                                   |  |

|      |      | 450  | •22.15.15 Flash Memory Version Electrical Characteristics 10,000 E/W Cycle     |  |

|      |      |      | Products description modified                                                  |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

|      |      |      |                                                                                |  |

RENESAS 16-BIT SINGLE-CHIP MICROCOMPUTER HARDWARE MANUAL M16C/29 Group

Publication Data : Rev.0.70 Mar. 29, 2004 Rev.1.12 Mar. 30, 2007

Published by : Sales Strategic Planning Div. Renesas Technology Corp.

© 2007. Renesas Technology Corp., All rights reserved. Printed in Japan.