#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                              |

| Number of I/O              | 55                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fchp-u7a |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

As of March. 2007

#### **1.3 Product List**

Tables 1.3 to 1.5 list the M16C/29 Group products and Figure 1.3 shows the type numbers, memory sizes and packages. Tables 1.6 to 1.8 list the product code of flash memory version for M16C/29 Group. Figure 1.4 to Figure 1.6 show the marking diagram of flash memory version for M16C/29 Group.

|                |                 | ai 011, 2007    |                        |             |                 |  |

|----------------|-----------------|-----------------|------------------------|-------------|-----------------|--|

| Type Number    | ROM<br>Capacity | RAM<br>Capacity | Package Type           | Remarks     | Product<br>Code |  |

| M30290FAHP     | 96 K + 4 K      | 8 K             | PLQP0080KB-A (80P6Q-A) |             |                 |  |

| M30290FCHP     | 128 K + 4 K     | 12 K            |                        | Flash       | U3, U5,         |  |

| M30291FAHP     | 96 K + 4 K      | 8 K             | PLQP0064KB-A (64P6Q-A) | Memory      | U7, U9          |  |

| M30291FCHP     | 128 K + 4 K     | 12 K            | FLQF0004KB-A (04F0Q-A) |             |                 |  |

| M30290M8-XXXHP | 64 K            | 4 K             |                        |             |                 |  |

| M30290MA-XXXHP | 96 K            | 8 K             | PLQP0080KB-A (80P6Q-A) | Mask<br>ROM |                 |  |

| M30290MC-XXXHP | 128 K           | 12 K            |                        |             |                 |  |

| M30291M8-XXXHP | 64 K            | 4 K             |                        |             | U3, U5          |  |

| M30291MA-XXXHP | 96 K            | 8 K             | PLQP0064KB-A (64P6Q-A) |             |                 |  |

| M30291MC-XXXHP | 128 K           | 12 K            |                        |             |                 |  |

#### Table 1.3 Product List (1) -Normal Version

#### Table 1.4 Product List (2) -T Version

| Table 1.4 Product List (2) | able 1.4 Product List (2) -T Version |                 |                          |         |                 |  |

|----------------------------|--------------------------------------|-----------------|--------------------------|---------|-----------------|--|

| Type Number                | ROM<br>Capacity                      | RAM<br>Capacity | Package Type             | Remarks | Product<br>Code |  |

| M30290FATHP                | 96 K + 4 K                           | 8 K             | PLQP0080KB-A (80P6Q-A)   |         |                 |  |

| M30290FCTHP                | 128 K + 4 K                          | 12 K            |                          | Flash   | U3, U5,         |  |

| M30291FATHP                | 96 K + 4 K                           | 8 K             |                          | Memory  | U7, U9          |  |

| M30291FCTHP                | 128 K + 4 K                          | 12 K            | - PLQP0064KB-A (64P6Q-A) |         |                 |  |

| M30290M8T-XXXHP            | 64 K                                 | 4 K             |                          |         |                 |  |

| M30290MAT-XXXHP            | 96 K                                 | 8 K             | PLQP0080KB-A (80P6Q-A)   |         |                 |  |

| M30290MCT-XXXHP            | 128 K                                | 12 K            |                          | Mask    | UO              |  |

| M30291M8T-XXXHP            | 64 K                                 | 4 K             |                          | ROM     | 00              |  |

| M30291MAT-XXXHP            | 96 K                                 | 8 K             | PLQP0064KB-A (64P6Q-A)   |         |                 |  |

| M30291MCT-XXXHP            | 128 K                                | 12 K            | 1                        |         |                 |  |

#### Table 4.6 SFR Information (6)

| Address            |                                      |          | Symbol | After reset |

|--------------------|--------------------------------------|----------|--------|-------------|

| 14016              | CAN0 message box 14: Identifier/DLC  |          |        | XX16        |

| 14116              |                                      |          |        | XX16        |

| )14216             |                                      |          |        | XX16        |

| 014316             |                                      |          |        | XX16        |

| 014416             |                                      |          |        | XX16        |

| 014516             |                                      |          |        | XX16        |

| 014616             | CAN0 message box 14 : Data field     |          |        | XX16        |

| 014716             |                                      |          |        | XX16        |

| 014816             |                                      |          |        | XX16        |

| 014916             |                                      |          |        | XX16        |

| 014A <sub>16</sub> |                                      |          |        | XX16        |

| 014B <sub>16</sub> |                                      |          |        | XX16        |

| 014C <sub>16</sub> |                                      |          |        | XX16        |

| 014D <sub>16</sub> |                                      |          |        | XX16        |

| 014E16             | CAN0 message box 14 : Time stamp     |          |        | XX16        |

| 014F <sub>16</sub> |                                      |          |        | XX16        |

| 015016             | CAN0 message box 15 : Identifier/DLC |          |        | XX16        |

| 015116             |                                      |          |        | XX16        |

| 015216             |                                      |          |        | XX16        |

| 015316             |                                      |          |        | XX16        |

| 015416             |                                      |          |        | XX16        |

| 015516             |                                      |          |        | XX16        |

| 015616             | CAN0 message box 15 : Data field     |          |        | XX16        |

| 015716             |                                      |          |        | XX16        |

| 015816             |                                      |          |        | XX16        |

| 015916             |                                      |          |        | XX16        |

| 015A <sub>16</sub> |                                      |          |        | XX16        |

| 015B16             |                                      |          |        | XX16        |

| 015C <sub>16</sub> |                                      |          |        | XX16        |

| 015D <sub>16</sub> |                                      |          |        | XX16        |

| 015E16             | CAN0 message box 15 : Time stamp     |          |        | XX16        |

| 015F <sub>16</sub> |                                      |          |        | XX16        |

| 016016             | CAN0 global mask register            |          | C0GMR  | XX16        |

| 016116             |                                      |          |        | XX16        |

| 016216             |                                      |          |        | XX16        |

| 016316             |                                      |          |        | XX16        |

| 016416             |                                      |          |        | XX16        |

| 016516             |                                      |          |        | XX16        |

| 016616             | CAN0 local mask A register           |          | C0LMAR | XX16        |

| 016716             |                                      |          |        | XX16        |

| 016816             |                                      |          |        | XX16        |

| 016916             |                                      |          |        | XX16        |

| 016A <sub>16</sub> |                                      |          |        | XX16        |

| 016B16             |                                      |          |        | XX16        |

| 016C16             | CAN0 local mask B register           |          | COLMBR | XX16        |

| 016D16             |                                      |          |        | XX16        |

| 016E16             |                                      |          |        | XX16        |

| 016F <sub>16</sub> |                                      |          |        | XX16        |

| 017016             |                                      |          |        | XX16        |

| 017116             |                                      |          |        | XX16        |

| :                  |                                      |          |        |             |

|                    |                                      |          |        |             |

|                    |                                      | (11.7.2) |        | 04000001/   |

| 01B316             | Flash memory control register 4      | (Note 2) | FMR4   | 0100000X2   |

| 01B4 <sub>16</sub> |                                      |          |        | 00010000    |

| 01B516             | Flash memory control register 1      | (Note 2) | FMR1   | 000XXX0X2   |

| 01B616             |                                      |          |        |             |

| 01B7 <sub>16</sub> | Flash memory control register 0      | (Note 2) | FMR0   | 0116        |

|                    |                                      |          |        |             |

|                    |                                      |          |        |             |

|                    |                                      |          |        |             |

| 01FD16             |                                      |          |        |             |

| 01FE16             |                                      |          |        |             |

| 01FF16             |                                      |          |        | 1           |

Note 1: The blank areas are reserved and cannot be used by users. Note 2: This register is included in the flash memory version.

X : Undefined

An  $\overline{\text{NMI}}$  interrupt request is generated when input on the  $\overline{\text{NMI}}$  pin changes state from high to low, after the  $\overline{\text{NMI}}$  interrupt was enabled by writing a 1 to bit 4 in the register PM2. The  $\overline{\text{NMI}}$  interrupt is a non-maskable interrupt, once it is enabled.

The input level of this  $\overline{\text{NMI}}$  interrupt input pin can be read by accessing the P8\_5 bit in the P8 register.

NMI is disabled by default after reset (the pin is a GPIO pin, P85) and can be enabled using bit 4 in the PM2 register. Once enabled, it can only be disabled by a reset signal.

The  $\overline{\text{NMI}}$  input has a digital debounce function for noise rejection. Refer to "**19.6 Digital Debounce function**" for details. When using  $\overline{\text{NMI}}$  interrupt to exit stop mode, set the NDDR register to FF16 before entering stop mode.

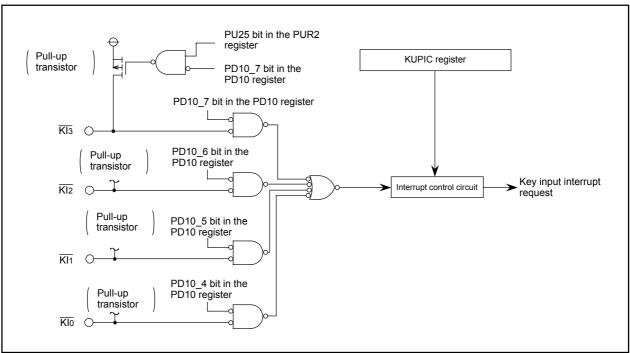

#### 9.8 Key Input Interrupt

A key input interrupt is generated when input on any of the P104 to P107 pins which has had bits PD10\_7 to PD10\_4 in the PD10 register set to 0 (= input) goes low. Key input interrupts can be used for a key-on wakeup function to get the MCU to exit stop or wait modes. However, if you intend to use the key input interrupt, do not use P104 to P107 as analog input ports. **Figure 9.12** shows the block diagram of the key input interrupt. Note, however, that while input on any pin which has had bits PD10\_7 to PD10\_4 set to 0 (= input mode) is pulled low, inputs on all other pins of the port are not detected as interrupts.

Figure 9.12 Key Input Interrupt

### 13.6.1 INPC17 Alternate Input Pin Selection

The input capture pin for IC/OC channel 7 can be assigned to one of two package pins. The CH7INSEL bit in the G1BCR0 register selects IC/OC INPC17 from P27/OUTC17/INPC17 or P17/INT5/INPC17/IDU.

### 13.6.2 Digital Debounce Function for Pin P17/INT5/INPC17

The INT5/INPC17 input from the P17/INT5/INPC17/IDU pin has an effective digital debounce function against a noise rejection. Refer to **19.6 Digital Debounce function** for this detail.

| Register            | Bit                  | Function                                                                                        |

|---------------------|----------------------|-------------------------------------------------------------------------------------------------|

| UITB <sup>(3)</sup> | 0 to 7               | Set transmission data                                                                           |

| UiRB <sup>(3)</sup> | 0 to 7               | Reception data can be read                                                                      |

|                     | OER                  | Overrun error flag                                                                              |

| UiBRG               | 0 to 7               | Set bit rate                                                                                    |

| UiMR <sup>(3)</sup> | SMD2 to SMD0         | Set to 0012                                                                                     |

|                     | CKDIR                | Select the internal clock or external clock                                                     |

|                     | IOPOL(i=2) (4)       | Set to 0                                                                                        |

| UiC0                | CLK1 to CLK0         | Select the count source for the UiBRG register                                                  |

|                     | CRS                  | Select CTS or RTS to use                                                                        |

|                     | TXEPT                | Transmit register empty flag                                                                    |

|                     | CRD                  | Enable or disable the CTS or RTS function                                                       |

|                     | NCH                  | Select TxDi pin output mode                                                                     |

|                     | CKPOL                | Select the transfer clock polarity                                                              |

|                     | UFORM                | Select the LSB first or MSB first                                                               |

| UiC1                | TE                   | Set this bit to 1 to enable transmission/reception                                              |

|                     | TI                   | Transmit buffer empty flag                                                                      |

|                     | RE                   | Set this bit to 1 to enable reception                                                           |

|                     | RI                   | Reception complete flag                                                                         |

|                     | U2IRS <sup>(1)</sup> | Select the source of UART2 transmit interrupt                                                   |

|                     | U2RRM <sup>(1)</sup> | Set this bit to 1 to use UART2 continuous receive mode                                          |

|                     | U2LCH <sup>(3)</sup> | Set this bit to 1 to use UART2 inverted data logic                                              |

|                     | U2ERE <sup>(3)</sup> | Set to 0                                                                                        |

| U2SMR               | 0 to 7               | Set to 0                                                                                        |

| U2SMR2              | 0 to 7               | Set to 0                                                                                        |

| U2SMR3              | 0 to 2               | Set to 0                                                                                        |

|                     | NODC                 | Select clock output mode                                                                        |

|                     | 4 to 7               | Set to 0                                                                                        |

| U2SMR4              | 0 to 7               | Set to 0                                                                                        |

| UCON                | U0IRS, U1IRS         | Select the source of UART0/UART1 transmit interrupt                                             |

|                     | U0RRM, U1RRM         | Set this bit to 1 to use continuous receive mode                                                |

|                     | CLKMD0               | Select the transfer clock output pin when CLKMD1 is set to 1                                    |

|                     | CLKMD1               | Set this bit to 1 to output UART1 transfer clock from two pins                                  |

|                     | RCSP                 | Set this bit to 1 to accept as input the UART0 $\overline{\text{CTS0}}$ signal from the P64 pin |

|                     | 7                    | Set to 0                                                                                        |

NOTES:

- 1. Set bits 5 and 4 in registers U0C1 and U1C1 to 0. Bits U0IRS, U1IRS, U0RRM, and U1RRM are in the UCON register.

- 2. Not all register bits are described above. Set those bits to 0 when writing to the registers in clock synchronous serial I/O mode.

- 3. Set bits 7 and 6 in registers U0C1 and U1C1 to 0.

- 4. Set the bit 7 in registers U0MR and U1MR to 0.

i=0 to 2

# 15. A/D Converter

#### Note

Ports P04 to P07(AN04 to AN07), P10 to P13(AN20 to AN23) and P95 to P97(AN25 to AN27) are not available in 64-pin package. Do not use port P04 to P07(AN04 to AN07), P10 to P13(AN20 to AN23) and P95 to P97(AN25 to AN27) as analog input pins in 64-pin package.

The MCU contains one A/D converter circuit based on 10-bit successive approximation method configured with a capacitive-coupling amplifier. The analog inputs share the pins with P100 to P107 (AN0 to AN7), P00 to P07 (AN00 to AN07), and P10 to P13, P93, P95 to P97 (AN20 to AN27), and P90 to P92 (AN30 to AN32). Similarly, ADTRG input shares the pin with P15. Therefore, when using these inputs, make sure the corresponding port direction bits are set to 0 (input mode).

When not using the A/D converter, set the VCUT bit to 0 (Vref unconnected), so that no current will flow from the Vref pin into the resistor ladder, helping to reduce the power consumption of the chip.

The A/D conversion result is stored in the ADi register bits for ANi, AN0i, AN2i (i = 0 to 7), and AN3i pins (i = 0 to 2). **Table 15.1** shows the A/D converter performance. **Figure 15.1** shows the A/D converter block diagram and **Figures 15.2** to **15.4** show the A/D converter associated with registers.

| Table 15.1 A/D Converter                 | Terrormanee                                                                        |

|------------------------------------------|------------------------------------------------------------------------------------|

| Item                                     | Performance                                                                        |

| A/D Conversion Method                    | Successive approximation (capacitive coupling amplifier)                           |

| Analog Input Voltage (1)                 | 0V to AVcc (Vcc)                                                                   |

| Operating Clock $\phi$ AD <sup>(2)</sup> | fAD/divided-by-2 or fAD/divided-by-3 or fAD/divided-by-4 or fAD/divided-by-6       |

|                                          | or fAD/divided-by-12 or fAD                                                        |

| Resolution                               | 8-bit or 10-bit (selectable)                                                       |

| Integral Nonlinearity Error              | When AVcc = Vref = 5V                                                              |

|                                          | With 8-bit resolution: ±2LSB                                                       |

|                                          | With 10-bit resolution: ±3LSB                                                      |

|                                          | When AVcc = Vref = 3.3V                                                            |

|                                          | With 8-bit resolution: ±2LSB                                                       |

|                                          | With 10-bit resolution: ±5LSB                                                      |

| Operating Modes                          | One-shot mode, repeat mode, single sweep mode, repeat sweep mode 0, repeat         |

|                                          | sweep mode 1, simultaneous sample sweep mode and delayed trigger mode 0,1          |

| Analog Input Pins                        | 8 pins (AN0 to AN7) + 8 pins (AN00 to AN07) + 8 pins (AN20 to AN27) + 3 pins (AN30 |

|                                          | to AN32) (80-pin package)                                                          |

|                                          | 8 pins (AN0 to AN7) + 4 pins (AN00 to AN03) + 1 pin (AN24) + 3 pins (AN30 to AN32) |

|                                          | (64-pin package)                                                                   |

| Conversion Speed Per Pin                 | Without sample and hold function                                                   |

|                                          | 8-bit resolution: 49 (AD cycles, 10-bit resolution: 59 (AD cycles                  |

|                                          | With sample and hold function                                                      |

|                                          | 8-bit resolution: 28 (AD cycles, 10-bit resolution: 33 (AD cycles                  |

#### Table 15.1 A/D Converter Performance

NOTES:

- 1. Not dependent on use of sample and hold function.

- 2. Set the  $\ensuremath{\varphi}AD$  frequency to 10 MHz or less.

Without sample-and-hold function, set the  $\phi$ AD frequency to 250kHz or more.

With the sample and hold function, set the  $\phi$ AD frequency to 1MHz or more.

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Symbol<br>ADTRG | Address<br>CON 03D216                                   | After Reset<br>0016                                         |    |

|-------------------------------------------------------|-----------------|---------------------------------------------------------|-------------------------------------------------------------|----|

|                                                       | Bit Symbol      | Bit Name                                                | Function                                                    | RW |

|                                                       | SSE             | A/D operation mode select bit 2                         | Simultaneous sample sweep mode or delayed trigger mode 0, 1 | RW |

| · · · · ·                                             | DTE             | A/D operation mode select bit 3                         | Delayed trigger mode 0, 1                                   | RW |

|                                                       | HPTRG0          | AN0 trigger select bit                                  | See Table 15.13                                             | RW |

|                                                       | HPTRG1          | AN1 trigger select bit                                  | See Table 15.13                                             | RW |

|                                                       | (b7-b4)         | Nothing is assigned. If nec When read, the content is 0 |                                                             | -  |

Figure 15.28 ADTRGCON Register in Delayed Trigger Mode 1

### Table 15.13 Trigger Select Bit Setting in Delayed Trigger Mode 1

| TRG | TRG1 | HPTRG0 | HPTRG1 | Trigger |

|-----|------|--------|--------|---------|

| 0   | 1    | 0      | 0      | ADTRG   |

### 16.13.2 Example of Slave Receive

For example, a slave receives data as shown below when following conditions are met: high-speed clock mode, SCL frequency of 400 kHz, ACK clock added and addressing format.

- 1) Set a slave address in the 7 high-order bits in the S0D0 register

- 2) Set A516 to the S20 register, 0002 to bits ICK4 to ICK2 in the S4D0 register, and 0016 to the S3D0 register to generate an ACK clock and set SCL clock frequency at 400kHz (f1 = 8 MHz, filc = f1)

- 3) Set 0016 to the S10 register to reset transmit/receive mode

- 4) Set 0816 to the S1D0 register to enable data communication

- 5) When a START condition is received, addresses are compared

- 6) •When the transmitted addresses are all 0 (general call), the ADR0 bit in the S10 register is set to 1 and an I<sup>2</sup>C bus interface interrupt request signal is generated.

•When the transmitted addresses match with the address set in 1), the ASS bit in the S10 register is set to 1 and an  $I^2C$  bus interface interrupt request signal is generated.

•In other cases, bits ADR0 and AAS are set to 0 and I<sup>2</sup>C bus interface interrupt request signal is not generated.

- 7) Write dummy data to the S00 register.

- After receiving 1-byte data, an ACK-CLK bit is automatically returned and an I<sup>2</sup>C bus interface interrupt request signal is generated.

- 9) To determine whether the ACK should be returned depending on contents in the received data, set dummy data to the S00 register to receive data after setting the WIT bit in te S3D0 register to 1 (enable the I<sup>2</sup>C bus interface interrupt of data receive completion). Because the I<sup>2</sup>C bus interface interrupt is generated when the 1-byte data is received, set the ACKBIT bit to 1 or 0 to output a signal from the ACKBIT bit.

- 10) When receiving more than 1-byte control data, repeat steps 7) and 8) or 7) and 9).

- 11) When a STOP condition is detected, the communication is ended.

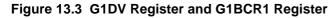

bit 0 bit 7 SID10 SID9 SID8 SID7 SID6 SID4 SID SID3 SID<sub>2</sub> SID1 SID<sub>0</sub> EID<sub>14</sub> EID<sub>17</sub> EID<sub>16</sub> EID<sub>15</sub> EID13 EID12 EID11 EID10 EID9 EID8 EID7 EID6 FID4 EID2 EID5 EID3 EID1 EID<sub>0</sub> DLC3 DLC2 DLC1 DLC<sub>0</sub> Data Byte 0 Data Byte 1 Data Byte 7 Time Stamp high-order byte Time Stamp low-order byte **CAN Data Frame:** SID 10 to 6 SID5 to 0 EID17 to 14 EID13 to 6 EID5 to 0 DLC3 to 0 Data Byte 0 Data Byte 1 -----Data Byte 7 NOTE: 1. When |X| is read, the value is the one written upon the transmission slot configuration. The value is 0 when read on the reception slot configuration.

**Figures 17.2** and **17.3** show the bit mapping in each slot in byte access and word access. The content of each slot remains unchanged unless transmission or reception of a new message is performed.

Figure 17.2 Bit Mapping in Byte Access

Figure 17.3 Bit Mapping in Word Access

RENESAS

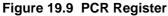

Figure 19.10 PACR Register

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbol<br>ROMCP | Address<br>0FFFFF16                              | Factory Setting<br>FF16 <sup>(4)</sup> |    |

|-------------------------|-----------------|--------------------------------------------------|----------------------------------------|----|

|                         | Bit Symbol      | Bit Name                                         | Function                               | RW |

|                         | (b5-b0)         | Reserved Bit                                     | Set to 1                               | RW |

|                         | ROMCP1          | ROM Code Protect Level<br>1 Set Bit (1, 2, 3, 4) | 00:<br>01: Enables protect             | RW |

|                         |                 |                                                  | 10: <b>J</b> Linables protect          | RW |

- 1. When the ROM code protect is active by the ROMCP1 bit setting, the flash memory is protected against reading or rewriting in parallel I/O mode.

- 2. Set the bit 5 to bit 0 to 1111112 when the ROMCP1 bit is set to a value other than 112. When the bit 5 to bit 0 are set to values other than 1111112, the ROM code protection may not become active by setting the ROMCP1 bit to a value other than 112.

- 3. To make the ROM code protection inactive, erase a block including the ROMCP address in standard serial I/O mode or CPU rewrite mode.

- 4. The ROMCP address is set to FF16 when a block, including the ROMCP address, is erased.

- 5. When a value of the ROMCP address is 0016 or FF16, the ROM code protect function is disabled.

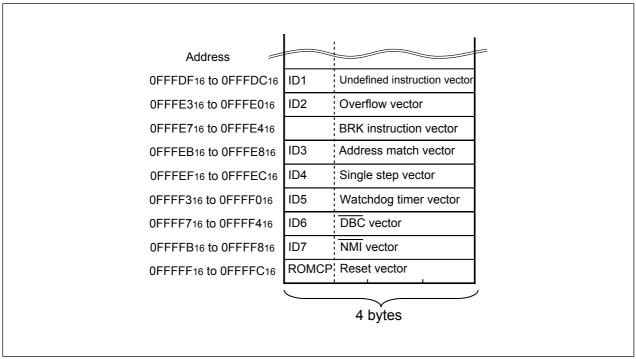

#### Figure 20.4 ROMCP Address

Figure 20.5 Address for ID Code Stored

## 20.11 CAN I/O Mode

Note

The CAN I/O mode is not available in M16C/29 T-ver./V-ver.

In CAN I/O mode, the user ROM area can be rewritten while the MCU is mounted on-board by using a CAN programmer which is applicable for the M16C/29 group. For more information about CAN programmers, contact the manufacturer of your CAN programmer. For details on how to use, refer to the user's manual included with your CAN programmer.

Table 20.9 lists pin functions for CAN I/O mode. Figures 20.19 and 20.20 show pin connections for CAN I/O mode.

### 20.11.1 ID code check function

This function determines whether the ID codes sent from the CAN programmer and those written in the flash memory match.(Refer to **20.3 Functions To Prevent Flash Memory from Rewriting**.)

| Symbol   |                    | Parameter                                                        |                                                             |                         |        | Stand  | lard        | Unit |

|----------|--------------------|------------------------------------------------------------------|-------------------------------------------------------------|-------------------------|--------|--------|-------------|------|

| Symbol   |                    | F                                                                | arameter                                                    |                         | Min.   | Тур.   | Max.        |      |

| Vcc      | Supply Voltage     |                                                                  |                                                             |                         | 2.7    |        | 5.5         | V    |

| AVcc     | Analog Supply Vo   | tage                                                             |                                                             |                         |        | Vcc    |             | V    |

| Vss      | Supply Voltage     |                                                                  |                                                             |                         |        | 0      |             | V    |

| AVss     | Analog Supply Vo   | ltage                                                            | age                                                         |                         |        | 0      |             | V    |

| Vih      | Input High ("H")   | P00 to P07, P10 t                                                | P00 to P07, P10 to P17, P20 to P27, P30 to P37, P60 to P67, |                         | 0.7Vcc |        | Vcc         | V    |

|          | Voltage            | P70 to P77, P80 t                                                | o P87, P90 to P93, P                                        | 95 to P97, P100 to P107 |        |        |             |      |

|          |                    | XIN, RESET, CI                                                   | IVSS                                                        |                         | 0.8Vcc |        | Vcc         | V    |

|          |                    |                                                                  | When I <sup>2</sup> C bus input                             | t level is selected     | 0.7Vcc |        | Vcc         | V    |

|          | SDAMM, SCLMM       | When SMBUS inpu                                                  | It level is selected                                        | 1.4                     |        | Vcc    | V           |      |

| VIL      | Input Low ("L")    | P00 to P07, P10 t                                                | o P17, P20 to P27, P                                        | 30 to P37, P60 to P67,  | 0      |        | 0.3Vcc      | V    |

|          | Voltage            | P70 to P77, P80 t                                                | o P87, P90 to P93, P                                        | 95 to P97, P100 to P107 |        |        |             |      |

|          | XIN, RESET, CN     | IVSS                                                             |                                                             | 0                       |        | 0.2Vcc | V           |      |

|          |                    | When I <sup>2</sup> C bus input                                  | t level is selected                                         | 0                       |        | 0.3Vcc | V           |      |

|          |                    | SDAMM, SCLMM                                                     | When SMBUS inpu                                             | It level is selected    | 0      |        | 0.6         | V    |

| OH(peak) | Peak Output High   | High P00 to P07, P10 to P17, P20 to P27, P30 to P37, P60 to P67, |                                                             |                         |        | -10.0  | mA          |      |

|          | ("H") Current      | P70 to P77, P80 to P87, P90 to P93, P95 to P97, P100 to P107     |                                                             |                         |        |        |             |      |

| OH(avg)  | Average Output     |                                                                  |                                                             | 30 to P37, P60 to P67,  |        |        | -5.0        | mA   |

|          | High ("H") Current | P70 to P77, P80 t                                                | o P87, P90 to P93, P                                        | 95 to P97, P100 to P107 |        |        |             |      |

| OL(peak) | Peak Output Low    | P00 to P07, P10 t                                                | o P17, P20 to P27, P                                        | 30 to P37, P60 to P67,  |        |        | 10.0        | mA   |

|          | ("L") Current      |                                                                  |                                                             | 95 to P97, P100 to P107 |        |        |             |      |

| OL(avg)  | Average Output     |                                                                  |                                                             | 30 to P37, P60 to P67,  |        |        | 5.0         | mA   |

|          | Low ("L") Current  |                                                                  |                                                             | 95 to P97, P100 to P107 |        |        |             |      |

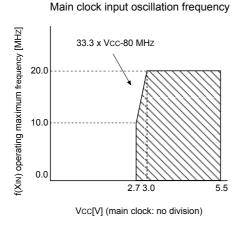

| f(XiN)   | Main Clock Input   | Oscillation Freque                                               | ency <sup>(4)</sup>                                         | Vcc=3.0 to 5.5V         | 0      |        | 20          | MHz  |

|          |                    |                                                                  |                                                             | Vcc=2.7 to 3.0V         | 0      |        | 33 X Vcc-80 | MHz  |

| f(Xcin)  | Sub Clock Oscilla  |                                                                  |                                                             |                         |        | 32.768 | 50          | kHz  |

| f1(ROC)  | On-chip Oscillator | Frequency 1                                                      |                                                             |                         | 0.5    | 1      | 2           | MHz  |

| f2(ROC)  | On-chip Oscillator | Frequency 2                                                      |                                                             |                         | 1      | 2      | 4           | MHz  |

| f3(ROC)  | On-chip Oscillator | Frequency 3                                                      |                                                             |                         | 8      | 16     | 26          | MHz  |

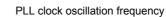

| f(PLL)   | PLL Clock Oscilla  | tion Frequency <sup>(4)</sup>                                    |                                                             | Vcc=3.0 to 5.5V         | 10     |        | 20          | MHz  |

|          |                    |                                                                  |                                                             | Vcc=2.7 to 3.0V         | 10     |        | 33 X Vcc-80 | MHz  |

| f(BCLK)  | CPU Operation C    | lock Frequency                                                   |                                                             | 1                       | 0      |        | 20          | MHz  |

| tsu(PLL) | Wait Time to Stab  | ilize PLL Frequer                                                | ncy Synthesizer                                             | Vcc=5.0V                |        |        | 20          | ms   |

|          |                    |                                                                  |                                                             | Vcc=3.0V                |        |        | 50          | ms   |

#### Table 21.2 Recommended Operating Conditions (Note 1)

NOTES:

1. Referenced to V $\infty$  = 2.7 to 5.5V at Topr = -20 to 85 ° C / -40 to 85 ° C unless otherwise specified. 2. The mean output current is the mean value within 100ms.

3. The total IOL(peak) for all ports must be 80mA or less. The total IOH(peak) for all ports must be -80mA or less.

4. Relationship among main clock oscillation frequency, PLL clock oscillation frequency and supply voltage.

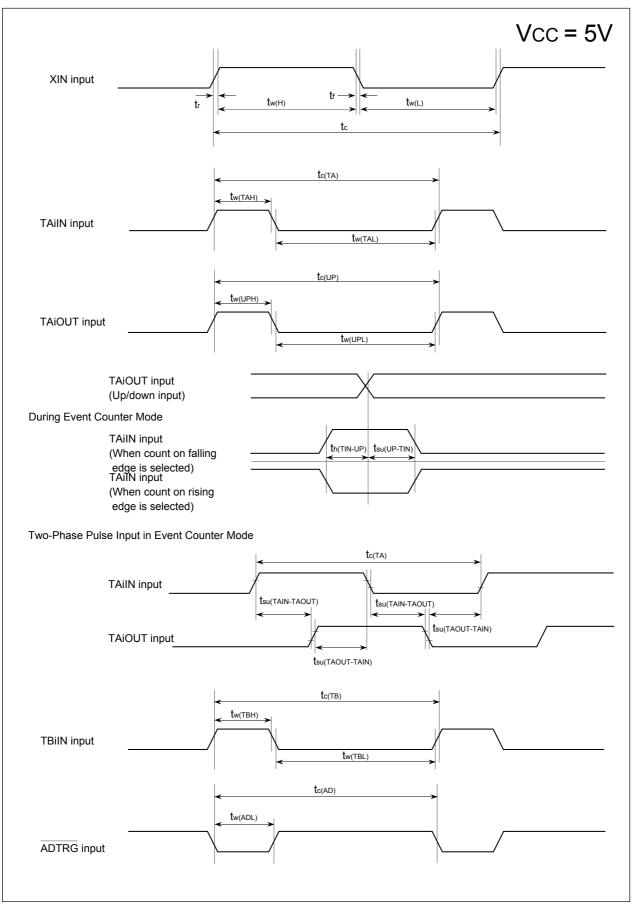

#### **Timing Requirements**

## Vcc = 5V

#### (VCC = 5V, VSS = 0V, at Topr = - 20 to 85°C / - 40 to 85°C unless otherwise specified)

#### Table 21.10 External Clock Input (XIN input)

| Symbol | Parameter                             |      | Standard |      |  |

|--------|---------------------------------------|------|----------|------|--|

| Symbol | Falantelei                            | Min. | Max.     | Unit |  |

| tc     | External Clock Input Cycle Time       | 50   |          | ns   |  |

| tw(H)  | External Clock Input High ("H") Width | 20   |          | ns   |  |

| tw(L)  | External Clock Input Low ("L") Width  | 20   |          | ns   |  |

| tr     | External Clock Rise Time              |      | 9        | ns   |  |

| tf     | External Clock Fall Time              |      | 9        | ns   |  |

#### **Timing Requirements**

## Vcc = 3V

### (VCC = 3V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| 0       |                                     | Standard clock mode |      | High-speed clock mode |      |      |

|---------|-------------------------------------|---------------------|------|-----------------------|------|------|

| Symbol  | Parameter                           | Min.                | Max. | Min.                  | Max. | Unit |

| tBUF    | Bus free time                       | 4.7                 |      | 1.3                   |      | μs   |

| tHD;STA | The hold time in start condition    | 4.0                 |      | 0.6                   |      | μs   |

| tLOW    | The hold time in SCL clock 0 status | 4.7                 |      | 1.3                   |      | μs   |

| tR      | SCL, SDA signals' rising time       |                     | 1000 | 20+0.1Cb              | 300  | ns   |

| tHD;DAT | Data hold time                      | 0                   |      | 0                     | 0.9  | μs   |

| tHIGH   | The hold time in SCL clock 1 status | 4.0                 |      | 0.6                   |      | μs   |

| tF      | SCL, SDA signals' falling time      |                     | 300  | 20+0.1Cb              | 300  | ns   |

| tsu;DAT | Data setup time                     | 250                 |      | 100                   |      | ns   |

| tsu;STA | The setup time in restart condition | 4.7                 |      | 0.6                   |      | μs   |

| tsu;STO | Stop condition setup time           | 4.0                 |      | 0.6                   |      | μs   |

#### Table 21.39 Multi-master I<sup>2</sup>C bus Line

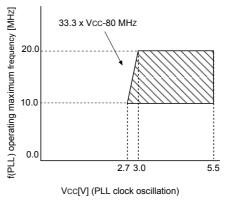

#### Table 21.45 Power Supply Circuit Timing Characteristics

| Symbol  | Parameter                                                        | Measurement Condition | Standard |      |      | Unit |

|---------|------------------------------------------------------------------|-----------------------|----------|------|------|------|

|         |                                                                  |                       | Min.     | Тур. | Max. |      |

| td(P-R) | Wait Time to Stabilize Internal Supply Voltage when<br>Power-on  |                       |          |      | 2    | ms   |

| td(ROC) | Wait Time to Stabilize Internal On-chip Oscillator when Power-on | Vcc = 3.0 to 5.5V     |          |      | 40   | μs   |

| td(R-S) | STOP Release Time <sup>(1)</sup>                                 |                       |          |      | 150  | μs   |

| td(W-S) | Low Power Dissipation Mode Wait Mode Release<br>Time             |                       |          |      | 150  | μs   |

Figure 21.7 Timing Diagram (1)

## **REVISION HISTORY**

## M16C/29 Hardware Manual

| Rev. | Date       |              | Description                                                                    |  |

|------|------------|--------------|--------------------------------------------------------------------------------|--|

|      |            | Page Summary |                                                                                |  |

|      |            | 360          | Table 21.1 is partly revised.                                                  |  |

|      |            | 368          | Section "21.4.2 EW1 Mode" is partly revised.                                   |  |

| 0.80 | Sep/03/Y04 | 2,3          | Table 1.2.1 and Table 1.2.2 are partly revised.                                |  |

|      |            | 6,7          | Table 1.4.1 to Table 1.4.3 are partly revised.                                 |  |

|      |            | 7            | Figure 1.4.1 is partly revised.                                                |  |

|      |            | 8,9          | Figure 1.5.1 and Figure 1.5.2 are partly revised.                              |  |

|      |            | 21           | Figure 4.7 is partly revised.                                                  |  |

|      |            | 24           | Figure 4.10 is partly revised.                                                 |  |

|      |            | 26           | Section "5.1.2 Hardware Reset 2" is partly revised.                            |  |

|      |            | 29 to 34     | Section "5.5 Voltage Detection Circuit" is revised.                            |  |

|      |            | 80           | Section "10.2 Cold start / Warm start" is added.                               |  |

|      |            | 322          | Table 20.2 is partly revised.                                                  |  |

|      |            | 323          | Table 20.3 is partly revised.                                                  |  |

|      |            | 325          | Table 20.6 and Table 20.7 are partly revised.                                  |  |

|      |            | 327          | Table 20.9 is partly revised.                                                  |  |

|      |            | 331          | Title of Table 20.23 is partly revised.                                        |  |

|      |            | 335          | Table 20.25 is partly revised.                                                 |  |

|      |            | 339          | Title of Table 20.39 is partly revised.                                        |  |

|      |            | 343          | Table 20.41 is partly revised.                                                 |  |

|      |            | 344          | Table 20.42 is partly revised.                                                 |  |

|      |            | 346          | "Low Voltage Detection Circuit Electrical Characteristics" is deleted.         |  |

|      |            |              | Talbe 20.45 is partly revised.                                                 |  |

|      |            | 348          | Table 20.47 is partly revised.                                                 |  |

|      |            | 352          | Title of Table 20.61 is partly revised.                                        |  |

|      |            | 356          | Talbe 20.63 is partly revised.                                                 |  |

|      |            | 360          | Title of Table 20.77 is partly revised.                                        |  |

|      |            | 398          | 64P6Q-A package is revised.                                                    |  |

| 1.00 | Nov/01/Y04 | All pages    | Words standardized (on-chip oscillator, A/D)                                   |  |

|      |            | 2, 3         | Table1.2.1 and Table 1.2.2 are partly revised.                                 |  |

|      |            | 8, 9         | Table 1.4.4 to 1.4.6 and figure 1.4.2 to 1.4.6 are added.                      |  |

|      |            | 28           | "5.1.2 Hardware Reset 2" is partly revised.                                    |  |

|      |            | 29           | "5.4 Oscillation Stop Detection Reset" is partly revised.                      |  |

|      |            | 38           | Table 7.1 is partly revised.                                                   |  |

|      |            | 41           | Note 6 in Figure 7.3 is partly revised. b7 to b4 bit in Figure 7.4 is revised. |  |

|      |            | 42           | Figure 7.5 is partly revised.                                                  |  |

|      |            | 43           | "PCLKR register" in Figure 7.6 is partly revised.                              |  |

|      |            | 50           | "7.6.1 Normal Operation Mode" is partly revised.                               |  |

|      |            | 51           | Note 1 in Table 7.6.1.1 is partly revised.                                     |  |

|      |            | 57           | "7.8 Oscillation Stop and Re-oscillation Detect Function" is partly revised.   |  |

### **REVISION HISTORY**

## M16C/29 Hardware Manual

| Rev. | Date |        | Description                                                                                                                                           |  |  |

|------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      |      | Page   | Summary                                                                                                                                               |  |  |

|      |      | 9      | Tables 1.6 to 1.8 Product Codes modified                                                                                                              |  |  |

|      |      | 19, 20 | Table 1.14 Pin Description pin description on I/O ports modified                                                                                      |  |  |

|      |      |        | Reset                                                                                                                                                 |  |  |

|      |      | 37     | Figure 5.2 Reset Sequence Vcc and ROC timings modified                                                                                                |  |  |

|      |      |        | Processor Mode                                                                                                                                        |  |  |

|      |      | 45     | • Figure 6.2 PM2 Register Description on notes 5 and 6 modified                                                                                       |  |  |

|      |      |        | Clock Generation Circuit                                                                                                                              |  |  |

|      |      | 52     | Figure 7.6 PM2 Register Description on notes 5 and 6 modified                                                                                         |  |  |

|      |      | 64     | Figure 7.12 State Transition in Normal Mode note 2 modified                                                                                           |  |  |

|      |      |        | Protection                                                                                                                                            |  |  |

|      |      | 69     | Description on protection modified                                                                                                                    |  |  |

|      |      |        | Figure 8.1 PRCR Register note 1 modified                                                                                                              |  |  |

|      |      |        | Interrupts                                                                                                                                            |  |  |

|      |      | 88     | Table 9.6 PC Value Saved in Stack Area When Address Match Interrupt                                                                                   |  |  |

|      |      |        | Request I Acknowledged instruction modified                                                                                                           |  |  |

|      |      |        | Watchdog Timer                                                                                                                                        |  |  |

|      |      | 90     | Figure10.2 WDTS Register modified                                                                                                                     |  |  |

|      |      |        | 10.1 Count Source Protective Mode description modified                                                                                                |  |  |

|      |      |        | Timer                                                                                                                                                 |  |  |

|      |      | 129    | Figure 12.28 ICTB2 Register modified                                                                                                                  |  |  |

|      |      |        | Multi-Master I <sup>2</sup> C bus Interface                                                                                                           |  |  |

|      |      | 256    | • Figure 16.1 Block Diagram of Multi-Master I <sup>2</sup> C bus Interface modified                                                                   |  |  |

|      |      | 005    | Flash Memory Version                                                                                                                                  |  |  |

|      |      | 335    | • 20.3.1 ROM Code Protect Function register name modified                                                                                             |  |  |

|      |      | 340    | • 20.5.2 Flash Memory Control Register 1 description on FMR17 bit modified                                                                            |  |  |

|      |      | 341    | Figure 20.6 FMR1 Register note 2 modified                                                                                                             |  |  |

|      |      | 343    | Figure 20.9 Setting and Resetting of EW Mode 1 modified     Electrical Characteristics                                                                |  |  |

|      |      | 369    |                                                                                                                                                       |  |  |

|      |      | 309    | • Table 21.5 Flash Memory Version Electrical Characteristics note 10 modi-                                                                            |  |  |

|      |      | 370    | fied                                                                                                                                                  |  |  |

|      |      | 370    | <ul> <li>Timing figure for td(P-R) and td(ROC) modified</li> <li>Table 21.9 Electrical Characteristics parameter and measurement condition</li> </ul> |  |  |

|      |      | 572    | modified, note 5 deleted                                                                                                                              |  |  |

|      |      | 380    | • Table 21.25 Electrical Characteristics measurement condition modified, note                                                                         |  |  |

|      |      | 500    | 5 deleted                                                                                                                                             |  |  |

|      |      | 390    | • Tables 21.43 and 44 Flash Memory Version Electrical Characteristics note                                                                            |  |  |

|      |      | 000    | 10 modified                                                                                                                                           |  |  |

|      |      | 391    | Timing figure for td(P-R) and td(ROC) modified                                                                                                        |  |  |

|      |      | 393    | • Table 21.47 Electrical Characteristics parameter and condition modified, note                                                                       |  |  |

|      |      | 293    | - Table 21.47 Electrical characteristics parameter and condition modified, note                                                                       |  |  |