#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

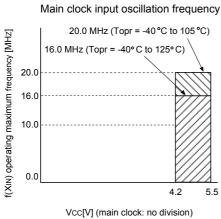

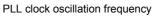

| Speed                      | 20MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                              |

| Number of I/O              | 55                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

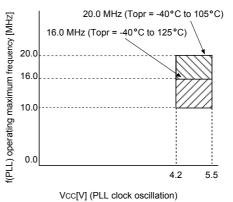

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fchp-u9a |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Quick Reference to Pages Classified by Address

| Address                                                                                | Register                                                             | Symbol | Page       | Address                                                                      | Register                                                             | Symbol | Page       |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|------------|

| 008016<br>008116<br>008216<br>008316<br>008416<br>008516                               | CAN0 message box 2: Identifier/DLC                                   |        | 289        | 00C016<br>00C116<br>00C216<br>00C316<br>00C416<br>00C516                     | CAN0 message box 6: Identifier/DLC                                   |        | 289        |

| 008616<br>008716<br>008816<br>008916<br>008A16<br>008B16<br>008C16<br>008D16           | CAN0 message box 2: Data field                                       |        | 289        | 00C616<br>00C716<br>00C816<br>00C916<br>00CA16<br>00CB16<br>00CC16<br>00CC16 | CAN0 message box 6: Data field                                       |        | 289        |

| 008E16<br>008F16                                                                       | CAN0 message box 2: time stamp                                       |        | 289        | 00CE16<br>00CF16                                                             | CAN0 message box 6: time stamp                                       |        | 289        |

| 009016<br>009116<br>009216<br>009316<br>009416<br>009516                               | CAN0 message box 3: Identifier/DLC                                   |        | 289        | 00D016<br>00D116<br>00D216<br>00D316<br>00D416<br>00D516                     | CAN0 message box 7: Identifier/DLC                                   |        | 289        |

| 009616<br>009716<br>009816<br>009916<br>009A16<br>009B16<br>009C16<br>009D16           | CAN0 message box 3: Data field                                       |        | 289        | 00D616<br>00D716<br>00D816<br>00D916<br>00DA16<br>00DB16<br>00DC16<br>00DD16 | CAN0 message box 7: Data field                                       |        | 289        |

| 009E16<br>009F16<br>00A016<br>00A116<br>00A216<br>00A316<br>00A416                     | CAN0 message box 3: time stamp<br>CAN0 message box 4: Identifier/DLC |        | 289<br>289 | 00DE16<br>00DF16<br>00E016<br>00E116<br>00E216<br>00E316<br>00E416           | CAN0 message box 7: time stamp<br>CAN0 message box 8: Identifier/DLC |        | 289<br>289 |

| 00A516<br>00A616<br>00A716<br>00A816<br>00A916<br>00AA16<br>00AB16<br>00AC16<br>00AD16 | CAN0 message box 4: Data field                                       |        | 289        | 00E516<br>00E616<br>00E716<br>00E816<br>00E916<br>00EA16<br>00EB16<br>00EC16 | CAN0 message box 8: Data field                                       |        | 289        |

| 00AE16<br>00AF16                                                                       | CAN0 message box 4: time stamp                                       |        | 289        | 00EE16<br>00EF16                                                             | CAN0 message box 8: time stamp                                       |        | 289        |

| 00B016<br>00B116<br>00B216<br>00B316<br>00B416<br>00B516                               | CAN0 message box 5: Identifier/DLC                                   |        | 289        | 00F016<br>00F116<br>00F216<br>00F316<br>00F416<br>00F516                     | CAN0 message box 9: Identifier/DLC                                   |        | 289        |

| 008616<br>008716<br>008816<br>008916<br>008A16<br>008A16<br>008B16<br>008C16           | CAN0 message box 5: Data field                                       |        | 289        | 00F616<br>00F716<br>00F816<br>00F916<br>00FA16<br>00FB16<br>00FC16<br>00FC16 | CAN0 message box 9: Data field                                       |        | 289        |

| 00BE16<br>00BF16                                                                       | CAN0 message box 5: time stamp                                       |        | 289        | 00FE16<br>00FF16                                                             | CAN0 message box 9: time stamp                                       |        | 289        |

Note: The blank areas are reserved and cannot be accessed by users.

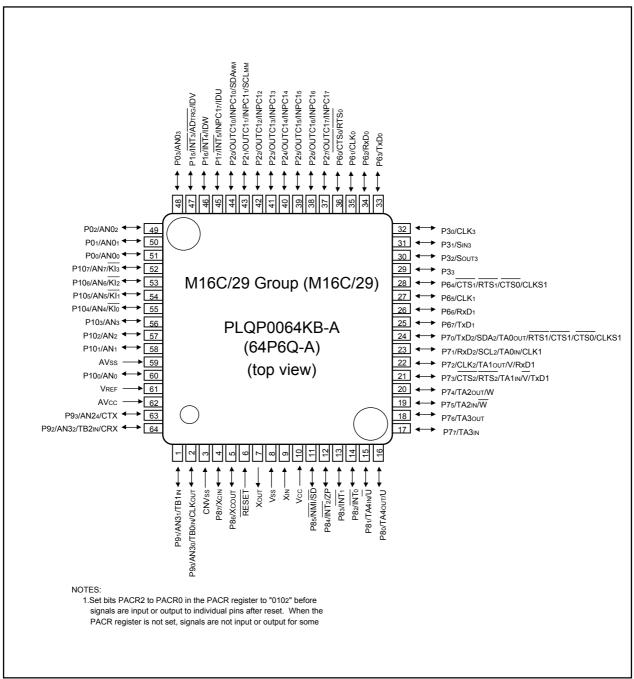

Figure 1.9 Pin Assignment (Top View) of 64-Pin Package

### Table 4.9 SFR Information (9)

|                                          | 4.9 SFR Information (9)                             | Current el     | After reach       |

|------------------------------------------|-----------------------------------------------------|----------------|-------------------|

| Address<br>0340 <sub>16</sub>            | Register                                            | Symbol         | After reset       |

| 034016                                   |                                                     |                |                   |

| 034216                                   | Timer A1-1 register                                 | TA11           | XX16              |

| 034316                                   |                                                     |                | XX16              |

| 034416                                   | Timer A2-1 register                                 | TA21           | XX16              |

| 034516                                   |                                                     |                | XX16              |

| 034616                                   | Timer A4-1 register                                 | TA41           | XX16              |

| 034716                                   |                                                     |                | XX16              |

| 034816                                   | Three phase PWM control register 0                  | INVC0          | 0016              |

| 034916                                   | Three phase PWM control register 1                  | INVC1          | 0016              |

| 034A <sub>16</sub>                       | Three phase output buffer register 0                | IDB0           | 0016              |

| 034B16                                   | Three phase output buffer register 1                | IDB1           | 0016              |

| 034C16                                   | Dead time timer                                     | DTT            | XX16              |

| 034D16                                   | Timer B2 Interrupt occurrence frequency set counter | ICTB2          | XX16              |

| 034E16                                   | Position - data - retain function control register  | PDRF           | XXXX00002         |

| 034F16<br>035016                         |                                                     |                |                   |

| 035016                                   |                                                     |                |                   |

| 035216                                   |                                                     |                |                   |

| 035316                                   |                                                     |                |                   |

| 035416                                   |                                                     |                |                   |

| 035516                                   |                                                     |                |                   |

| 035616                                   |                                                     |                |                   |

| 035716                                   |                                                     |                |                   |

| 035816                                   | Port function control register                      | PFCR           | 001111112         |

| 035916                                   |                                                     |                |                   |

| 035A16                                   |                                                     |                |                   |

| 035B16                                   |                                                     |                |                   |

| 035C16                                   |                                                     |                |                   |

| 035D16                                   | Interrupt cause select register 2 <sup>(2)</sup>    |                | 00////000-        |

| 035E16<br>035F16                         | Interrupt cause select register 2(*)                | IFSR2A<br>IFSR | 00XXX0002<br>0016 |

| 036016                                   | SI/O3 transmit/receive register                     | S3TRR          | XX16              |

| 036116                                   |                                                     | 001111         | 70(10             |

| 036216                                   | SI/O3 control register                              | S3C            | 01000002          |

| 036316                                   | SI/O3 bit rate register                             | S3BRG          | XX16              |

| 036416                                   | SI/O4 transmit/receive register                     | S4TRR          | XX16              |

| 036516                                   |                                                     |                |                   |

| 036616                                   | SI/O4 control register                              | S4C            | 01000002          |

| 036716                                   | SI/O4 bit rate register                             | S4BRG          | XX16              |

| 036816                                   |                                                     |                |                   |

| 036916                                   |                                                     |                |                   |

| 036A16                                   |                                                     |                |                   |

| 036B16                                   |                                                     |                |                   |

| 036C16<br>036D16                         |                                                     |                |                   |

| 036D16                                   |                                                     |                |                   |

| 036F16                                   |                                                     |                |                   |

| 037016                                   |                                                     |                |                   |

| 037116                                   |                                                     |                |                   |

| 037216                                   |                                                     |                |                   |

| 037316                                   |                                                     |                |                   |

| 037416                                   | UART2 special mode register 4                       | U2SMR4         | 0016              |

| 037516                                   | UART2 special mode register 3                       | U2SMR3         | 000X0X0X2         |

| 037616                                   | UART2 special mode register 2                       | U2SMR2         | X0000002          |

| 037716                                   | UART2 special mode register                         | U2SMR          | X0000002          |

| 037816                                   | UART2 transmit/receive mode register                | U2MR           | 0016              |

| 037916                                   | UART2 bit rate register                             | U2BRG<br>U2TB  | XX16<br>XX16      |

| 037A16                                   | UART2 transmit buffer register                      | UZIB           | XX16<br>XX16      |

| 037B <sub>16</sub><br>037C <sub>16</sub> | UART2 transmit/receive control register 0           | U2C0           | 000010002         |

| 037C16                                   | UART2 transmit/receive control register 0           | U2C1           | 000010002         |

| 037D16                                   | UART2 receive buffer register                       | U2RB           | XX16              |

| 037F16                                   |                                                     |                | XX16              |

|                                          |                                                     |                |                   |

Note 1: The blank areas are reserved and cannot be used by users. Note 2: Write 0 to the bit 0 after reset.

X : Undefined

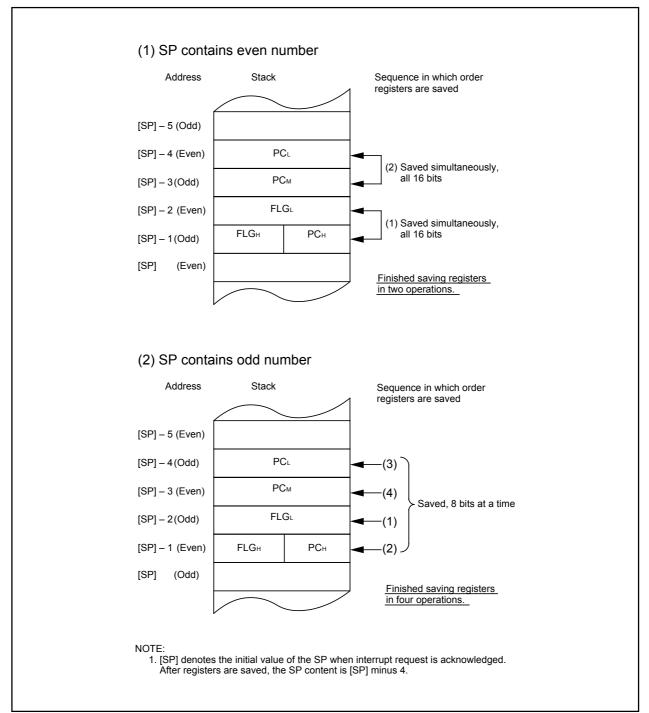

The operation of saving registers carried out in the interrupt sequence is dependent on whether the  $SP^{(1)}$ , at the time of acceptance of an interrupt request, is even or odd. If the stack pointer <sup>(1)</sup> is even, the FLG register and the PC are saved, 16 bits at a time. If odd, they are saved in two steps, 8 bits at a time. **Figure 9.8** shows the operation of the saving registers.

NOTE:

1. When any INT instruction in software numbers 32 to 63 has been executed, this is the SP indicated by the U flag. Otherwise, it is the ISP.

Figure 9.8 Operation of Saving Register

3. When the two-phase pulse signal processing function is not used, set the corresponding bit to 0.

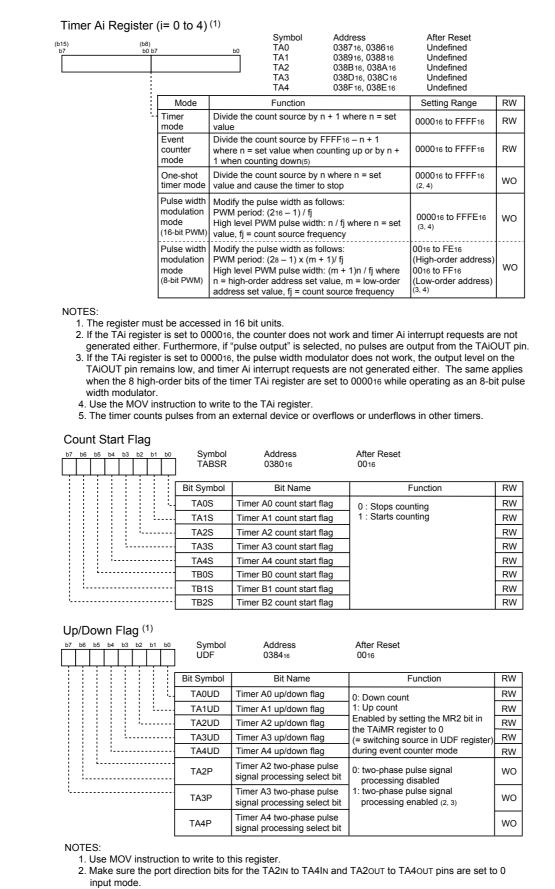

### Figure 12.5 TA0 to TA4 Registers, TABSR Register, and UDF Register

RENESAS

# 12.2.2 Event Counter Mode

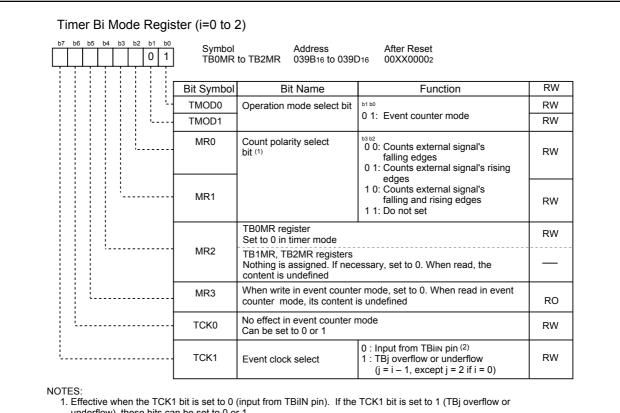

In event counter mode, the timer counts pulses from an external device or overflows and underflows of other timers (see Table 12.7). Figure 12.19 shows the TBiMR register in event counter mode.

| Item                                | Specification                                                                    |

|-------------------------------------|----------------------------------------------------------------------------------|

|                                     | •                                                                                |

| Count source                        | • External signals input to TBiIN pin (i=0 to 2) (effective edge can be selected |

|                                     | in program)                                                                      |

|                                     | <ul> <li>Timer Bj overflow or underflow (j=i-1, except j=2 if i=0)</li> </ul>    |

| Count operation                     | Decrement                                                                        |

|                                     | When the timer underflows, it reloads the reload register contents and           |

|                                     | continues counting                                                               |

| Divide ratio                        | 1/(n+1) n: set value of TBi register 000016 to FFFF16                            |

| Count start condition               | Set TBiS bit <sup>(1)</sup> to 1 (start counting)                                |

| Count stop condition                | Set TBiS bit to 0 (stop counting)                                                |

| Interrupt request generation timing | Timer underflow                                                                  |

| TBilN pin function                  | Count source input                                                               |

| Read from timer                     | Count value can be read by reading TBi register                                  |

| Write to timer                      | When not counting and until the 1st count source is input after counting start   |

|                                     | Value written to TBi register is written to both reload register and counter     |

|                                     | <ul> <li>When counting (after 1st count source input)</li> </ul>                 |

|                                     | Value written to TBi register is written to only reload register                 |

|                                     | (Transferred to counter when reloaded next)                                      |

Table 12.7 Specifications in Event Counter Mode

NOTE:

1. Bits TB2S to TB0S are assigned to the bit 7 to bit 5 in the TABSR register.

underflow), these bits can be set to 0 or 1

2. The port direction bit for the TBilN pin must be set to 0 (= input mode).

### Figure 12.19 TBiMR Register in Event Counter Mode

# 12.3.1 Position-Data-Retain Function

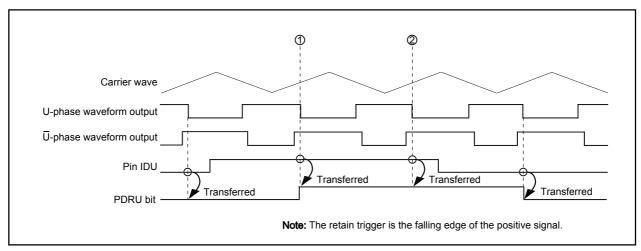

This function is used to retain the position data synchronously with the three-phase waveform output. There are three position-data input pins for U, V, and W phases.

A trigger to retain the position data (hereafter, this trigger is referred to as "retain trigger") can be selected by the PDRT bit in the PDRF register. This bit selects the retain trigger to be the falling edge of each positive phase, or the rising edge of each positive phase.

### 12.3.1.1 Operation of the Position-data-retain Function

**Figure 12.35** shows a usage example of the position-data-retain function (U phase) when the retain trigger is selected as the falling edge of the positive signal.

- (1) At the falling edge of the U-phase waveform ouput, the state at pin IDU is transferred to the PDRU bit in the PDRF register.

- (2) Until the next falling edge of the Uphase waveform output, the above value is retained.

Figure 12.35 Usage Example of Position-data-retain Function (U phase )

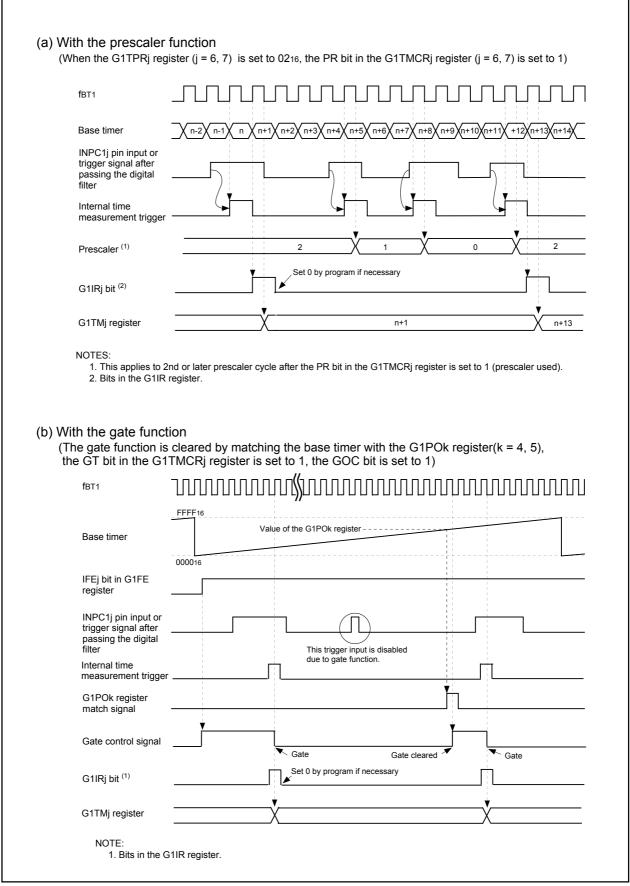

Figure 13.21 Prescaler Function and Gate Function

# 13.5.3 Set/Reset Waveform Output (SR Waveform Output) Mode

Output signal level of the OUTC1j pin becomes high ("H") when the INV bit in the G1POCRi (i=0 to 7) is set to 0 (output is not reversed) and the base timer value matches the G1POj register value (j=0, 2, 4, 6). The "H" signal switches to a low-level ("L") signal when the base timer value matches the G1POk (k=j+1) register value. **Table 13.10** lists specifications of SR waveform mode. **Figure 13.24** shows an example of the SR waveform mode operation.

| Item                            | Specification                                                                                          |

|---------------------------------|--------------------------------------------------------------------------------------------------------|

| Output waveform                 | Free-running operation                                                                                 |

|                                 | (the RST1, RTS2, and RST4 bits of the G1BCR1 and G1BCR0 registers are set                              |

|                                 | to 0 (no reset))                                                                                       |

|                                 | Cycle <u>: 65536</u><br>fBT1                                                                           |

|                                 | Inverse level width <sup>(1)</sup> :                                                                   |

|                                 | • The base timer is cleared to 000016 by matching the base timer with either                           |

|                                 | following register                                                                                     |

|                                 | (a) G1PO0 register (enabled by setting RST1 bit to 1, and bits RST4 and RST2 to 0) <sup>(2)</sup> , or |

|                                 | (b) G1BTRR register (enabled by setting RST4 bit to 1, and bits RST2 and RST1 to 0)                    |

|                                 | Cycle :                                                                                                |

|                                 | Inverse level width <sup>(1)</sup> :fBT1                                                               |

|                                 | m : setting value of the G1POj register(j=0, 2, 4, 6 )                                                 |

|                                 | n : setting value of the G1POk register (k=j+1)                                                        |

|                                 | p : setting value of the G1PO0 register or G1BTRR register                                             |

|                                 | value range of m, n, p: 000116 to FFFD16                                                               |

| Waveform output start condition | Bits IFEj and IFEk in the G1FE register is set to 1 (channel j function enabled)                       |

| Waveform output stop condition  | Bits IFEj and IFEk are set to 0 (channel j function disabled)                                          |

| Interrupt request               | The G1IRj bit in the G1IR register is set to 1 when the base timer value                               |

|                                 | matches the G1POj register value.                                                                      |

|                                 | The G1IRk bit in the interrupt request register is set to 1 when the base timer                        |

|                                 | value matches the G1POk register value (See Figure 13.24)                                              |

| OUTC1j pin <sup>(3)</sup>       | Pulse signal output pin                                                                                |

| Selectable function             | Default value set function : Set starting waveform output level                                        |

|                                 | Inverse output function: Waveform output signal is inversed and provided                               |

|                                 | from the OUTC1j pin                                                                                    |

NOTES:

- 1. The odd channel's waveform generating register must have greater value than the even channel's.

- 2. When the G1PO0 register resets the base timer, the channel 0 and channel 1 SR waveform generating functions are not available.

- 3. Pins OUTC10, OUTC12, OUTC14, OUTC16.

| b7 b6 b5 b4 b<br>0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 3 b2 b1 b0                  |                                                                                      | Symbol Addres<br>U0MR, U1MR 03A016                                                                                                                                                                                                       | s After Reset<br>6, 03A816 0016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|----------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                                          |                             | Bit<br>Symbol                                                                        | Bit Name                                                                                                                                                                                                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RV                         |

|                                                          |                             | SMD0                                                                                 | Serial I/O mode select bit                                                                                                                                                                                                               | b2 b1 b0<br>0 0 0 : Serial I/O disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RV                         |

|                                                          |                             | SMD1                                                                                 |                                                                                                                                                                                                                                          | 0 0 1 : Clock synchronous serial I/O mode<br>1 0 0 : UART mode transfer data 7 bit long<br>1 0 1 : UART mode transfer data 8 bit long                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RV                         |

|                                                          |                             | SMD2                                                                                 |                                                                                                                                                                                                                                          | 1 1 0 : UART mode transfer data 9 bit long<br>Do not set the value other than the above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RV                         |

|                                                          |                             | CKDIR                                                                                | Internal/external clock select bit                                                                                                                                                                                                       | 0 : Internal clock<br>1 : External clock <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RV                         |

|                                                          |                             | STPS                                                                                 | Stop bit length select bit                                                                                                                                                                                                               | 0 : One stop bit<br>1 : Two stop bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RV                         |

|                                                          |                             | PRY                                                                                  | Odd/even parity select bit                                                                                                                                                                                                               | Effective when PRYE = 1<br>0 : Odd parity<br>1 : Even parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RV                         |

| L                                                        |                             | PRYE                                                                                 | Parity enable bit                                                                                                                                                                                                                        | 0 : Parity disabled<br>1 : Parity enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RV                         |

|                                                          |                             |                                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| 2. To receiv<br>IART2 Tran                               | e data, set ti              | he corresp                                                                           | Reserve bit<br>ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address                                                                                                                         | Set to 0<br>o 0 (input mode).<br>each RxDi pin to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RV                         |

| 1. Set the co<br>2. To receiv                            | e data, set ti<br>smit/rece | g port dire<br>he corresp                                                            | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register                                                                                                                                                          | Set to 0<br>o 0 (input mode).<br>each RxDi pin to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

| 1. Set the co<br>2. To receiv                            | e data, set ti<br>smit/rece | g port dire<br>he corresp<br>eive Mo<br>Bit                                          | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address<br>U2MR 037816                                                                                                                         | Set to 0<br>D (input mode).<br>each RxDi pin to 0.<br>After Reset<br>0016<br>Function<br>b2 b1 b0<br>0 0 0 : Serial I/O disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                          |

| 1. Set the co<br>2. To receiv                            | e data, set ti<br>smit/rece | g port dire<br>he corresp<br><b>tive Mo</b><br>Bit<br>Symbol                         | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address<br>U2MR 037816<br>Bit Name<br>Serial I/O mode select bit                                                                               | Set to 0 Set to 0 O (input mode). each RxDi pin to 0. After Reset 0016 Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R\                         |

| 1. Set the co<br>2. To receiv                            | e data, set ti<br>smit/rece | port dire<br>he corresp<br><b>tive Mo</b><br>Bit<br>Symbol<br>SMD0                   | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address<br>U2MR 037816<br>Bit Name<br>Serial I/O mode select bit                                                                               | Set to 0<br>D (input mode).<br>each RxDi pin to 0.<br>After Reset<br>0016<br>Function<br><sup>b2b1b0</sup><br>0 0 0 : Serial I/O disabled<br>0 0 1 : Clock synchronous serial I/O mode<br>0 1 0 : I <sup>2</sup> C bus mode(3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RV<br>RV<br>R\<br>R\<br>R\ |

| 1. Set the co<br>2. To receiv                            | e data, set ti<br>smit/rece | port dire<br>he corresp<br>ive Mo<br>Bit<br>Symbol<br>SMD0<br>SMD1                   | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address<br>U2MR 037816<br>Bit Name<br>Serial I/O mode select bit                                                                               | Set to 0 Set to 0 O (input mode). each RxDi pin to 0. After Reset 0016 Function b2b1b0 0 0 0 : Serial I/O disabled 0 0 1 : Clock synchronous serial I/O mode 0 1 0 : I/2C bus mode(3) 1 0 0 : UART mode transfer data 7 bit long 1 0 1 : UART mode transfer data 8 bit long 1 1 0 : UART mode transfer data 9 bits long 1 0 : UART mode transfer data 9 bits long                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R\<br>R\<br>R\<br>R\       |

| 1. Set the co<br>2. To receiv                            | re data, set ti             | g port dire<br>he corresp<br>sive Mo<br>Bit<br>Symbol<br>SMD0<br>SMD1<br>SMD2        | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address<br>U2MR 037816<br>Bit Name<br>Serial I/O mode select bit<br>(2)<br>Internal/external clock                                             | Set to 0 Set to 0 O (input mode). each RxDi pin to 0. After Reset 0016 Function b2b1b0 0 0 0 : Serial I/O disabled 0 0 1 : Clock synchronous serial I/O mode 0 1 0 : I <sup>2</sup> C bus mode(3) 1 0 0 : UART mode transfer data 7 bit long 1 0 1 : UART mode transfer data 8 bit long 1 1 0 : UART mode transfer data 9 bits long Do not set the value other than the above 0 : Internal clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R\<br>R\<br>R\<br>R\<br>R\ |

| 1. Set the co<br>2. To receiv                            | re data, set ti             | port dire<br>he corresp<br>eive Mo<br>Bit<br>Symbol<br>SMD0<br>SMD1<br>SMD2<br>CKDIR | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address<br>U2MR 037816<br>Bit Name<br>Serial I/O mode select bit<br>(2)<br>Internal/external clock<br>select bit                               | Set to 0 Set to 0 O (input mode). each RxDi pin to 0. After Reset 0016 Function b2b1b0 0 0 : Serial I/O disabled 0 0 1 : Clock synchronous serial I/O mode 0 1 0 : I/2C bus mode(3) 1 0 0 : UART mode transfer data 7 bit long 1 0 1 : UART mode transfer data 8 bit long 1 1 0 : UART mode transfer data 8 bit long 1 1 0 : UART mode transfer data 8 bit long Do not set the value other than the above 0 : Internal clock 1 : External clock (1) 0 : One stop bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R)<br>R)<br>R)             |

| 1. Set the co<br>2. To receiv                            | re data, set ti             | sive Mo<br>Bit<br>Symbol<br>SMD1<br>SMD2<br>CKDIR<br>STPS                            | ction bit for each CLKi pin to<br>bonding port direction bit for<br>de Register<br>Symbol Address<br>U2MR 037816<br>Bit Name<br>Serial I/O mode select bit<br>(2)<br>Internal/external clock<br>select bit<br>Stop bit length select bit | Set to 0 Set |                            |

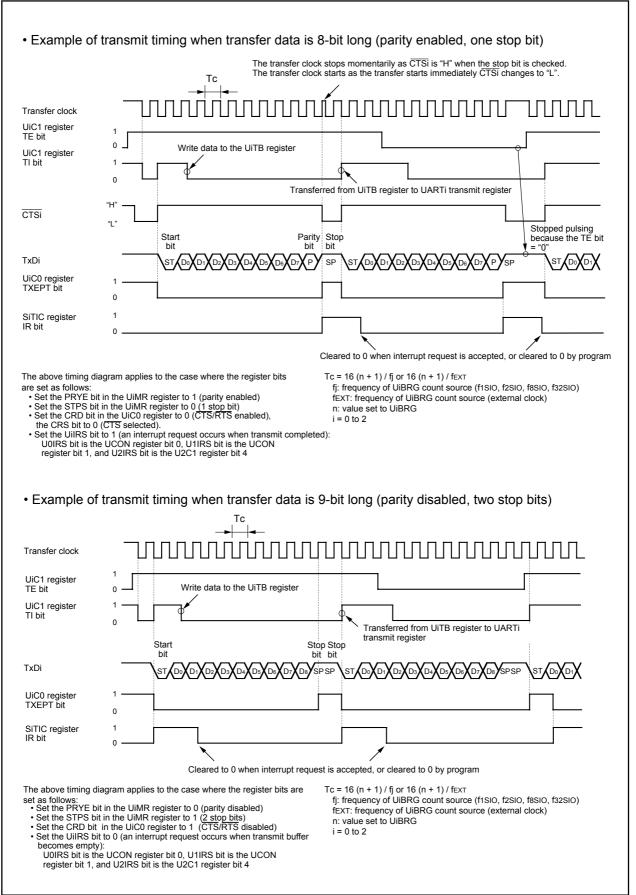

Figure 14.5 U0MR to U2MR Registers

Figure 14.16 Typical transmit timing in UART mode (UART0, UART1)

RENESAS

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Symbol<br>ADTRG | Address<br>CON 03D216                                   | After Reset<br>0016                                         |    |

|-------------------------------------------------------|-----------------|---------------------------------------------------------|-------------------------------------------------------------|----|

|                                                       | Bit Symbol      | Bit Name                                                | Function                                                    | RW |

|                                                       | SSE             | A/D operation mode select bit 2                         | Simultaneous sample sweep mode or delayed trigger mode 0, 1 | RW |

| · · · · ·                                             | DTE             | A/D operation mode select bit 3                         | Delayed trigger mode 0, 1                                   | RW |

|                                                       | HPTRG0          | AN0 trigger select bit                                  | See Table 15.13                                             | RW |

|                                                       | HPTRG1          | AN1 trigger select bit                                  | See Table 15.13                                             | RW |

|                                                       | (b7-b4)         | Nothing is assigned. If nec When read, the content is 0 |                                                             | -  |

Figure 15.28 ADTRGCON Register in Delayed Trigger Mode 1

## Table 15.13 Trigger Select Bit Setting in Delayed Trigger Mode 1

| TRG | TRG1 | HPTRG0 | HPTRG1 | Trigger |

|-----|------|--------|--------|---------|

| 0   | 1    | 0      | 0      | ADTRG   |

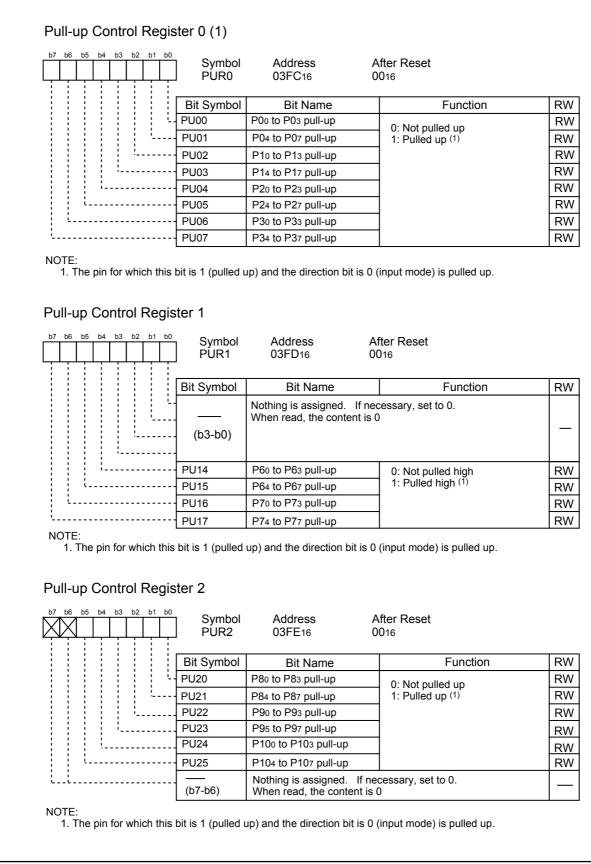

Figure 19.8 PUR0 to PUR2 Registers

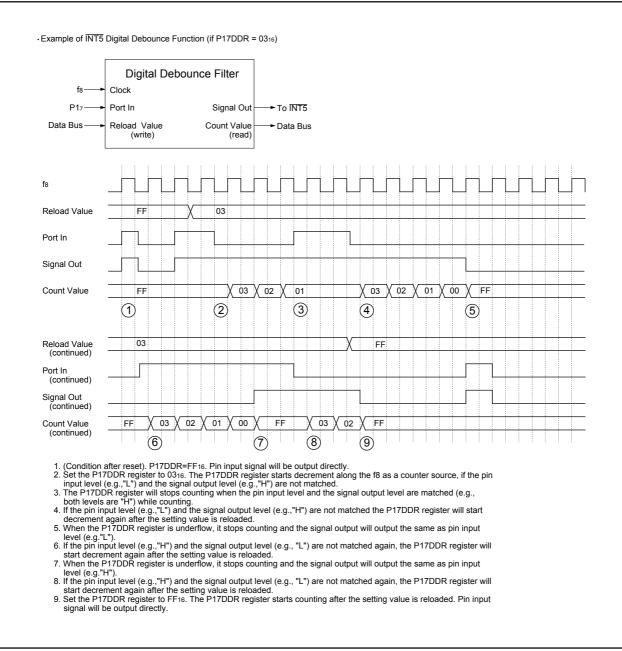

Figure 19.12 Functioning of Digital Debounce Filter

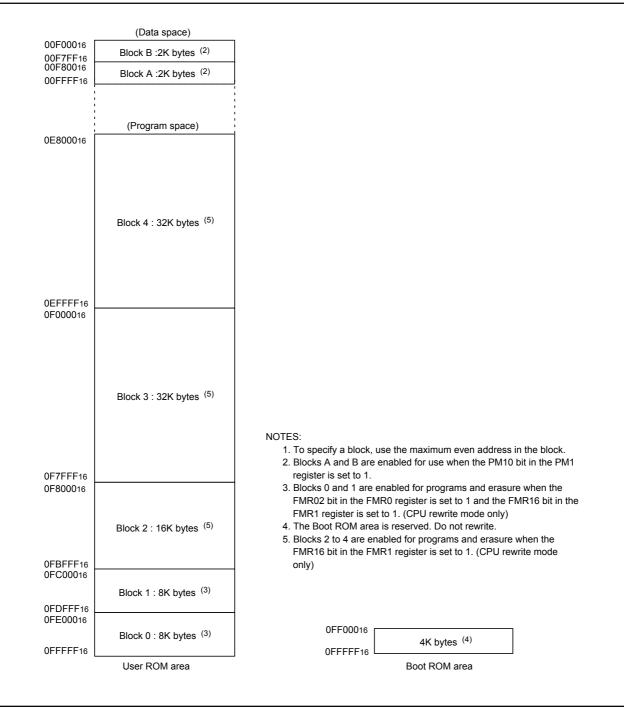

Figure 20.2 Flash Memory Block Diagram (ROM capacity 96 Kbytes)

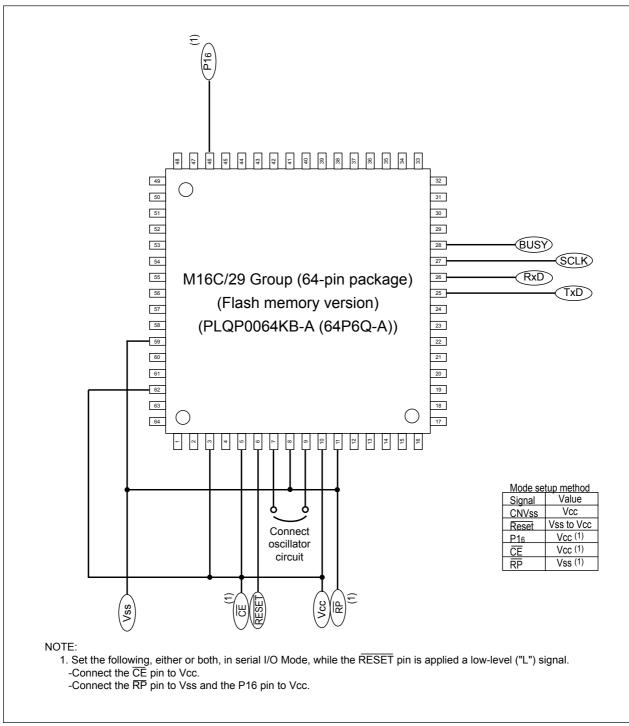

Figure 20.15 Pin Connections for Serial I/O Mode (1)

### **Timing Requirements**

# Vcc = 5V

## (VCC = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 21.11 | Timer A Input (Counter Input in Event Counter Mode) |

|-------------|-----------------------------------------------------|

|-------------|-----------------------------------------------------|

| Cumbol  | Derewster                   | Standard |      | Unit |

|---------|-----------------------------|----------|------|------|

| Symbol  | Parameter                   |          | Max. |      |

| tc(TA)  | TAin input cycle time       | 100      |      | ns   |

| tw(TAH) | TAin input HIGH pulse width | 40       |      | ns   |

| tw(TAL) | TAin input LOW pulse width  | 40       |      | ns   |

### Table 21.12 Timer A Input (Gating Input in Timer Mode)

| Ormahad | Parameter                    |     | Standard |      |

|---------|------------------------------|-----|----------|------|

| Symbol  |                              |     | Max.     | Unit |

| tc(TA)  | TAilN input cycle time       |     |          | ns   |

| tw(TAH) | TAilN input HIGH pulse width |     |          | ns   |

| tw(TAL) | TAin input LOW pulse width   | 200 |          | ns   |

### Table 21.13 Timer A Input (External Trigger Input in One-shot Timer Mode)

| Symbol  | Parameter                        | Stan | dard | Unit |

|---------|----------------------------------|------|------|------|

| Symbol  | Falameter                        | Min. | Max. | Unit |

| tc(TA)  | 200                              |      | ns   |      |

| tw(TAH) | TAil input HIGH pulse width      | 100  |      | ns   |

| tw(TAL) | (TAL) TAin input LOW pulse width |      |      | ns   |

### Table 21.14 Timer A Input (External Trigger Input in Pulse Width Modulation Mode)

| Cumhal  | Parameter                   | Standard |      | Linit      |

|---------|-----------------------------|----------|------|------------|

| Symbol  | Parameter                   | Min.     | Max. | Unit<br>ns |

| tw(TAH) | TAin input HIGH pulse width | 100      |      | ns         |

| tw(TAL) | TAin input LOW pulse width  | 100      |      | ns         |

### Table 21.15 Timer A Input (Counter Increment/decrement Input in Event Counter Mode)

| C: make al  | Deverator                    | Star | 11-14 |      |