#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | -                                                                                |

| Core Size                  | -                                                                                |

| Speed                      | -                                                                                |

| Connectivity               | -                                                                                |

| Peripherals                | -                                                                                |

| Number of I/O              | -                                                                                |

| Program Memory Size        | -                                                                                |

| Program Memory Type        | -                                                                                |

| EEPROM Size                | -                                                                                |

| RAM Size                   | -                                                                                |

| Voltage - Supply (Vcc/Vdd) | -                                                                                |

| Data Converters            | -                                                                                |

| Oscillator Type            | -                                                                                |

| Operating Temperature      | -                                                                                |

| Mounting Type              | -                                                                                |

| Package / Case             | -                                                                                |

| Supplier Device Package    | -                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fcthp-u3a |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3. Register Notation

The symbols and terms used in register diagrams are described below.

| b b5 b4 b3 b2 b1 b0 | F          | Symbol<br>XXX                                  | Address<br>XXX                           | After Reset<br>0016        |    |

|---------------------|------------|------------------------------------------------|------------------------------------------|----------------------------|----|

|                     | Bit Symbol | Bit Name                                       |                                          | Function                   | RW |

|                     | XXX0       | XXX bits                                       | <sup>b1 b0</sup><br>1 0: XXX<br>0 1: XXX |                            | RW |

|                     | XXX1       |                                                | 1 0: Do not set.<br>1 1: XXX             |                            | RW |

|                     | (b2)       | Nothing is assigned. I<br>When read, the conte | f necessary, set to nt is undefined.     | 0.                         | _  |

|                     | (b3)       | Reserved bits                                  | Set to 0.                                |                            | RW |

|                     | XXX4       | XXX bits                                       | Function varies a mode.                  | according to the operating | RW |

| l                   | XXX5       |                                                |                                          |                            | wo |

|                     | XXX6       |                                                |                                          |                            | RW |

|                     | XXX7       | XXX bit                                        | 0: XXX<br>1: XXX                         |                            | RO |

\*1

Blank: Set to 0 or 1 according to the application.0: Set to 0.1: Set to 1.X: Nothing is assigned.

\*2

RW: Read and write. RO: Read only. WO: Write only. -: Nothing is assigned.

\*3

• Reserved bit

Reserved bit. Set to specified value.

\*4

• Nothing is assigned

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information on the individual modes.

# Table of Contents

| Quick Reference to Pages Classified by Address                 | B-1 |

|----------------------------------------------------------------|-----|

| 1. Overview                                                    | 1   |

| 1.1 Features                                                   |     |

| 1.1.1 Applications                                             | 1   |

| 1.1.2 Specifications                                           | 2   |

| 1.2 Block Diagram                                              | 4   |

| 1.3 Product List                                               |     |

| 1.4 Pin Assignments                                            | 12  |

| 1.5 Pin Description                                            |     |

| 2. Central Processing Unit (CPU)                               | 21  |

| 2.1 Data Registers (R0, R1, R2 and R3)                         | 21  |

| 2.2 Address Registers (A0 and A1)                              | 21  |

| 2.3 Frame Base Register (FB)                                   | 22  |

| 2.4 Interrupt Table Register (INTB)                            | 22  |

| 2.5 Program Counter (PC)                                       | 22  |

| 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) | 22  |

| 2.7 Static Base Register (SB)                                  | 22  |

| 2.8 Flag Register (FLG)                                        | 22  |

| 2.8.1 Carry Flag (C Flag)                                      | 22  |

| 2.8.2 Debug Flag (D Flag)                                      | 22  |

| 2.8.3 Zero Flag (Z Flag)                                       |     |

| 2.8.4 Sign Flag (S Flag)                                       | 22  |

| 2.8.5 Register Bank Select Flag (B Flag)                       | 22  |

| 2.8.6 Overflow Flag (O Flag)                                   | 22  |

| 2.8.7 Interrupt Enable Flag (I Flag)                           | 22  |

| 2.8.8 Stack Pointer Select Flag (U Flag)                       | 22  |

| 2.8.9 Processor Interrupt Priority Level (IPL)                 | 22  |

| 2.8.10 Reserved Area                                           | 22  |

| 3. Memory                                                      | 23  |

| 4. Special Function Registers (SFRs)                           | 24  |

| Pin<br>No. | Control<br>Pin | Port | Interrupt<br>Pin | Timer Pin  | Timer S Pin     | UART/CAN Pin                                | Mult-master<br>I <sup>2</sup> C bus Pin | Analog Pin |

|------------|----------------|------|------------------|------------|-----------------|---------------------------------------------|-----------------------------------------|------------|

| 1          |                | P91  |                  | TB1IN      |                 |                                             |                                         | AN31       |

| 2          | CLKOUT         | P90  |                  | TBOIN      |                 |                                             |                                         | AN30       |

| 3          | CNVss          |      |                  |            |                 |                                             |                                         |            |

| 4          | XCIN           | P87  |                  |            |                 |                                             |                                         |            |

| 5          | Хсоит          | P86  |                  |            |                 |                                             |                                         |            |

| 6          | RESET          |      |                  |            |                 |                                             |                                         |            |

| 7          | Xout           |      |                  |            |                 |                                             |                                         |            |

| 8          | Vss            |      |                  |            |                 |                                             |                                         |            |

| 9          | XIN            |      |                  |            |                 |                                             |                                         |            |

| 10         | Vcc            |      |                  |            |                 |                                             |                                         |            |

| 11         |                | P85  | NMI              | SD         |                 |                                             |                                         |            |

| 12         |                | P84  | INT <sub>2</sub> | ZP         |                 |                                             |                                         |            |

| 13         |                | P83  | INT1             |            |                 |                                             |                                         |            |

| 14         |                | P82  | INT <sub>0</sub> |            |                 |                                             |                                         |            |

| 15         |                | P81  |                  | TA4IN / Ū  |                 |                                             |                                         |            |

| 16         |                | P80  |                  | ТА40UT / U |                 |                                             |                                         |            |

| 17         |                | P77  |                  | ΤΑ3ΙΝ      |                 |                                             |                                         |            |

| 18         |                | P76  |                  | ТАзоит     |                 |                                             |                                         |            |

| 19         |                | P75  |                  | TA2IN / W  |                 |                                             |                                         |            |

| 20         |                | P74  |                  | ТА20UT / W |                 |                                             |                                         |            |

| 21         |                | P73  |                  | TA1IN / V  |                 | CTS2 / RTS2 / TXD1                          |                                         |            |

| 22         |                | P72  |                  | TA10UT / V |                 | CLK2 / RxD1                                 |                                         |            |

| 23         | _              | P71  |                  | TAOIN      |                 | RxD2 / SCL2 / CLK1                          |                                         |            |

| 24         |                | P70  |                  | ΤΑοουτ     |                 | TxD2 / SDA2 / RTS1 /<br>CTS1 / CTS0 / CLKS1 |                                         |            |

| 25         |                | P67  |                  |            |                 | TxD1                                        |                                         |            |

| 26         |                | P66  |                  |            |                 | RxD1                                        |                                         |            |

| 27         |                | P65  |                  |            |                 | CLK1                                        |                                         |            |

| 28         |                | P64  |                  |            |                 | RTS1 / CTS1/ CTS0 /<br>CLKS1                |                                         |            |

| 29         |                | P33  |                  |            |                 |                                             |                                         |            |

| 30         |                | P32  |                  |            |                 | Sout3                                       |                                         |            |

| 31         |                | P31  |                  |            |                 | SIN3                                        |                                         |            |

| 32         |                | P30  |                  |            |                 | CLK3                                        |                                         |            |

| 33         |                | P63  |                  |            |                 | TxD0                                        |                                         |            |

| 34         |                | P62  |                  |            |                 | RxD0                                        |                                         |            |

| 35         |                | P61  |                  |            |                 | CLK0                                        |                                         |            |

| 36         |                | P60  |                  |            |                 | RTS0 / CTS0                                 |                                         |            |

| 37         |                | P27  |                  |            | OUTC17 / INPC17 |                                             |                                         |            |

| 38         |                | P26  |                  |            | OUTC16 / INPC16 |                                             |                                         |            |

| 39         |                | P25  |                  |            | OUTC15 / INPC15 |                                             |                                         |            |

| 40         |                | P24  |                  |            | OUTC14 / INPC14 |                                             |                                         |            |

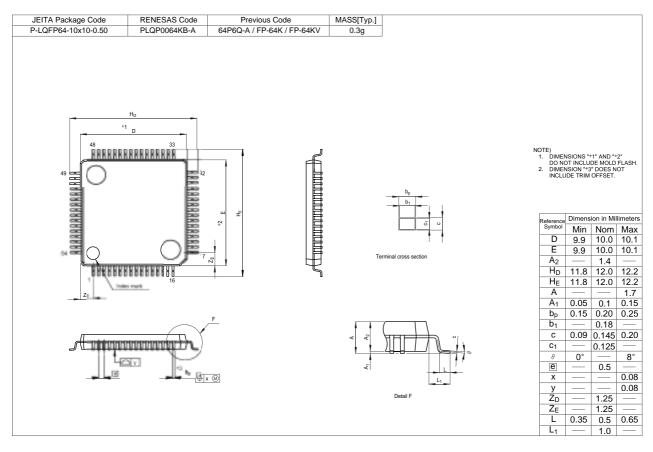

Table 1.13 Pin Characteristics for 64-Pin Package

#### 5.5.2. Limitations on Stop Mode

When all the conditions below are met, the low voltage detection interrupt is generated and the MCU exits stop mode as soon as the CM10 bit in the CM1 register is set to 1 (all clocks stopped).

- the VC27 bit in the VCR2 register is set to 1 (low voltage detection circuit enabled)

- the D40 bit in the D4INT register is set to 1 (low voltage detection interrupt enabled)

- the D41 bit in the D4INT register is set to 1 (low voltage detection interrupt is used to exit stop mode)

- the voltage applied to the VCC pin is higher than Vdet4 (the VC13 bit in the VCR1 register is 1)

Set the CM10 bit to 1 when the VC13 bit is set to set to 0 (Vcc < Vdet4), if the MCU is configured to enter stop mode when voltage applied to the Vcc pin drops Vdet4 or below and to exit stop mode when the voltage applied rises to Vdet4 or above.

#### 5.5.3. Limitations on WAIT Instruction

When all the conditions below are met, the low voltage detection interrupt is generated and the MCU exits wait mode as soon as WAIT instruction is executed.

- the CM02 bit in the CM0 register is set to 1 (stop peripheral function clock)

- the VC27 bit in the VCR2 register is set to 1 (low voltage detection circuit enabled)

- the D40 bit in the D4INT register is set to 1 (low voltage detection interrupt enabled)

- the D41 bit in the D4INT register is set to 1 (low voltage detection interrupt is used to exit wait mode)

- the voltage applied to the Vcc pin is higher than Vdet4 (the VC13 bit in the VCR1 register is 1)

Execute the WAIT instruction when the VC13 bit is set to set to 0 (Vcc < Vdet4), if the MCU is configured to enter wait mode when voltage applied to the Vcc pin drops Vdet4 or below and to exit wait mode when the voltage applied rises to Vdet4 or above.

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbo<br>TA0MF | Address Address R to TA4MR 39616 to        |                                                                                                                                                                |    |

|-------------------------|----------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                         | Bit Symbol     | Bit Name                                   | Function                                                                                                                                                       | RW |

|                         | TMOD0          | Operation mode select bit                  | b1 b0                                                                                                                                                          | RW |

|                         | TMOD1          |                                            | 1 0: One-shot timer mode                                                                                                                                       | RW |

|                         | MR0            | Pulse output function select bit           | <ul> <li>0: Pulse is not output (TAio∪⊤ pin functions<br/>as I/O port)</li> <li>1: Pulse is output (TAio∪⊤ pin functions as a<br/>pulse output pin)</li> </ul> | RW |

|                         | MR1            | External trigger select bit <sup>(1)</sup> | 0: Falling edge of input signal to TAilN pin <sup>(2)</sup><br>1: Rising edge of input signal to TAilN pin <sup>(2)</sup>                                      | RW |

|                         | MR2            | Trigger select bit                         | 0: TAiOS bit is enabled<br>1: Selected by bits TAiTGH to TAiTGL                                                                                                | RW |

|                         | MR3            | Set to 0 in one-shot timer m               | ode                                                                                                                                                            | RW |

|                         | TCK0           | . Count source select bit                  | <sup>b7 b6</sup><br>О О: f1 or f2<br>О 1: f8                                                                                                                   | RW |

|                         | TCK1           |                                            | 1 0: f32<br>1 1: fC32                                                                                                                                          | RW |

Figure 12.11 TAIMR Register in One-shot Timer Mode

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbol<br>TB0MR | Address<br>to TB1MR 039B16 to                                          | After Reset<br>039C16 00XX00002                 |    |

|-------------------------|-----------------|------------------------------------------------------------------------|-------------------------------------------------|----|

|                         | Bit Symbol      | Bit Name                                                               | Function                                        | RW |

|                         | TMOD0           | Operation mode select bit                                              | 0 0: Timer mode or A/D trigger mode             | RW |

|                         | TMOD1           |                                                                        | 0 0. Timer mode of A/D trigger mode             | RW |

|                         | MR0             | Invalid in A/D trigger mode                                            |                                                 | RW |

|                         | MR1             | Either 0 or 1 is enabled                                               |                                                 | RW |

|                         | MR2             | TB0MR register<br>Set to 0 in A/D trigger mode                         | e                                               | RV |

|                         |                 | TB1MR register<br>Nothing is assigned. If nece<br>content is undefined | essary, set to 0. When read, its                |    |

|                         | MR3             | When write in A/D trigger m mode, its content is undefir               | node, set to 0. When read in A/D trigger<br>ned | RO |

| ·                       | TCK0            | Count source select bit <sup>(1)</sup>                                 | <sup>b7 b6</sup><br>О О: f1 or f2<br>О 1: f8    | RW |

|                         | TCK1            |                                                                        | 1 0: f32<br>1 1: fC32                           | RW |

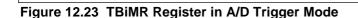

#### Figure 12.24 TB2SC Register in A/D Trigger Mode

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Symbol<br>TB2SC | Address<br>039E16                                        | After Reset<br>X00000002                                                                                                                                                                            |    |

|-------------------------------------------------------|-----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                       | Bit Symbol      | Bit Name                                                 | Function                                                                                                                                                                                            | RW |

|                                                       | PWCON           | Timer B2 reload timing switch bit (2)                    | 0: Timer B2 underflow<br>1: Timer A output at odd-numbered                                                                                                                                          | RW |

|                                                       | IVPCR1          | Three-phase output port<br>SD control bit 1<br>(3, 4, 7) | <ul> <li>0: Three-phase output forcible cutoff by SD pin input<br/>(high impedance) disabled</li> <li>1: Three-phase output forcible cutoff by SD pin input<br/>(high impedance) enabled</li> </ul> | RW |

|                                                       | TB0EN           | Timer B0 operation mode select bit                       | 0: Other than A/D trigger mode<br>1: A/D trigger mode (5)                                                                                                                                           | RW |

| · · · · · · · · · · · · · · · · · · ·                 | TB1EN           | Timer B1 operation mode select bit                       | 0: Other than A/D trigger mode<br>1: A/D trigger mode (5)                                                                                                                                           | RW |

|                                                       | TB2SEL          | Trigger select bit (6)                                   | 0: TB2 interrupt<br>1: Underflow of TB2 interrupt<br>generation frequency setting counter [ICTB2]                                                                                                   | RW |

| (b6-b5)                                               |                 | Reserved bits                                            | Set to 0                                                                                                                                                                                            | RW |

| L                                                     | (b7)            | Nothing is assigned. If ne<br>When read, the content is  |                                                                                                                                                                                                     | —  |

1. Write to this register after setting the PRC1 bit in the PRCR register to 1 (write enabled).

2. If the INV11 bit is 0 (three-phase mode 0) or the INV06 bit is 1 (triangular wave modulation mode), set this bit to 0 (timer B2 underflow).

3. When setting the IVPCR1 bit to 1 (three-phase output forcible cutoff by SD pin input enabled), Set the PD85 bit to 0 (= input mode).

4. Related pins are U(P8<sub>0</sub>), U(P8<sub>1</sub>), V(P7<sub>2</sub>), V(P7<sub>3</sub>), W(P7<sub>4</sub>), W(P7<sub>5</sub>). When a high-level ("H") signal is applied to the SD pin and set the IVPCR1 bit to 0 after forcible cutoff, pins U, U, V, V, w, and W are exit from the high-impedance state. If a lowlevel ("L") signal is applied to the  $\overline{SD}$  pin, three-phase motor control timer output will be disabled (INV03=0). At this time, when the IVPCR1 bit is 0, pins U, U, V, W, and W become programmable I/O ports. When the IVPCR1 bit is set to 1, pins U, U, V, V, W, and W are placed in a high-impedance state regardless of which function of those pins is used.

5. When this bit is used in delayed trigger mode 0, set bits TB0EN and TB1EN to 1 (A/D trigger mode).

6. When setting the TB2SEL bit to 1 (underflow of TB2 interrupt generation frequency setting counter[ICTB2]), set the INV02 bit to 1 (three-phase motor control timer function).

7. Refer to "19.6 Digital Debounce Function" for the SD input.

The effect of SD pin input is below.

| 1.Case of INV03 = 1(Three-phase motor control timer output enabled) |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| SD pin inputs <sup>(3)</sup> | Status of U/V/W pins             | Remarks                                                                                                        |

|------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|

| Н                            | Three-phase PWM output           |                                                                                                                |

| L <sup>(1)</sup>             | High impedance <sup>(4)</sup>    | Three-phase output<br>forcrible cutoff                                                                         |

| Н                            | Three-phase PWM output           |                                                                                                                |

| L <sup>(1)</sup>             | Input/output port <sup>(2)</sup> |                                                                                                                |

|                              | H<br>L <sup>(1)</sup>            | H     Three-phase PWM output       L <sup>(1)</sup> High impedance <sup>(4)</sup> H     Three-phase PWM output |

NOTES:

1. When "L" is applied to the SD pin, INV03 bit is changed to 0 at the same time.

2. The value of the port register and the port direction register becomes effective.

3. When SD function is not used, set to 0 (Input) in PD85 and pullup to "H" in SD pin from outside.

4. To leave the high-impedance state and restart the three-phase PWM signal output after the three-phase PWM signal output forced cutoff, set the IVPCR1 bit to 0 after the SD pin input level becomes high ("H").

2 Case of INV03 = 0 (Three-phase motor control timer output disabled)

| IVPCR1 bit                | $\overline{\text{SD}}$ pin inputs | Status of U/V/W pins                            | Remarks                                               |  |  |  |  |

|---------------------------|-----------------------------------|-------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| 1<br>(Three-phase output  | Н                                 | Peripheral input/output<br>or input/output port |                                                       |  |  |  |  |

| forcrible cutoff enable)  | L                                 | High impedance                                  | Three-phase output<br>forcrible cutoff <sup>(1)</sup> |  |  |  |  |

| 0<br>(Three-phase output  | Н                                 | Peripheral input/output<br>or input/output port |                                                       |  |  |  |  |

| forcrible cutoff disable) | L                                 | Peripheral input/output<br>or input/output port |                                                       |  |  |  |  |

NOTE:

1. The three-phase output forcrible cutoff function becomes effective if the INPCR1 bit is set to 1 (three-phase output forcrible cutoff function enable) even when the INV03 bit is 0 (three-phase motor control timer output disalbe)

#### Figure 12.30 TB2SC Register

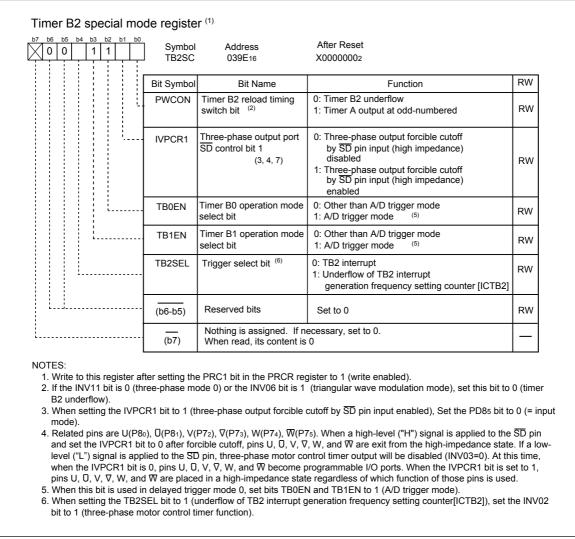

Figure 13.14 Base Timer Operation in Two-phase Pulse Signal Processing Mode

RENESAS

| Register            | Bit                              | Func                                                                                                                                                                                                                                                                                                                         | ction                                                                                                                                                                                                                                                                                |  |  |

|---------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                     |                                  | Master                                                                                                                                                                                                                                                                                                                       | Slave                                                                                                                                                                                                                                                                                |  |  |

| U2TB                | 0 to 7                           | Set transmission data                                                                                                                                                                                                                                                                                                        | Set transmission data                                                                                                                                                                                                                                                                |  |  |

| U2RB <sup>(1)</sup> | 0 to 7                           | Reception data can be read                                                                                                                                                                                                                                                                                                   | Reception data can be read                                                                                                                                                                                                                                                           |  |  |

|                     | 8                                | ACK or NACK is set in this bit                                                                                                                                                                                                                                                                                               | ACK or NACK is set in this bit                                                                                                                                                                                                                                                       |  |  |

|                     | ABT                              | Arbitration lost detection flag                                                                                                                                                                                                                                                                                              | Invalid                                                                                                                                                                                                                                                                              |  |  |

|                     | OER                              | Overrun error flag                                                                                                                                                                                                                                                                                                           | Overrun error flag                                                                                                                                                                                                                                                                   |  |  |

| U2BRG               | 0 to 7                           | Set bit rate                                                                                                                                                                                                                                                                                                                 | Invalid                                                                                                                                                                                                                                                                              |  |  |

| U2MR <sup>(1)</sup> | SMD2 to SMD0                     | Set to 0102                                                                                                                                                                                                                                                                                                                  | Set to 0102                                                                                                                                                                                                                                                                          |  |  |

|                     | CKDIR                            | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |  |  |

|                     | IOPOL                            | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |  |  |

| U2C0                | CLK1, CLK0                       | Select the count source for the U2BRG register                                                                                                                                                                                                                                                                               | Invalid                                                                                                                                                                                                                                                                              |  |  |

|                     | CRS                              | Invalid because CRD = 1                                                                                                                                                                                                                                                                                                      | Invalid because CRD = 1                                                                                                                                                                                                                                                              |  |  |

|                     | TXEPT                            | Transmit buffer empty flag                                                                                                                                                                                                                                                                                                   | Transmit buffer empty flag                                                                                                                                                                                                                                                           |  |  |

|                     | CRD                              | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |  |  |

|                     | NCH                              | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |  |  |

|                     | CKPOL                            | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |  |  |

|                     | UFORM                            | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |  |  |

| U2C1                | TE                               | Set this bit to 1 to enable transmission                                                                                                                                                                                                                                                                                     | Set this bit to 1 to enable transmission                                                                                                                                                                                                                                             |  |  |

|                     | ТІ                               | Transmit buffer empty flag                                                                                                                                                                                                                                                                                                   | Transmit buffer empty flag                                                                                                                                                                                                                                                           |  |  |

|                     | RE                               | Set this bit to 1 to enable reception                                                                                                                                                                                                                                                                                        | Set this bit to 1 to enable reception                                                                                                                                                                                                                                                |  |  |

|                     | RI                               | Reception complete flag                                                                                                                                                                                                                                                                                                      | Reception complete flag                                                                                                                                                                                                                                                              |  |  |

|                     | U2IRS                            | Invalid                                                                                                                                                                                                                                                                                                                      | Invalid                                                                                                                                                                                                                                                                              |  |  |

|                     | U2RRM,<br>U2LCH, U2ERE           | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |  |  |

| U2SMR               | IICM                             | Set to 1                                                                                                                                                                                                                                                                                                                     | Set to 1                                                                                                                                                                                                                                                                             |  |  |

|                     | ABC                              | Select the timing at which arbitration-lost is detected                                                                                                                                                                                                                                                                      | Invalid                                                                                                                                                                                                                                                                              |  |  |

|                     | BBS                              | Bus busy flag                                                                                                                                                                                                                                                                                                                | Bus busy flag                                                                                                                                                                                                                                                                        |  |  |

|                     | 3 to 7                           | Set to 0                                                                                                                                                                                                                                                                                                                     | Set to 0                                                                                                                                                                                                                                                                             |  |  |

| U2SMR2              | IICM2                            | Refer to Table 14.13                                                                                                                                                                                                                                                                                                         | Refer to Table 14.13                                                                                                                                                                                                                                                                 |  |  |

|                     | CSC                              | Set this bit to 1 to enable clock                                                                                                                                                                                                                                                                                            | Set to 0                                                                                                                                                                                                                                                                             |  |  |

|                     |                                  | synchronization                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

|                     | SWC                              | synchronization<br>Set this bit to 1 to have SCL2 output                                                                                                                                                                                                                                                                     | Set this bit to 1 to have SCL2 output                                                                                                                                                                                                                                                |  |  |

|                     | SWC                              | 5                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                    |  |  |

|                     | SWC                              | Set this bit to 1 to have SCL2 output                                                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                                                    |  |  |

|                     | SWC<br>ALS                       | Set this bit to 1 to have SCL2 output fixed to L at the falling edge of the 9th                                                                                                                                                                                                                                              | fixed to "L" at the falling edge of the 9 <sup>th</sup>                                                                                                                                                                                                                              |  |  |

|                     |                                  | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output                                                                                                                                                                                  | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock                                                                                                                                                                                                              |  |  |

|                     | ALS                              | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output                                                                                | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output                                                                                |  |  |

|                     | ALS<br>STAC<br>SWC2              | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low                                                         | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low                                                         |  |  |

|                     | ALS                              | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             |  |  |

| U2SMR3              | ALS<br>STAC<br>SWC2<br>SDHI<br>7 | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output<br>Set to 0 | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output<br>Set to 0 |  |  |

| U2SMR3              | ALS<br>STAC<br>SWC2<br>SDHI      | Set this bit to 1 to have SCL2 output<br>fixed to L at the falling edge of the 9th<br>bit of clock<br>Set this bit to 1 to have SDA2 output<br>stopped when arbitration-lost is detected<br>Set to 0<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             | fixed to "L" at the falling edge of the 9 <sup>th</sup><br>bit of clock<br>Set to 0<br>Set this bit to 1 to initialize UART2 at<br>start condition detection<br>Set this bit to 1 to have SCL2 output<br>forcibly pulled low<br>Set this bit to 1 to disable SDA2 output             |  |  |

#### Table 14.11 Registers to Be Used and Settings in I<sup>2</sup>C bus mode (1) (Continued)

NOTE:

1. Not all bits in the register are described above. Set those bits to 0 when writing to the registers in I<sup>2</sup>C bus mode.

#### 16.6.4 Bits 4,5 : SDA/SCL Logic Output Value Monitor Bits SDAM/SCLM

Bits SDAM/SCLM can monitor the logic value of the SDA and SCL output signals from the I<sup>2</sup>C bus interface circuit. The SDAM bit monitors the SDA output logic value. The SCLM bit monitors the SCL output logic value. The SDAM and SCLM bits are read-only. If necessary, set them to 0.

### 16.6.5 Bits 6,7 : I<sup>2</sup>C System Clock Select Bits ICK0, ICK1

The ICK1 bit, ICK0 bit, bits ICK4 to ICK2 in the S4D0 register, and the PCLK0 bit in the PCLKR register can select the system clock (VIIC) of the  $I^2C$  bus interface circuit.

The I<sup>2</sup>C bus system clock VIIC can be selected among 1/2 filc, 1/2.5 filc, 1/3 filc, 1/4 filc, 1/5 filc, 1/6 filc and 1/8 filc. filc can be selected between f1 and f2 by the PCLK0 bit setting.

|             | ,          |            |            |            |                               |

|-------------|------------|------------|------------|------------|-------------------------------|

| I3CK4[S4D0] | ICK3[S4D0] | ICK2[S4D0] | ICK1[S3D0] | ICK0[S3D0] | I <sup>2</sup> C system clock |

| 0           | 0          | 0          | 0          | 0          | VIIC = 1/2 fIIC               |

| 0           | 0          | 0          | 0          | 1          | VIIC = 1/4 fIIC               |

| 0           | 0          | 0          | 1          | 0          | VIIC = 1/8 fIIC               |

| 0           | 0          | 1          | Х          | Х          | VIIC = 1/2.5 fIIC             |

| 0           | 1          | 0          | Х          | Х          | VIIC = 1/3 fIIC               |

| 0           | 1          | 1          | Х          | Х          | VIIC = 1/5 fIIC               |

| 1           | 0          | 0          | Х          | Х          | VIIC = 1/6 fIIC               |

#### Table 16.6 I<sup>2</sup>C system clock select bits

( Do not set the combination other than the above)

#### 16.6.6 Address Receive in STOP/WAIT Mode

When WAIT mode is entered after the CM02 bit in the CM0 register is set to 0 (do not stop the peripheral function clock in wait mode), the  $I^2C$  bus interface circuit can receive address data in WAIT mode. However, the  $I^2C$  bus interface circuit is not operated in STOP mode or in low power consumption mode, because the  $I^2C$  bus system clock VIIC is not supplied.

# 16.7 I<sup>2</sup>C0 Control Register 2 (S4D0 Register)

The S4D0 register controls the error communication detection.

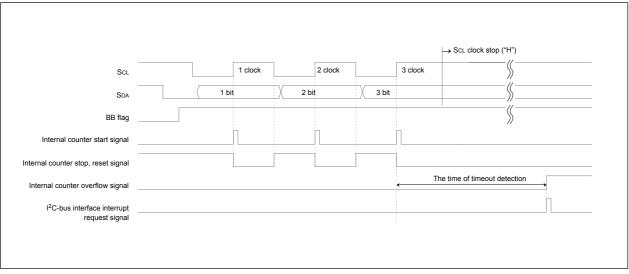

If the SCL clock is stopped counting dring data transfer, each device is stopped, staying online. To avoid the situation, the  $I^2C$  bus interface circuit has a function to detect the time-out when the SCL clock is stopped in high-level ("H") state for a specific period, and to generate an  $I^2C$  bus interface interrupt request. See **Figure 16.13**.

Figure 16.13 The timing of time-out detection

#### 16.7.1 Bit0: Time-Out Detection Function Enable Bit (TOE)

The TOE bit enables the time-out detection function. When the TOE bit is set to 1, time-out is detected and the  $I^2C$  bus interface interrupt request is generated when the following conditions are met.

1) the BB flag in the S10 register is set to 1 (bus busy)

2) the SCL clock stops for time-out detection period while high-level ("H") signal is maintained (see **Table 16.7**)

The internal counter measures the time-out detection time and the TOSEL bit selects between two modes, long time and short time. When time-out is detected, set the ES0 bit to 0 (I<sup>2</sup>C bus interface disabled) and reset the counter.

## 16.7.2 Bit1: Time-Out Detection Flag (TOF)

The TOF flag indicates the time-out detection. If the internal counter which measures the time-out period overflows, the TOF flag is set to 1 and the  $I^2C$  bus interface interrupt request is generated at the same time.

#### 16.7.3 Bit2: Time-Out Detection Period Select Bit (TOSEL)

The TOSEL bit selects time-out detection period from long time mode and short time mode. When the TOSEL bit is set to 0, long time mode is selected. When it is set to 1, short time mode is selected, respectively. The internal counter increments as a 16-bit counter in long time mode, while the counter increments as a 14-bit counter in short time mode, based on the I<sup>2</sup>C system clock (VIIC) as a counter source. **Table 16.7** shows examples of time-out detection period.

|           | Time-out Detection Tenou | (onit: ins)     |

|-----------|--------------------------|-----------------|

| VIIC(MHz) | Long time mode           | Short time mode |

| 4         | 16.4                     | 4.1             |

| 2         | 32.8                     | 8.2             |

| 1         | 65.6                     | 16.4            |

Table 16.7 Examples of Time-out Detection Period (Unit: ms)

#### 16.7.4 Bits 3,4,5: I<sup>2</sup>C System Clock Select Bits (ICK2-4)

Bits ICK4 to ICK2, and bits ICK1 and ICK0 in the S3D0 register, and the PCLK0 bit in the PCLKR register select the system clock (VIIC) of the  $I^2$ C bus interface circuit. See **Table 16.6** for the setting values.

### 16.7.5 Bit7: STOP Condition Detection Interrupt Request Bit (SCPIN)

The SCPIN bit monitors the stop condition detection interrupt. The SCPIN bit is set to 1 when the  $I^2C$  bus interface interrupt is generated by detecting the STOP condition. When this bit is set to 0 by program, it becomes 0. However, no change occurs even if it is set to 1.

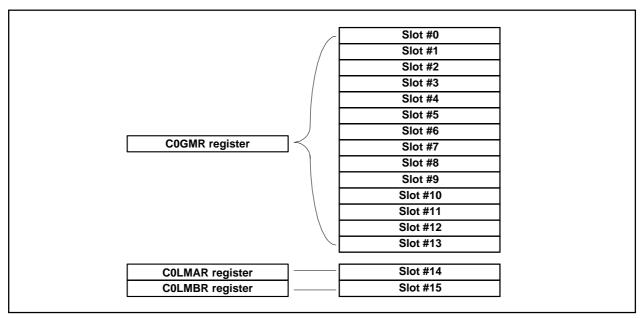

#### 17.1 CAN Module-Related Registers

The CAN0 module has the following registers.

#### (1) CAN Message Box

A CAN module is equipped with 16 slots (16 bytes or 8 words each). Slots 14 and 15 can be used as Basic CAN.

- Priority of the slots: The smaller the number of the slot, the higher the priority, in both transmission and reception.

- A program can define whether a slot is defined as transmitter or receiver.

#### (2) Acceptance Mask Registers

A CAN module is equipped with 3 masks for the acceptance filter.

- CAN0 global mask register (C0GMR register: 6 bytes)

- Configuration of the masking condition for acceptance filtering processing to slots 0 to 13

- CAN0 local mask A register (C0LMAR register: 6 bytes)

Configuration of the masking condition for acceptance filtering processing to slot 14

- CAN0 local mask B register (C0LMBR register: 6 bytes) Configuration of the masking condition for acceptance filtering processing to slot 15

#### (3) CAN SFR Registers

- CAN0 message control register j (C0MCTLj register: 8 bits X 16) (j = 0 to 15) Control of transmission and reception of a corresponding slot

- CANi control register (CiCTLR register: 16 bits) (i = 0, 1) Control of the CAN protocol

- CAN0 status register (C0STR register: 16 bits)

Indication of the protocol status

- CAN0 slot status register (C0SSTR register: 16 bits) Indication of the status of contents of each slot

- CAN0 interrupt control register (C0ICR register: 16 bits) Selection of "interrupt enabled or disabled" for each slot

- CAN0 extended ID register (C0IDR register: 16 bits)

Selection of ID format (standard or extended) for each slot

- CAN0 configuration register (C0CONR register: 16 bits) Configuration of the bus timing

- CAN0 receive error count register (C0RECR register: 8 bits) Indication of the error status of the CAN module in reception: the counter value is incremented or decremented according to the error occurrence.

- CAN0 transmit error count register (C0TECR register: 8 bits) Indication of the error status of the CAN module in transmission: the counter value is incremented or decremented according to the error occurrence.

- CAN0 time stamp register (C0TSR register: 16 bits) Indication of the value of the time stamp counter

- CAN0 acceptance filter support register (C0AFS register: 16 bits) Decoding the received ID for use by the acceptance filter support unit

Explanation of each register is given as follows.

#### **17.4 Acceptance Filtering Function and Masking Function**

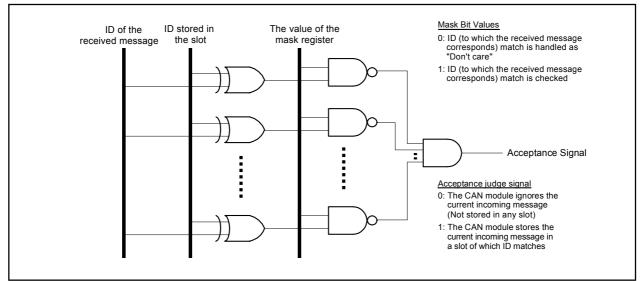

These functions serve the users to select and receive a facultative message. The COGMR register, the COLMAR register, and the COLMBR register can perform masking to the standard ID and the extended ID of 29 bits. The COGMR register corresponds to slots 0 to 13, the COLMAR register corresponds to slot 14, and the COLMBR register corresponds to slot 15. The masking function becomes valid to 11 bits or 29 bits of a received ID according to the value in the corresponding slot of the COIDR register upon acceptance filtering operation. When the masking function is employed, it is possible to receive a certain range of IDs. **Figure 17.21** shows correspondence of the mask registers and slots, **Figure 17.22** shows the acceptance function.

Figure 17.21 Correspondence of Mask Registers to Slots

Figure 17.22 Acceptance Function

When using the acceptance function, note the following points.

- (1) When one ID is defined in two slots, the one with a smaller number alone is valid.

- (2) When it is configured that slots 14 and 15 receive all IDs with Basic CAN mode, slots 14 and 15 receive all IDs which are not stored into slots 0 to 13.

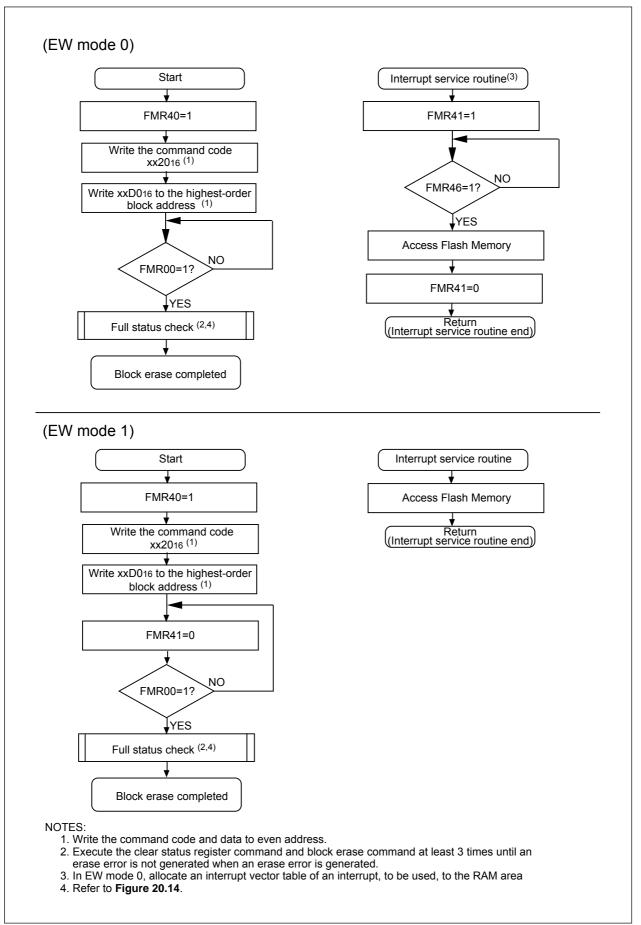

Figure 20.13 Block Erase Command (at use erase suspend)

RENESAS

#### **Timing Requirements**

# Vcc = 5V

#### (VCC = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 21.17 | Timer B Input (Counter Input in Event Counter Mode) |

|-------------|-----------------------------------------------------|

|-------------|-----------------------------------------------------|

| Symbol  | Parameter                                           | Standard |      | Linit |

|---------|-----------------------------------------------------|----------|------|-------|

|         |                                                     | Min.     | Max. | Unit  |

| tc(TB)  | TBin input cycle time (counted on one edge)         | 100      |      | ns    |

| tw(TBH) | TBin input HIGH pulse width (counted on one edge)   | 40       |      | ns    |

| tw(TBL) | TBin input LOW pulse width (counted on one edge)    | 40       |      | ns    |

| tc(TB)  | TBiin input cycle time (counted on both edges)      | 200      |      | ns    |

| tw(TBH) | TBin input HIGH pulse width (counted on both edges) | 80       |      | ns    |

| tw(TBL) | TBin input LOW pulse width (counted on both edges)  | 80       |      | ns    |

#### Table 21.18 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Standard |      | Unit |

|---------|------------------------------|----------|------|------|

|         |                              | Min.     | Max. | Unit |

| tc(TB)  | TBin input cycle time        | 400      |      | ns   |

| tw(TBH) | TBiin input HIGH pulse width | 200      |      | ns   |

| tw(TBL) | TBin input LOW pulse width   | 200      |      | ns   |

#### Table 21.19 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                   | Standard |      | Unit |

|---------|-----------------------------|----------|------|------|

|         |                             | Min.     | Max. |      |

| tc(TB)  | TBin input cycle time       | 400      |      | ns   |

| tw(TBH) | TBin input HIGH pulse width | 200      |      | ns   |

| tw(TBL) | TBin input LOW pulse width  | 200      |      | ns   |

#### Table 21.20 A /D Trigger Input

| Symbol Parameter | Parameter                                     | Standard |      | Unit |

|------------------|-----------------------------------------------|----------|------|------|

|                  | Faldifieter                                   | Min.     | Max. | Unit |

| tc(AD)           | ADTRG input cycle time (trigger able minimum) | 1000     |      | ns   |

| tw(ADL)          | ADTRG input LOW pulse width                   | 125      |      | ns   |

#### Table 21.21 Serial I/O

| Symbol   | Parameter                   | Standard |      | Unit |

|----------|-----------------------------|----------|------|------|

|          |                             | Min.     | Max. | Unit |

| tc(CK)   | CLKi input cycle time       | 200      |      | ns   |

| tw(CKH)  | CLKi input HIGH pulse width | 100      |      | ns   |

| tw(CKL)  | CLKi input LOW pulse width  | 100      |      | ns   |

| td(C-Q)  | TxDi output delay time      |          | 80   | ns   |

| th(C-Q)  | TxDi hold time              | 0        |      | ns   |

| tsu(D-C) | RxDi input setup time       | 70       |      | ns   |

| th(C-D)  | RxDi input hold time        | 90       |      | ns   |

#### Table 21.22 External Interrupt INTi Input

| Symbol  | Parameter                   | Standard |      | Unit |

|---------|-----------------------------|----------|------|------|

|         | i didineter                 | Min.     | Max. | Onit |

| tw(INH) | INTi input HIGH pulse width | 250      |      | ns   |

| tw(INL) | INTi input LOW pulse width  | 250      |      | ns   |

Vcc = 5V

μĀ

3

0.8

#### Standard Symbol Parameter Measurement Condition Unit Min. Typ. Max. Mask ROM f(BCLK) = 20 MHz, lcc Power Supply Output pins are 25 18 mΑ Current left open and main clock, no division (Vcc=4.2 to 5.5V) other pins are f(BCLK) = 16 MHz, 14 20 mΑ connected to Vss main clock, no division On-chip oscillation, 2 mΑ f2(ROC) selected, f(BCLK) = 1 MHz f(BCLK) = 20 MHz. 18 25 mΑ Flash memory main clock, no division f(BCLK) = 16 MHz. 14 20 mΑ main clock, no division On-chip oscillation, f2(ROC) selected, 2 mΑ f(BCLK) = 1 MHz Flash memory 11 mΑ f(BCLK) = 10 MHz, Vcc = 5.0 V program Flash memory 11 mΑ f(BCLK) = 10 MHz, Vcc = 5.0 V erase μĀ Mask ROM f(BCLK) = 32 kHz,25 In low-power consumption mode, Program running on ROM<sup>(3)</sup> On-chip oscillation, 50 μΑ f2(ROC) selected, f(BCLK) = 1 MHz, In wait mode f(BCLK) = 32 kHz,μA 25 Flash memory In low-power consumption mode, Program running on RAM<sup>(3)</sup> f(BCLK) = 32 kHz. 450 μA In low-power consumption mode, Program running on flash memory<sup>(3)</sup> On-chip oscillation, f2(ROC) selected, 50 μΑ f(BCLK) = 1 MHz, In wait mode f(BCLK) = 32 kHz, In wait mode<sup>(2)</sup>, Mask ROM, 8.5 μΑ Flash memory Oscillation capacity high μĀ f(BCLK) = 32 kHz, In wait mode<sup>(2)</sup>, 3 Oscillation capacity low

#### Table 21.85 Electrical Characteristics (2) (1)

NOTES:

1. Referenced to V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0 V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V $\infty$  = 4.2 to 5.5 V, V $\otimes$  = 0V at Topr = -40 to 105 ° C, f(BCLK) = 20MHz / V \infty

While clock stops, Topr = 25° C

Topr = -40 to 125 ° C, f(BCLK) = 16 MHz, unless otherwise specified.

2. With one timer operates, using fc32.

3. This indicates the memory in which the program to be executed exists.

- 6. When a count is started and the first effective edge is input, an undefined value is transferred to the reload register. At this time, timer Bi interrupt request is not generated.

- 7. A value of the counter is undefined at the beginning of a count. MR3 may be set to 1 and timer Bi interrupt request may be generated between a count start and an effective edge input.

- 8. For pulse width measurement, pulse widths are successively measured. Use program to check whether the measurement result is an "H" level width or an "L" level width.

#### 22.6.3 Three-phase Motor Control Timer Function

When the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forced cutoff by SD pin input (high-impedance) enabled), the INV03 bit in the INVC0 register is set to 1 (three-phase motor control timer output enabled), and a low-level ("L") signal is applied to the  $\overline{SD}$  pin while a three-phase PWM signal is output, the MCU is forced to cutoff and pins U,  $\overline{U}$ , V,  $\overline{V}$ , W, and  $\overline{W}$  are placed in a high-impedance state and the INV03 bit is set to 0 (three-phase motor control timer output disabled).

To resume the three-phase PWM signal output from pins U,  $\overline{U}$ , V,  $\overline{V}$ , W, and  $\overline{W}$ , set the INV03 bit to 1 and the IVPCR1 bit to 0 (three-phase output forced cutoff disabled) after the  $\overline{SD}$  pin level becomes "H". Then set the IVPCR1 bit to 1 (three-phase output forced cutoff enabled) in order to enable the three-phase output forced cutoff function by input to the SD pin again.

The INV03 bit cannot be set to 1 while an "L" signal is input to the  $\overline{SD}$  pin. To set the INV03 bit to 1 after forcible cutoff, write 1 to the INV03 bit and read the bit to ensure that it is set to 1 by program. Then set the IVPCR1 bit to 1 after setting it to 0.

- 8. If the CPU reads the ADi register (i = 0 to 7) at the same time the conversion result is stored in the ADi register after completion of A/D conversion, an incorrect value may be stored in the ADi register. This problem occurs when a divide-by-n clock derived from the main clock or a subclock is selected for CPU clock.

- When operating in one-shot, single-sweep mode, simultaneous sample sweep mode, delayed trigger mode 0 or delayed trigger mode 1