# Renesas Electronics America Inc - <u>M30291FCTHP#U7A-T Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

**E·XF**

| Product Status             | Obsolete                                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                  |

| Core Size                  | -                                                                                  |

| Speed                      | -                                                                                  |

| Connectivity               | -                                                                                  |

| Peripherals                | -                                                                                  |

| Number of I/O              | -                                                                                  |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | -                                                                                  |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | -                                                                                  |

| Voltage - Supply (Vcc/Vdd) | -                                                                                  |

| Data Converters            | -                                                                                  |

| Oscillator Type            | -                                                                                  |

| Operating Temperature      | -                                                                                  |

| Mounting Type              | -                                                                                  |

| Package / Case             | -                                                                                  |

| Supplier Device Package    | -                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30291fcthp-u7a-t |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin<br>No. | Control<br>Pin | Port | Interrupt<br>Pin | Timer Pin  | Timer S Pin | UART/CAN Pin                                | Multi-master<br>I <sup>2</sup> C bus Pin | Analog Pin |

|------------|----------------|------|------------------|------------|-------------|---------------------------------------------|------------------------------------------|------------|

| 1          |                | P95  |                  |            |             | CLK4                                        |                                          | AN25       |

| 2          |                | P93  |                  |            |             | СТХ                                         |                                          | AN24       |

| 3          |                | P92  |                  | TB2IN      |             | CRX                                         |                                          | AN32       |

| 4          |                | P91  |                  | TB1IN      |             |                                             |                                          | AN31       |

| 5          | CLKOUT         | P90  |                  | ΤΒοιΝ      |             |                                             |                                          | AN30       |

| 6          | CNVss          |      |                  |            |             |                                             |                                          |            |

| 7          | XCIN           | P87  |                  |            |             |                                             |                                          |            |

| 8          | Хсоит          | P86  |                  |            |             |                                             |                                          |            |

| 9          | RESET          |      |                  |            |             |                                             |                                          |            |

| 10         | Хоит           |      |                  |            |             |                                             |                                          |            |

| 11         | Vss            |      |                  |            |             |                                             |                                          |            |

| 12         | Xin            |      |                  |            |             |                                             |                                          |            |

| 13         | Vcc            |      |                  |            |             |                                             |                                          |            |

| 14         |                | P85  | NMI              | SD         |             |                                             |                                          |            |

| 15         |                | P84  | INT <sub>2</sub> | ZP         |             |                                             |                                          |            |

| 16         |                | P83  | INT <sub>1</sub> |            |             |                                             |                                          |            |

| 17         |                | P82  | ĪNT <sub>0</sub> |            |             |                                             |                                          |            |

| 18         |                | P81  |                  | TA4IN / U  |             |                                             |                                          |            |

| 19         |                | P80  |                  | ТА40UT / U |             |                                             |                                          |            |

| 20         |                | P77  |                  | ТАзіл      |             |                                             |                                          |            |

| 21         |                | P76  |                  | ТАзоит     |             |                                             |                                          |            |

| 22         |                | P75  |                  | TA2IN / W  |             |                                             |                                          |            |

| 23         |                | P74  |                  | TA20UT / W |             |                                             |                                          |            |

| 24         |                | P73  |                  | TA1IN / V  |             | CTS2 / RTS2 / TxD1                          |                                          |            |

| 25         |                | P72  |                  | TA10UT / V |             | CLK2 / RxD1                                 |                                          |            |

| 26         |                | P71  |                  | TAOIN      |             | RxD2 / SCL2 / CLK1                          |                                          |            |

| 27         |                | P70  |                  | ΤΑυουτ     |             | TxD2 / SDA2 / RTS1 /<br>CTS1 / CTS0 / CLKS1 |                                          |            |

| 28         |                | P67  |                  |            |             | TxD1                                        |                                          |            |

| 29         |                | P66  |                  |            |             | RxD1                                        |                                          |            |

| 30         |                | P65  |                  |            |             | CLK1                                        |                                          |            |

| 31         |                | P64  |                  |            |             | RTS1 / CTS1/ CTS0 /<br>CLKS1                |                                          |            |

| 32         |                | P37  |                  |            |             |                                             |                                          |            |

| 33         |                | P36  |                  |            |             |                                             |                                          |            |

| 34         |                | P35  |                  |            |             |                                             |                                          |            |

| 35         |                | P34  |                  |            |             |                                             |                                          |            |

| 36         |                | P33  |                  |            |             |                                             |                                          |            |

| 37         |                | P32  |                  |            |             | Sout3                                       |                                          |            |

| 38         |                | P31  |                  |            |             | SIN3                                        |                                          |            |

| 39         |                | P30  |                  |            |             | CLK3                                        |                                          |            |

| 40         |                | P63  |                  |            |             | TxD0                                        |                                          |            |

Table 1 12 Pin Characteristics for 80-Pin Package

# Table 4.4 SFR Information (4)

| Table   | 4.4 SFR Information (4)             |        |             |

|---------|-------------------------------------|--------|-------------|

| Address | Register                            | Symbol | After reset |

| 00C016  | CAN0 message box 6: Identifier/DLC  |        | XX16        |

| 00C116  |                                     |        | XX16        |

| 00C216  |                                     |        | XX16        |

| 00C316  |                                     |        | XX16        |

| 00C416  |                                     |        | XX16        |

|         |                                     |        | XX16        |

| 00C516  | CANO message her 6 : Date field     |        | XX16        |

| 00C616  | CAN0 message box 6 : Data field     |        |             |

| 00C716  |                                     |        | XX16        |

| 00C816  |                                     |        | XX16        |

| 00C916  |                                     |        | XX16        |

| 00CA16  |                                     |        | XX16        |

| 00CB16  |                                     |        | XX16        |

| 00CC16  |                                     |        | XX16        |

| 00CD16  |                                     |        | XX16        |

| 00CE16  | CAN0 message box 6 : Time stamp     |        | XX16        |

| 00CF16  |                                     |        | XX16        |

| 00D016  | CAN0 message box 7 : Identifier/DLC |        | XX16        |

|         | CANO message box 7 . Identilien/DEC |        | XX16        |

| 00D116  |                                     |        |             |

| 00D216  |                                     |        | XX16        |

| 00D316  |                                     |        | XX16        |

| 00D416  |                                     |        | XX16        |

| 00D516  |                                     |        | XX16        |

| 00D616  | CAN0 message box 7 : Data field     |        | XX16        |

| 00D716  |                                     |        | XX16        |

| 00D816  |                                     |        | XX16        |

| 00D916  |                                     |        | XX16        |

| 00DA16  |                                     |        | XX16        |

| 00DB16  |                                     |        | XX16        |

|         |                                     |        | XX16        |

| 00DC16  |                                     |        |             |

| 00DD16  |                                     |        | XX16        |

| 00DE16  | CAN0 message box 7 : Time stamp     |        | XX16        |

| 00DF16  |                                     |        | XX16        |

| 00E016  | CAN0 message box 8: Identifier/DLC  |        | XX16        |

| 00E116  |                                     |        | XX16        |

| 00E216  |                                     |        | XX16        |

| 00E316  |                                     |        | XX16        |

| 00E416  |                                     |        | XX16        |

| 00E516  |                                     |        | XX16        |

| 00E616  | CAN0 message box 8: Data field      |        | XX16        |

| 00E716  | er in oblige box e. Buta noia       |        | XX16        |

| 00E716  |                                     |        | XX16        |

|         |                                     |        |             |

| 00E916  |                                     |        | XX16        |

| 00EA16  |                                     |        | XX16        |

| 00EB16  |                                     |        | XX16        |

| 00EC16  |                                     |        | XX16        |

| 00ED16  |                                     |        | XX16        |

| 00EE16  | CAN0 message box 8 : Time stamp     |        | XX16        |

| 00EF16  |                                     |        | XX16        |

| 00F016  | CAN0 message box 9 : Identifier/DLC |        | XX16        |

| 00F116  |                                     |        | XX16        |

| 00F216  |                                     |        | XX16        |

|         |                                     |        | XX16        |

| 00F316  |                                     |        |             |

| 00F416  |                                     |        | XX16        |

| 00F516  |                                     |        | XX16        |

| 00F616  | CAN0 message box 9 : Data field     |        | XX16        |

| 00F716  |                                     |        | XX16        |

| 00F816  |                                     |        | XX16        |

| 00F916  |                                     |        | XX16        |

| 00FA16  |                                     |        | XX16        |

| 00FB16  |                                     |        | XX16        |

| 00FC16  |                                     |        | XX16        |

| 00FD16  |                                     |        | XX16        |

|         | CAN0 message box 9 : Time stamp     |        | XX16        |

| 00FE16  | Univ messaye but a . Time sidilip   |        |             |

| 00FF16  |                                     |        | XX16        |

Note 1: The blank areas are reserved and cannot be used by users.

X : Undefined

### Table 4.9 SFR Information (9)

|                                          | 4.9 SFR Information (9)                             | Current el     | After reach       |

|------------------------------------------|-----------------------------------------------------|----------------|-------------------|

| Address<br>0340 <sub>16</sub>            | Register                                            | Symbol         | After reset       |

| 034016                                   |                                                     |                |                   |

| 034216                                   | Timer A1-1 register                                 | TA11           | XX16              |

| 034316                                   |                                                     |                | XX16              |

| 034416                                   | Timer A2-1 register                                 | TA21           | XX16              |

| 034516                                   |                                                     |                | XX16              |

| 034616                                   | Timer A4-1 register                                 | TA41           | XX16              |

| 034716                                   |                                                     |                | XX16              |

| 034816                                   | Three phase PWM control register 0                  | INVC0          | 0016              |

| 034916                                   | Three phase PWM control register 1                  | INVC1          | 0016              |

| 034A <sub>16</sub>                       | Three phase output buffer register 0                | IDB0           | 0016              |

| 034B16                                   | Three phase output buffer register 1                | IDB1           | 0016              |

| 034C16                                   | Dead time timer                                     | DTT            | XX16              |

| 034D16                                   | Timer B2 Interrupt occurrence frequency set counter | ICTB2          | XX16              |

| 034E16                                   | Position - data - retain function control register  | PDRF           | XXXX00002         |

| 034F16<br>035016                         |                                                     |                |                   |

| 035016                                   |                                                     |                |                   |

| 035216                                   |                                                     |                |                   |

| 035316                                   |                                                     |                |                   |

| 035416                                   |                                                     |                |                   |

| 035516                                   |                                                     |                |                   |

| 035616                                   |                                                     |                |                   |

| 035716                                   |                                                     |                |                   |

| 035816                                   | Port function control register                      | PFCR           | 001111112         |

| 035916                                   |                                                     |                |                   |

| 035A16                                   |                                                     |                |                   |

| 035B16                                   |                                                     |                |                   |

| 035C16                                   |                                                     |                |                   |

| 035D16                                   | Interrupt cause select register 2 <sup>(2)</sup>    |                | 00////000-        |

| 035E16<br>035F16                         | Interrupt cause select register 2(*)                | IFSR2A<br>IFSR | 00XXX0002<br>0016 |

| 036016                                   | SI/O3 transmit/receive register                     | S3TRR          | XX16              |

| 036116                                   |                                                     | 001111         | 70(10             |

| 036216                                   | SI/O3 control register                              | S3C            | 01000002          |

| 036316                                   | SI/O3 bit rate register                             | S3BRG          | XX16              |

| 036416                                   | SI/O4 transmit/receive register                     | S4TRR          | XX16              |

| 036516                                   |                                                     |                |                   |

| 036616                                   | SI/O4 control register                              | S4C            | 01000002          |

| 036716                                   | SI/O4 bit rate register                             | S4BRG          | XX16              |

| 036816                                   |                                                     |                |                   |

| 036916                                   |                                                     |                |                   |

| 036A16                                   |                                                     |                |                   |

| 036B16                                   |                                                     |                |                   |

| 036C16<br>036D16                         |                                                     |                |                   |

| 036D16                                   |                                                     |                |                   |

| 036F16                                   |                                                     |                |                   |

| 037016                                   |                                                     |                |                   |

| 037116                                   |                                                     |                |                   |

| 037216                                   |                                                     |                |                   |

| 037316                                   |                                                     |                |                   |

| 037416                                   | UART2 special mode register 4                       | U2SMR4         | 0016              |

| 037516                                   | UART2 special mode register 3                       | U2SMR3         | 000X0X0X2         |

| 037616                                   | UART2 special mode register 2                       | U2SMR2         | X0000002          |

| 037716                                   | UART2 special mode register                         | U2SMR          | X0000002          |

| 037816                                   | UART2 transmit/receive mode register                | U2MR           | 0016              |

| 037916                                   | UART2 bit rate register                             | U2BRG<br>U2TB  | XX16<br>XX16      |

| 037A16                                   | UART2 transmit buffer register                      | UZIB           | XX16<br>XX16      |

| 037B <sub>16</sub><br>037C <sub>16</sub> | UART2 transmit/receive control register 0           | U2C0           | 000010002         |

| 037C16                                   | UART2 transmit/receive control register 0           | U2C1           | 000010002         |

| 037D16                                   | UART2 receive buffer register                       | U2RB           | XX16              |

| 037F16                                   |                                                     |                | XX16              |

|                                          |                                                     |                |                   |

Note 1: The blank areas are reserved and cannot be used by users. Note 2: Write 0 to the bit 0 after reset.

X : Undefined

# 7.6 Power Control

There are three power control modes. In this chapter, all modes other than wait and stop modes are referred to as normal operation mode.

# 7.6.1 Normal Operation Mode

Normal operation mode is further classified into seven modes.

In normal operation mode, because the CPU clock and the peripheral function clocks both are on, the CPU and the peripheral functions are operating. Power control is exercised by controlling the CPU clock frequency. The higher the CPU clock frequency, the greater the processing capability. The lower the CPU clock frequency, the smaller the power consumption in the chip. If the unnecessary oscillator circuits are turned off, the power consumption is further reduced.

Before the clock sources for the CPU clock can be switched over, the new clock source must be in stable oscillation. If the new clock source is the main clock, sub clock or PLL clock, allow a sufficient wait time in a program until it becomes oscillating stably.

Note that operation modes cannot be changed directly from low power dissipation mode to on-chip oscillator mode or on-chip oscillator low power dissipation mode. Nor can operation modes be changed directly from on-chip oscillator mode or on-chip oscillator low power dissipation mode to low power dissipation mode.

When the CPU clock source is changed from the on-chip oscillator to the main clock, change the operation mode to the medium speed mode (divided by 8 mode) after the clock was divided by 8 (the CM06 bit in the CM0 register was set to 1) in the on-chip oscillator mode.

# 7.6.1.1 High-speed Mode

The main clock divided by 1 provides the CPU clock. If the sub clock is on, fc32 can be used as the count source for timers A and B.

# 7.6.1.2 PLL Operation Mode

The main clock multiplied by 2 or 4 provides the PLL clock, and this PLL clock serves as the CPU clock. If the sub clock is on, fC32 can be used as the count source for timers A and B. PLL operation mode can be entered from high speed mode. If PLL operation mode is to be changed to wait or stop mode, first go to high speed mode before changing.

# 7.6.1.3 Medium-speed Mode

The main clock divided by 2, 4, 8 or 16 provides the CPU clock. If the sub clock is on, fC32 can be used as the count source for timers A and B.

# 7.6.1.4 Low-speed Mode

The sub clock provides the CPU clock. The main clock is used as the clock source for the peripheral function clock when the CM21 bit is set to 0 (on-chip oscillator turned off), and the on-chip oscillator clock is used when the CM21 bit is set to 1 (on-chip oscillator oscillating).

The fC32 clock can be used as the count source for timers A and B.

# 7.6.1.5 Low Power Dissipation Mode

In this mode, the main clock is turned off after being placed in low speed mode. The sub clock provides the CPU clock. The fc32 clock can be used as the count source for timers A and B. Peripheral function clock can use only fc32.

Simultaneously when this mode is selected, the CM06 bit in the CM0 register becomes 1 (divided by 8 mode). In the low power dissipation mode, do not change the CM06 bit. Consequently, the medium speed (divided by 8) mode is to be selected when the main clock is operated next.

# 7.6.3 Stop Mode

In stop mode, all oscillator circuits are turned off, so are the CPU clock and the peripheral function clocks. Therefore, the CPU and the peripheral functions clocked by these clocks stop operating. The least amount of power is consumed in this mode. If the voltage applied to Vcc pin is VRAM or more, the internal RAM is retained. When applying 2.7 or less voltage to Vcc pin, make sure Vcc≥VRAM.

However, the peripheral functions clocked by external signals keep operating. The following interrupts can be used to exit stop mode.

- $\bullet \ \overline{\text{NMI}} \ \text{interrupt}$

- Key interrupt

- INT interrupt

- Timer A, Timer B interrupt (when counting external pulses in event counter mode)

- Serial I/O interrupt (when external clock is selected)

- Low voltage detection interrup (refer to "Low Voltage Detection Interrupt" for an operating condition)

- CAN0 Wake\_up interrupt (in CAN sleep mode)

# 7.6.3.1 Entering Stop Mode

The MCU is placed into stop mode by setting the CM10 bit in the CM1 register to 1 (all clocks turned off). At the same time, the CM06 bit in the CM0 register is set to 1 (divide-by-8 mode) and the CM15 bit in the CM10 register is set to 1 (main clock oscillator circuit drive capability high).

Before entering stop mode, set the CM20 bit to 0 (oscillation stop, re-oscillation detection function disable).

Also, if the CM11 bit is 1 (PLL clock for the CPU clock source), set the CM11 bit to 0 (main clock for the CPU clock source) and the PLC07 bit to 0 (PLL turned off) before entering stop mode.

# 7.6.3.2 Pin Status during Stop Mode

The I/O pins retain their status held just prior to entering stop mode.

# 7.6.3.3 Exiting Stop Mode

The MCU is moved out of stop mode by a hardware reset,  $\overline{\text{NMI}}$  interrupt or peripheral function interrupt. If the MCU is to be moved out of stop mode by a hardware reset or  $\overline{\text{NMI}}$  interrupt, set the peripheral function interrupt priority bits ILVL2 to ILVL0 to 0002 (interrupts disable) before setting the CM10 bit to 1. If the MCU is to be moved out of stop mode by a peripheral function interrupt, set up the following before setting the CM10 bit to 1.

1. In bits ILVL2 to ILVL0 of the interrupt control register, set the interrupt priority level of the peripheral function interrupt to be used to exit stop mode.

Also, for all of the peripheral function interrupts not used to exit stop mode, set bits ILVL2 to ILVL0 to 0002.

- 2. Set the I flag to 1.

- 3. Enable the peripheral function whose interrupt is to be used to exit stop mode.

In this case, when an interrupt request is generated and the CPU clock is thereby turned on, an interrupt service routine is executed.

Which CPU clock will be used after exiting stop mode by a peripheral function or  $\overline{\text{NMI}}$  interrupt is determined by the CPU clock that was on when the MCU was placed into stop mode as follows: If the CPU clock before entering stop mode was derived from the sub clock: sub clock If the CPU clock before entering stop mode was derived from the main clock: main clock divide-by-8 If the CPU clock before entering stop mode was derived from the on-chip oscillator clock: on-chip oscillator clock:

lator clock divide-by-8

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbol<br>TB0MR | Address<br>to TB1MR 039B16 to                                          | After Reset<br>039C16 00XX00002                 |    |

|-------------------------|-----------------|------------------------------------------------------------------------|-------------------------------------------------|----|

|                         | Bit Symbol      | Bit Name                                                               | Function                                        | RW |

|                         | TMOD0           | Operation mode select bit                                              | 0 0: Timer mode or A/D trigger mode             | RW |

|                         | TMOD1           |                                                                        | 0 0. Timer mode of A/D trigger mode             | RW |

|                         | MR0             | Invalid in A/D trigger mode                                            |                                                 | RW |

|                         | MR1             | Either 0 or 1 is enabled                                               |                                                 | RW |

|                         | MR2             | TB0MR register<br>Set to 0 in A/D trigger mode                         | e                                               | RV |

|                         |                 | TB1MR register<br>Nothing is assigned. If nece<br>content is undefined | essary, set to 0. When read, its                |    |

|                         | MR3             | When write in A/D trigger m<br>mode, its content is undefir            | node, set to 0. When read in A/D trigger<br>ned | RO |

| ·                       | TCK0            | Count source select bit <sup>(1)</sup>                                 | <sup>b7 b6</sup><br>О О: f1 or f2<br>О 1: f8    | RW |

|                         | TCK1            |                                                                        | 1 0: f32<br>1 1: fC32                           | RW |

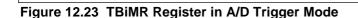

### Figure 12.24 TB2SC Register in A/D Trigger Mode

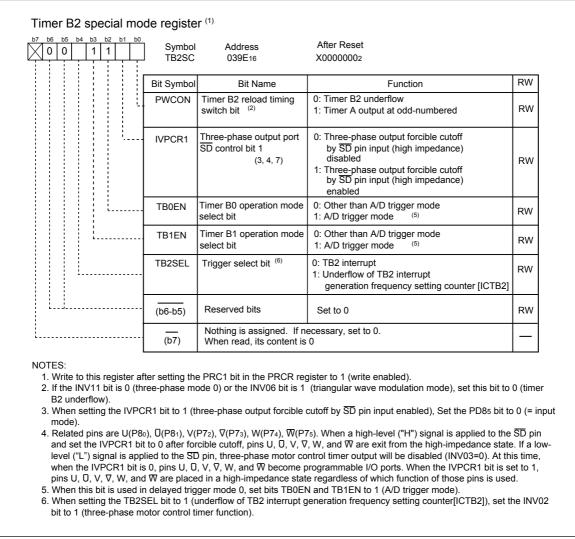

# 12.3.2 Three-phase/Port Output Switch Function

When the INVC03 bit in the INVC0 register set to 1 (Timer output enabled for three-phase motor control) and setting the PFCi (i=0 to 5) in the PFCR register to 0 (I/O port), the three-phase PWM output pin (U,  $\overline{U}$ , V,  $\overline{V}$ , W and  $\overline{W}$ ) functions as I/O port. Each bit of the PFCi bits (i=0 to 5) is applicable for each one of three-phase PWM output pins. **Figure 12.37** shows the example of three-phase/port output switch function. **Figure 12.38** shows the PFCR register and the three-phase protect control register.

Figure 12.37 Usage Example of Three-phse/Port Output Switch Function

| Function                       | STSPSEL = 0                     | STSPSEL = 1                          |

|--------------------------------|---------------------------------|--------------------------------------|

| Output of SCL2 and SDA2 pins   | Output transfer clock and data/ | The STAREQ, RSTAREQ and              |

|                                | Program with a port determines  | STPREQ bit determine how the         |

|                                | how the start condition or stop | start condition or stop condition is |

|                                | condition is output             | output                               |

| Start/stop condition interrupt | Start/stop condition are detec- | Start/stop condition generation      |

| request generation timing      | ted                             | are completed                        |

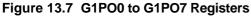

Table 14.14 STSPSEL Bit Functions

Figure 14.25 STSPSEL Bit Functions

# 14.1.3.3 Arbitration

Unmatching of the transmit data and SDA2 pin input data is checked synchronously with the rising edge of SCL2. Use the ABC bit in the U2SMR register to select the timing at which the ABT bit in the U2RB register is updated. If the ABC bit is set to 0 (updated bitwise), the ABT bit is set to 1 at the same time unmatching is detected during check, and is cleared to 0 when not detected. In cases when the ABC bit is set to 1, if unmatching is detected even once during check, the ABT bit is set to 1 (unmatching detected) at the falling edge of the clock pulse of 9th bit. If the ABT bit needs to be updated bytewise, clear the ABT bit to 0 (undetected) after detecting acknowledge in the first byte, before transferring the next byte.

Setting the ALS bit in the U2SMR2 register to 1 (SDA2 output stop enabled) causes arbitration-lost to occur, in which case the SDA2 pin is placed in the high-impedance state at the same time the ABT bit is set to 1 (unmatching detected).

# 15. A/D Converter

### Note

Ports P04 to P07(AN04 to AN07), P10 to P13(AN20 to AN23) and P95 to P97(AN25 to AN27) are not available in 64-pin package. Do not use port P04 to P07(AN04 to AN07), P10 to P13(AN20 to AN23) and P95 to P97(AN25 to AN27) as analog input pins in 64-pin package.

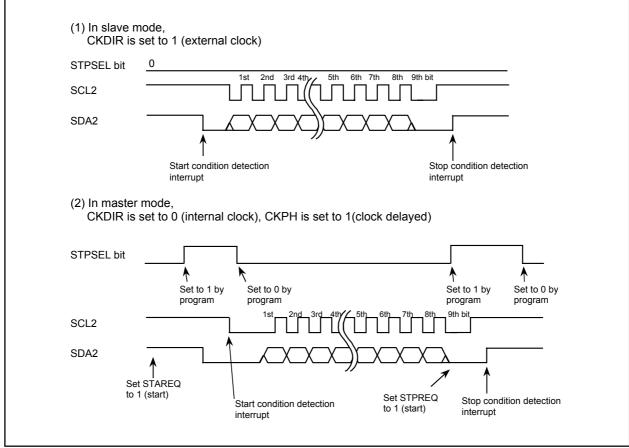

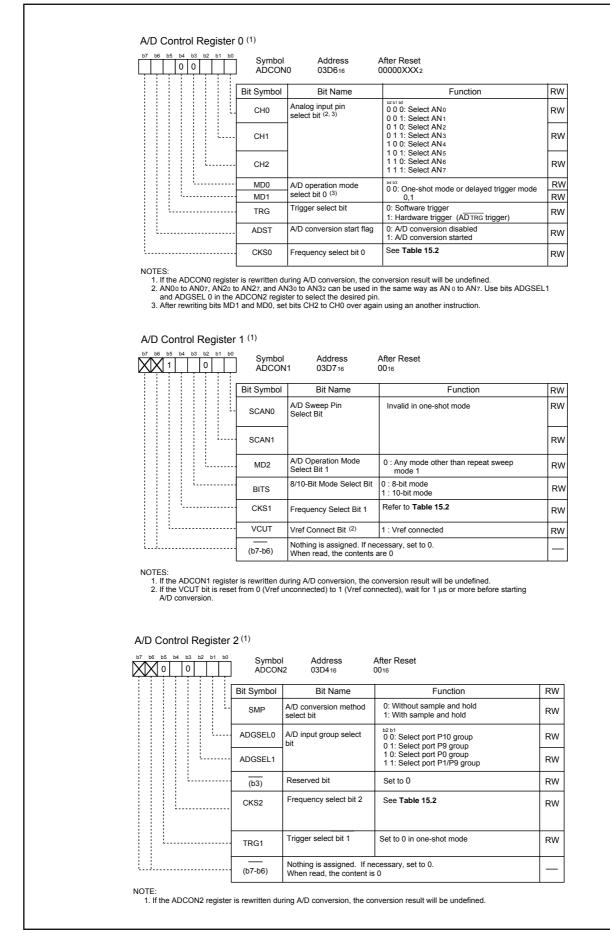

The MCU contains one A/D converter circuit based on 10-bit successive approximation method configured with a capacitive-coupling amplifier. The analog inputs share the pins with P100 to P107 (AN0 to AN7), P00 to P07 (AN00 to AN07), and P10 to P13, P93, P95 to P97 (AN20 to AN27), and P90 to P92 (AN30 to AN32). Similarly, ADTRG input shares the pin with P15. Therefore, when using these inputs, make sure the corresponding port direction bits are set to 0 (input mode).

When not using the A/D converter, set the VCUT bit to 0 (Vref unconnected), so that no current will flow from the Vref pin into the resistor ladder, helping to reduce the power consumption of the chip.

The A/D conversion result is stored in the ADi register bits for ANi, AN0i, AN2i (i = 0 to 7), and AN3i pins (i = 0 to 2). **Table 15.1** shows the A/D converter performance. **Figure 15.1** shows the A/D converter block diagram and **Figures 15.2** to **15.4** show the A/D converter associated with registers.

| Table 15.1 A/D Converter                 | Terrormanee                                                                        |

|------------------------------------------|------------------------------------------------------------------------------------|

| Item                                     | Performance                                                                        |

| A/D Conversion Method                    | Successive approximation (capacitive coupling amplifier)                           |

| Analog Input Voltage (1)                 | 0V to AVcc (Vcc)                                                                   |

| Operating Clock $\phi$ AD <sup>(2)</sup> | fAD/divided-by-2 or fAD/divided-by-3 or fAD/divided-by-4 or fAD/divided-by-6       |

|                                          | or fAD/divided-by-12 or fAD                                                        |

| Resolution                               | 8-bit or 10-bit (selectable)                                                       |

| Integral Nonlinearity Error              | When AVcc = Vref = 5V                                                              |

|                                          | With 8-bit resolution: ±2LSB                                                       |

|                                          | With 10-bit resolution: ±3LSB                                                      |

|                                          | When AVcc = Vref = 3.3V                                                            |

|                                          | With 8-bit resolution: ±2LSB                                                       |

|                                          | With 10-bit resolution: ±5LSB                                                      |

| Operating Modes                          | One-shot mode, repeat mode, single sweep mode, repeat sweep mode 0, repeat         |

|                                          | sweep mode 1, simultaneous sample sweep mode and delayed trigger mode 0,1          |

| Analog Input Pins                        | 8 pins (AN0 to AN7) + 8 pins (AN00 to AN07) + 8 pins (AN20 to AN27) + 3 pins (AN30 |

|                                          | to AN32) (80-pin package)                                                          |

|                                          | 8 pins (AN0 to AN7) + 4 pins (AN00 to AN03) + 1 pin (AN24) + 3 pins (AN30 to AN32) |

|                                          | (64-pin package)                                                                   |

| Conversion Speed Per Pin                 | Without sample and hold function                                                   |

|                                          | 8-bit resolution: 49 (AD cycles, 10-bit resolution: 59 (AD cycles                  |

|                                          | With sample and hold function                                                      |

|                                          | 8-bit resolution: 28 (AD cycles, 10-bit resolution: 33 (AD cycles                  |

### Table 15.1 A/D Converter Performance

NOTES:

- 1. Not dependent on use of sample and hold function.

- 2. Set the  $\ensuremath{\varphi}\mbox{AD}$  frequency to 10 MHz or less.

Without sample-and-hold function, set the  $\phi$ AD frequency to 250kHz or more.

With the sample and hold function, set the  $\phi$ AD frequency to 1MHz or more.

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                   | Symbol<br>ADCON0 |                              | After Reset<br>00000XXX2                                                  |    |

|---------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|---------------------------------------------------------------------------|----|

|                                                                                                                           | Bit Symbol       | Bit Name                     | Function                                                                  | R۱ |

|                                                                                                                           | CH0              |                              |                                                                           | R١ |

| ·                                                                                                                         | CH1              | Analog input pin select bit  | Invalid in repeat sweep mode 0                                            | R  |

|                                                                                                                           | CH2              |                              |                                                                           | R  |

|                                                                                                                           | MD0              | A/D operation mode           | 1 1: Repeat sweep mode 0 or                                               | R  |

|                                                                                                                           | MD1              | select bit 0                 | repeat sweep mode 1                                                       | R  |

|                                                                                                                           | TRG              | Trigger select bit           | 0: Software trigger<br>1: Hardware trigger (ADTRG trigger)                | R  |

|                                                                                                                           | ADST             | A/D conversion start flag    | 0: A/D conversion disabled<br>1: A/D conversion started                   | R  |

|                                                                                                                           | CKS0             | Frequency select bit 0       | See Table 15.2                                                            | R  |

| OTE:<br>1. If the ADCON0 registe<br>D Control Register<br>b6 b5 b4 b3 b2 b1 b0<br>1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |                  | Address                      | onversion result will be undefined.<br>After Reset<br>0016                |    |

|                                                                                                                           | Bit Symbol       | Bit Name                     | Function                                                                  | R  |

|                                                                                                                           | SCAN0            |                              | When repeat sweep mode 0 is selected,<br>b1b0<br>0 0: AN0 to AN1 (2 pins) | R  |

|                                                                                                                           |                  | A/D sweep pin select bit (2) |                                                                           |    |

NOTES:

If the ADCON1 register is rewritten during A/D conversion, the conversion result will be undefined.

AN00 to AN07, AN20 to AN27, and AN30 to AN32 can be used in the same way as AN0 to AN7. Use bits ADGSEL1 and ADGSEL 0 in the ADCON2 register to select the desired pin.

3. If the VCUT bit is reset from 0 (Vref unconnected) to 1 (Vref connected), wait for 1 µs or more before starting A/D conversion.

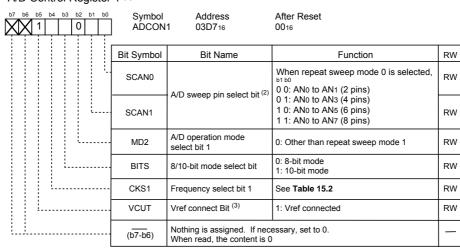

A/D Control Register 2(1)

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbol<br>ADCON | Address<br>2 03D4 <sub>16</sub>                         | After Reset<br>0016                                       |    |

|-------------------------|-----------------|---------------------------------------------------------|-----------------------------------------------------------|----|

|                         | Bit Symbol      | Bit Name                                                | Function                                                  | RV |

|                         | SMP             | A/D conversion method<br>select bit                     | 0: Without sample and hold<br>1: With sample and hold     | RV |

|                         | ADGSEL0         | A/D input group select bit                              | 0 0: Select port P10 group<br>0 1: Select port P9 group   | RV |

|                         | ADGSEL1         |                                                         | 1 0: Select port P0 group<br>1 1: Select port P1/P9 group | RV |

|                         | (b3)            | Reserved bit                                            | Set to 0                                                  | RV |

|                         | CKS2            | Frequency select bit 2                                  | See Table 15.2                                            | RV |

|                         | TRG1            | Trigger select bit                                      | Set to 0 in repeat sweep mode 0                           | RV |

| <u>   </u>              | (b7-b6)         | Nothing is assigned. If nec When read, the content is 0 |                                                           | -  |

1. If the ADCON2 register is rewritten during A/D conversion, the conversion result will be undefined.

### Figure 15.13 ADCON0 to ADCON2 Registers in Repeat Sweep Mode 0

RENESAS

# 15.1.7 Delayed Trigger Mode 0

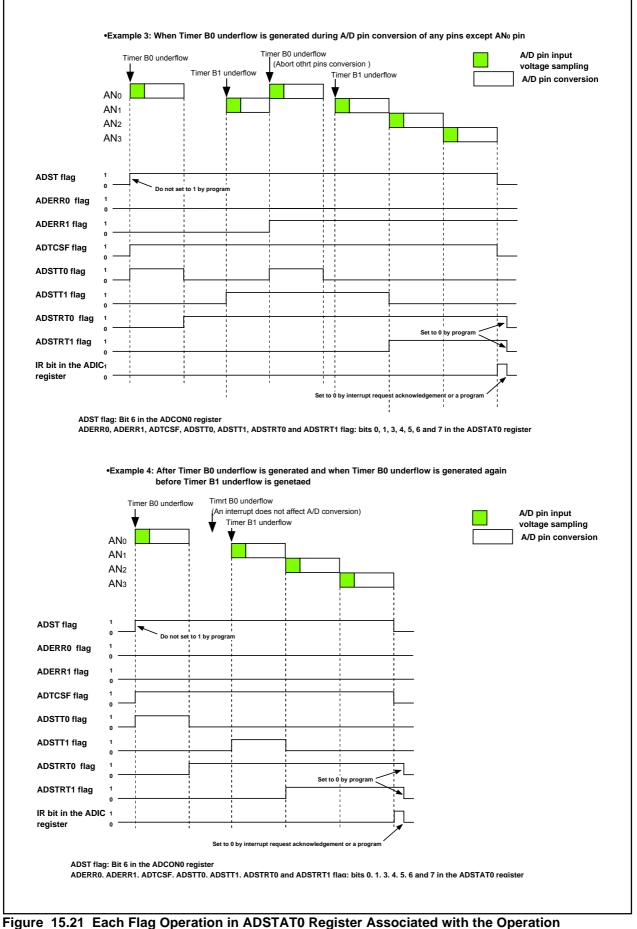

In delayed trigger mode 0, analog voltages applied to the selected pins are converted one-by-one to a digital code. The delayed trigger mode 0 used in combination with A/D trigger mode of Timer B. The Timer B0 underflow starts a single sweep conversion. After completing the ANo pin conversion, the AN1 pin is not sampled and converted until the Timer B1 underflow is generated. When the Timer B1 underflow is generated, the single sweep conversion is restarted with the AN1 pin. **Table 15.10** shows the delayed trigger mode 0 specifications. **Figure 15.19** shows the operation example in delayed trigger mode 0. **Figures 15.20** and **15.21** show each flag operation in the ADSTAT0 register that corresponds to the operation example. **Figure 15.22** shows registers ADCON0 to ADCON2 in delayed trigger mode 0. **Figure 15.23** shows the ADTRGCON register in delayed trigger mode 0 and **Table 15.11** shows the trigger select bit setting in delayed trigger mode 0.

| Item                      | Specification                                                                          |

|---------------------------|----------------------------------------------------------------------------------------|

| Function                  | Bits SCAN1 and SCAN0 in the ADCON1 register and bits ADGSEL1 and ADGSEL0               |

|                           | in the ADCON2 register select pins. Analog voltage applied to the input voltage of     |

|                           | the selected pins are converted one-by-one to the digital code. At this time, timer B0 |

|                           | underflow generation starts ANo pin conversion. Timer B1 underflow generation          |

|                           | starts conversion after the AN1 pin. <sup>(1)</sup>                                    |

| A/D Conversion Start      | ANo pin conversion start condition                                                     |

|                           | •When Timer B0 underflow is generated if Timer B0 underflow is generated again         |

|                           | before Timer B1 underflow is generated , the conversion is not affected                |

|                           | •When Timer B0 underflow is generated during A/D conversion of pins after the          |

|                           | AN1 pin, conversion is halted and the sweep is restarted from the AN0 pin again        |

|                           | AN1 pin conversion start condition                                                     |

|                           | •When Timer B1 underflow is generated during A/D conversion of the ANo pin, the        |

|                           | input voltage of the AN1 pin is sampled. The AN1 conversion and the rest of the        |

|                           | sweep start when AN <sub>0</sub> conversion is completed.                              |

| A/D Conversion Stop       | •When single sweep conversion from the AN0 pin is completed                            |

| Condition                 | •Set the ADST bit to 0 (A/D conversion halted) <sup>(2)</sup>                          |

| Interrupt request         | A/D conversion completed                                                               |

| generation timing         |                                                                                        |

| Analog input pin          | Select from AN0 to AN1 (2 pins), AN0 to AN3 (4 pins), AN0 to AN5 (6 pins)              |

|                           | and AN₀ to AN⁊ (8 pins) <sup>(3)</sup>                                                 |

| Readout of A/D conversion | Readout one of registers AN0 to AN7 that corresponds to the selected pins              |

| result                    |                                                                                        |

### Table 15.10 Delayed Trigger Mode 0 Specifications

NOTES:

- 1. Set the larger value than the value of the timer B0 register to the timer B1 register. The count source for timer B0 and timer B1 must be the same.

- 2. Do not write 1 (A/D conversion started) to the ADST bit in delayed trigger mode 0. When write 1, unexpected interrupts may be generated.

- 3. AN00 to AN07, AN 20 to AN27, and AN30 to AN32 can be used in the same way as AN0 to AN7. However, all input pins need to belong to the same group.

Example in Delayed Trigger Mode 0 (2)

RENESAS

# 20.3 Functions To Prevent Flash Memory from Rewriting

The flash memory has a built-in ROM code protect function for parallel I/O mode and a built-in ID code check function for standard input/output mode to prevent the flash memory from reading or rewriting.

# 20.3.1 ROM Code Protect Function

The ROM code protect function disables reading or changing the contents of the on-chip flash memory in parallel I/O mode. **Figure 20.4** shows the ROMCP address. The ROMCP address is located in a user ROM area. To enable ROM code protect, set the ROMCP1 bit to "002", "012", or "102" and set the bit 5 to bit 0 to "1111112".

To cancel ROM code protect, erase the block including the the ROMCP register in CPU rewrite mode or standard serial I/O mode.

# 20.3.2 ID Code Check Function

Use the ID code check function in standard serial input/output mode. Unless the flash memory is blank, the ID code sent from the programmer and the 7-byte ID code written in the flash memory are compared for match. If the ID codes do not match, the commands sent from the programmer are not acknowledged. The ID code consists of 8-bit data, starting with the first byte, into addresses, 0FFFDF16, 0FFFE316, 0FFFE316, 0FFFE316, 0FFFF316, 0FFFF716, and 0FFFFB16. The flash memory must have a program with the ID code set in these addresses.

# **20.5 Register Description**

**Figure 20.6** shows the flash memory control register 0 and flash memory control register 1. **Figure 20.7** shows the flash memory control register 4.

# 20.5.1 Flash Memory Control Register 0 (FMR0)

# •FMR 00 Bit

The FMR00 bit indicates the operating state of the flash memory. Its value is 0 while the program, erase, or erase-suspend command is being executed, otherwise, it is 1.

# •FMR01 Bit

The MCU can accept commands when the FMR01 bit is set to 1 (CPU rewrite mode). To set the FMR01 bit to 1, first set it to 0 and then 1. The FMR01 bit is set to 0 only by writing 0.

# •FMR02 Bit

The combined settings of bits FMR02 and FMR16 enable program and erase in the user ROM area. See **Table 20.4** for setting details. To set the FMR02 bit to 1, first set it to 0 and then 1. The FMR02 bit is valid only when the FMR01 bit is set to 1 (CPU rewrite mode enable).

# •FMSTP Bit

The FMSTP bit initializes the flash memory control circuits and minimizes power consumption in the flash memory. Access to the on-chip flash memory is disabled when the FMSTP bit is set to 1. Set the FMSTP bit by program in a space other than the flash memory.

Set the FMSTP bit to 1 if one of the following occurs:

•A flash memory access error occurs during erasing or programming in EW mode 0 (FMR00 bit does not switch back to 1 (ready)).

•Low-power consumption mode or on-chip oscillator low-power consumption mode is entered.

**Figure 20.10** shows a flow chart illustrating how to start and stop the flash memory before and after entering low power mode. Follow the procedure in this flow chart.

When entering stop or wait mode while the CPU rewrite mode is disabled, do not set the FMR0 register because the on-chip flash memory is automatically turned off and turned back on when exiting.

# •FMR06 Bit

The FMR06 bit is a read-only bit indicating an auto-program operation state. The FMR06 bit is set to 1 when a program error occurs; otherwise, it is set to 0. For details, refer to **20.8.4 Full Status Check**.

# •FMR07 Bit

The FMR07 bit is a read-only bit indicating an auto-erase operation status. The FMR07 bit is set to 1 when an erase error occurs; otherwise, it is set to 0. For details, refer to **20.8.4 Full Status Check**.

Figure 20.8 shows a EW mode 0 set/reset flowchart, Figure 20.9 shows a EW mode 1 set/reset flowchart.

# 20.9 Standard Serial I/O Mode

In standard serial I/O mode, the serial programmer supporting the M16C/29 group can be used to rewrite the flash memory user ROM area, while the MCU is mounted on a board. For more information about the serial programmer, contact your serial programmer manufacturer. Refer to the user's manual included with your serial programmer for instruction.

**Table 20.8** lists pin description (flash memory standard serial input/output mode). **Figures 20.15** and **20.16** show pin connections for standard serial input/output mode.

# 20.9.1 ID Code Check Function

The ID code check function determines whether or not the ID codes sent from the serial programmer matches those written in the flash memory. (Refer to **20.3 Functions To Prevent Flash Memory from Rewriting**.)

| Symbol   |                                                | Parameter                                                    |                                           |                         |        | Stand  | lard        | Unit |

|----------|------------------------------------------------|--------------------------------------------------------------|-------------------------------------------|-------------------------|--------|--------|-------------|------|

| Symbol   |                                                | F                                                            | arameter                                  |                         | Min.   | Тур.   | Max.        |      |

| Vcc      | Supply Voltage                                 |                                                              |                                           | 2.7                     |        | 5.5    | V           |      |

| AVcc     | Analog Supply Vo                               | ltage                                                        |                                           |                         |        | Vcc    |             | V    |

| Vss      | Supply Voltage                                 |                                                              |                                           |                         |        | 0      |             | V    |

| AVss     | Analog Supply Vo                               | ltage                                                        |                                           |                         |        | 0      |             | V    |

| Vih      | Input High ("H")                               | P00 to P07, P10 t                                            | o P17, P20 to P27, P                      | 30 to P37, P60 to P67,  | 0.7Vcc |        | Vcc         | V    |

|          | Voltage                                        | P70 to P77, P80 t                                            | o P87, P90 to P93, P                      | 95 to P97, P100 to P107 |        |        |             |      |

|          |                                                | XIN, RESET, CI                                               | IVSS                                      |                         | 0.8Vcc |        | Vcc         | V    |

|          |                                                |                                                              | When I <sup>2</sup> C bus input           | t level is selected     | 0.7Vcc |        | Vcc         | V    |

|          |                                                | SDAMM, SCLMM                                                 | When SMBUS inpu                           | It level is selected    | 1.4    |        | Vcc         | V    |

| VIL      | Input Low ("L")                                | P00 to P07, P10 t                                            | o P17, P20 to P27, P                      | 30 to P37, P60 to P67,  | 0      |        | 0.3Vcc      | V    |

|          | Voltage                                        | P70 to P77, P80 t                                            | o P87, P90 to P93, P                      | 95 to P97, P100 to P107 |        |        |             |      |

|          |                                                | XIN, RESET, CN                                               | IVSS                                      |                         | 0      |        | 0.2Vcc      | V    |

|          |                                                |                                                              | When I <sup>2</sup> C bus input           | t level is selected     | 0      |        | 0.3Vcc      | V    |

|          |                                                | SDAMM, SCLMM                                                 | When SMBUS inpu                           | It level is selected    | 0      |        | 0.6         | V    |

| OH(peak) | Peak Output High                               | P00 to P07, P10 t                                            | o P17, P20 to P27, P                      | 30 to P37, P60 to P67,  |        |        | -10.0       | mA   |

|          | ("H") Current                                  | P70 to P77, P80 to P87, P90 to P93, P95 to P97, P100 to P107 |                                           |                         |        |        |             |      |

| OH(avg)  | Average Output                                 |                                                              |                                           |                         |        | -5.0   | mA          |      |

|          | High ("H") Current                             | P70 to P77, P80 t                                            | P87, P90 to P93, P95 to P97, P100 to P107 |                         |        |        |             |      |

| OL(peak) | Peak Output Low                                | P00 to P07, P10 t                                            | o P17, P20 to P27, P                      | 30 to P37, P60 to P67,  |        |        | 10.0        | mA   |

|          | ("L") Current                                  |                                                              |                                           | 95 to P97, P100 to P107 |        |        |             |      |

| OL(avg)  | Average Output                                 |                                                              |                                           | 30 to P37, P60 to P67,  |        |        | 5.0         | mA   |

|          | Low ("L") Current                              |                                                              |                                           | 95 to P97, P100 to P107 |        |        |             |      |

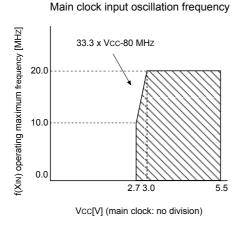

| f(XiN)   | Main Clock Input                               | Oscillation Freque                                           | ency <sup>(4)</sup>                       | Vcc=3.0 to 5.5V         | 0      |        | 20          | MHz  |

|          |                                                |                                                              |                                           | Vcc=2.7 to 3.0V         | 0      |        | 33 X Vcc-80 | MHz  |

| f(Xcin)  | Sub Clock Oscilla                              |                                                              |                                           |                         |        | 32.768 | 50          | kHz  |

| f1(ROC)  | On-chip Oscillator                             | Frequency 1                                                  |                                           |                         | 0.5    | 1      | 2           | MHz  |

| f2(ROC)  | On-chip Oscillator Frequency 2                 |                                                              |                                           |                         | 1      | 2      | 4           | MHz  |

| f3(ROC)  | On-chip Oscillator                             | o Oscillator Frequency 3                                     |                                           |                         |        | 16     | 26          | MHz  |

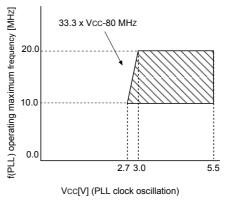

| f(PLL)   | PLL Clock Oscillation Frequency <sup>(4)</sup> |                                                              | Vcc=3.0 to 5.5V                           | 10                      |        | 20     | MHz         |      |

|          |                                                | V∞=2.7 to 3.0V                                               |                                           |                         |        |        | 33 X Vcc-80 | MHz  |

| f(BCLK)  | CPU Operation C                                | lock Frequency                                               |                                           | 1                       | 0      |        | 20          | MHz  |

| tsu(PLL) | Wait Time to Stab                              | ilize PLL Frequer                                            | ncy Synthesizer                           | Vcc=5.0V                |        |        | 20          | ms   |

|          |                                                |                                                              |                                           | Vcc=3.0V                |        |        | 50          | ms   |

# Table 21.2 Recommended Operating Conditions (Note 1)

NOTES:

1. Referenced to V $\infty$  = 2.7 to 5.5V at Topr = -20 to 85 ° C / -40 to 85 ° C unless otherwise specified. 2. The mean output current is the mean value within 100ms.

3. The total IOL(peak) for all ports must be 80mA or less. The total IOH(peak) for all ports must be -80mA or less.

4. Relationship among main clock oscillation frequency, PLL clock oscillation frequency and supply voltage.

# 22.6.1.4 Timer A (Pulse Width Modulation Mode)

- The timer remains idle after reset. Set the mode, count source, counter value, etc. using bits TA0TGL and TA0TGH in the TAiMR (i = 0 to 4) register, the TAi register, the ONSF register and the TRGSR register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure bits TA0TGL and TA0TGH in the TAiMR register, the ONSF register and the TRGSR register are modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. The IR bit is set to 1 when setting a timer operation mode with any of the following procedures:

- Select the PWM mode after reset.

- Change an operation mode from timer mode to PWM mode.

- Change an operation mode from event counter mode to PWM mode.

To use the timer Ai interrupt (interrupt request bit), set the IR bit to 0 by program after the above listed changes have been made.

- 3. When setting TAiS register to 0 (count stop) during PWM pulse output, the following action occurs:Stop counting.

- When TAiout pin is output "H", output level is set to "L" and the IR bit is set to 1.

- When TAiout pin is output "L", both output level and the IR bit remains unchanged.

- 4. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

# **REVISION HISTORY**

# M16C/29 Hardware Manual

| Rev. | Date        |      | Description                                                                      |

|------|-------------|------|----------------------------------------------------------------------------------|

|      |             | Page | Summary                                                                          |

| 0.70 | Mar/ 29/Y04 | 1    | "1. Overview" and "1.1. Application" are partly revised.                         |

|      |             | 2, 3 | Table 1.2.1 and 1.2.2 are partly revised.                                        |

|      |             | 8, 9 | Figure 1.5.1 and 1.5.2 are partly revised.                                       |

|      |             | 10   | Table 1.6.1 is revised.                                                          |

|      |             | 22   | Figure 4.8 is partly revised.                                                    |

|      |             | 28   | Section "5.5 Voltage Detection Circuit" and Figure 5.5.2 are partly revised.     |

|      |             | 30   | Figure 5.5.3 is partly revised.                                                  |

|      |             | 31   | Figure 5.5.4 is partly revised.                                                  |

|      |             | 32   | Section "5.5.1 Voltage Detection Interrupt" and "5.5.1.1.1 Limitations of Stop   |

|      |             |      | Mode" are partly revised.                                                        |

|      |             | 36   | Figure 7.1 is partly revised.                                                    |

|      |             | 37   | Figure 7.2 is partly revised.                                                    |

|      |             | 38   | Figure 7.3 is partly revised.                                                    |

|      |             | 39   | Figure 7.5 is partly revised.                                                    |

|      |             | 40   | Figure 7.6 is partly revised.                                                    |

|      |             | 41   | "CCLKR register" of Figure 7.7 is partly revised.                                |

|      |             | 42   | Section "7.1 Main clock" is partly revised.                                      |

|      |             | 45   | Figure 7.4.1 is partly revised.                                                  |

|      |             | 46   | Section "7.5 CPU Clock and Peripheral Function Clock" and "7.5.2 Peripheral      |

|      |             |      | Function Clock" are partly revised.                                              |

|      |             | 54   | Section "7.7 System Clock Protective Function" and "7.8 Oscillation Stop and Re- |

|      |             |      | oscillation Detect Function" are partly revised.                                 |

|      |             | 57   | Figure 8.1 is partly revised.                                                    |

|      |             | 64   | Figure 9.3.1 is partly revised.                                                  |

|      |             | 65   | IFSR2A registerin Figure 9.3.2 is partly revised.                                |

|      |             | 66   | Section "9.3.2 IR Bit" is partly revised.                                        |

|      |             | 67   | Section "9.4 Interrupt Sequence" is partly revised.                              |

|      |             | 68   | Section "9.4.1 Interrupt Response Time" and Figure 9.4.1.1 are partly revised.   |

|      |             | 73   | Section "9.6 INT Interrupt" is partly revised.                                   |

|      |             | 74   | Section "9.9 CAN0 Wake-up Interrupt" is partly revised.                          |

|      |             | 94   | "Divide ratio" of Table 12.1.1.1 is partly revised.                              |

|      |             | 102  | "8-bit PWM" of Table 12.1.4.1 is partly revised.                                 |

|      |             | 106  | "Timer Bi register" in Figure 12.2.3 is partly revised.                          |

|      |             | 111  | Section "12.2.4 A-D Trigger mode" and Table 12.2.4.1 are partly revised.         |

|      |             | 112  | Figure 12.2.4.2 is partly revised.                                               |

|      |             | 115  | Figure 12.3.2 is partly revised.                                                 |

|      |             | 117  | "Timer B2 interrupt occurences fequency set counter" in Figure 12.3.4 is partly  |

|      |             |      | revised.                                                                         |

|      |             | 119  | Figure 12.3.6 is partly revised.                                                 |