# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | e200z6                                                               |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 132MHz                                                               |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                            |

| Peripherals                | DMA, POR, PWM, WDT                                                   |

| Number of I/O              | 256                                                                  |

| Program Memory Size        | 2MB (2M x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 64K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.35V ~ 1.65V                                                        |

| Data Converters            | A/D 40x12b                                                           |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 416-BBGA                                                             |

| Supplier Device Package    | 416-PBGA (27x27)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/sc5554mvr132 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

The MPC5500 family of parts contains many new features coupled with high performance CMOS technology to provide significant performance improvement over the MPC565.

The MPC5554 has two levels of memory hierarchy. The fastest accesses are to the 32-kilobytes (KB) unified cache. The next level in the hierarchy contains the 64-KB on-chip internal SRAM and two-megabytes (MB) internal flash memory. The internal SRAM and flash memory hold instructions and data. The external bus interface is designed to support most of the standard memories used with the MPC5*xx* family.

The complex input/output timer functions of the MPC5554 are performed by two enhanced time processor unit (eTPU) engines. Each eTPU engine controls 32 hardware channels, providing a total of 64 hardware channels. The eTPU has been enhanced over the TPU by providing: 24-bit timers, double-action hardware channels, variable number of parameters per channel, angle clock hardware, and additional control and arithmetic instructions. The eTPU is programmed using a high-level programming language.

The less complex timer functions of the MPC5554 are performed by the enhanced modular input/output system (eMIOS). The eMIOS' 24 hardware channels are capable of single-action, double-action, pulse-width modulation (PWM), and modulus-counter operations. Motor control capabilities include edge-aligned and center-aligned PWM.

Off-chip communication is performed by a suite of serial protocols including controller area networks (FlexCANs), enhanced deserial/serial peripheral interfaces (DSPIs), and enhanced serial communications interfaces (eSCIs). The DSPIs support pin reduction through hardware serialization and deserialization of timer channels and general-purpose input/output (GPIOs) signals.

The MCU has an on-chip enhanced queued dual analog-to-digital converter (eQADC). 324 s40-channels.

The system integration unit (SIU) performs several chip-wide configuration functions. Pad configuration and general-purpose input and output (GPIO) are controlled from the SIU. External interrupts and reset control are also determined by the SIU. The internal multiplexer submodule provides multiplexing of eQADC trigger sources, daisy chaining the DSPIs, and external interrupt signal multiplexing.

## 3 Electrical Characteristics

This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications for the MCU.

## 3.1 Maximum Ratings

| Spec | Characteristic                                                                                           | Symbol                               | Min.                                   | Max.                                 | Unit |

|------|----------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|--------------------------------------|------|

| 1    | 1.5 V core supply voltage <sup>2</sup>                                                                   | V <sub>DD</sub>                      | -0.3                                   | 1.7                                  | V    |

| 2    | Flash program/erase voltage                                                                              | V <sub>PP</sub>                      | -0.3                                   | 6.5                                  | V    |

| 4    | Flash read voltage                                                                                       | V <sub>FLASH</sub>                   | -0.3                                   | 4.6                                  | V    |

| 5    | SRAM standby voltage                                                                                     | V <sub>STBY</sub>                    | -0.3                                   | 1.7                                  | V    |

| 6    | Clock synthesizer voltage                                                                                | V <sub>DDSYN</sub>                   | -0.3                                   | 4.6                                  | V    |

| 7    | 3.3 V I/O buffer voltage                                                                                 | V <sub>DD33</sub>                    | -0.3                                   | 4.6                                  | V    |

| 8    | Voltage regulator control input voltage                                                                  | V <sub>RC33</sub>                    | -0.3                                   | 4.6                                  | V    |

| 9    | Analog supply voltage (reference to V <sub>SSA</sub> )                                                   | V <sub>DDA</sub>                     | -0.3                                   | 5.5                                  | V    |

| 10   | I/O supply voltage (fast I/O pads) <sup>3</sup>                                                          | V <sub>DDE</sub>                     | -0.3                                   | 4.6                                  | V    |

| 11   | I/O supply voltage (slow and medium I/O pads) $^3$                                                       | V <sub>DDEH</sub>                    | -0.3                                   | 6.5                                  | V    |

| 12   | DC input voltage <sup>4</sup><br>V <sub>DDEH</sub> powered I/O pads<br>V <sub>DDE</sub> powered I/O pads | V <sub>IN</sub>                      | -1.0 <sup>5</sup><br>-1.0 <sup>5</sup> | 6.5 <sup>6</sup><br>4.6 <sup>7</sup> | v    |

| 13   | Analog reference high voltage (reference to V <sub>RL</sub> )                                            | V <sub>RH</sub>                      | -0.3                                   | 5.5                                  | V    |

| 14   | $V_{SS}$ to $V_{SSA}$ differential voltage                                                               | $V_{SS} - V_{SSA}$                   | -0.1                                   | 0.1                                  | V    |

| 15   | V <sub>DD</sub> to V <sub>DDA</sub> differential voltage                                                 | $V_{DD} - V_{DDA}$                   | -V <sub>DDA</sub>                      | V <sub>DD</sub>                      | V    |

| 16   | V <sub>REF</sub> differential voltage                                                                    | V <sub>RH</sub> – V <sub>RL</sub>    | -0.3                                   | 5.5                                  | V    |

| 17   | V <sub>RH</sub> to V <sub>DDA</sub> differential voltage                                                 | V <sub>RH</sub> – V <sub>DDA</sub>   | -5.5                                   | 5.5                                  | V    |

| 18   | V <sub>RL</sub> to V <sub>SSA</sub> differential voltage                                                 | V <sub>RL</sub> – V <sub>SSA</sub>   | -0.3                                   | 0.3                                  | V    |

| 19   | V <sub>DDEH</sub> to V <sub>DDA</sub> differential voltage                                               | V <sub>DDEH</sub> – V <sub>DDA</sub> | -V <sub>DDA</sub>                      | V <sub>DDEH</sub>                    | V    |

| 20   | $V_{DDF}$ to $V_{DD}$ differential voltage                                                               | $V_{DDF} - V_{DD}$                   | -0.3                                   | 0.3                                  | V    |

| 21   | $V_{\text{RC33}}$ to $V_{\text{DDSYN}}$ differential voltage spec has been moved to                      | Table 9 DC Electric                  | al Specificatio                        | ons, Spec 43a                        |      |

| 22   | $V_{SSSYN}$ to $V_{SS}$ differential voltage                                                             | $V_{\rm SSSYN} - V_{\rm SS}$         | -0.1                                   | 0.1                                  | V    |

| 23   | V <sub>RCVSS</sub> to V <sub>SS</sub> differential voltage                                               | $V_{RCVSS} - V_{SS}$                 | -0.1                                   | 0.1                                  | V    |

| 24   | Maximum DC digital input current <sup>8</sup><br>(per pin, applies to all digital pins) <sup>4</sup>     | I <sub>MAXD</sub>                    | -2                                     | 2                                    | mA   |

| 25   | Maximum DC analog input current <sup>9</sup><br>(per pin, applies to all analog pins)                    | I <sub>MAXA</sub>                    | -3                                     | 3                                    | mA   |

| 26   | Maximum operating temperature range <sup>10</sup><br>Die junction temperature                            | Т <sub>Ј</sub>                       | ΤL                                     | 150.0                                | °C   |

| 27   | Storage temperature range                                                                                | T <sub>STG</sub>                     | -55.0                                  | 150.0                                | °C   |

### Table 2. Absolute Maximum Ratings <sup>1</sup>

| Spec | Characteristic                                                                   | Symbol           | Min. | Max.           | Unit |

|------|----------------------------------------------------------------------------------|------------------|------|----------------|------|

| 28   | Maximum solder temperature <sup>11</sup><br>Lead free (Pb-free)<br>Leaded (SnPb) | T <sub>SDR</sub> |      | 260.0<br>245.0 | °C   |

| 29   | Moisture sensitivity level <sup>12</sup>                                         | MSL              | —    | 3              |      |

Table 2. Absolute Maximum Ratings <sup>1</sup> (continued)

<sup>1</sup> Functional operating conditions are given in the DC electrical specifications. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond any of the listed maxima can affect device reliability or cause permanent damage to the device.

- <sup>2</sup> 1.5 V  $\pm$  10% for proper operation. This parameter is specified at a maximum junction temperature of 150 °C.

- <sup>3</sup> All functional non-supply I/O pins are clamped to V<sub>SS</sub> and V<sub>DDE</sub>, or V<sub>DDEH</sub>.

- <sup>4</sup> AC signal overshoot and undershoot of up to ± 2.0 V of the input voltages is permitted for an accumulative duration of 60 hours over the complete lifetime of the device (injection current not limited for this duration).

- <sup>5</sup> Internal structures hold the voltage greater than -1.0 V if the injection current limit of 2 mA is met. Keep the negative DC voltage greater than -0.6 V on eTPUB[15] and SINB during the internal power-on reset (POR) state.

- <sup>6</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDEH</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDEH</sub> is within the operating voltage specifications.

- <sup>7</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDE</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDE</sub> is within the operating voltage specifications.

- <sup>8</sup> Total injection current for all pins (including both digital and analog) must not exceed 25 mA.

- <sup>9</sup> Total injection current for all analog input pins must not exceed 15 mA.

- <sup>10</sup> Lifetime operation at these specification limits is not guaranteed.

- <sup>11</sup> Moisture sensitivity profile per IPC/JEDEC J-STD-020D.

<sup>12</sup> Moisture sensitivity per JEDEC test method A112.

## 3.2 Thermal Characteristics

The shaded rows in the following table indicate information specific to a four-layer board.

### Table 3. MPC5554 Thermal Characteristics

| Spec | MPC5554 Thermal Characteristic                                                   | Symbol              | 416 PBGA | Unit |

|------|----------------------------------------------------------------------------------|---------------------|----------|------|

| 1    | Junction to ambient <sup>1, 2</sup> , natural convection (one-layer board)       | $R_{	ext{	heta}JA}$ | 24       | °C/W |

| 2    | Junction to ambient <sup>1, 3</sup> , natural convection (four-layer board 2s2p) | $R_{	ext{	heta}JA}$ | 18       | °C/W |

| 3    | Junction to ambient <sup>1, 3</sup> (@200 ft./min., one-layer board)             | R <sub>0JMA</sub>   | 19       | °C/W |

| 4    | Junction to ambient <sup>1, 3</sup> (@200 ft./min., four-layer board 2s2p)       | R <sub>0JMA</sub>   | 15       | °C/W |

| 5    | Junction to board <sup>4</sup> (four-layer board 2s2p)                           | $R_{\theta JB}$     | 9        | °C/W |

| 6    | Junction to case <sup>5</sup>                                                    | $R_{	ext{	heta}JC}$ | 5        | °C/W |

| 7    | Junction to package top <sup>6</sup> , natural convection                        | Ψ <sub>JT</sub>     | 2        | °C/W |

<sup>1</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

- <sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

- <sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

| Spec | Characte                                                                                                                                                                        | Symbol                | Min.               | Max.             | Units |   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|------------------|-------|---|

| 8    | Voltage differential during power up su<br>V <sub>DD33</sub> can lag V <sub>DDSYN</sub> or V <sub>DDEH6</sub> befo<br>V <sub>POR33</sub> and V <sub>POR5</sub> minimums respect | V <sub>DD33_LAG</sub> | _                  | 1.0              | v     |   |

| 9    | Absolute value of slew rate on power s                                                                                                                                          | _                     | _                  | 50               | V/ms  |   |

|      | Required gain at Tj:                                                                                                                                                            | – 55° C <sup>7</sup>  |                    | 70               |       | — |

| 10   | $I_{DD} \div I_{VRCCTL} (@ f_{sys} = f_{MAX})^{6, 8, 9, 10}$                                                                                                                    | – 40 <sup>o</sup> C   | DET 11             | 70               | _     | — |

| 10   |                                                                                                                                                                                 | 25° C                 | BETA <sup>11</sup> | 85 <sup>11</sup> | —     | _ |

|      |                                                                                                                                                                                 |                       | 105 <sup>11</sup>  | 500              | —     |   |

The internal POR signals are  $V_{POR15}$ ,  $V_{POR33}$ , and  $V_{POR5}$ . On power up, assert **RESET** before the internal POR negates. **RESET** must remain asserted until the power supplies are within the operating conditions as specified in Table 9 DC Electrical Specifications. On power down, assert **RESET** before any power supplies fall outside the operating conditions and until the internal POR asserts.

- $^2$  V<sub>IL S</sub> (Table 9, Spec15) is guaranteed to scale with V<sub>DDEH6</sub> down to V<sub>POR5</sub>.

- <sup>3</sup> Supply full operating current for the 1.5 V supply when the 3.3 V supply reaches this range.

- <sup>4</sup> It is possible to reach the current limit during ramp up—do not treat this event as short circuit current.

- <sup>5</sup> At peak current for device.

- <sup>6</sup> Requires compliance with Freescale's recommended board requirements and transistor recommendations. Board signal traces/routing from the V<sub>RCCTL</sub> package signal to the base of the external pass transistor and between the emitter of the pass transistor to the V<sub>DD</sub> package signals must have a maximum of 100 nH inductance and minimal resistance (less than 1  $\Omega$ ). V<sub>RCCTL</sub> must have a nominal 1  $\mu$ F phase compensation capacitor to ground. V<sub>DD</sub> must have a 20  $\mu$ F (nominal) bulk capacitor (greater than 4  $\mu$ F over all conditions, including lifetime). Place high-frequency bypass capacitors consisting of eight 0.01  $\mu$ F, two 0.1  $\mu$ F, and one 1  $\mu$ F capacitors around the package on the V<sub>DD</sub> supply signals.

- $^7$  Only available on devices that support -55° C.

- <sup>8</sup>  $I_{VRCCTL}$  is measured at the following conditions:  $V_{DD} = 1.35$  V,  $V_{RC33} = 3.1$  V,  $V_{VRCCTL} = 2.2$  V.

- <sup>9</sup> Refer to Table 1 for the maximum operating frequency.

<sup>10</sup> Values are based on I<sub>DD</sub> from high-use applications as explained in the I<sub>DD</sub> Electrical Specification.

<sup>11</sup> BETA represents the worst-case external transistor. It is measured on a per-part basis and calculated as (I<sub>DD</sub> ÷ I<sub>VRCCTL</sub>).

## 3.7 Power-Up/Down Sequencing

Power sequencing between the 1.5 V power supply and  $V_{DDSYN}$  or the RESET power supplies is required if using an external 1.5 V power supply with  $V_{RC33}$  tied to ground (GND). To avoid power-sequencing,  $V_{RC33}$  must be powered up within the specified operating range, even if the on-chip voltage regulator controller is not used. Refer to Section 3.7.2, "Power-Up Sequence (VRC33 Grounded)," and Section 3.7.3, "Power-Down Sequence (VRC33 Grounded)."

Power sequencing requires that  $V_{DD33}$  must reach a certain voltage where the values are read as ones before the POR signal negates. Refer to Section 3.7.1, "Input Value of Pins During POR Dependent on VDD33."

Although power sequencing is not required between  $V_{RC33}$  and  $V_{DDSYN}$  during power up,  $V_{RC33}$  must not lead  $V_{DDSYN}$  by more than 600 mV or lag by more than 100 mV for the  $V_{RC}$  stage turn-on to operate within specification. Higher spikes in the emitter current of the pass transistor occur if  $V_{RC33}$  leads or lags  $V_{DDSYN}$  by more than these amounts. The value of that higher spike in current depends on the board power supply circuitry and the amount of board level capacitance.

To avoid this condition, minimize the ramp time of the  $V_{DD}$  supply to a time period less than the time required to enable the external circuitry connected to the device outputs.

During initial power ramp-up, when Vstby is 0.6v or above. a typical current of 1-3mA and maximum of 4mA may be seen until  $V_{DD}$  is applied. This current will not reoccur until  $V_{stby}$  is lowered below  $V_{stby}$  min. specification.

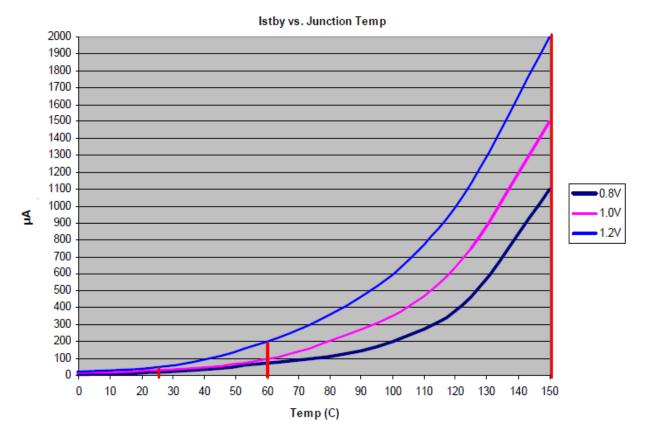

Figure 2 shows an approximate interpolation of the  $I_{STBY}$  worst-case specification to estimate values at different voltages and temperatures. The vertical lines shown at 25 °C, 60 °C, and 150 °C in Figure 2 are the actual  $I_{DD}$  STBY specifications (27d) listed in Table 9.

Figure 2. fISTBY Worst-case Specifications

## 3.7.1 Input Value of Pins During POR Dependent on V<sub>DD33</sub>

When powering up the device,  $V_{DD33}$  must not lag the latest  $V_{DDSYN}$  or RESET power pin ( $V_{DDEH6}$ ) by more than the  $V_{DD33}$  lag specification listed in Table 6, spec 8. This avoids accidentally selecting the bypass clock mode because the internal versions of PLLCFG[0:1] and RSTCFG are not powered and therefore cannot read the default state when POR negates.  $V_{DD33}$  can lag  $V_{DDSYN}$  or the RESET power pin ( $V_{DDEH6}$ ), but cannot lag both by more than the  $V_{DD33}$  lag specification. This  $V_{DD33}$  lag specification applies during power up only.  $V_{DD33}$  has no lead or lag requirements when powering down.

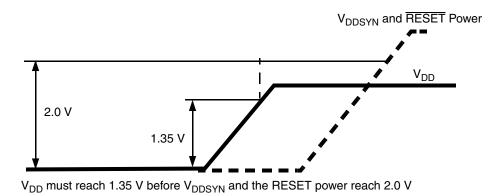

## 3.7.2 Power-Up Sequence (V<sub>RC33</sub> Grounded)

The 1.5 V V<sub>DD</sub> power supply must rise to 1.35 V before the 3.3 V V<sub>DDSYN</sub> power supply and the RESET power supply rises above 2.0 V. This ensures that digital logic in the PLL for the 1.5 V power supply does not begin to operate below the specified operation range lower limit of 1.35 V. Because the internal 1.5 V POR is disabled, the internal 3.3 V POR or the RESET power POR must hold the device in reset. Since they can negate as low as 2.0 V, V<sub>DD</sub> must be within specification before the 3.3 V POR and the RESET POR negate.

Figure 3. Power-Up Sequence (V<sub>RC33</sub> Grounded)

## 3.7.3 Power-Down Sequence (V<sub>RC33</sub> Grounded)

The only requirement for the power-down sequence with  $V_{RC33}$  grounded is if  $V_{DD}$  decreases to less than its operating range,  $V_{DDSYN}$  or the RESET power must decrease to less than 2.0 V before the  $V_{DD}$  power increases to its operating range. This ensures that the digital 1.5 V logic, which is reset only by an ORed POR and can cause the 1.5 V supply to decrease less than its specification value, resets correctly. See Table 6, footnote 1.

## 3.8 DC Electrical Specifications

### Table 9. DC Electrical Specifications ( $T_A = T_L$ to $T_H$ )

| Spec | Characteristic                                                                                                                 | Symbol                                                            | Min                                                                         | Max.                                             | Unit                 |

|------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|----------------------|

| 1    | Core supply voltage (average DC RMS voltage)                                                                                   | V <sub>DD</sub>                                                   | 1.35                                                                        | 1.65                                             | V                    |

| 2    | Input/output supply voltage (fast input/output) <sup>1</sup>                                                                   | V <sub>DDE</sub>                                                  | 1.62                                                                        | 3.6                                              | V                    |

| 3    | Input/output supply voltage (slow and medium input/output)                                                                     | V <sub>DDEH</sub>                                                 | 3.0                                                                         | 5.25                                             | V                    |

| 4    | 3.3 V input/output buffer voltage                                                                                              | V <sub>DD33</sub>                                                 | 3.0                                                                         | 3.6                                              | V                    |

| 5    | Voltage regulator control input voltage                                                                                        | V <sub>RC33</sub>                                                 | 3.0                                                                         | 3.6                                              | V                    |

| 6    | Analog supply voltage <sup>2</sup>                                                                                             | V <sub>DDA</sub>                                                  | 4.5                                                                         | 5.25                                             | V                    |

| 8    | Flash programming voltage <sup>3</sup>                                                                                         | V <sub>PP</sub>                                                   | 4.5                                                                         | 5.25                                             | V                    |

| 9    | Flash read voltage                                                                                                             | V <sub>FLASH</sub>                                                | 3.0                                                                         | 3.6                                              | V                    |

| 10   | SRAM standby voltage <sup>4</sup>                                                                                              | V <sub>STBY</sub>                                                 | 0.8                                                                         | 1.2                                              | V                    |

| 11   | Clock synthesizer operating voltage                                                                                            | V <sub>DDSYN</sub>                                                | 3.0                                                                         | 3.6                                              | V                    |

| 12   | Fast I/O input high voltage                                                                                                    | V <sub>IH_F</sub>                                                 | $0.65 \times V_{DDE}$                                                       | V <sub>DDE</sub> + 0.3                           | V                    |

| 13   | Fast I/O input low voltage                                                                                                     | V <sub>IL_F</sub>                                                 | V <sub>SS</sub> – 0.3                                                       | $0.35 \times V_{DDE}$                            | V                    |

| 14   | Medium and slow I/O input high voltage                                                                                         | edium and slow I/O input high voltage $V_{IH_S}$ 0.65 × $V_{DDI}$ |                                                                             | V <sub>DDEH</sub> + 0.3                          | V                    |

| 15   | Medium and slow I/O input low voltage                                                                                          | V <sub>IL_S</sub>                                                 | V <sub>SS</sub> – 0.3                                                       | $0.35 \times V_{DDEH}$                           | V                    |

| 16   | Fast input hysteresis                                                                                                          | V <sub>HYS_F</sub>                                                | $0.1 \times V_{DDE}$                                                        |                                                  | V                    |

| 17   | Medium and slow I/O input hysteresis                                                                                           | V <sub>HYS_S</sub>                                                | 0.1 ×                                                                       | V <sub>DDEH</sub>                                | V                    |

| 18   | Analog input voltage                                                                                                           | V <sub>INDC</sub>                                                 | V <sub>SSA</sub> – 0.3                                                      | V <sub>DDA</sub> + 0.3                           | V                    |

| 19   | Fast output high voltage (I <sub>OH_F</sub> = −2.0 mA)                                                                         | V <sub>OH_F</sub>                                                 | $0.8 \times V_{DDE}$                                                        | _                                                | V                    |

| 20   | Slow and medium output high voltage $I_{OH_S} = -2.0 \text{ mA}$<br>$I_{OH_S} = -1.0 \text{ mA}$                               | V <sub>OH_S</sub>                                                 | $\begin{array}{c} 0.80 \times V_{DDEH} \\ 0.85 \times V_{DDEH} \end{array}$ | _                                                | v                    |

| 21   | Fast output low voltage (I <sub>OL_F</sub> = 2.0 mA)                                                                           | V <sub>OL_F</sub>                                                 | —                                                                           | $0.2 \times V_{DDE}$                             | V                    |

| 22   | Slow and medium output low voltage $I_{OL_S} = 2.0 \text{ mA}$<br>$I_{OL_S} = 1.0 \text{ mA}$                                  | V <sub>OL_S</sub>                                                 | _                                                                           | $0.20 \times V_{DDEH}$<br>$0.15 \times V_{DDEH}$ | V                    |

| 23   | Load capacitance (fast I/O) <sup>5</sup><br>DSC (SIU_PCR[8:9]) = 0b00<br>= 0b01<br>= 0b10<br>= 0b11                            | CL                                                                | <br>                                                                        | 10<br>20<br>30<br>50                             | pF<br>pF<br>pF<br>pF |

| 24   | Input capacitance (digital pins)                                                                                               | C <sub>IN</sub>                                                   | —                                                                           | 7                                                | pF                   |

| 25   | Input capacitance (analog pins)                                                                                                | C <sub>IN_A</sub>                                                 | —                                                                           | 10                                               | pF                   |

| 26   | Input capacitance:<br>(Shared digital and analog pins AN[12]_MA[0]_SDS,<br>AN[13]_MA[1]_SDO, AN[14]_MA[2]_SDI, and AN[15]_FCK) | C <sub>IN_M</sub>                                                 | _                                                                           | 12                                               | pF                   |

| Spec | Characteristic                                                                                                                 | Symbol                                                                                                               | Min                    | Max.                               | Unit                       |

|------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------|----------------------------|

| 30   | Operating current V <sub>DDE</sub> supplies: <sup>12</sup><br>V <sub>DDEH1</sub><br>V <sub>DDE2</sub><br>V <sub>DDE3</sub>     | I <sub>DD1</sub><br>I <sub>DD2</sub><br>I <sub>DD3</sub>                                                             | <br><br>               | Refer to<br>footnote <sup>12</sup> | mA<br>mA<br>mA             |

|      | V <sub>DDEH4</sub><br>V <sub>DDE5</sub><br>V <sub>DDEH6</sub><br>V <sub>DDE7</sub><br>V <sub>DDEH8</sub><br>V <sub>DDEH9</sub> | I <sub>DD4</sub><br>I <sub>DD5</sub><br>I <sub>DD6</sub><br>I <sub>DD7</sub><br>I <sub>DD8</sub><br>I <sub>DD9</sub> | <br><br>               |                                    | mA<br>mA<br>mA<br>mA<br>mA |

| 31   | Fast I/O weak pullup current <sup>13</sup><br>1.62–1.98 V<br>2.25–2.75 V<br>3.00–3.60 V                                        | I <sub>ACT_F</sub>                                                                                                   | 10<br>20<br>20         | 110<br>130<br>170                  | μΑ<br>μΑ<br>μΑ             |

|      | Fast I/O weak pulldown current <sup>13</sup><br>1.62–1.98 V<br>2.25–2.75 V<br>3.00–3.60 V                                      | 'ACT_F                                                                                                               | 10<br>20<br>20         | 100<br>130<br>170                  | μΑ<br>μΑ<br>μΑ             |

| 32   | Slow and medium I/O weak pullup/down current <sup>13</sup><br>3.0–3.6 V<br>4.5–5.5 V                                           | I <sub>ACT_S</sub>                                                                                                   | 10<br>20               | 150<br>170                         | μ <b>Α</b><br>μΑ           |

| 33   | I/O input leakage current <sup>14</sup>                                                                                        | I <sub>INACT_D</sub>                                                                                                 | -2.5                   | 2.5                                | μΑ                         |

| 34   | DC injection current (per pin)                                                                                                 | I <sub>IC</sub>                                                                                                      | -2.0                   | 2.0                                | mA                         |

| 35   | Analog input current, channel off <sup>15</sup>                                                                                | I <sub>INACT_A</sub>                                                                                                 | -150                   | 150                                | nA                         |

| 35a  | Analog input current, shared analog / digital pins<br>(AN[12], AN[13], AN[14], AN[15])                                         | I <sub>INACT_AD</sub>                                                                                                | -2.5                   | 2.5                                | μA                         |

| 36   | $V_{SS}$ to $V_{SSA}$ differential voltage <sup>16</sup>                                                                       | $V_{SS} - V_{SSA}$                                                                                                   | -100                   | 100                                | mV                         |

| 37   | Analog reference low voltage                                                                                                   | V <sub>RL</sub>                                                                                                      | V <sub>SSA</sub> – 0.1 | V <sub>SSA</sub> + 0.1             | V                          |

| 38   | V <sub>RL</sub> differential voltage                                                                                           | V <sub>RL</sub> – V <sub>SSA</sub>                                                                                   | -100                   | 100                                | mV                         |

| 39   | Analog reference high voltage                                                                                                  | V <sub>RH</sub>                                                                                                      | V <sub>DDA</sub> – 0.1 | V <sub>DDA</sub> + 0.1             | V                          |

| 40   | V <sub>REF</sub> differential voltage                                                                                          | V <sub>RH</sub> – V <sub>RL</sub>                                                                                    | 4.5                    | 5.25                               | V                          |

| 41   | V <sub>SSSYN</sub> to V <sub>SS</sub> differential voltage                                                                     | $V_{\rm SSSYN} - V_{\rm SS}$                                                                                         | -50                    | 50                                 | mV                         |

| 42   | V <sub>RCVSS</sub> to V <sub>SS</sub> differential voltage                                                                     | $V_{RCVSS} - V_{SS}$                                                                                                 | -50                    | 50                                 | mV                         |

| 43   | V <sub>DDF</sub> to V <sub>DD</sub> differential voltage                                                                       | $V_{DDF} - V_{DD}$                                                                                                   | -100                   | 100                                | mV                         |

| 43a  | V <sub>RC33</sub> to V <sub>DDSYN</sub> differential voltage                                                                   | $V_{RC33} - V_{DDSYN}$                                                                                               | -0.1                   | 0.1 <sup>17</sup>                  | V                          |

| 44   | Analog input differential signal range (with common mode 2.5 V)                                                                | V <sub>IDIFF</sub>                                                                                                   | -2.5                   | 2.5                                | V                          |

| 45   | Operating temperature range, ambient (packaged)                                                                                | $T_A = (T_L \text{ to } T_H)$                                                                                        | ΤL                     | т <sub>н</sub>                     | °C                         |

| 46   | Slew rate on power-supply pins                                                                                                 | —                                                                                                                    | _                      | 50                                 | V/ms                       |

## Table 9. DC Electrical Specifications ( $T_A = T_L \text{ to } T_H$ ) (continued)

<sup>1</sup> V<sub>DDE2</sub> and V<sub>DDE3</sub> are limited to 2.25–3.6 V only if SIU\_ECCR[EBTS] = 0; V<sub>DDE2</sub> and V<sub>DDE3</sub> have a range of 1.6–3.6 V if SIU\_ECCR[EBTS] = 1.

- $^{2}$  | V<sub>DDA0</sub> V<sub>DDA1</sub> | must be < 0.1 V.

- $^{3}$  V<sub>PP</sub> can drop to 3.0 V during read operations.

- <sup>4</sup> If standby operation is not required, connect V<sub>STBY</sub> to ground.

- <sup>5</sup> Applies to CLKOUT, external bus pins, and Nexus pins.

- <sup>6</sup> Maximum average RMS DC current.

- <sup>7</sup> Average current measured on automotive benchmark.

- <sup>8</sup> Peak currents can be higher on specialized code.

- <sup>9</sup> High use current measured while running optimized SPE assembly code with all code and data 100% locked in cache (0% miss rate) with all channels of the eMIOS and eTPU running autonomously, plus the eDMA transferring data continuously from SRAM to SRAM. Higher currents are possible if an "idle" loop that crosses cache lines is run from cache. Write code that avoids this condition.

- <sup>10</sup> The current specification relates to average standby operation after SRAM has been loaded with data. For power up current see Section 3.7, "Power-Up/Down Sequencing", Figure 2.

- <sup>11</sup> Power requirements for the V<sub>DD33</sub> supply depend on the frequency of operation, load of all I/O pins, and the voltages on the I/O segments. Refer to Table 11 for values to calculate the power dissipation for a specific operation.

- <sup>12</sup> Power requirements for each I/O segment are dependent on the frequency of operation and load of the I/O pins on a particular I/O segment, and the voltage of the I/O segment. Refer to Table 10 for values to calculate power dissipation for specific operation. The total power consumption of an I/O segment is the sum of the individual power consumptions for each pin on the segment.

- $^{13}$  Absolute value of current, measured at  $V_{IL}$  and  $V_{IH}.$

- <sup>14</sup> Weak pullup/down inactive. Measured at  $V_{DDE} = 3.6$  V and  $V_{DDEH} = 5.25$  V. Applies to pad types: pad\_fc, pad\_sh, and pad\_mh.

- <sup>15</sup> Maximum leakage occurs at maximum operating temperature. Leakage current decreases by approximately one-half for each 8 °C to 12 °C, in the ambient temperature range of 50 °C to 125 °C. Applies to pad types: pad\_a and pad\_ae.

- $^{16}$  V<sub>SSA</sub> refers to both V<sub>SSA0</sub> and V<sub>SSA1</sub>. | V<sub>SSA0</sub> V<sub>SSA1</sub> | must be < 0.1 V.

- <sup>17</sup> Up to 0.6 V during power up and power down.

## 3.8.1 I/O Pad Current Specifications

The power consumption of an I/O segment depends on the usage of the pins on a particular segment. The power consumption is the sum of all output pin currents for a segment. The output pin current can be calculated from Table 10 based on the voltage, frequency, and load on the pin. Use linear scaling to calculate pin currents for voltage, frequency, and load parameters that fall outside the values given in Table 10.

| Spec | Pad Type | Symbol              | Frequency<br>(MHz) | Load <sup>2</sup> (pF) | Voltage (V) | Drive Select /<br>Slew Rate<br>Control Setting | Current (mA) |

|------|----------|---------------------|--------------------|------------------------|-------------|------------------------------------------------|--------------|

| 1    |          |                     | 25                 | 50                     | 5.25        | 11                                             | 8.0          |

| 2    | Slow     |                     | 10                 | 50                     | 5.25        | 01                                             | 3.2          |

| 3    | 51000    | I <sub>DRV_SH</sub> | 2                  | 50                     | 5.25        | 00                                             | 0.7          |

| 4    |          |                     | 2                  | 200                    | 5.25        | 00                                             | 2.4          |

| 5    |          |                     | 50                 | 50                     | 5.25        | 11                                             | 17.3         |

| 6    | Medium   |                     | 20                 | 50                     | 5.25        | 01                                             | 6.5          |

| 7    | Medium   | I <sub>DRV_MH</sub> | 3.33               | 50                     | 5.25        | 00                                             | 1.1          |

| 8    |          |                     | 3.33               | 200                    | 5.25        | 00                                             | 3.9          |

| 9    |          |                     | 66                 | 10                     | 3.6         | 00                                             | 2.8          |

| 10   |          |                     | 66                 | 20                     | 3.6         | 01                                             | 5.2          |

| 11   | -        |                     | 66                 | 30                     | 3.6         | 10                                             | 8.5          |

| 12   |          |                     | 66                 | 50                     | 3.6         | 11                                             | 11.0         |

| 13   |          |                     | 66                 | 10                     | 1.98        | 00                                             | 1.6          |

| 14   |          |                     | 66                 | 20                     | 1.98        | 01                                             | 2.9          |

| 15   |          |                     | 66                 | 30                     | 1.98        | 10                                             | 4.2          |

| 16   |          |                     | 66                 | 50                     | 1.98        | 11                                             | 6.7          |

| 17   |          |                     | 56                 | 10                     | 3.6         | 00                                             | 2.4          |

| 18   |          |                     | 56                 | 20                     | 3.6         | 01                                             | 4.4          |

| 19   |          |                     | 56                 | 30                     | 3.6         | 10                                             | 7.2          |

| 20   | Fast     | I                   | 56                 | 50                     | 3.6         | 11                                             | 9.3          |

| 21   | Tasi     | I <sub>DRV_FC</sub> | 56                 | 10                     | 1.98        | 00                                             | 1.3          |

| 22   |          |                     | 56                 | 20                     | 1.98        | 01                                             | 2.5          |

| 23   |          |                     | 56                 | 30                     | 1.98        | 10                                             | 3.5          |

| 24   |          |                     | 56                 | 50                     | 1.98        | 11                                             | 5.7          |

| 25   |          |                     | 40                 | 10                     | 3.6         | 00                                             | 1.7          |

| 26   |          |                     | 40                 | 20                     | 3.6         | 01                                             | 3.1          |

| 27   |          |                     | 40                 | 30                     | 3.6         | 10                                             | 5.1          |

| 28   |          |                     | 40                 | 50                     | 3.6         | 11                                             | 6.6          |

| 29   |          |                     | 40                 | 10                     | 1.98        | 00                                             | 1.0          |

| 30   |          |                     | 40                 | 20                     | 1.98        | 01                                             | 1.8          |

| 31   |          |                     | 40                 | 30                     | 1.98        | 10                                             | 2.5          |

| 32   |          |                     | 40                 | 50                     | 1.98        | 11                                             | 4.0          |

| Table 10. I/O Pad Average DC Current | $(T_A = T_L \text{ to } T_H)^1$ |

|--------------------------------------|---------------------------------|

|--------------------------------------|---------------------------------|

<sup>1</sup> These values are estimates from simulation and are not tested. Currents apply to output pins only.

<sup>2</sup> All loads are lumped.

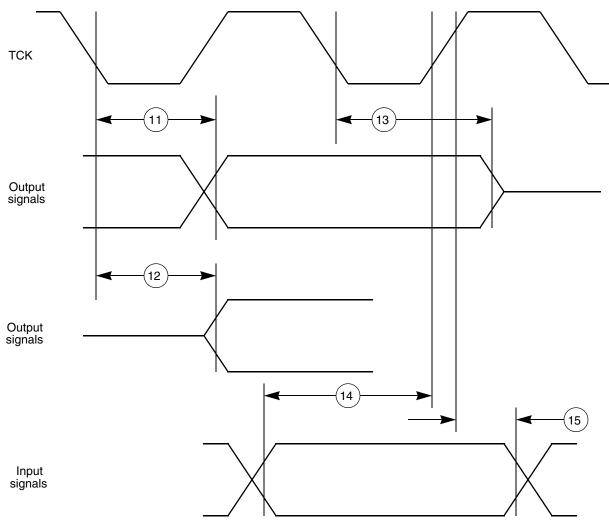

Figure 9. JTAG Boundary Scan Timing

## 3.13.4 External Bus Interface (EBI) Timing

Table 22 lists the timing information for the external bus interface (EBI).

|      | Characteristic                                                                                                                                                                                                                                                                                       |                  |                          | Extern                     | al Bus F                 | requen                   | cy <sup>2, 3</sup>       |                          |                |                                                                                        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|----------------------------|--------------------------|--------------------------|--------------------------|--------------------------|----------------|----------------------------------------------------------------------------------------|

| Spec | and                                                                                                                                                                                                                                                                                                  | Symbol           | 40 MHz                   |                            | 56 I                     | MHz                      | 66 I                     | MHz                      | Unit           | Notes                                                                                  |

|      | Description                                                                                                                                                                                                                                                                                          |                  | Min.                     | Max.                       | Min.                     | Max.                     | Min.                     | Max.                     |                |                                                                                        |

| 1    | CLKOUT period                                                                                                                                                                                                                                                                                        | т <sub>с</sub>   | 24.4                     | _                          | 17.5                     | _                        | 15.2                     | _                        | ns             | Signals are measured at 50% V <sub>DDE</sub> .                                         |

| 2    | CLKOUT duty cycle                                                                                                                                                                                                                                                                                    | t <sub>CDC</sub> | 45%                      | 55%                        | 45%                      | 55%                      | 45%                      | 55%                      | Τ <sub>C</sub> |                                                                                        |

| 3    | CLKOUT rise time                                                                                                                                                                                                                                                                                     | t <sub>CRT</sub> | —                        | 4                          |                          | 4                        |                          | 4                        | ns             |                                                                                        |

| 4    | CLKOUT fall time                                                                                                                                                                                                                                                                                     | t <sub>CFT</sub> | —                        | 4                          |                          | 4                        |                          | 4                        | ns             |                                                                                        |

| 5    | CLKOUT positive edge to output<br>signal <i>invalid</i> or Hi-Z (hold time)<br>External bus interface<br>BG <sup>5</sup><br>BR <sup>6</sup><br>BB<br>CS[0:3]<br>ADDR[8:31]<br>DATA[0:31] <sup>7</sup><br>BDIP<br>OE<br>RD_WR<br>TA<br>TEA <sup>8</sup><br>TS<br>TSIZ[0:1]<br>WE/BE[0:3] <sup>9</sup> | tсон             | 1.0 <sup>10</sup><br>1.5 |                            | 1.0 <sup>10</sup><br>1.5 |                          | 1.0 <sup>10</sup><br>1.5 |                          | ns             | EBTS = 0<br>EBTS = 1<br>Hold time selectable<br>via SIU_ECCR<br>[EBTS] bit.            |

| 6    | CLKOUT positive edge to output<br>signal <i>valid</i> (output delay)<br>External bus interface<br>BG <sup>5</sup><br>BR <sup>6</sup><br>BB<br>CS[0:3]<br>ADDR[8:31]<br>DATA[0:31] <sup>7</sup><br>BDIP<br>OE<br>RD_WR<br>TA<br>TEA <sup>8</sup><br>TS<br>TSIZ[0:1]<br>WE/BE[0:3] <sup>9</sup>        | tcov             |                          | 10.0 <sup>10</sup><br>11.0 |                          | 7.5 <sup>10</sup><br>8.5 | _                        | 6.0 <sup>10</sup><br>7.0 | ns             | EBTS = 0<br>EBTS = 1<br>Output valid time<br>selectable via<br>SIU_ECCR<br>[EBTS] bit. |

### Table 22. Bus Operation Timing<sup>1</sup>

Figure 15. External Interrupt Timing

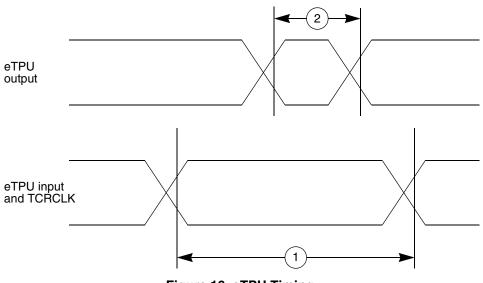

## 3.13.6 eTPU Timing

Table 24. eTPU Timing <sup>1</sup>

| Spec | Characteristic                  | Symbol            | Min.           | Мах | Unit             |

|------|---------------------------------|-------------------|----------------|-----|------------------|

| 1    | eTPU input channel pulse width  | t <sub>ICPW</sub> | 4              | _   | t <sub>CYC</sub> |

| 2    | eTPU output channel pulse width | t <sub>OCPW</sub> | 2 <sup>2</sup> |     | t <sub>CYC</sub> |

<sup>1</sup> eTPU timing specified at:  $V_{DDEH} = 3.0-5.25$  V and  $T_A = T_L$  to  $T_H$ .

<sup>2</sup> This specification does not include the rise and fall times. When calculating the minimum eTPU pulse width, include the rise and fall times defined in the slew rate control fields (SRC) of the pad configuration registers (PCR).

Figure 16. eTPU Timing

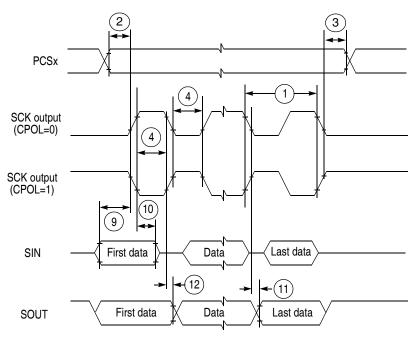

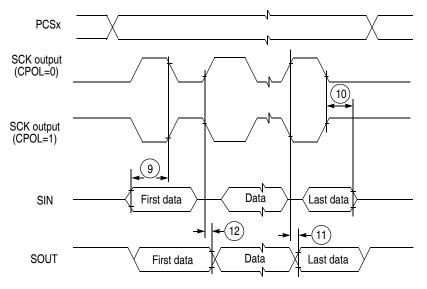

Figure 18. DSPI Classic SPI Timing—Master, CPHA = 0

#### Mechanicals

| 14         | 15         | 16          | 17          | 18          | 19          | 20             | 21          | 22         | 23          | 24           | 25            | 26          |    |

|------------|------------|-------------|-------------|-------------|-------------|----------------|-------------|------------|-------------|--------------|---------------|-------------|----|

| VSSA0      | AN15       | ETRIG<br>1  | ETPUB<br>18 | ETPUB<br>20 | ETPUB<br>24 | ETPUB<br>27    | GPIO<br>205 | MDO11      | MDO8        | VDD          | VDD33         | VSS         | А  |

| VSSA0      | AN14       | ETRIG<br>0  | ETPUB<br>21 | ETPUB<br>25 | ETPUB<br>28 | ETPUB<br>31    | MDO10       | MDO7       | MDO4        | MDO0         | VSS           | VDDE7       | в  |

| VDDA0      | AN13       | ETPUB<br>19 | ETPUB<br>22 | ETPUB<br>26 | ETPUB<br>30 | MDO9           | MDO6        | MDO3       | MDO1        | VSS          | VDDE7         | VDD         | С  |

| VDDEH<br>9 | AN12       | ETPUB<br>16 | ETPUB<br>17 | ETPUB<br>23 | ETPUB<br>29 | MDO5           | MDO2        | VDDEH<br>8 | VSS         | VDDE7        | TCK           | TDI         | D  |

|            |            |             |             |             |             |                |             |            | VDDE7       | TMS          | TDO           | TEST        | Е  |

|            |            |             |             |             |             |                |             |            | MSEO0       | JCOMP        | EVTI          | EVTO        | F  |

|            |            |             |             |             |             |                |             |            | MSEO1       | МСКО         | GPIO<br>204   | ETPUB<br>15 | G  |

|            |            |             |             |             |             |                |             |            | RDY         | GPIO<br>203  | ETPUB<br>14   | ETPUB<br>13 | Н  |

|            |            |             |             |             |             |                |             |            | VDDEH<br>6  | ETPUB<br>12  | ETPUB<br>11   | ETPUB<br>9  | J  |

| VDDE7      | VDDE7      | VDDE7       | VDDE7       |             |             |                |             |            | ETPUB<br>10 | ETPUB<br>8   | ETPUB<br>7    | ETPUB<br>5  | к  |

| VSS        | VSS        | VSS         | VDDE7       |             |             |                |             |            | ETPUB<br>6  | ETPUB<br>4   | ETPUB<br>3    | ETPUB<br>2  | L  |

| VSS        | VSS        | VSS         | VDDE7       |             |             |                |             |            | TCRCLK<br>B | ETPUB<br>1   | ETPUB<br>0    | SINB        | М  |

| VSS        | VSS        | VSS         | VDDE7       |             |             |                |             |            | SOUTB       | PCSB3        | PCSB0         | PCSB1       | N  |

| VSS        | VSS        | VSS         | VSS         |             |             |                |             |            | PCSA3       | PCSB4        | SCKB          | PCSB2       | Ρ  |

| VSS        | VSS        | VSS         | VSS         |             |             |                |             |            | PCSB5       | SOUTA        | SINA          | SCKA        | R  |

| VDDE2      | VDDE2      | VSS         | VSS         |             |             |                |             |            | PCSA1       | PCSA0        | PCSA2         | VPP         | т  |

| VDDE2      | VDDE2      | VSS         | VSS         |             |             |                |             |            | PCSA4       | TXDA         | PCSA5         | VFLASH      | U  |

|            |            |             |             |             |             |                |             |            | CNTXC       | RXDA         | RSTOUT        | RST<br>CFG  | V  |

|            |            |             |             |             |             |                |             |            | RXDB        | CNRXC        | TXDB          | RESET       | W  |

| 1          | Note:      | NC          | No co       | nnect.      | AC22 8      | AD23           | reserve     | ed         | WKP<br>CFG  | BOOT<br>CFG1 | VRC<br>VSS    | VSS<br>SYN  | Y  |

|            |            |             |             |             |             |                |             |            | VDDEH<br>6  | PLL<br>CFG1  | BOOT<br>CFG0  | EXTAL       | AA |

|            |            |             |             |             |             |                |             |            | VDD         | VRC<br>CTL   | PLL<br>CFG0   | XTAL        | AB |

| DATA<br>12 | DATA<br>14 | EMIOS<br>2  | 8           | EMIOS<br>12 | EMIOS<br>21 | VDDEH<br>4     | VDDE5       | NC         | VSS         | VDD          | VRC33         | VDD<br>SYN  | AC |

| DATA<br>15 | EMIOS<br>3 | EMIOS<br>6  | EMIOS<br>10 | EMIOS<br>15 | EMIOS<br>17 | EMIOS<br>22    | CNTXA       | VDDE5      | NC          | VSS          | VDD           | VDD33       | AD |

| BG         | EMIOS<br>1 | EMIOS<br>5  | EMIOS<br>9  | EMIOS<br>13 | EMIOS<br>16 | EMIOS<br>19    | EMIOS<br>23 | CNRXA      | VDDE5       | CLKOUT       | VSS           | VDD         | AE |

| BB         | EMIOS<br>0 | EMIOS<br>4  | 7           | EMIOS<br>11 | EMIOS<br>14 | EMIOS<br>18    | EMIOS<br>20 | CNTXB      | CNRXB       |              | ENG<br>CLK    | VSS         | AF |

| 14         | 15         | 16          | 17          | 18          | 19          | 20<br>7 41 C F | 21          | 22         | 23          | 24           | 25<br>0 of 0) | 26          |    |

|            | F          | igure :     | 30. IVIP    | C0003       | J4000/      | 410 H          | аскад       | e Righ     | 1 3100      | (view        | 2 01 2)       |             |    |

Figure 31. MPC5567 416 Package

MPC5554 Microcontroller Data Sheet, Rev. 4

#### Mechanicals

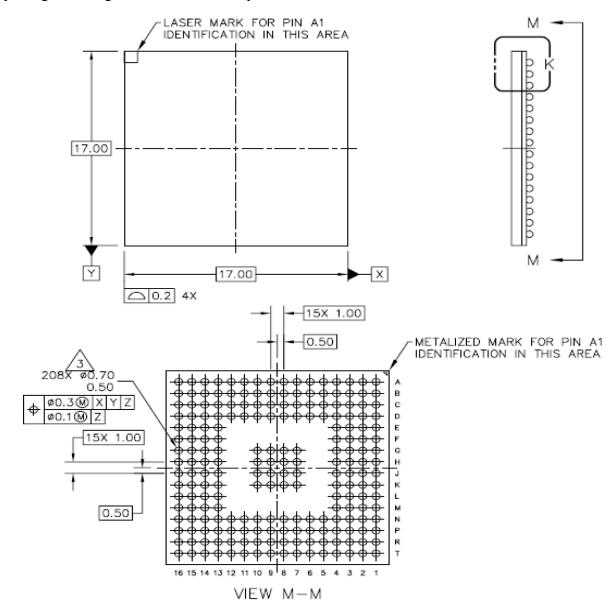

The package drawings of the MPC55 208-pin MAP BGA are shown below.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | T TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|------------|

| TITLE:                                                  | •         | DOCUMENT NO  | ): 98ARS23882W   | REV: D     |

| 208 I/O MAP BG/<br>17 X 17 PKG, 1-MM                    |           | CASE NUMBER  | 02 AUG 2005      |            |

|                                                         | i iioii   | STANDARD: JE | DEC MO-151 AAF-1 |            |

Figure 32. 208-Pin Package

MPC5554 Microcontroller Data Sheet, Rev. 4

Mechanicals

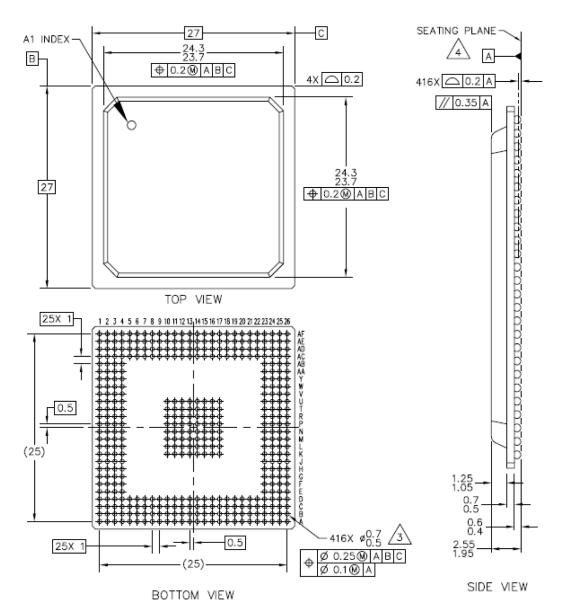

## 4.2 MPC5554 416-Pin Package Dimensions

The package drawings of the MPC5554 416 pin TEPBGA package are shown in Figure 34.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: 416 I/O, PBGA                                    |           | DOCUMENT NO  | ): 98ARE10523D   | REV: A      |

| 27 X 27 PKG,                                            |           | CASE NUMBER  | 2: 1494–01       | 13 JUL 2005 |

| 1 MM PITCH (OMP                                         | AC)       | STANDARD: JE | DEC MS-034 AAL-1 |             |

MPC5554 Microcontroller Data Sheet, Rev. 4

#### Revision History for the MPC5554 Data Sheet

### Table 28. Changes Between Rev. 2.0 and 3.0 (continued)

| Location    | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

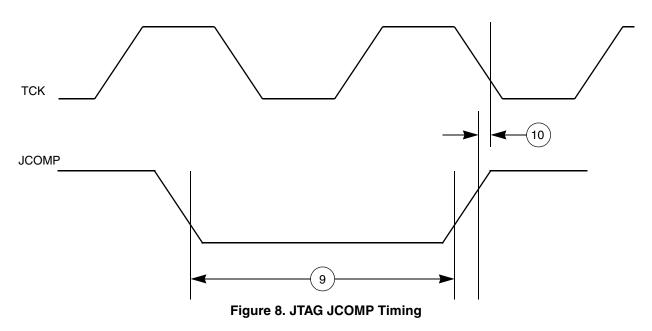

| Table 20 (J | TAG Pin AC Electrical Characteristics) JTAG Pin AC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | • Footnote 1: Removed $V_{DD}$ = 1.35–1.65 V, and $V_{DD33}$ and $V_{DDSYN}$ = 3.0–3.6 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 22 (B | us Operation Timing) Bus Operation Timing:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | <ul> <li>External Bus Frequency in the table heading: Added footnote that reads: Speed is the nominal maximum frequency. Max speed is the maximum speed allowed including frequency modulation (FM). 82 MHz parts allow for 80 MHz system clock + 2% FM; 114 MHz parts allow for 112 MHz system clock + 2% FM; and 132 MHz parts allow for 128 MHz system clock + 2% FM.</li> <li>Specifications 5, 6, 7, and 8: Reordered the EBI signals within each specification.</li> <li>Specifications 7 and 8: Removed EBI signals BDIP, OE, TSIZ[0:1], WE/BE[0:3].</li> <li>Footnote 1: Removed V<sub>DD</sub> = 1.35–1.65 V, and V<sub>DD33</sub> and V<sub>DDSYN</sub> = 3.0–3.6 V.</li> <li>Footnote 8: Changed EBTS to SIU_ECCR[EBTS].</li> </ul> |

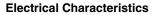

| Table 23 (E | xternal Interrupt Timing) External Interrupt Timing (IRQ Signals)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | • Footnote 1: Removed $V_{DD}$ = 1.35–1.65 V; changed $V_{DDEH}$ = 3.0–5.5 V to $V_{DDEH}$ = 3.0–5.25 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 24 (e | TPU Timing) eTPU Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | <ul> <li>Footnote 1: Changed V<sub>DDEH</sub> = 3.0–5.5 V to V<sub>DDEH</sub> = 3.0–5.25 V.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 25 (e | MIOS Timing) eMIOS Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | • Footnote 1: Changed $V_{DDEH}$ = 3.0–5.5 V to $V_{DDEH}$ = 3.0–5.25 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 26 (D | SPI Timing') DSPI Timing:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | <ul> <li>Footnote 1, changed 'V<sub>DDEH</sub> = 3.0–5.5 V;' to 'V<sub>DDEH</sub> = 3.0–5.25 V;'</li> <li>Table Title: Added footnote that reads: Speed is the nominal maximum frequency. Max speed is the maximum speed allowed including frequency modulation (FM). 82 MHz parts allow for 80 MHz system clock + 2% FM; 114 MHz parts allow for 112 MHz system clock + 2% FM; and 132 MHz parts allow for 128 MHz system clock + 2% FM.</li> <li>Spec 1: SCK cycle time; Changed to 80 MHz minimum column from 25 to 24.4; 112 MHz minimum column from 17.9 to 17.5; 112 MHz maximum column from 2.0 to 2.1.</li> </ul>                                                                                                                      |

| Table 27 (E | QADC SSI Timing Characteristics) EQADC SSI Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |