# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 18MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                        |

| Number of I/O              | 26                                                                        |

| Program Memory Size        | 8KB (8K x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                               |

| Data Converters            | A/D 8x8b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 28-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc9351fdh-518 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8-bit microcontroller with 8-bit ADC

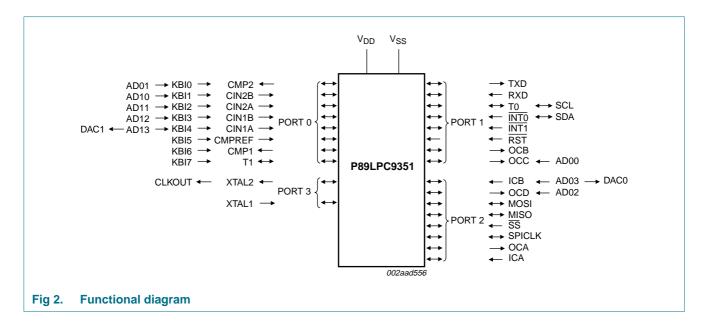

### 5. Functional diagram

### **NXP Semiconductors**

# P89LPC9351

#### 8-bit microcontroller with 8-bit ADC

| Symbol         | Pin                | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|--------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | PLCC28,<br>TSSOP28 |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P0.6/CMP1/KBI6 | 20                 | I/O                   | P0.6 — Port 0 bit 6. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                    | 0                     | CMP1 — Comparator 1 output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                    | I                     | KBI6 — Keyboard input 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P0.7/T1/KBI7   | 19                 | I/O                   | P0.7 — Port 0 bit 7. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                    | I/O                   | T1 — Timer/counter 1 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |                    | I                     | KBI7 — Keyboard input 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1.0 to P1.7   |                    | I/O, I<br>[ <u>1]</u> | <b>Port 1:</b> Port 1 is an 8-bit I/O port with a user-configurable output type, except for three pins as noted below. During reset Port 1 latches are configured in the input only mode with the internal pull-up disabled. The operation of the configurable Port 1 pins as inputs and outputs depends upon the port configuration selected. Each of the configurable port pins are programmed independently. Refer to <u>Section 7.16.1 "Port configurations"</u> and <u>Table 10 "Static characteristics"</u> for details. P1.2 to P1.3 are open drain when used as outputs. P1.5 is input only. |

|                |                    |                       | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                    |                       | Port 1 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P1.0/TXD       | 18                 | I/O                   | <b>P1.0</b> — Port 1 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                    | 0                     | <b>TXD</b> — Transmitter output for serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.1/RXD 17     |                    | I/O                   | P1.1 — Port 1 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |                    | I                     | <b>RXD</b> — Receiver input for serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1.2/T0/SCL    | 12                 | I/O                   | P1.2 — Port 1 bit 2 (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                    | I/O                   | <b>T0</b> — Timer/counter 0 external count input or overflow output (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                    | I/O                   | SCL — I <sup>2</sup> C-bus serial clock input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P1.3/INT0/SDA  | 11                 | I/O                   | P1.3 — Port 1 bit 3 (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                    | I                     | INT0 — External interrupt 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                |                    | I/O                   | <b>SDA</b> — I <sup>2</sup> C-bus serial data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P1.4/INT1      | 10                 | I/O                   | P1.4 — Port 1 bit 4. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                    | I                     | INT1 — External interrupt 1 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P1.5/RST       | 6                  | I                     | P1.5 — Port 1 bit 5 (input only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |                    | I                     | <b>RST</b> — External Reset input during power-on or if selected via UCFG1. When functioning as a reset input, a LOW on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor begins execution at address 0. Also used during a power-on sequence to force ISP mode.                                                                                                                                                                                                                                                             |

| P1.6/OCB       | 5                  | I/O                   | P1.6 — Port 1 bit 6. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                    | 0                     | OCB — Output Compare B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P1.7/OCC/AD00  | 4                  | I/O                   | P1.7 — Port 1 bit 7. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                    | 0                     | <b>OCC</b> — Output Compare C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |                    | Ι                     | AD00 — ADC0 channel 0 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### **NXP Semiconductors**

### P89LPC9351

#### 8-bit microcontroller with 8-bit ADC

| Symbol        | Pin                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | PLCC28,<br>TSSOP28 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P2.0 to P2.7  |                    | I/O  | <b>Port 2:</b> Port 2 is an 8-bit I/O port with a user-configurable output type. During reset Port 2 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 2 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <u>Section 7.16.1 "Port configurations"</u> and <u>Table 10 "Static characteristics"</u> for details. |

|               |                    |      | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                             |

|               |                    |      | Port 2 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                |

| P2.0/ICB/DAC0 | 1                  | I/O  | <b>P2.0</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| /AD03         |                    | I    | ICB — Input Capture B.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                    | 0    | DAC0 — Digital-to-analog converter output.                                                                                                                                                                                                                                                                                                                                                                                                        |

|               |                    | I    | AD03 — ADC0 channel 3 analog input.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P2.1/OCD/AD02 | 2                  | I/O  | <b>P2.1</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                    | 0    | OCD — Output Compare D.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |                    | Ι    | AD02 — ADC0 channel 2 analog input.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P2.2/MOSI     | 13                 | I/O  | <b>P2.2</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                    | I/O  | <b>MOSI</b> — SPI master out slave in. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                                |

| P2.3/MISO     | 14                 | I/O  | <b>P2.3</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                    | I/O  | <b>MISO</b> — When configured as master, this pin is input, when configured as slave, this pin is output.                                                                                                                                                                                                                                                                                                                                         |

| P2.4/SS       | 15                 | I/O  | <b>P2.4</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                    | I/O  | SS — SPI Slave select.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P2.5/SPICLK   | 16                 | I/O  | <b>P2.5</b> — Port 2 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                    | I/O  | <b>SPICLK</b> — SPI clock. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                                            |

| P2.6/OCA      | 27                 | I/O  | <b>P2.6</b> — Port 2 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                    | 0    | OCA — Output Compare A.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P2.7/ICA      | 28                 | I/O  | <b>P2.7</b> — Port 2 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                    | I    | ICA — Input Capture A.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P3.0 to P3.1  |                    | I/O  | <b>Port 3:</b> Port 3 is a 2-bit I/O port with a user-configurable output type. During reset Port 3 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 3 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <u>Section 7.16.1 "Port configurations"</u> and <u>Table 10 "Static characteristics"</u> for details.  |

|               |                    |      | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                             |

|               |                    |      | Port 2 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                |

Port 3 also provides various special functions as described below:

# Table 4.Special function registers\* indicates SFRs that are bit addressable.

| Name    | Description                        | SFR    | Bit functio | ns and addre | sses  |           |        |           |        |           | Reset | value    |

|---------|------------------------------------|--------|-------------|--------------|-------|-----------|--------|-----------|--------|-----------|-------|----------|

|         |                                    | addr.  | MSB         |              |       |           |        |           |        | LSB       | Hex   | Binary   |

|         | Bit a                              | ddress | E7          | <b>E6</b>    | E5    | <b>E4</b> | E3     | <b>E2</b> | E1     | <b>E0</b> |       |          |

| ACC*    | Accumulator                        | E0H    |             |              |       |           |        |           |        |           | 00    | 0000 000 |

| ADCON0  | A/D control<br>register 0          | 8EH    | ENBI0       | ENADCI0      | TMM0  | EDGE0     | ADCI0  | ENADC0    | ADCS01 | ADCS00    | 00    | 0000 000 |

| ADCON1  | A/D control<br>register 1          | 97H    | ENBI1       | ENADCI1      | TMM1  | EDGE1     | ADCI1  | ENADC1    | ADCS11 | ADCS10    | 00    | 0000 000 |

| ADINS   | A/D input<br>select                | A3H    | ADI13       | ADI12        | ADI11 | ADI10     | ADI03  | ADI02     | ADI01  | ADI00     | 00    | 0000 00  |

| ADMODA  | A/D mode<br>register A             | C0H    | BNDI1       | BURST1       | SCC1  | SCAN1     | BNDI0  | BURST0    | SCC0   | SCAN0     | 00    | 0000 00  |

| ADMODB  | A/D mode<br>register B             | A1H    | CLK2        | CLK1         | CLK0  | -         | ENDAC1 | ENDAC0    | BSA1   | BSA0      | 00    | 000x 00  |

| AD0BH   | A/D_0<br>boundary high<br>register | BBH    |             |              |       |           |        |           |        |           | FF    | 1111 11  |

| AD0BL   | A/D_0<br>boundary low<br>register  | A6H    |             |              |       |           |        |           |        |           | 00    | 0000 00  |

| AD0DAT0 | A/D_0 data<br>register 0           | C5H    |             |              |       |           |        |           |        |           | 00    | 0000 00  |

| AD0DAT1 | A/D_0 data<br>register 1           | C6H    |             |              |       |           |        |           |        |           | 00    | 0000 00  |

| AD0DAT2 | A/D_0 data<br>register 2           | C7H    |             |              |       |           |        |           |        |           | 00    | 0000 00  |

| AD0DAT3 | A/D_0 data<br>register 3           | F4H    |             |              |       |           |        |           |        |           | 00    | 0000 00  |

| AD1BH   | A/D_1<br>boundary high<br>register | C4H    |             |              |       |           |        |           |        |           | FF    | 1111 11  |

| AD1BL   | A/D_1<br>boundary low<br>register  | BCH    |             |              |       |           |        |           |        |           | 00    | 0000 00  |

| AD1DAT0 | A/D_1 data register 0              | D5H    |             |              |       |           |        |           |        |           | 00    | 0000 00  |

8-bit microcontroller with 8-bit ADC

P89LPC9351

#### Table 4.Special function registers ... continued\* indicates SFRs that are bit addressable. Table 4. P89LPC9351\_

SFR Bit functions and addresses

Description

| Preliminary |

|-------------|

| data sheet  |

Name

| Rev.  |

|-------|

| 01    |

|       |

| 19    |

| Novem |

| ber   |

| 2008  |

| Name            | Description                                       | SFR    | Bit functio | ns and addre | esses   |         |         |         |         |         | Reset         | value     |

|-----------------|---------------------------------------------------|--------|-------------|--------------|---------|---------|---------|---------|---------|---------|---------------|-----------|

|                 |                                                   | addr.  | MSB         |              |         |         |         |         |         | LSB     | Hex           | Binary    |

| CMP2            | Comparator 2 control register                     | ADH    | -           | -            | CE2     | CP2     | CN2     | OE2     | CO2     | CMF2    | 00 <u>[1]</u> | xx00 0000 |

| DEECON          | Data EEPROM<br>control register                   | F1H    | EEIF        | HVERR        | ECTL1   | ECTL0   | -       | EWERR1  | EWERR0  | EADR8   | 08            | 00001000  |

| DEEDAT          | Data EEPROM<br>data register                      | F2H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

| DEEADR          | Data EEPROM<br>address<br>register                | F3H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

| DIVM            | CPU clock<br>divide-by-M<br>control               | 95H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

| DPTR            | Data pointer<br>(2 bytes)                         |        |             |              |         |         |         |         |         |         |               |           |

| DPH             | Data pointer<br>high                              | 83H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

| DPL             | Data pointer<br>low                               | 82H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

| FMADRH          | Program flash<br>address high                     | E7H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

| FMADRL          | Program flash<br>address low                      | E6H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

| FMCON           | Program flash control (Read)                      | E4H    | BUSY        | -            | -       | -       | HVA     | HVE     | SV      | OI      | 70            | 0111 0000 |

|                 | Program flash control (Write)                     | E4H    | FMCMD.7     | FMCMD.6      | FMCMD.5 | FMCMD.4 | FMCMD.3 | FMCMD.2 | FMCMD.1 | FMCMD.0 |               |           |

| FMDATA          | Program flash<br>data                             | E5H    |             |              |         |         |         |         |         |         | 00            | 0000 0000 |

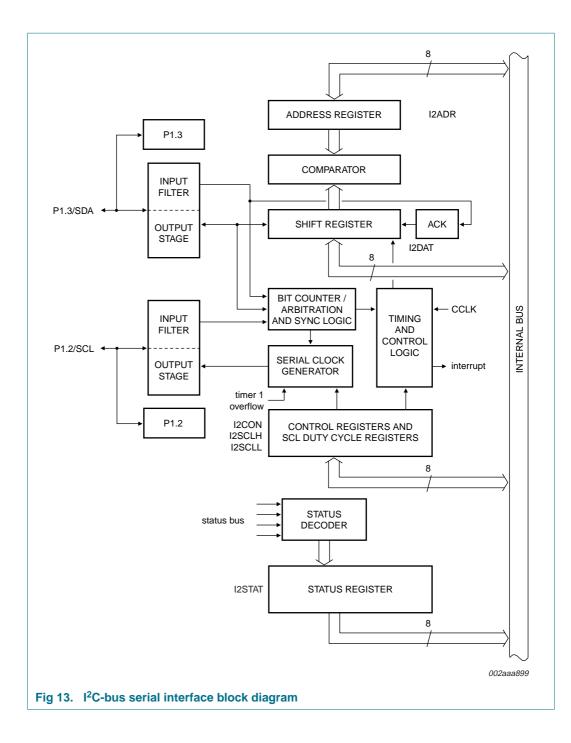

| I2ADR<br>I2CON* | l <sup>2</sup> C-bus slave<br>address<br>register | DBH    | I2ADR.6     | I2ADR.5      | I2ADR.4 | I2ADR.3 | I2ADR.2 | I2ADR.1 | I2ADR.0 | GC      | 00            | 0000 0000 |

| ~<br>           | Bit a                                             | ddress | DF          | DE           | DD      | DC      | DB      | DA      | D9      | D8      |               |           |

| I2CON*          | l <sup>2</sup> C-bus control register             | D8H    | -           | I2EN         | STA     | STO     | SI      | AA      | -       | CRSEL   | 00            | x000 00x0 |

Reset value

8-bit microcontroller with 8-bit ADC P89LPC9351

14 of 74

#### Table 4.Special function registers ... continued\* indicates SFRs that are bit addressable. P89LPC9

| Name  | Description              | SFR     | Bit function | ns and addre | esses          |               |               |               |               |              | Reset               | value    |

|-------|--------------------------|---------|--------------|--------------|----------------|---------------|---------------|---------------|---------------|--------------|---------------------|----------|

|       |                          | addr.   | MSB          |              |                |               |               |               |               | LSB          | Hex                 | Binary   |

|       | Bit a                    | address | 87           | 86           | 85             | 84            | 83            | 82            | 81            | 80           |                     |          |

| P0*   | Port 0                   | 80H     | T1/KB7       | CMP1<br>/KB6 | CMPREF<br>/KB5 | CIN1A<br>/KB4 | CIN1B<br>/KB3 | CIN2A<br>/KB2 | CIN2B<br>/KB1 | CMP2<br>/KB0 | <u>[1]</u>          |          |

|       | Bit a                    | address | 97           | 96           | 95             | 94            | 93            | 92            | 91            | 90           |                     |          |

| P1*   | Port 1                   | 90H     | 000          | OCB          | RST            | INT1          | INT0/SDA      | T0/SCL        | RXD           | TXD          | <u>[1]</u>          |          |

|       | Bit a                    | address | A7           | A6           | A5             | A4            | A3            | A2            | A1            | A0           |                     |          |

| P2*   | Port 2                   | A0H     | ICA          | OCA          | SPICLK         | SS            | MISO          | MOSI          | OCD           | ICB          | [1]                 |          |

|       | Bit a                    | address | B7           | <b>B6</b>    | B5             | <b>B4</b>     | <b>B</b> 3    | <b>B2</b>     | B1            | <b>B0</b>    |                     |          |

| P3*   | Port 3                   | B0H     | -            | -            | -              | -             | -             | -             | XTAL1         | XTAL2        | <u>[1]</u>          |          |

| P0M1  | Port 0 output<br>mode 1  | 84H     | (P0M1.7)     | (P0M1.6)     | (P0M1.5)       | (P0M1.4)      | (P0M1.3)      | (P0M1.2)      | (P0M1.1)      | (P0M1.0)     | FF <u>[1]</u>       | 1111 111 |

| P0M2  | Port 0 output<br>mode 2  | 85H     | (P0M2.7)     | (P0M2.6)     | (P0M2.5)       | (P0M2.4)      | (P0M2.3)      | (P0M2.2)      | (P0M2.1)      | (P0M2.0)     | 00 <u>[1]</u>       | 0000 000 |

| P1M1  | Port 1 output<br>mode 1  | 91H     | (P1M1.7)     | (P1M1.6)     | -              | (P1M1.4)      | (P1M1.3)      | (P1M1.2)      | (P1M1.1)      | (P1M1.0)     | D3[1]               | 11x1 xx1 |

| P1M2  | Port 1 output<br>mode 2  | 92H     | (P1M2.7)     | (P1M2.6)     | -              | (P1M2.4)      | (P1M2.3)      | (P1M2.2)      | (P1M2.1)      | (P1M2.0)     | 00 <u>[1]</u>       | 00x0 xx0 |

| P2M1  | Port 2 output<br>mode 1  | A4H     | (P2M1.7)     | (P2M1.6)     | (P2M1.5)       | (P2M1.4)      | (P2M1.3)      | (P2M1.2)      | (P2M1.1)      | (P2M1.0)     | FF <u>[1]</u>       | 1111 111 |

| P2M2  | Port 2 output<br>mode 2  | A5H     | (P2M2.7)     | (P2M2.6)     | (P2M2.5)       | (P2M2.4)      | (P2M2.3)      | (P2M2.2)      | (P2M2.1)      | (P2M2.0)     | 00 <u>[1]</u>       | 0000 000 |

| P3M1  | Port 3 output<br>mode 1  | B1H     | -            | -            | -              | -             | -             | -             | (P3M1.1)      | (P3M1.0)     | 03 <mark>[1]</mark> | xxxx xx1 |

| P3M2  | Port 3 output<br>mode 2  | B2H     | -            | -            | -              | -             | -             | -             | (P3M2.1)      | (P3M2.0)     | 00 <u>[1]</u>       | xxxx xx0 |

| PCON  | Power control register   | 87H     | SMOD1        | SMOD0        | -              | BOI           | GF1           | GF0           | PMOD1         | PMOD0        | 00                  | 0000 000 |

| PCONA | Power control register A | B5H     | RTCPD        | DEEPD        | VCPD           | ADPD          | I2PD          | SPPD          | SPD           | CCUPD        | 00 <u>[1]</u>       | 0000 000 |

|       | Bit a                    | address | D7           | D6           | D5             | D4            | D3            | D2            | D1            | <b>D0</b>    |                     |          |

| PSW*  | Program status<br>word   | D0H     | CY           | AC           | F0             | RS1           | RS0           | OV            | F1            | Р            | 00                  | 0000 000 |

8-bit microcontroller with 8-bit ADC P89LPC9351

ights reserved. 17 of 74

Preliminary data sheet

Each interrupt source can be individually programmed to one of four priority levels by setting or clearing bits in the interrupt priority registers IPO, IPOH, IP1 and IP1H. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other interrupt source. If two requests of different priority level is serviced.

If requests of the same priority level are pending at the start of an instruction, an internal polling sequence determines which request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used to resolve pending requests of the same priority level.

#### 7.15.1 External interrupt inputs

The P89LPC9351 has two external interrupt inputs as well as the Keypad Interrupt function. The two interrupt inputs are identical to those present on the standard 80C51 microcontrollers.

These external interrupts can be programmed to be level-triggered or edge-triggered by setting or clearing bit IT1 or IT0 in Register TCON.

In edge-triggered mode, if successive samples of the INTn pin show a HIGH in one cycle and a LOW in the next cycle, the interrupt request flag IEn in TCON is set, causing an interrupt request.

If an external interrupt is enabled when the P89LPC9351 is put into Power-down or Idle mode, the interrupt will cause the processor to wake-up and resume operation. Refer to Section 7.18 "Power reduction modes" for details.

P89LPC9351 1

#### 7.19.1 Reset vector

Following reset, the P89LPC9351 will fetch instructions from either address 0000H or the Boot address. The Boot address is formed by using the boot vector as the high byte of the address and the low byte of the address = 00H.

The boot address will be used if a UART break reset occurs, or the non-volatile boot status bit (BOOTSTAT.0) = 1, or the device is forced into ISP mode during power-on (see P89LPC9351 *User manual*). Otherwise, instructions will be fetched from address 0000H.

#### 7.20 Timers/counters 0 and 1

The P89LPC9351 has two general purpose counter/timers which are upward compatible with the standard 80C51 Timer 0 and Timer 1. Both can be configured to operate either as timers or event counters. An option to automatically toggle the T0 and/or T1 pins upon timer overflow has been added.

In the 'Timer' function, the register is incremented every machine cycle.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once during every machine cycle.

Timer 0 and Timer 1 have five operating modes (Modes 0, 1, 2, 3 and 6). Modes 0, 1, 2 and 6 are the same for both Timers/Counters. Mode 3 is different.

#### 7.20.1 Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. In this mode, the Timer register is configured as a 13-bit register. Mode 0 operation is the same for Timer 0 and Timer 1.

#### 7.20.2 Mode 1

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register are used.

#### 7.20.3 Mode 2

Mode 2 configures the Timer register as an 8-bit Counter with automatic reload. Mode 2 operation is the same for Timer 0 and Timer 1.

#### 7.20.4 Mode 3

When Timer 1 is in Mode 3 it is stopped. Timer 0 in Mode 3 forms two separate 8-bit counters and is provided for applications that require an extra 8-bit timer. When Timer 1 is in Mode 3 it can still be used by the serial port as a baud rate generator.

#### 7.20.5 Mode 6

In this mode, the corresponding timer can be changed to a PWM with a full period of 256 timer clocks.

When a reload occurs, the CCU Timer Overflow Interrupt Flag will be set, and an interrupt generated if enabled. The 16-bit CCU timer may also be used as an 8-bit up/down timer.

#### 7.22.4 Output compare

There are four output compare channels: A, B, C and D. Each output compare channel needs to be enabled in order to operate and the user will have to set the associated I/O pin to the desired output mode to connect the pin. When the contents of the timer matches that of a capture compare control register, the Timer Output Compare Interrupt Flag (TOCFx) becomes set. An interrupt will occur if enabled.

#### 7.22.5 Input capture

Input capture is always enabled. Each time a capture event occurs on one of the two input capture pins, the contents of the timer is transferred to the corresponding 16-bit input capture register. The capture event can be programmed to be either rising or falling edge triggered. A simple noise filter can be enabled on the input capture by enabling the Input Capture Noise Filter bit. If set, the capture logic needs to see four consecutive samples of the same value in order to recognize an edge as a capture event. An event counter can be set to delay a capture by a number of capture events.

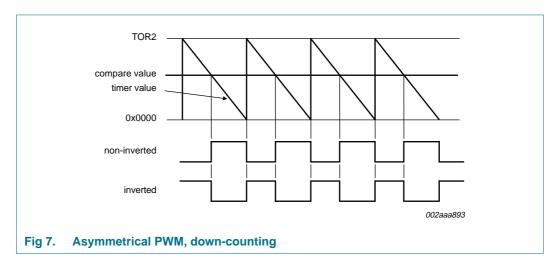

#### 7.22.6 PWM operation

PWM operation has two main modes, symmetrical and asymmetrical.

In asymmetrical PWM operation the CCU timer operates in down-counting mode regardless of the direction control bit.

In symmetrical mode, the timer counts up/down alternately. The main difference from basic timer operation is the operation of the compare module, which in PWM mode is used for PWM waveform generation.

As with basic timer operation, when the PWM (compare) pins are connected to the compare logic, their logic state remains unchanged. However, since bit FCO is used to hold the halt value, only a compare event can change the state of the pin.

#### 8-bit microcontroller with 8-bit ADC

#### **NXP Semiconductors**

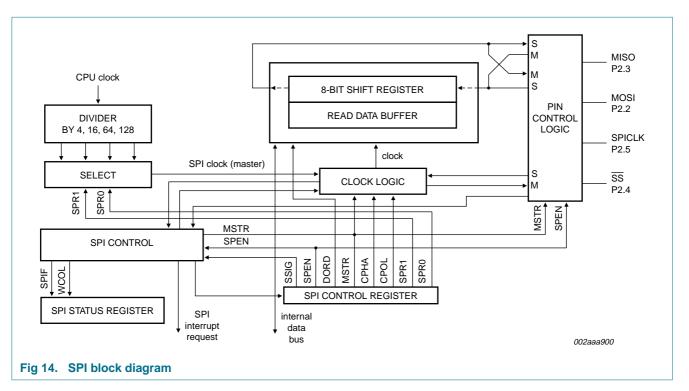

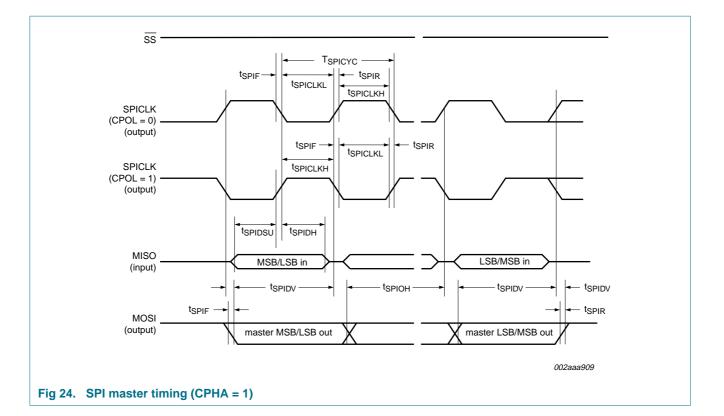

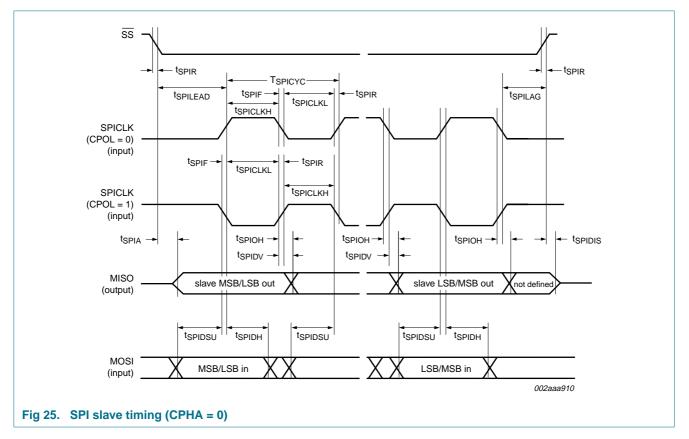

#### 7.25 SPI

The P89LPC9351 provides another high-speed serial communication interface: the SPI interface. SPI is a full-duplex, high-speed, synchronous communication bus with two operation modes: Master mode and Slave mode. Up to 3 Mbit/s can be supported in either Master mode or Slave mode. It has a Transfer Completion Flag and Write Collision Flag Protection.

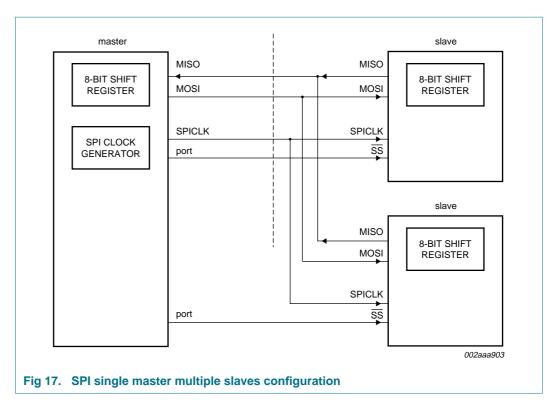

The SPI interface has four pins: SPICLK, MOSI, MISO and  $\overline{SS}$ :

- SPICLK, MOSI and MISO are typically tied together between two or more SPI devices. Data flows from master to slave on MOSI (Master Out Slave In) pin and flows from slave to master on MISO (Master In Slave Out) pin. The SPICLK signal is output in the Master mode and is input in the Slave mode. If the SPI system is disabled, i.e., SPEN (SPCTL.6) = 0 (reset value), these pins are configured for port functions.

- SS is the optional slave select pin. In a typical configuration, an SPI master asserts one of its port pins to select one SPI device as the current slave. An SPI slave device uses its SS pin to determine whether it is selected.

Typical connections are shown in Figure 15 through Figure 17.

P89LPC9351 1

#### 8-bit microcontroller with 8-bit ADC

#### 7.26 Analog comparators

Two analog comparators are provided on the P89LPC9351. Input and output options allow use of the comparators in a number of different configurations. Comparator operation is such that the output is a logical one (which may be read in a register and/or routed to a pin) when the positive input (one of two selectable inputs) is greater than the negative input (selectable from a pin or an internal reference voltage). Otherwise the output is a zero. Each comparator may be configured to cause an interrupt when the output value changes.

The positive inputs of comparators could be amplified by Programmable Gain Amplifier 1 (PGA1) module. The PGA1 can supply gain factors of 2x, 4x, 8x, or 16x, eliminating the need for external op-amps in the end application.

The overall connections to both comparators are shown in Figure 18. The comparators function to  $V_{DD}$  = 2.4 V.

When each comparator is first enabled, the comparator output and interrupt flag are not guaranteed to be stable for 10  $\mu$ s. The corresponding comparator interrupt should not be enabled during that time, and the comparator interrupt flag must be cleared before the interrupt is enabled in order to prevent an immediate interrupt service.

When a comparator is disabled the comparator's output, COn, goes HIGH. If the comparator output was LOW and then is disabled, the resulting transition of the comparator output from a LOW to HIGH state will set the comparator flag, CMFn. This will cause an interrupt if the comparator interrupt is enabled. The user should therefore disable the comparator interrupt prior to disabling the comparator. Additionally, the user should clear the comparator flag, CMFn, after disabling the comparator.

#### 7.30.4 Using flash as data storage

The flash code memory array of this device supports individual byte erasing and programming. Any byte in the code memory array may be read using the MOVC instruction, provided that the sector containing the byte has not been secured (a MOVC instruction is not allowed to read code memory contents of a secured sector). Thus any byte in a non-secured sector may be used for non-volatile data storage.

#### 7.30.5 Flash programming and erasing

Four different methods of erasing or programming of the flash are available. The flash may be programmed or erased in the end-user application (IAP) under control of the application's firmware. Another option is to use the ICP mechanism. This ICP system provides for programming through a serial clock/serial data interface. As shipped from the factory, the upper 512 bytes of user code space contains a serial ISP routine allowing for the device to be programmed in circuit through the serial port. The flash may also be programmed or erased using a commercially available EPROM programmer which supports this device. This device does not provide for direct verification of code memory contents. Instead, this device provides a 32-bit CRC result on either a sector or the entire user code space.

**Remark:** When voltage supply is lower than 2.4 V, the BOD FLASH is tripped and flash erase/program is blocked.

#### 7.30.6 ICP

ICP is performed without removing the microcontroller from the system. The ICP facility consists of internal hardware resources to facilitate remote programming of the P89LPC9351 through a two-wire serial interface. The NXP ICP facility has made in-circuit programming in an embedded application - using commercially available programmers - possible with a minimum of additional expense in components and circuit board area. The ICP function uses five pins. Only a small connector needs to be available to interface your application to a commercial programmer in order to use this feature. Additional details may be found in the P89LPC9351 *User manual*.

#### 7.30.7 IAP

IAP is performed in the application under the control of the microcontroller's firmware. The IAP facility consists of internal hardware resources to facilitate programming and erasing. The NXP IAP has made in-application programming in an embedded application possible without additional components. Two methods are available to accomplish IAP. A set of predefined IAP functions are provided in a Boot ROM and can be called through a common interface, PGM\_MTP. Several IAP calls are available for use by an application program to permit selective erasing and programming of flash sectors, pages, security bits, configuration bytes, and device ID. These functions are selected by setting up the microcontroller's registers before making a call to PGM\_MTP at FF03H. The Boot ROM occupies the program memory space at the top of the address space from FF00H to FEFFH, thereby not conflicting with the user program memory space.

In addition, IAP operations can be accomplished through the use of four SFRs consisting of a control/status register, a data register, and two address registers. Additional details may be found in the P89LPC9351 *User manual*.

#### 7.30.8 ISP

ISP is performed without removing the microcontroller from the system. The ISP facility consists of a series of internal hardware resources coupled with internal firmware to facilitate remote programming of the P89LPC9351 through the serial port. This firmware is provided by NXP and embedded within each P89LPC9351 device. The NXP ISP facility has made in-system programming in an embedded application possible with a minimum of additional expense in components and circuit board area. The ISP function uses five pins (V<sub>DD</sub>, V<sub>SS</sub>, TXD, RXD, and  $\overline{RST}$ ). Only a small connector needs to be available to interface your application to an external circuit in order to use this feature.

#### 7.30.9 Power-on reset code execution

The P89LPC9351 contains two special flash elements: the Boot Vector and the Boot Status bit. Following reset, the P89LPC9351 examines the contents of the Boot Status bit. If the Boot Status bit is set to zero, power-up execution starts at location 0000H, which is the normal start address of the user's application code. When the Boot Status bit is set to a value other than zero, the contents of the Boot Vector are used as the high byte of the execution address and the low byte is set to 00H.

Table 8 shows the factory default Boot Vector setting for these devices. A factory-provided bootloader is pre-programmed into the address space indicated and uses the indicated bootloader entry point to perform ISP functions. This code can be erased by the user.

**Remark:** Users who wish to use this loader should take precautions to avoid erasing the 1 kB sector that contains this bootloader. Instead, the page erase function can be used to erase the first eight 64-byte pages located in this sector.

A custom bootloader can be written with the Boot Vector set to the custom bootloader, if desired.

| Device     | Default<br>boot vector | Default<br>bootloader<br>entry point | Default bootloader code range | 1 kB sector<br>range |

|------------|------------------------|--------------------------------------|-------------------------------|----------------------|

| P89LPC9351 | 1FH                    | 1F00H                                | 1E00H to 1FFFH                | 1C00H to 1FFFH       |

Table 8.

Default boot vector values and ISP entry points

#### 7.30.10 Hardware activation of the bootloader

The bootloader can also be executed by forcing the device into ISP mode during a power-on sequence (see the P89LPC9351 *User manual* for specific information). This has the same effect as having a non-zero status byte. This allows an application to be built that will normally execute user code but can be manually forced into ISP operation. If the factory default setting for the boot vector (1FH) is changed, it will no longer point to the factory pre-programmed ISP bootloader code. After programming the flash, the status byte should be programmed to zero in order to allow execution of the user's application code beginning at address 0000H.

#### 7.31 User configuration bytes

Some user-configurable features of the P89LPC9351 must be defined at power-up and therefore cannot be set by the program after start of execution. These features are configured through the use of the flash byte UCFG1 and UCFG2. Please see the P89LPC9351 *User's Manual* for additional details.

#### 7.32 User sector security bytes

There are eight User Sector Security Bytes on the P89LPC9351. Each byte corresponds to one sector. Please see the P89LPC9351 *User manual* for additional details.

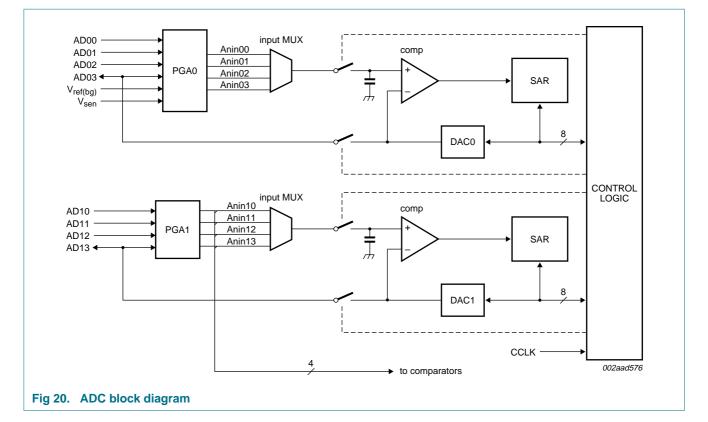

### 8. ADC

#### 8.1 General description

The P89LPC9351 has two 8-bit, 4-channel multiplexed successive approximation analog-to-digital converter modules. Two high-speed programmable gain amplifiers (PGA) are integrated. The PGAs provide selectable gains of 2x, 4x, 8x, or 16x. An on-chip temperature sensor is integrated within one of the ADC and operates over wide temperature. A block diagram of the ADC is shown in Figure 20 "ADC block diagram".

Both ADCs consist of an 4-input multiplexer which feeds a sample-and-hold circuit providing an input signal to comparator inputs. The control logic in combination with the SAR drives a digital-to-analog converter which provides the other input to the comparator. The output of the comparator is fed to the SAR.

#### 8.2 Features

- Two 8-bit, 4-channel multiplexed input, successive approximation ADCs.

- Programmable Gain Amplifier (PGA) with selectable gains of 2x, 4x, 8x, or 16x.

- On-chip wide range temperature sensor.

- Four result registers for each A/D.

- Six operating modes:

- Fixed channel, single conversion mode.

- Fixed channel, continuous conversion mode.

- Auto scan, single conversion mode.

- Auto scan, continuous conversion mode.

- Dual channel, continuous conversion mode.

- Single step mode.

- Four conversion start modes:

- Timer triggered start.

- Start immediately.

- Edge triggered.

- Dual start immediately.

- **8**-bit conversion time of  $\geq$ 1.61 µs at an A/D clock of 8.0 MHz.

- Interrupt or polled operation.

- Boundary limits interrupt.

- DAC output to a port pin with high output impedance.

- Clock divider.

- Power-down mode.

8-bit microcontroller with 8-bit ADC

#### 8.3 Block diagram

#### 8.4 PGA

Additional PGA module is integrated in each ADC module to improve the effective resolution of the ADC. A single channel can be selected for amplification. The gain of PGA can be programmable to 2, 4, 8 and 16. Please refer to <u>Table 10 "Static characteristics"</u> for detailed specifications.

Register PGACONx and PGACONxB are used to for PGA configuration. Register PGAxTRIM2X4X and PGAxTRIM8X16X provide trim value of PGA gain level. As power-on, default trim value for each gain setting is loaded into the PGA trim registers. For accurate measurements, offset calibration is required.

Please see the P89LPC9351 *User manual* for detail configuration, calibration, and usage information.

#### 8.5 Temperature sensor

An on-chip wide-temperature range temperature sensor is integrated with ADC0 module. It provides temperature sensing capability of -40 °C ~ 85 °C. It is necessary to measure the 1.2 V reference voltage via the ADC before measuring temperature. The reference voltage, temperature sensor and AD03 input pin multiplex one input to PGA0. Please see the P89LPC9351 *User manual* for detail usage of temperature sensor.

#### 8-bit microcontroller with 8-bit ADC

#### 8.9 DAC output to a port pin with high output impedance

Each ADC's DAC block can be output to a port pin. In this mode, the ADxDAT3 register is used to hold the value fed to the DAC. After a value has been written to the DAC (written to ADxDAT3), the DAC output will appear on the channel 3 pin.

#### 8.10 Clock divider

The ADC requires that its internal clock source be in the range of 320 kHz to 8 MHz to maintain accuracy. A programmable clock divider that divides the clock from 1 to 8 is provided for this purpose.

#### 8.11 Power-down and Idle mode

In Idle mode the ADC, if enabled, will continue to function and can cause the device to exit Idle mode when the conversion is completed if the A/D interrupt is enabled. In Power-down mode or Total Power-down mode, the A/D, PGA and temperature sensor do not function. If the PGAs, temperature sensor or the A/D are enabled, they will consume power. Power can be reduced by disabling the PGA, temperature sensor and A/D.

#### **NXP Semiconductors**

### P89LPC9351

#### 8-bit microcontroller with 8-bit ADC

### 12.2 ADC/PGA/temp sensor electrical characteristics

#### Table 15. ADC/PGA/temp sensor electrical characteristics

$V_{DD}$  = 2.4 V to 3.6 V, unless otherwise specified.

$T_{amb} = -40 \circ C$  to +85  $\circ C$  for industrial applications, unless otherwise specified.

All limits valid for an external source impedance of less than 10 k $\Omega$ .

| Symbol                | Parameter                     | Conditions               | Min            | Тур   | Max                    | Unit  |

|-----------------------|-------------------------------|--------------------------|----------------|-------|------------------------|-------|

| V <sub>DDA(ADC)</sub> | ADC analog supply voltage     |                          |                |       |                        |       |

| V <sub>SSA</sub>      | analog ground voltage         |                          |                |       |                        |       |

| V <sub>IA</sub>       | analog input voltage          |                          | $V_{SS} - 0.2$ | -     | V <sub>DD</sub> + 0.2  | V     |

| C <sub>ia</sub>       | analog input capacitance      |                          | -              | -     | 15                     | pF    |

| E <sub>D</sub>        | differential linearity error  |                          | -              | -     | ±1                     | LSB   |

| E <sub>L(adj)</sub>   | integral non-linearity        |                          | -              | -     | ±1                     | LSB   |

| Eo                    | offset error                  |                          | -              | -     | ±2                     | LSB   |

| E <sub>G</sub>        | gain error                    |                          | -              | -     | ±1                     | LSB   |

| E <sub>u(tot)</sub>   | total unadjusted error        |                          | -              | -     | ±2                     | LSB   |

| M <sub>CTC</sub>      | channel-to-channel matching   |                          | -              | -     | ±1                     | LSB   |

| $\alpha_{ct(port)}$   | crosstalk between port inputs | 0 kHz to 100 kHz         | -              | -     | -60                    | dB    |

| SR <sub>in</sub>      | input slew rate               |                          | -              | -     | 100                    | V/ms  |

| T <sub>cy(ADC)</sub>  | ADC clock cycle time          |                          | 111            | -     | 2000                   | ns    |

| t <sub>ADC</sub>      | ADC conversion time           | ADC enabled              | -              | -     | 13T <sub>cy(ADC)</sub> | μs    |

| PGA                   |                               |                          |                |       |                        |       |

| t <sub>s(PGA)</sub>   | PGA settling time             | within accuracy of ADC   | -              | -     | 1                      | μs    |

| G <sub>PGA</sub>      | PGA gain                      | G = 1                    | 0.95           | 1.00  | 1.05                   | V/V   |

|                       |                               | G = 2                    | 1.87           | 1.97  | 2.07                   | V/V   |

|                       |                               | G = 4                    | 3.70           | 3.89  | 4.08                   | V/V   |

|                       |                               | G = 8                    | 7.22           | 7.60  | 7.98                   | V/V   |

|                       |                               | G = 16                   | 14.38          | 15.14 | 15.90                  | V/V   |

| t <sub>startup</sub>  | start-up time                 |                          | -              | -     | 2                      | μs    |

| Voffset(O)(nom)       | nominal output offset voltage |                          | -              | 100   | -                      | mV    |

| temperature           | sensor                        |                          |                |       |                        |       |

| V <sub>sen</sub>      | sensor voltage                | T <sub>amb</sub> = +0 °C | -              | 890   | -                      | mV    |

| тс                    | temperature coefficient       |                          | -              | 11.3  | -                      | mV/°C |

|                       |                               |                          |                |       |                        |       |

8-bit microcontroller with 8-bit ADC

### **18. Contents**

| 1        | General description                      | . 1 | 7.1        |

|----------|------------------------------------------|-----|------------|

| 2        | Features                                 | . 1 | 7.19       |

| 2.1      | Principal features                       | . 1 | 7.1        |

| 2.2      | Additional features                      | . 2 | 7.2        |

| 3        | Ordering information                     | . 3 | 7.2<br>7.2 |

| 3.1      | Ordering options                         | . 3 | 7.2        |

| 4        | Block diagram                            | . 4 | 7.2        |

| 5        | Functional diagram                       | . 5 | 7.2        |

| 6        | Pinning information                      |     | 7.2        |

| 6.1      | Pinning                                  |     | 7.2        |

| 6.2      | Pin description                          |     | 7.2        |

| 7        | Functional description                   | 11  | 7.2        |

| 7.1      | Special function registers               | 11  | 7.2        |

| 7.2      | Enhanced CPU                             | 22  | 7.2        |

| 7.3      | Clocks                                   | 22  |            |

| 7.3.1    | Clock definitions                        | 22  | 7.2        |

| 7.3.2    | CPU clock (OSCCLK)                       | 22  | 7.2        |

| 7.4      | External crystal oscillator option       | 22  |            |

| 7.4.1    | Low speed oscillator option              | 22  | 7.2        |

| 7.4.2    | Medium speed oscillator option           | 22  | 7.2        |

| 7.4.3    | High speed oscillator option             | 22  | 7.2        |

| 7.5      | Clock output                             | 23  | 7.2        |

| 7.6      | On-chip RC oscillator option             | 23  | 7.2        |

| 7.7      | Watchdog oscillator option               | 23  | 7.2        |

| 7.8      | External clock input option              | 23  | 7.2        |

| 7.9      | Clock sources switch on the fly          |     | 7.2        |

| 7.10     | CCLK wake-up delay                       | 24  | 7.2        |

| 7.11     | CCLK modification: DIVM register         | 24  | 7.2        |

| 7.12     | Low power select                         | 24  | 7.2        |

| 7.13     | Memory organization                      | 25  | 7.2        |

| 7.14     | Data RAM arrangement                     |     | 7.0        |

| 7.15     | Interrupts                               | 25  | 7.2        |

| 7.15.1   | External interrupt inputs                |     | 7.0        |

| 7.16     | I/O ports                                |     | 7.2        |

| 7.16.1   | Port configurations                      |     | 7.2        |

| 7.16.1.1 | Quasi-bidirectional output configuration | 28  | 7.2        |

| 7.16.1.2 | Open-drain output configuration          | 28  | 7.2        |

| 7.16.1.3 | Input-only configuration                 | 29  | 7.2        |

| 7.16.1.4 |                                          |     | 7.2        |

| 7.16.2   | Port 0 analog functions                  |     | 7.2        |

| 7.16.3   | Additional port features                 |     | 7.2        |

| 7.17     | Power monitoring functions.              |     | 7.2        |

| 7.17.1   | Brownout detection                       |     | 7.2        |

| 7.17.2   | Power-on detection                       |     | 7.2        |

| 7.18     | Power reduction modes                    |     | 7.2        |

| 7.18.1   | Idle mode                                |     | 7.2        |

| 7.18.2   | Power-down mode                          |     | 7.3        |

| 8.3      | Total Power-down mode                               | . 31 |

|----------|-----------------------------------------------------|------|

| 9.0<br>9 | Reset                                               |      |

| 9.1      | Reset vector                                        | -    |

| 0        | Timers/counters 0 and 1                             |      |

| 0.1      | Mode 0                                              |      |

| 0.2      | Mode 1                                              |      |

| 0.2      | Mode 2                                              | -    |

| 0.4      | Mode 3                                              |      |

| 0.5      | Mode 6                                              | -    |

| 0.6      | Timer overflow toggle output                        |      |

| 1        | RTC/system timer.                                   |      |