Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | CIP-51 8051                                                            |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 25MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                            |

| Data Converters            | A/D 15x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-WFQFN Exposed Pad                                                   |

| Supplier Device Package    | 20-QFN (3x3)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8bb10f4i-a-qfn20r |

### 1. Feature List

The EFM8BB1 highlighted features are listed below.

- · Core:

- · Pipelined CIP-51 Core

- · Fully compatible with standard 8051 instruction set

- 70% of instructions execute in 1-2 clock cycles

- · 25 MHz maximum operating frequency

- · Memory:

- Up to 8 kB flash memory, in-system re-programmable from firmware.

- Up to 512 bytes RAM (including 256 bytes standard 8051 RAM and 256 bytes on-chip XRAM)

- Power

- · Internal LDO regulator for CPU core voltage

- · Power-on reset circuit and brownout detectors

- I/O: Up to 18 total multifunction I/O pins:

- · All pins 5 V tolerant under bias

- · Flexible peripheral crossbar for peripheral routing

- 5 mA source, 12.5 mA sink allows direct drive of LEDs

- · Clock Sources:

- Internal 24.5 MHz oscillator with ±2% accuracy

- · Internal 80 kHz low-frequency oscillator

- · External CMOS clock option

- · Timers/Counters and PWM:

- 3-channel programmable counter array (PCA) supporting PWM, capture/compare, and frequency output modes

- 4 x 16-bit general-purpose timers

- Independent watchdog timer, clocked from the low frequency oscillator

- · Communications and Digital Peripherals:

- UART

- SPI™ Master / Slave

- SMBus™/I2C™ Master / Slave

- 16-bit CRC unit, supporting automatic CRC of flash at 256byte boundaries

- · Analog:

- · 12-Bit Analog-to-Digital Converter (ADC)

- 2 x Low-current analog comparators with adjustable reference

- On-Chip, Non-Intrusive Debugging

- · Full memory and register inspection

- Four hardware breakpoints, single-stepping

- · Pre-loaded UART bootloader

- Temperature range -40 to 85 °C or -40 to 125 °C

- Single power supply 2.2 to 3.6 V

- QSOP24, SOIC16, and QFN20 packages

With on-chip power-on reset, voltage supply monitor, watchdog timer, and clock oscillator, the EFM8BB1 devices are truly standalone system-on-a-chip solutions. The flash memory is reprogrammable in-circuit, providing non-volatile data storage and allowing field upgrades of the firmware. The on-chip debugging interface (C2) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging. Each device is specified for 2.2 to 3.6 V operation, is AEC-Q100 qualified, and is available in 20-pin QFN, 16-pin SOIC or 24-pin QSOP packages. All package options are lead-free and RoHS compliant.

### 3.2 Power

All internal circuitry draws power from the VDD supply pin. External I/O pins are powered from the VIO supply voltage (or VDD on devices without a separate VIO connection), while most of the internal circuitry is supplied by an on-chip LDO regulator. Control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers and serial buses, have their clocks gated off and draw little power when they are not in use.

Table 3.1. Power Modes

| Power Mode | Details                                                                                                                          | Mode Entry                                             | Wake-Up Sources                   |

|------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------|

| Normal     | Core and all peripherals clocked and fully operational                                                                           | _                                                      | _                                 |

| Idle       | <ul><li>Core halted</li><li>All peripherals clocked and fully operational</li><li>Code resumes execution on wake event</li></ul> | Set IDLE bit in PCON0                                  | Any interrupt                     |

| Stop       | <ul><li>All internal power nets shut down</li><li>Pins retain state</li><li>Exit on any reset source</li></ul>                   | 1. Clear STOPCF bit in REG0CN 2. Set STOP bit in PCON0 | Any reset source                  |

| Shutdown   | <ul><li>All internal power nets shut down</li><li>Pins retain state</li><li>Exit on pin or power-on reset</li></ul>              | 1. Set STOPCF bit in REG0CN 2. Set STOP bit in PCON0   | RSTb pin reset     Power-on reset |

### 3.3 I/O

Digital and analog resources are externally available on the device's multi-purpose I/O pins. Port pins P0.0-P1.7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources through the crossbar or dedicated channels, or assigned to an analog function. Port pins P2.0 and P2.1 can be used as GPIO. Additionally, the C2 Interface Data signal (C2D) is shared with P2.0.

- Up to 18 multi-functions I/O pins, supporting digital and analog functions.

- Flexible priority crossbar decoder for digital peripheral assignment.

- · Two drive strength settings for each port.

- Two direct-pin interrupt sources with dedicated interrupt vectors (INT0 and INT1).

- Up to 16 direct-pin interrupt sources with shared interrupt vector (Port Match).

## 3.4 Clocking

The CPU core and peripheral subsystem may be clocked by both internal and external oscillator resources. By default, the system clock comes up running from the 24.5 MHz oscillator divided by 8.

- · Provides clock to core and peripherals.

- 24.5 MHz internal oscillator (HFOSC0), accurate to ±2% over supply and temperature corners.

- 80 kHz low-frequency oscillator (LFOSC0).

- External CMOS clock input (EXTCLK).

- Clock divider with eight settings for flexible clock scaling: Divide the selected clock source by 1, 2, 4, 8, 16, 32, 64, or 128.

## 3.6 Communications and Other Digital Peripherals

#### Universal Asynchronous Receiver/Transmitter (UART0)

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates. Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

The UART module provides the following features:

- · Asynchronous transmissions and receptions.

- Baud rates up to SYSCLK/2 (transmit) or SYSCLK/8 (receive).

- · 8- or 9-bit data.

- · Automatic start and stop generation.

- Single-byte FIFO on transmit and receive.

### Serial Peripheral Interface (SPI0)

The serial peripheral interface (SPI) module provides access to a flexible, full-duplex synchronous serial bus. The SPI can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select the SPI in slave mode, or to disable master mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a firmware-controlled chip-select output in master mode, or disabled to reduce the number of pins required. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

The SPI module includes the following features:

- Supports 3- or 4-wire operation in master or slave modes.

- Supports external clock frequencies up to SYSCLK / 2 in master mode and SYSCLK / 10 in slave mode.

- · Support for four clock phase and polarity options.

- · 8-bit dedicated clock clock rate generator.

- · Support for multiple masters on the same data lines.

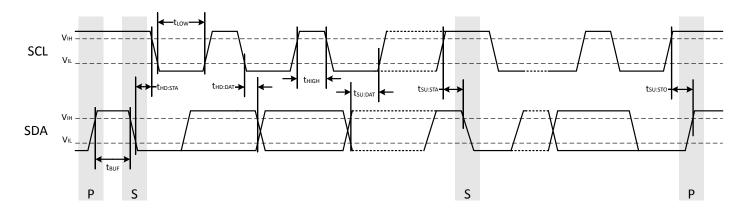

## System Management Bus / I2C (SMB0)

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus.

The SMBus module includes the following features:

- Standard (up to 100 kbps) and Fast (400 kbps) transfer speeds.

- Support for master, slave, and multi-master modes.

- · Hardware synchronization and arbitration for multi-master mode.

- Clock low extending (clock stretching) to interface with faster masters.

- · Hardware support for 7-bit slave and general call address recognition.

- Firmware support for 10-bit slave address decoding.

- Ability to inhibit all slave states.

- · Programmable data setup/hold times.

## 16-bit CRC (CRC0)

The cyclic redundancy check (CRC) module performs a CRC using a 16-bit polynomial. CRC0 accepts a stream of 8-bit data and posts the 16-bit result to an internal register. In addition to using the CRC block for data manipulation, hardware can automatically CRC the flash contents of the device.

The CRC module is designed to provide hardware calculations for flash memory verification and communications protocols. The CRC module supports the standard CCITT-16 16-bit polynomial (0x1021), and includes the following features:

- Support for CCITT-16 polynomial

- · Byte-level bit reversal

- · Automatic CRC of flash contents on one or more 256-byte blocks

- Initial seed selection of 0x0000 or 0xFFFF

### 3.7 Analog

### 12-Bit Analog-to-Digital Converter (ADC0)

The ADC is a successive-approximation-register (SAR) ADC with 12-, 10-, and 8-bit modes, integrated track-and hold and a program-mable window detector. The ADC is fully configurable under software control via several registers. The ADC may be configured to measure different signals using the analog multiplexer. The voltage reference for the ADC is selectable between internal and external reference sources.

- · Up to 16 external inputs.

- · Single-ended 12-bit and 10-bit modes.

- Supports an output update rate of 200 ksps samples per second in 12-bit mode or 800 ksps samples per second in 10-bit mode.

- Operation in low power modes at lower conversion speeds.

- Asynchronous hardware conversion trigger, selectable between software, external I/O and internal timer sources.

- Output data window comparator allows automatic range checking.

- Support for burst mode, which produces one set of accumulated data per conversion-start trigger with programmable power-on settling and tracking time.

- · Conversion complete and window compare interrupts supported.

- · Flexible output data formatting.

- Includes an internal fast-settling reference with two levels (1.65 V and 2.4 V) and support for external reference and signal ground.

- · Integrated temperature sensor.

## Low Current Comparators (CMP0, CMP1)

Analog comparators are used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. External input connections to device I/O pins and internal connections are available through separate multiplexers on the positive and negative inputs. Hysteresis, response time, and current consumption may be programmed to suit the specific needs of the application.

The comparator module includes the following features:

- · Up to 8 external positive inputs.

- Up to 8 external negative inputs.

- · Additional input options:

- · Internal connection to LDO output.

- · Direct connection to GND.

- · Synchronous and asynchronous outputs can be routed to pins via crossbar.

- Programmable hysteresis between 0 and ±20 mV

- · Programmable response time.

- · Interrupts generated on rising, falling, or both edges.

| Parameter                                                   | Symbol              | Test Condition                     | Min | Тур | Max  | Unit |

|-------------------------------------------------------------|---------------------|------------------------------------|-----|-----|------|------|

| ADC0 Always-on <sup>4</sup>                                 | I <sub>ADC</sub>    | 800 ksps, 10-bit conversions or    | _   | 845 | 1200 | μA   |

|                                                             |                     | 200 ksps, 12-bit conversions       |     |     |      |      |

|                                                             |                     | Normal bias settings               |     |     |      |      |

|                                                             |                     | V <sub>DD</sub> = 3.0 V            |     |     |      |      |

|                                                             |                     | 250 ksps, 10-bit conversions or    | _   | 425 | 580  | μA   |

|                                                             |                     | 62.5 ksps 12-bit conversions       |     |     |      |      |

|                                                             |                     | Low power bias settings            |     |     |      |      |

|                                                             |                     | V <sub>DD</sub> = 3.0 V            |     |     |      |      |

| ADC0 Burst Mode, 10-bit single                              | I <sub>ADC</sub>    | 200 ksps, V <sub>DD</sub> = 3.0 V  | _   | 370 | _    | μA   |

| conversions, external reference                             |                     | 100 ksps, V <sub>DD</sub> = 3.0 V  | _   | 185 | _    | μA   |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V   | _   | 19  | _    | μA   |

| ADC0 Burst Mode, 10-bit single                              | I <sub>ADC</sub>    | 200 ksps, V <sub>DD</sub> = 3.0 V  | _   | 490 | _    | μA   |

| conversions, internal reference,<br>Low power bias settings |                     | 100 ksps, V <sub>DD</sub> = 3.0 V  | _   | 245 | _    | μA   |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V   | _   | 23  | _    | μA   |

| ADC0 Burst Mode, 12-bit single                              | I <sub>ADC</sub>    | 100 ksps, V <sub>DD</sub> = 3.0 V  | _   | 530 | _    | μA   |

| conversions, external reference                             |                     | 50 ksps, V <sub>DD</sub> = 3.0 V   | _   | 265 | _    | μA   |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V   | _   | 53  | _    | μA   |

| ADC0 Burst Mode, 12-bit single                              | I <sub>ADC</sub>    | 100 ksps, V <sub>DD</sub> = 3.0 V, | _   | 950 | _    | μA   |

| conversions, internal reference                             |                     | Normal bias                        |     |     |      |      |

|                                                             |                     | 50 ksps, V <sub>DD</sub> = 3.0 V,  | _   | 420 | _    | μA   |

|                                                             |                     | Low power bias                     |     |     |      |      |

|                                                             |                     | 10 ksps, V <sub>DD</sub> = 3.0 V,  | _   | 85  | _    | μA   |

|                                                             |                     | Low power bias                     |     |     |      |      |

| Internal ADC0 Reference, Always-                            | I <sub>VREFFS</sub> | Normal Power Mode                  | _   | 680 | 790  | μA   |

| on <sup>5</sup>                                             |                     | Low Power Mode                     | _   | 160 | 210  | μA   |

| Temperature Sensor                                          | I <sub>TSENSE</sub> |                                    | _   | 75  | 120  | μA   |

| Comparator 0 (CMP0),                                        | I <sub>CMP</sub>    | CPMD = 11                          | _   | 0.5 | _    | μA   |

| Comparator 1 (CMP1)                                         |                     | CPMD = 10                          | _   | 3   | _    | μA   |

|                                                             |                     | CPMD = 01                          | _   | 10  | _    | μA   |

|                                                             |                     | CPMD = 00                          |     | 25  |      | μA   |

| Voltage Supply Monitor (VMON0)                              | I <sub>VMON</sub>   |                                    | _   | 15  | 20   | μA   |

| Parameter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

|           |        |                |     |     |     |      |

### Note:

- 1. Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 2. Includes supply current from internal regulator, supply monitor, and High Frequency Oscillator.

- 3. Includes supply current from internal regulator, supply monitor, and Low Frequency Oscillator.

- 4. ADC0 always-on power excludes internal reference supply current.

- 5. The internal reference is enabled as-needed when operating the ADC in burst mode to save power.

### 4.1.3 Reset and Supply Monitor

Table 4.3. Reset and Supply Monitor

| Parameter                                                            | Symbol            | Test Condition                                          | Min               | Тур   | Max  | Unit |

|----------------------------------------------------------------------|-------------------|---------------------------------------------------------|-------------------|-------|------|------|

| V <sub>DD</sub> Supply Monitor Threshold                             | V <sub>VDDM</sub> |                                                         | 1.85 <sup>1</sup> | 1.95  | 2.1  | V    |

| Power-On Reset (POR) Threshold                                       | V <sub>POR</sub>  | Rising Voltage on V <sub>DD</sub>                       | _                 | 1.4   | _    | V    |

|                                                                      |                   | Falling Voltage on V <sub>DD</sub>                      | 0.75              | _     | 1.36 | V    |

| V <sub>DD</sub> Ramp Time                                            | t <sub>RMP</sub>  | Time to V <sub>DD</sub> ≥ 2.2 V                         | 10                | _     | _    | μs   |

| Reset Delay from POR                                                 | t <sub>POR</sub>  | Relative to V <sub>DD</sub> ≥ V <sub>POR</sub>          | 3                 | 10    | 31   | ms   |

| Reset Delay from non-POR source                                      | t <sub>RST</sub>  | Time between release of reset source and code execution | _                 | 39    | _    | μs   |

| RST Low Time to Generate Reset                                       | t <sub>RSTL</sub> |                                                         | 15                | _     | _    | μs   |

| Missing Clock Detector Response<br>Time (final rising edge to reset) | t <sub>MCD</sub>  | F <sub>SYSCLK</sub> > 1 MHz                             | _                 | 0.625 | 1.2  | ms   |

| Missing Clock Detector Trigger Frequency                             | F <sub>MCD</sub>  |                                                         | _                 | 7.5   | 13.5 | kHz  |

| V <sub>DD</sub> Supply Monitor Turn-On Time                          | t <sub>MON</sub>  |                                                         | _                 | 2     | _    | μs   |

## Note:

1. MCU core, digital logic, flash memory, and RAM operation is guaranteed down to the minimum VDD Supply Monitor Threshold.

# 4.1.4 Flash Memory

Table 4.4. Flash Memory

| Parameter                                               | Symbol             | Test Condition                 | Min | Тур  | Max | Units  |

|---------------------------------------------------------|--------------------|--------------------------------|-----|------|-----|--------|

| Write Time <sup>1</sup> , <sup>2</sup>                  | t <sub>WRITE</sub> | One Byte,                      | 19  | 20   | 21  | μs     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| Erase Time <sup>1,2</sup>                               | t <sub>ERASE</sub> | One Page,                      | 5.2 | 5.35 | 5.5 | ms     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| V <sub>DD</sub> Voltage During Programming <sup>3</sup> | V <sub>PROG</sub>  |                                | 2.2 | _    | 3.6 | V      |

| Endurance (Write/Erase Cycles)                          | N <sub>WE</sub>    |                                | 20k | 100k | _   | Cycles |

| CRC Calculation Time                                    | t <sub>CRC</sub>   | One 256-Byte Block             | _   | 11   | _   | μs     |

|                                                         |                    | SYSCLK = 24.5 MHz              |     |      |     |        |

### Note:

- 1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

- 2. The internal High-Frequency Oscillator has a programmable output frequency using the HFO0CAL register, which is factory programmed to 24.5 MHz. If user firmware adjusts the oscillator speed, it must be between 22 and 25 MHz during any flash write or erase operation. It is recommended to write the HFO0CAL register back to its reset value when writing or erasing flash.

- 3. Flash can be safely programmed at any voltage above the supply monitor threshold (V<sub>VDDM</sub>).

- 4. Data Retention Information is published in the Quarterly Quality and Reliability Report.

### 4.1.5 Internal Oscillators

Table 4.5. Internal Oscillators

| Parameter                       | Symbol               | Test Condition                    | Min | Тур  | Max | Unit   |

|---------------------------------|----------------------|-----------------------------------|-----|------|-----|--------|

| High Frequency Oscillator 0 (24 | I.5 MHz)             |                                   |     |      |     |        |

| Oscillator Frequency            | f <sub>HFOSC0</sub>  | Full Temperature and Supply Range | 24  | 24.5 | 25  | MHz    |

| Power Supply Sensitivity        | PSS <sub>HFOS</sub>  | T <sub>A</sub> = 25 °C            | _   | 0.5  | _   | %/V    |

| Temperature Sensitivity         | TS <sub>HFOSC0</sub> | V <sub>DD</sub> = 3.0 V           | _   | 40   | _   | ppm/°C |

| Low Frequency Oscillator (80 k  | Hz)                  |                                   |     |      |     |        |

| Oscillator Frequency            | f <sub>LFOSC</sub>   | Full Temperature and Supply Range | 75  | 80   | 85  | kHz    |

| Power Supply Sensitivity        | PSS <sub>LFOSC</sub> | T <sub>A</sub> = 25 °C            | _   | 0.05 | _   | %/V    |

| Temperature Sensitivity         | TS <sub>LFOSC</sub>  | V <sub>DD</sub> = 3.0 V           | _   | 65   | _   | ppm/°C |

# 4.1.6 External Clock Input

# Table 4.6. External Clock Input

| Parameter                           | Symbol             | Test Condition | Min | Тур | Max | Unit |

|-------------------------------------|--------------------|----------------|-----|-----|-----|------|

| External Input CMOS Clock           | f <sub>CMOS</sub>  |                | 0   | _   | 25  | MHz  |

| Frequency (at EXTCLK pin)           |                    |                |     |     |     |      |

| External Input CMOS Clock High Time | t <sub>CMOSH</sub> |                | 18  | _   | _   | ns   |

| External Input CMOS Clock Low Time  | t <sub>CMOSL</sub> |                | 18  | _   | _   | ns   |

# 4.1.9 Temperature Sensor

Table 4.9. Temperature Sensor

| Parameter                 | Symbol           | Test Condition        | Min | Тур  | Max | Unit  |

|---------------------------|------------------|-----------------------|-----|------|-----|-------|

| Offset                    | V <sub>OFF</sub> | T <sub>A</sub> = 0 °C | _   | 757  | _   | mV    |

| Offset Error <sup>1</sup> | E <sub>OFF</sub> | T <sub>A</sub> = 0 °C | _   | 17   | _   | mV    |

| Slope                     | М                |                       | _   | 2.85 | _   | mV/°C |

| Slope Error <sup>1</sup>  | E <sub>M</sub>   |                       | _   | 70   | _   | μV/°C |

| Linearity                 |                  |                       | _   | 0.5  | _   | °C    |

| Turn-on Time              |                  |                       | _   | 1.8  | _   | μs    |

### Note:

# 4.1.10 1.8 V Internal LDO Voltage Regulator

Table 4.10. 1.8V Internal LDO Voltage Regulator

| Parameter      | Symbol                | Test Condition | Min  | Тур | Max  | Unit |

|----------------|-----------------------|----------------|------|-----|------|------|

| Output Voltage | V <sub>OUT_1.8V</sub> |                | 1.74 | 1.8 | 1.85 | V    |

<sup>1.</sup> Represents one standard deviation from the mean.

# 4.1.11 Comparators

Table 4.11. Comparators

| Parameter                      | Symbol              | Test Condition       | Min | Тур  | Max | Unit |

|--------------------------------|---------------------|----------------------|-----|------|-----|------|

| Response Time, CPMD = 00       | t <sub>RESP0</sub>  | +100 mV Differential | _   | 100  | _   | ns   |

| (Highest Speed)                |                     | -100 mV Differential | _   | 150  | _   | ns   |

| Response Time, CPMD = 11 (Low- | t <sub>RESP3</sub>  | +100 mV Differential | _   | 1.5  | _   | μs   |

| est Power)                     |                     | -100 mV Differential | _   | 3.5  | _   | μs   |

| Positive Hysterisis            | HYS <sub>CP+</sub>  | CPHYP = 00           | _   | 0.4  | _   | mV   |

| Mode 0 (CPMD = 00)             |                     | CPHYP = 01           | _   | 8    | _   | mV   |

|                                |                     | CPHYP = 10           | _   | 16   | _   | mV   |

|                                |                     | CPHYP = 11           | _   | 32   | _   | mV   |

| Negative Hysterisis            | HYS <sub>CP</sub> - | CPHYN = 00           | _   | -0.4 | _   | mV   |

| Mode 0 (CPMD = 00)             |                     | CPHYN = 01           | _   | -8   | _   | mV   |

|                                |                     | CPHYN = 10           | _   | -16  | _   | mV   |

|                                |                     | CPHYN = 11           | _   | -32  | _   | mV   |

| Positive Hysterisis            | HYS <sub>CP+</sub>  | CPHYP = 00           | _   | 0.5  | _   | mV   |

| Mode 1 (CPMD = 01)             |                     | CPHYP = 01           | _   | 6    | _   | mV   |

|                                |                     | CPHYP = 10           | _   | 12   | _   | mV   |

|                                |                     | CPHYP = 11           | _   | 24   | _   | mV   |

| Negative Hysterisis            | HYS <sub>CP</sub> - | CPHYN = 00           | _   | -0.5 | _   | mV   |

| Mode 1 (CPMD = 01)             |                     | CPHYN = 01           | _   | -6   | _   | mV   |

|                                |                     | CPHYN = 10           | _   | -12  | _   | mV   |

|                                |                     | CPHYN = 11           | _   | -24  | _   | mV   |

| Positive Hysterisis            | HYS <sub>CP+</sub>  | CPHYP = 00           | _   | 0.7  | _   | mV   |

| Mode 2 (CPMD = 10)             |                     | CPHYP = 01           | _   | 4.5  | _   | mV   |

|                                |                     | CPHYP = 10           | _   | 9    | _   | mV   |

|                                |                     | CPHYP = 11           | _   | 18   | _   | mV   |

| Negative Hysterisis            | HYS <sub>CP</sub> - | CPHYN = 00           | _   | -0.6 | _   | mV   |

| Mode 2 (CPMD = 10)             |                     | CPHYN = 01           | _   | -4.5 | _   | mV   |

|                                |                     | CPHYN = 10           | _   | -9   | _   | mV   |

|                                |                     | CPHYN = 11           | _   | -18  | _   | mV   |

| Positive Hysteresis            | HYS <sub>CP+</sub>  | CPHYP = 00           | _   | 1.5  | _   | mV   |

| Mode 3 (CPMD = 11)             |                     | CPHYP = 01           | _   | 4    | _   | mV   |

|                                |                     | CPHYP = 10           | _   | 8    | _   | mV   |

|                                |                     | CPHYP = 11           | _   | 16   | _   | mV   |

| Parameter                    | Symbol              | Test Condition         | Min   | Тур  | Max                   | Unit  |

|------------------------------|---------------------|------------------------|-------|------|-----------------------|-------|

| Negative Hysteresis          | HYS <sub>CP</sub> - | CPHYN = 00             | _     | -1.5 | _                     | mV    |

| Mode 3 (CPMD = 11)           |                     | CPHYN = 01             | _     | -4   | _                     | mV    |

|                              |                     | CPHYN = 10             | _     | -8   | _                     | mV    |

|                              |                     | CPHYN = 11             | _     | -16  | _                     | mV    |

| Input Range (CP+ or CP-)     | V <sub>IN</sub>     |                        | -0.25 | _    | V <sub>DD</sub> +0.25 | V     |

| Input Pin Capacitance        | C <sub>CP</sub>     |                        | _     | 7.5  | _                     | pF    |

| Common-Mode Rejection Ratio  | CMRR <sub>CP</sub>  |                        | _     | 70   | _                     | dB    |

| Power Supply Rejection Ratio | PSRR <sub>CP</sub>  |                        | _     | 72   | _                     | dB    |

| Input Offset Voltage         | V <sub>OFF</sub>    | T <sub>A</sub> = 25 °C | -10   | 0    | 10                    | mV    |

| Input Offset Tempco          | TC <sub>OFF</sub>   |                        | _     | 3.5  | _                     | μV/°C |

# 4.1.12 Port I/O

Table 4.12. Port I/O

| Parameter                                          | Symbol          | Test Condition                                             | Min                   | Тур  | Max  | Unit |

|----------------------------------------------------|-----------------|------------------------------------------------------------|-----------------------|------|------|------|

| Output High Voltage (Low Drive) <sup>1</sup>       | V <sub>OH</sub> | I <sub>OH</sub> = -1 mA                                    | V <sub>DD</sub> – 0.7 | _    | _    | V    |

| Output High Voltage (High Drive) <sup>1</sup>      | V <sub>OH</sub> | I <sub>OH</sub> = -3 mA                                    | V <sub>DD</sub> - 0.7 | _    | _    | V    |

| Output Low Voltage (Low Drive) <sup>1</sup>        | V <sub>OL</sub> | I <sub>OL</sub> = 1.4 mA                                   | _                     | _    | 0.6  | V    |

| Output Low Voltage (High Drive) <sup>1</sup>       | V <sub>OL</sub> | I <sub>OL</sub> = 8.5 mA                                   | _                     | _    | 0.6  | V    |

| Output Low Voltage (High Drive) <sup>1</sup>       | V <sub>OL</sub> | I <sub>OL</sub> = 10 mA                                    | _                     | 0.25 | 0.33 | V    |

|                                                    |                 | -10 °C ≤ T <sub>A</sub> ≤ 60 °C                            |                       |      |      |      |

|                                                    |                 | V <sub>DD</sub> = 3.0 V                                    |                       |      |      |      |

|                                                    |                 | Guaranteed by characterization                             |                       |      |      |      |

| Output Low Voltage (High Drive) <sup>1</sup>       | V <sub>OL</sub> | I <sub>OL</sub> = 10 mA                                    | _                     | 0.23 | 0.31 | V    |

|                                                    |                 | -10 °C ≤ T <sub>A</sub> ≤ 60 °C                            |                       |      |      |      |

|                                                    |                 | V <sub>DD</sub> = 3.6 V                                    |                       |      |      |      |

|                                                    |                 | Guaranteed by characterization                             |                       |      |      |      |

| Input High Voltage                                 | V <sub>IH</sub> |                                                            | V <sub>DD</sub> - 0.6 | _    | _    | V    |

| Input Low Voltage                                  | V <sub>IL</sub> |                                                            | _                     | _    | 0.6  | V    |

| Pin Capacitance                                    | C <sub>IO</sub> |                                                            | _                     | 7    | _    | pF   |

| Weak Pull-Up Current                               | I <sub>PU</sub> | V <sub>DD</sub> = 3.6                                      | -30                   | -20  | -10  | μA   |

| (V <sub>IN</sub> = 0 V)                            |                 |                                                            |                       |      |      |      |

| Input Leakage (Pullups off or Analog)              | I <sub>LK</sub> | GND < V <sub>IN</sub> < V <sub>DD</sub>                    | -1.1                  | _    | 1.1  | μА   |

| Input Leakage Current with $V_{IN}$ above $V_{DD}$ | I <sub>LK</sub> | V <sub>DD</sub> < V <sub>IN</sub> < V <sub>DD</sub> +2.0 V | 0                     | 5    | 150  | μА   |

# Note:

1. See Figure 4.6 Typical  $V_{OH}$  Curves on page 30 and Figure 4.7 Typical  $V_{OL}$  Curves on page 30 for more information.

| Parameter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

|           |        |                |     |     |     |      |

### Note:

- 1. The minimum SMBus frequency is limited by the maximum Clock High Period requirement of the SMBus specification.

- 2. The maximum I2C and SMBus frequencies are limited by the minimum Clock Low Period requirements of their respective specifications. The maximum frequency cannot be achieved with all combinations of oscillators and dividers available, but the effective frequency must not exceed 256 kHz.

- 3. Data setup and hold timing at 25 MHz or lower with EXTHOLD set to 1.

- 4. SMBus has a maximum requirement of 50  $\mu$ s for Clock High Period. Operating frequencies lower than 40 kHz will be longer than 50  $\mu$ s. I2C can support periods longer than 50  $\mu$ s.

Table 4.14. SMBus Peripheral Timing Formulas (Master Mode)

| Parameter                                       | Symbol              | Clocks               |

|-------------------------------------------------|---------------------|----------------------|

| SMBus Operating Frequency                       | f <sub>SMB</sub>    | f <sub>CSO</sub> / 3 |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    | 2 / f <sub>CSO</sub> |

| Hold Time After (Repeated) START Condition      | t <sub>HD:STA</sub> | 1 / f <sub>CSO</sub> |

| Repeated START Condition Setup Time             | t <sub>SU:STA</sub> | 2 / f <sub>CSO</sub> |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub> | 2 / f <sub>CSO</sub> |

| Clock Low Period                                | t <sub>LOW</sub>    | 1/f <sub>CSO</sub>   |

| Clock High Period                               | t <sub>HIGH</sub>   | 2 / f <sub>CSO</sub> |

### Note:

$1.\,f_{\mbox{\footnotesize{CSO}}}$  is the SMBus peripheral clock source overflow frequency.

Figure 4.1. SMBus Peripheral Timing Diagram (Master Mode)

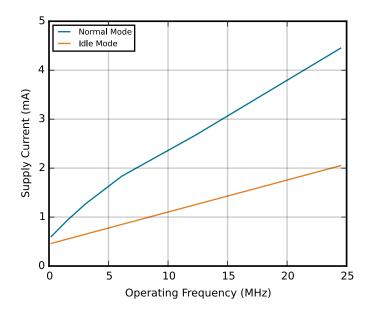

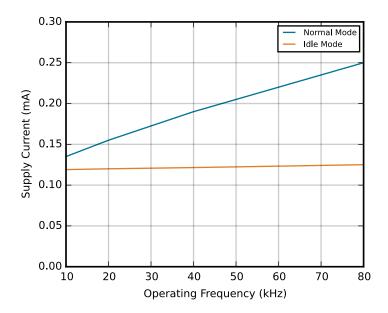

# 4.4 Typical Performance Curves

Figure 4.2. Typical Operating Supply Current using HFOSC0

Figure 4.3. Typical Operating Supply Current using LFOSC

# 5.3 Other Connections

Other components or connections may be required to meet the system-level requirements. Application note, "AN203: 8-bit MCU Printed Circuit Board Design Notes", contains detailed information on these connections. Application Notes can be accessed on the Silicon Labs website (www.silabs.com/8bit-appnotes).

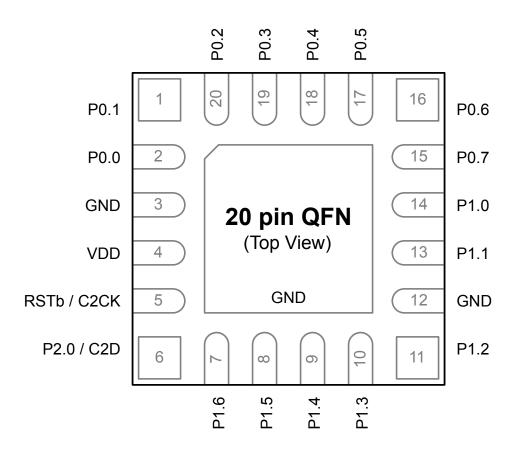

Figure 6.2. EFM8BB1x-QFN20 Pinout

Table 6.2. Pin Definitions for EFM8BB1x-QFN20

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 1             | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                      | ADC0.1           |

|               |          |                   |                     | INT0.1                       | CMP0P.1          |

|               |          |                   |                     | INT1.1                       | CMP0N.1          |

|               |          |                   |                     |                              | AGND             |

| 2             | P0.0     | Multifunction I/O | Yes                 | P0MAT.0                      | ADC0.0           |

|               |          |                   |                     | INT0.0                       | CMP0P.0          |

|               |          |                   |                     | INT1.0                       | CMP0N.0          |

|               |          |                   |                     |                              | VREF             |

| Pin    | Pin Name | Description         | Crossbar Capability | Additional Digital | Analog Functions |

|--------|----------|---------------------|---------------------|--------------------|------------------|

| Number |          |                     |                     | Functions          |                  |

| 3      | GND      | Ground              |                     |                    |                  |

| 4      | VDD      | Supply Power Input  |                     |                    |                  |

| 5      | RSTb /   | Active-low Reset /  |                     |                    |                  |

|        | C2CK     | C2 Debug Clock      |                     |                    |                  |

| 6      | P2.0 /   | Multifunction I/O / |                     |                    |                  |

|        | C2D      | C2 Debug Data       |                     |                    |                  |

| 7      | P1.6     | Multifunction I/O   | Yes                 | P1MAT.6            | ADC0.14          |

|        |          |                     |                     |                    | CMP1P.6          |

|        |          |                     |                     |                    | CMP1N.6          |

| 8      | P1.5     | Multifunction I/O   | Yes                 | P1MAT.5            | ADC0.13          |

|        |          |                     |                     |                    | CMP1P.5          |

|        |          |                     |                     |                    | CMP1N.5          |

| 9      | P1.4     | Multifunction I/O   | Yes                 | P1MAT.4            | ADC0.12          |

|        |          |                     |                     |                    | CMP1P.4          |

|        |          |                     |                     |                    | CMP1N.4          |

| 10     | P1.3     | Multifunction I/O   | Yes                 | P1MAT.3            | ADC0.11          |

|        |          |                     |                     |                    | CMP1P.3          |

|        |          |                     |                     |                    | CMP1N.3          |

| 11     | P1.2     | Multifunction I/O   | Yes                 | P1MAT.2            | ADC0.10          |

|        |          |                     |                     |                    | CMP1P.2          |

|        |          |                     |                     |                    | CMP1N.2          |

| 12     | GND      | Ground              |                     |                    |                  |

| 13     | P1.1     | Multifunction I/O   | Yes                 | P1MAT.1            | ADC0.9           |

|        |          |                     |                     |                    | CMP1P.1          |

|        |          |                     |                     |                    | CMP1N.1          |

| 14     | P1.0     | Multifunction I/O   | Yes                 | P1MAT.0            | ADC0.8           |

|        |          |                     |                     |                    | CMP1P.0          |

|        |          |                     |                     |                    | CMP1N.0          |

| 15     | P0.7     | Multifunction I/O   | Yes                 | P0MAT.7            | ADC0.7           |

|        |          |                     |                     | INT0.7             | CMP0P.7          |

|        |          |                     |                     | INT1.7             | CMP0N.7          |

| 16     | P0.6     | Multifunction I/O   | Yes                 | P0MAT.6            | ADC0.6           |

|        |          |                     |                     | CNVSTR             | CMP0P.6          |

|        |          |                     |                     | INT0.6             | CMP0N.6          |

|        |          |                     |                     | INT1.6             |                  |

| Dimension | Min  | Тур  | Max |  |

|-----------|------|------|-----|--|

| aaa       | 0.20 |      |     |  |

| bbb       | 0.18 |      |     |  |

| ccc       |      | 0.10 |     |  |

| ddd       | 0.10 |      |     |  |

# Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

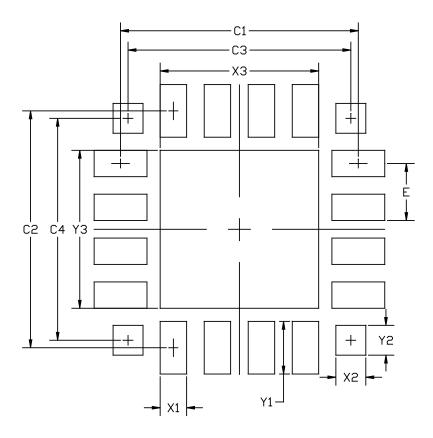

# 8.2 QFN20 PCB Land Pattern

Figure 8.2. QFN20 PCB Land Pattern Drawing

Table 8.2. QFN20 PCB Land Pattern Dimensions

| Dimension | Min  | Max  |  |  |

|-----------|------|------|--|--|

| C1        | 3.10 |      |  |  |

| C2        | 3.10 | 3.10 |  |  |

| C3        | 2.50 | )    |  |  |

| C4        | 2.50 | )    |  |  |

| E         | 0.50 | 0.50 |  |  |

| X1        | 0.30 | 0.30 |  |  |

| X2        | 0.25 | 0.35 |  |  |

| Х3        | 1.80 |      |  |  |

| Y1        | 0.90 |      |  |  |

| Y2        | 0.25 | 0.35 |  |  |

| Y3        | 1.80 |      |  |  |

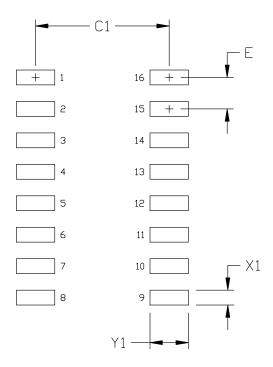

## 9.2 SOIC16 PCB Land Pattern

Figure 9.2. SOIC16 PCB Land Pattern Drawing

Table 9.2. SOIC16 PCB Land Pattern Dimensions

| Dimension | Feature            | (mm) |

|-----------|--------------------|------|

| C1        | Pad Column Spacing | 5.40 |

| E         | Pad Row Pitch      | 1.27 |

| X1        | Pad Width          | 0.60 |

| Y1        | Pad Length         | 1.55 |

## Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on IPC-7351 pattern SOIC127P600X165-16N for Density Level B (Median Land Protrusion).

- 3. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.