Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                      |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | STM8A                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

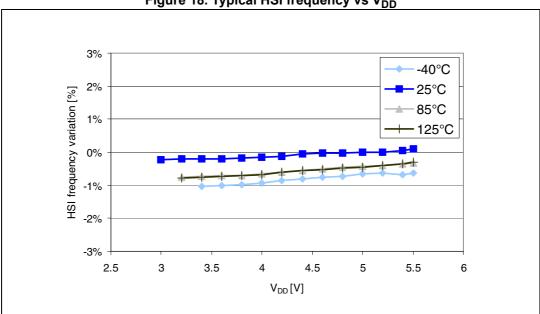

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

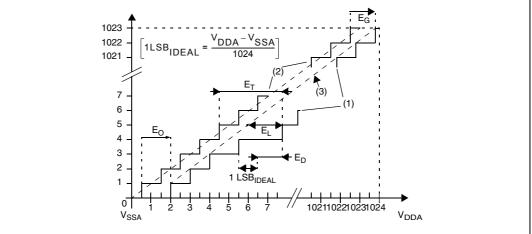

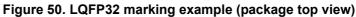

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6246tasssy |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet refers to the STM8AF6246, STM8AF6248, STM8AF6266 and STM8AF6268 products with 16 to 32 Kbyte of Flash program memory.

In the order code, the letter 'F' refers to product versions with data EEPROM and 'H' refers to product versions without data EEPROM. The identifiers 'F' and 'H' do not coexist in a given order code.

The datasheet contains the description of family features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8 Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

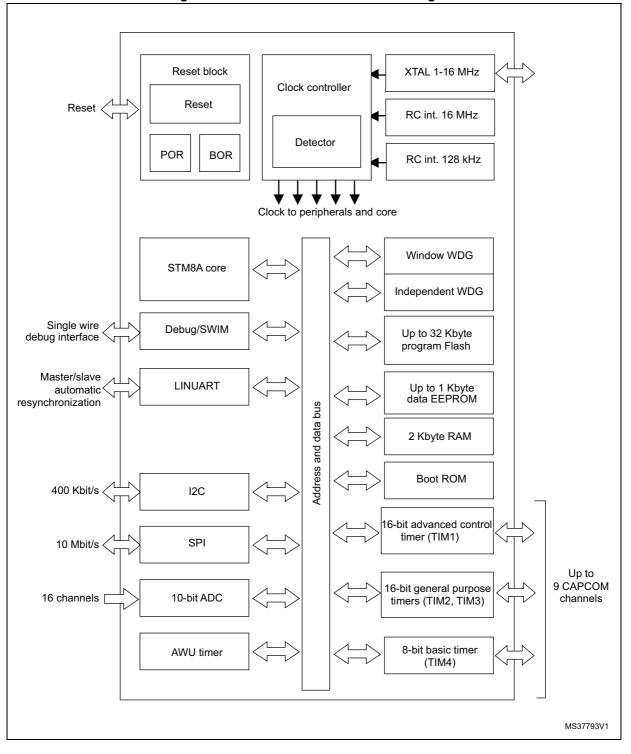

# 4 Block diagram

Legend: ADC: Analog-to-digital converter beCAN: Controller area network BOR: Brownout reset I<sup>2</sup>C: Inter-integrated circuit multimaster interface IWDG: Independent window watchdog LINUART: Local interconnect network universal asynchronous receiver transmitter POR: Power on reset SPI: Serial peripheral interface SWIM: Single wire interface module USART: Universal synchronous asynchronous receiver transmitter Window WDG: Window watchdog

### 5.4.4 Read-out protection (ROP)

The STM8A provides a read-out protection of the code and data memory which can be activated by an option byte setting (see the ROP option byte in section 10).

The read-out protection prevents reading and writing Flash program memory, data memory and option bytes via the debug module and SWIM interface. This protection is active in all device operation modes. Any attempt to remove the protection by overwriting the ROP option byte triggers a global erase of the program and data memory.

The ROP circuit may provide a temporary access for debugging or failure analysis. The temporary read access is protected by a user defined, 8-byte keyword stored in the option bytes area. This keyword must be entered via the SWIM interface to temporarily unlock the device.

If desired, the temporary unlock mechanism can be permanently disabled by the user through OPT6/NOPT6 option bytes.

### 5.5 Clock controller

The clock controller distributes the system clock coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness.

### 5.5.1 Features

#### Clock sources

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

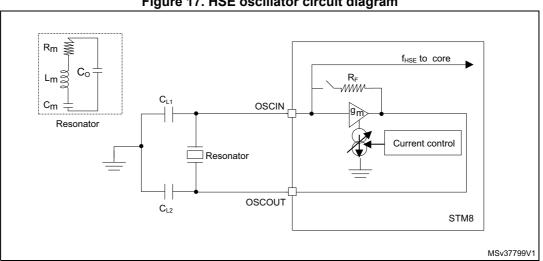

- 1-16 MHz high-speed external crystal (HSE)

- Up to 16 MHz high-speed user-external clock (HSE user-ext)

- Reset: After reset the microcontroller restarts by default with an internal 2-MHz clock (16 MHz/8). The clock source and speed can be changed by the application program as soon as the code execution starts.

- **Safe clock switching**: Clock sources can be changed safely on the fly in Run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management**: To reduce power consumption, the clock controller can stop the clock to the core or individual peripherals.

- Wakeup: In case the device wakes up from low-power modes, the internal RC oscillator (16 MHz/8) is used for quick startup. After a stabilization time, the device switches to the clock source that was selected before Halt mode was entered.

- Clock security system (CSS): The CSS permits monitoring of external clock sources and automatic switching to the internal RC (16 MHz/8) in case of a clock failure.

- **Configurable main clock output (CCO)**: This feature permits to output a clock signal for use by the application.

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure. If the hardware watchdog feature is enabled through the device option bits, the watchdog is automatically enabled at power-on, and generates a reset unless the key register is written by software before the counter reaches the end of count.

### 5.7.2 Auto-wakeup counter

This counter is used to cyclically wakeup the device in Active-halt mode. It can be clocked by the internal 128 kHz internal low-frequency RC oscillator or external clock.

LSI clock can be internally connected to TIM3 input capture channel 1 for calibration.

### 5.7.3 Beeper

This function generates a rectangular signal in the range of 1, 2 or 4 kHz which can be output on a pin. This is useful when audible sounds without interference need to be generated for use in the application.

### 5.7.4 Advanced control and general purpose timers

STM8A devices described in this datasheet, contain up to three 16-bit advanced control and general purpose timers providing nine CAPCOM channels in total. A CAPCOM channel can be used either as input compare, output compare or PWM channel. These timers are named TIM1, TIM2 and TIM3.

| Timer | Counter<br>width | Counter<br>type | Prescaler<br>factor           | Channels | Inverted outputs | Repetition counter | trigger<br>unit | External trigger | Break<br>input |

|-------|------------------|-----------------|-------------------------------|----------|------------------|--------------------|-----------------|------------------|----------------|

| TIM1  | 16-bit           | Up/down         | 1 to 65536                    | 4        | 3                | Yes                | Yes             | Yes              | Yes            |

| TIM2  | 16-bit           | Up              | 2 <sup>n</sup><br>n = 0 to 15 | 3        | None             | No                 | No              | No               | No             |

| TIM3  | 16-bit           | Up              | 2 <sup>n</sup><br>n = 0 to 15 | 2        | None             | No                 | No              | No               | No             |

#### Table 3. Advanced control and general purpose timers

| Pi     | -             |                             |      |          |      |                | •         |       | ,   |    |                                |                               |                                                      |

|--------|---------------|-----------------------------|------|----------|------|----------------|-----------|-------|-----|----|--------------------------------|-------------------------------|------------------------------------------------------|

| num    |               |                             |      |          | Inpu | t              |           | Out   | put |    |                                |                               |                                                      |

| LQFP48 | VFQFPN/LQFP32 | Pin name                    | Type | floating | wpu  | Ext. interrupt | High sink | Speed | OD  | ЬР | Main function<br>(after reset) | Default alternate<br>function | Alternate<br>function after<br>remap<br>[option bit] |

| 1      | 1             | NRST                        | I/O  | -        | Х    | -              | -         | -     | -   | -  | Reset                          | •                             | -                                                    |

| 2      | 2             | PA1/OSCIN <sup>(3)</sup>    | I/O  | Χ        | Х    | -              | -         | 01    | Х   | Х  | Port A1                        | Resonator/crystal in          | -                                                    |

| 3      | 3             | PA2/OSCOUT                  | I/O  | Χ        | Х    | Х              | -         | 01    | Х   | Х  | Port A2                        | Resonator/crystal out         | -                                                    |

| 4      | -             | V <sub>SSIO_1</sub>         | S    | -        | -    | -              | -         | -     | -   | -  | I/O groun                      | d                             | -                                                    |

| 5      | 4             | V <sub>SS</sub>             | S    | -        | -    | -              | -         | -     | -   | -  | Digital gro                    | bund                          | -                                                    |

| 6      | 5             | VCAP                        | S    | -        | -    | -              | -         | -     | -   | -  | 1.8 V reg                      | ulator capacitor              | -                                                    |

| 7      | 6             | V <sub>DD</sub>             | S    | -        | -    | -              | -         | -     | -   | -  | Digital po                     | wer supply                    | -                                                    |

| 8      | 7             | V <sub>DDIO_1</sub>         | S    | -        | -    | -              | -         | -     | -   | -  | I/O power supply               |                               | -                                                    |

| -      | 8             | PF4/AIN12 <sup>(4)(5)</sup> | I/O  | X        | Х    |                | -         | 01    | Х   | Х  | Port F4                        | Analog input 12               | -                                                    |

| 9      | -             | PA3/TIM2_CH3                | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port A3                        | Timer 2 - channel 3           | TIM3_CH1<br>[AFR1]                                   |

| 10     | -             | PA4                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A4                        |                               | -                                                    |

| 11     | -             | PA5                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A5                        |                               | -                                                    |

| 12     | -             | PA6                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A6                        |                               | -                                                    |

| 13     | 9             | V <sub>DDA</sub>            | S    | -        | -    | -              | -         | -     | -   | -  | Analog po                      | ower supply                   | -                                                    |

| 14     | 10            | V <sub>SSA</sub>            | S    | -        | -    | -              | -         | -     | -   | -  | Analog gr                      | ound                          | -                                                    |

| 15     | -             | PB7/AIN7                    | I/O  | Х        | Х    | Х              | -         | 01    | Х   | Х  | Port B7                        | Analog input 7                | -                                                    |

| 16     | -             | PB6/AIN6                    | I/O  | Х        | Х    | Х              | -         | 01    | Х   | Х  | Port B6                        | Analog input 6                | -                                                    |

| 17     | 11            | PB5/AIN5                    | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port B5                        | Analog input 5                | I <sup>2</sup> C_SDA<br>[AFR6]                       |

| 18     | 12            | PB4/AIN4                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B4                        | Analog input 4                | I <sup>2</sup> C_SCL<br>[AFR6]                       |

| 19     | 13            | PB3/AIN3                    | I/O  | x        | х    | х              | I         | 01    | х   | х  | Port B3                        | Analog input 3                | TIM1_ETR<br>[AFR5]                                   |

| 20     | 14            | PB2/AIN2                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B2                        | Analog input                  | TIM1_NCC3<br>[AFR5]                                  |

| 21     | 15            | PB1/AIN1                    | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port B1                        | Analog input 1                | TIM1_NCC2<br>[AFR5]                                  |

| 22     | 16            | PB0/AIN0                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B0                        | Analog input 0                | TIM1_NCC1<br>[AFR5]                                  |

| 23     | -             | PE7/AIN8                    | I/O  | X        | Х    |                | -         | 01    | Х   | Х  | Port E7                        | Analog input 8                | -                                                    |

| Table 8. STM8AF6246/48/66/68 ( | (32 Kbv | vte) micro | ocontroller | pin descri | ption <sup>(1)(2)</sup> |

|--------------------------------|---------|------------|-------------|------------|-------------------------|

|                                |         |            |             | pin acour  | puon                    |

| AddressBlockRegister labelRegister nameRest status0x00 5300ADC_DB0RHADC data buffer register 0 high0x000x00 5321ADC_DB0RLADC data buffer register 1 high0x000x00 5323ADC_DB1RLADC data buffer register 1 high0x000x00 5324ADC_DB1RLADC data buffer register 1 high0x000x00 5355ADC_DB1RLADC data buffer register 1 high0x000x00 5356ADC_DB3RLADC data buffer register 2 high0x000x00 5357ADC_DB3RLADC data buffer register 3 high0x000x00 5368ADC_DB3RLADC data buffer register 4 high0x000x00 5369ADC_DB3RLADC data buffer register 4 high0x000x00 5360ADC_DB4RLADC data buffer register 4 high0x000x00 5361ADC_DB5RLADC data buffer register 5 high0x000x00 5362ADC_DB5RLADC data buffer register 5 high0x000x00 5362ADC_DB5RLADC data buffer register 6 high0x000x00 5376ADC_DB7RLADC data buffer register 7 high0x000x00 5376ADC_DB8RLADC data buffer register 7 h                                                                                                                                                                                                                                                                                      |           | Table 1 | 1. General hardw | /are register map (continued)    |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------------------|----------------------------------|------|

| 0x00 53E1         ADC_DB0RL         ADC data buffer register 0 low         0x00           0x00 53E2         ADC_DB1RH         ADC data buffer register 1 high         0x00           0x00 53E3         ADC_DB1RL         ADC data buffer register 1 high         0x00           0x00 53E4         ADC_DB2RH         ADC data buffer register 2 high         0x00           0x00 53E5         ADC_DB3RL         ADC data buffer register 2 high         0x00           0x00 53E6         ADC_DB3RL         ADC data buffer register 3 high         0x00           0x00 53E8         ADC_DB4RL         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB5RL         ADC data buffer register 4 low         0x00           0x00 53E8         ADC_DB6RL         ADC data buffer register 5 high         0x00           0x00 53E8         ADC_DB6RL         ADC data buffer register 6 high         0x00           0x00 53E8         ADC_DB7RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 8 high         0x00           0x00 53F3                                                                                                    | Address   | Block   | Register label   | Register name                    |      |

| 0x00 53E2         ADC_DB1RH         ADC data buffer register 1 high         0x00           0x00 53E3         ADC_DB1RL         ADC data buffer register 1 low         0x00           0x00 53E4         ADC_DB2RH         ADC data buffer register 2 high         0x00           0x00 53E5         ADC_DB2RL         ADC data buffer register 2 high         0x00           0x00 53E6         ADC_DB3RH         ADC data buffer register 3 high         0x00           0x00 53E7         ADC_DB4RH         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB4RL         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB5RL         ADC data buffer register 5 high         0x00           0x00 53E8         ADC_DB6RL         ADC data buffer register 5 low         0x00           0x00 53E8         ADC_DB7RL         ADC data buffer register 6 high         0x00           0x00 53E9         ADC_DB7RL         ADC data buffer register 7 high         0x00           0x00 53F0         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 8 high         0x00           0x00 53F5                                                                                                    | 0x00 53E0 |         | ADC _DB0RH       | ADC data buffer register 0 high  | 0x00 |

| 0x00 53E3         ADC_DB1RL         ADC data buffer register 1 low         0x00           0x00 53E4         ADC_DB2RH         ADC data buffer register 2 high         0x00           0x00 53E5         ADC_DB2RL         ADC data buffer register 2 low         0x00           0x00 53E6         ADC_DB3RH         ADC data buffer register 3 high         0x00           0x00 53E7         ADC_DB3RL         ADC data buffer register 3 low         0x00           0x00 53E8         ADC_DB4RH         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB4RL         ADC data buffer register 4 low         0x00           0x00 53E8         ADC_DB5RH         ADC data buffer register 4 low         0x00           0x00 53E8         ADC_DB5RL         ADC data buffer register 5 low         0x00           0x00 53E8         ADC_DB6RH         ADC data buffer register 6 high         0x00           0x00 53E6         ADC_DB7RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 8 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 9 high         0x00           0x00 53F3 <td>0x00 53E1</td> <td></td> <td>ADC _DB0RL</td> <td>ADC data buffer register 0 low</td> <td>0x00</td> | 0x00 53E1 |         | ADC _DB0RL       | ADC data buffer register 0 low   | 0x00 |

| 0x00 53E4<br>0x00 53E5<br>0x00 53E5ADC _DB2RHADC data buffer register 2 high0x000x00 53E6<br>0x00 53E7<br>0x00 53E8<br>0x00 53E8<br>0x00 53E8ADC _DB3RHADC data buffer register 3 high0x000x00 53E8<br>0x00 53E8<br>0x00 53E8ADC _DB4RHADC data buffer register 3 high0x000x00 53E6<br>0x00 53E8<br>0x00 53E8ADC _DB4RHADC data buffer register 4 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 4 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6<br>0x00 53E6ADC _DB6RHADC data buffer register 6 high0x000x00 53E6<br>0x00 53E6ADC _DB7RHADC data buffer register 6 high0x000x00 53E7<br>0x00 53F1ADC _DB7RHADC data buffer register 7 high0x000x00 53F1<br>0x00 53F2ADC _DB8RHADC data buffer register 7 high0x000x00 53F3ADC _DB8RHADC data buffer register 8 high0x000x00 53F4 to<br>0x00 53F4<br>0x00 53F4ADC _DB8RHADC control/status register0x000x00 53F4 to<br>0x00 53F4ADC _CR1ADC configuration register 10x000x00 5400<br>0x00 5401ADC _CR2ADC configuration register 20x000x00 5403<br>0x00 5404ADC _DRHADC configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5407ADC _DRHADC configuration register 10x000x00 5408ADC _TDRHADC Configuration register 10x0                                                                                                                                                                    | 0x00 53E2 |         | ADC _DB1RH       | ADC data buffer register 1 high  | 0x00 |

| ADC _DB2RLADC data buffer register 2 low0x000x00 53E6ADC _DB3RHADC data buffer register 3 high0x000x00 53E7ADC _DB3RLADC data buffer register 3 low0x000x00 53E8ADC _DB4RHADC data buffer register 4 high0x000x00 53E9ADC _DB5RHADC data buffer register 4 low0x000x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6ADC _DB5RLADC data buffer register 5 low0x000x00 53E6ADC _DB5RLADC data buffer register 6 high0x000x00 53E6ADC _DB6RHADC data buffer register 7 low0x000x00 53E6ADC _DB6RLADC data buffer register 7 high0x000x00 53E6ADC _DB7RHADC data buffer register 7 low0x000x00 53F1ADC _DB7RLADC data buffer register 7 low0x000x00 53F2ADC _DB7RLADC data buffer register 8 low0x000x00 53F3ADC _DB8RHADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53F6ADC _DB9RLADC data buffer register 9 low0x000x00 53F4ADC _CRSRADC control/status register0x000x00 5402ADC_CR2ADC configuration register 10x000x00 5403ADC_DRHADC data register low0xXX0x00 5404ADC_CR3ADC configuration register 30x000x00 5405ADC_CR3ADC configuration register 10x000x00 5406ADC_DRHADC data register low0xXX0x00 5406 </td <td>0x00 53E3</td> <td></td> <td>ADC _DB1RL</td> <td>ADC data buffer register 1 low</td> <td>0x00</td>                                                                                                                                                                                      | 0x00 53E3 |         | ADC _DB1RL       | ADC data buffer register 1 low   | 0x00 |

| 0x00 53E6<br>0x00 53E7ADC _DB3RHADC data buffer register 3 high0x000x00 53E8<br>0x00 53E9ADC _DB4RHADC data buffer register 4 high0x000x00 53E8<br>0x00 53E4ADC _DB4RLADC data buffer register 4 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6<br>0x00 53E6ADC _DB6RHADC data buffer register 6 high0x000x00 53E6<br>0x00 53E6ADC _DB6RHADC data buffer register 6 high0x000x00 53E6<br>0x00 53E7ADC _DB7RHADC data buffer register 7 high0x000x00 53F1<br>0x00 53F1ADC _DB7RHADC data buffer register 7 high0x000x00 53F2ADC _DB7RHADC data buffer register 8 high0x000x00 53F3ADC _DB7RHADC data buffer register 8 high0x000x00 53F3ADC _DB8RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4<br>0x00 5402ADC _DB9RHADC control/status register 9 low0x000x00 5402<br>0x00 5403ADC_CR3ADC configuration register 10x000x00 5403<br>0x00 5404ADC_DRHADC configuration register 30x000x00 5406ADC_DRHADC configuration register 10w0xXX0x00 5406ADC_CR3ADC configuration register 10w0xXX0x00 5406ADC_DRHADC data register high0x000x00 5406ADC_DRHADC data register low0xXX0x00 54                                                                                                                                                                                                                           | 0x00 53E4 |         | ADC _DB2RH       | ADC data buffer register 2 high  | 0x00 |

| 0x00 53E7ADC _DB3RLADC data buffer register 3 low0x000x00 53E8ADC _DB4RHADC data buffer register 4 low0x000x00 53E4ADC _DB4RLADC data buffer register 4 low0x000x00 53E6ADC _DB5RHADC data buffer register 5 low0x000x00 53E6ADC _DB6RHADC data buffer register 5 low0x000x00 53E7ADC _DB6RHADC data buffer register 6 low0x000x00 53E7ADC _DB6RHADC data buffer register 7 low0x000x00 53F6ADC _DB7RHADC data buffer register 7 low0x000x00 53F7ADC _DB8RLADC data buffer register 7 low0x000x00 53F1ADC _DB8RHADC data buffer register 8 low0x000x00 53F2ADC _DB8RHADC data buffer register 8 low0x000x00 53F4ADC _DB8RLADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53F7ADC _DB9RLADC control/status register0x000x00 5400ADC _CR3ADC configuration register 10x000x00 5401ADC_CR2ADC configuration register 30x000x00 5405ADC_DRHADC data register low0xXX0x00 5406ADC_DRHADC Configuration register 10x000x00 5407ADC_DRHADC Configuration register 10x000x00 5408ADC_DRHADC Control/status register0x000x00 5408ADC_DRHADC Configuration register 30x000x00 5407ADC_DRHADC Configuration register 10x000x00                                                                                                                                                                                                                                                                                                          | 0x00 53E5 |         | ADC _DB2RL       | ADC data buffer register 2 low   | 0x00 |

| 0x00 53E8<br>0x00 53E9ADC _DB4RHADC data buffer register 4 high0x000x00 53E4ADC _DB4RLADC data buffer register 4 low0x000x00 53E4ADC _DB5RHADC data buffer register 5 low0x000x00 53E6ADC _DB6RHADC data buffer register 5 low0x000x00 53E7ADC _DB6RHADC data buffer register 6 high0x000x00 53E7ADC _DB7RHADC data buffer register 7 high0x000x00 53F1ADC _DB7RHADC data buffer register 7 low0x000x00 53F2ADC _DB8RHADC data buffer register 7 low0x000x00 53F3ADC _DB8RHADC data buffer register 8 high0x000x00 53F4ADC _DB8RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F7ADC _DB9RHADC data buffer register 9 high0x000x00 5400ADC _DB9RLADC data buffer register 9 high0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRHADC Cata register low0xXX0x00 5406ADC_DRHADC Cata buffer register 10x000x00 5407ADC_DRHADC Cata register low0xXX0x00 5408ADC_DRHADC Configuration register 10x000x00 5408ADC_DRHADC Configuration register 10x000x00 5407ADC_DRHADC Configuration register 10x00 <tr< td=""><td>0x00 53E6</td><td></td><td>ADC _DB3RH</td><td>ADC data buffer register 3 high</td><td>0x00</td></tr<>                                                                                                                                                                                | 0x00 53E6 |         | ADC _DB3RH       | ADC data buffer register 3 high  | 0x00 |

| ADCADCADCADCADCADCADC0x0053E3ADCADCDB5RHADC data buffer register 5 high0x000x0053E3ADCDB5RLADC data buffer register 5 low0x000x0053E0ADCDB6RHADC data buffer register 6 low0x000x0053E1ADCDB6RLADC data buffer register 6 low0x000x0053E2ADCDB7RHADC data buffer register 7 low0x000x0053E7ADCDB7RHADC data buffer register 7 low0x000x0053F3ADCDB8RHADC data buffer register 8 low0x000x0053F3ADCDB8RLADC data buffer register 8 low0x000x0053F4ADCADCDB8RLADC data buffer register 9 low0x000x0053F4ADCADCDB9RHADC data buffer register 9 low0x000x0053F4ADCADCDB9RLADC cata buffer register 9 low0x000x0053F4ADCADCCSRADC control/status register0x000x0053F4ADCADCCR2ADC configuration register 10x000x0053F4ADCADC_CR3ADC configuration register 20x000x005400ADCADC_CR3ADC configuration register 10x000x005403ADC_DRHADC data register high0xXX0x005406ADC_DRLADC control/status register0x00<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 53E7 |         | ADC _DB3RL       | ADC data buffer register 3 low   | 0x00 |

| ADCADC_DBSRHADC data buffer register 5 high0x000x00 53EAADC_DBSRLADC data buffer register 5 low0x000x00 53EBADC_DB6RLADC data buffer register 6 high0x000x00 53EDADC_DB6RLADC data buffer register 6 low0x000x00 53EDADC_DB7RHADC data buffer register 7 high0x000x00 53EFADC_DB7RLADC data buffer register 7 low0x000x00 53F0ADC_DB7RLADC data buffer register 7 low0x000x00 53F1ADC_DB8RHADC data buffer register 8 high0x000x00 53F2ADC_DB8RLADC data buffer register 8 low0x000x00 53F3ADC_DB9RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4ADC_DB9RLADC data buffer register 9 high0x000x00 5400ADC_CR3ADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRLADC configuration register 10x000x00 5406ADC_DRLADC Control/status register0x000x00 5407ADC_DRHADC control/status register high0xXX0x00 5408ADC_TDRHADC control/status register high0xXX0x00 5408ADC_DRLADC control/status register high0xXX0x00 5407ADC_TDRHADC control/status register high0x000x00 5408ADC_TDRHADC control/status register high0x00 <tr< td=""><td>0x00 53E8</td><td></td><td>ADC _DB4RH</td><td>ADC data buffer register 4 high</td><td>0x00</td></tr<>                                                                                                                                                                               | 0x00 53E8 |         | ADC _DB4RH       | ADC data buffer register 4 high  | 0x00 |

| ADC _DB5RHADC data buffer register 5 high0x000x00 53EBADC _DB5RLADC data buffer register 5 low0x000x00 53ECADC _DB6RHADC data buffer register 6 high0x000x00 53EDADC _DB6RLADC data buffer register 6 low0x000x00 53EDADC _DB7RHADC data buffer register 7 high0x000x00 53F1ADC _DB7RHADC data buffer register 7 high0x000x00 53F2ADC _DB8RHADC data buffer register 8 high0x000x00 53F3ADC _DB8RHADC data buffer register 8 high0x000x00 53F4 to<br>0x00 53F4 to<br>0x00 5402ADC _CSRADC control/status register 9 high0x000x00 5402ADC _CR2ADC configuration register 10x000x00 5403ADC _CR3ADC configuration register 30x000x00 5404ADC _DRHADC data puffer register 10x000x00 5406ADC _CR3ADC configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5407ADC _DRHADC configuration register high0xXX0x00 5408ADC _TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC _TDRHADC Schmitt trigger disable register high0x000x00 5408ADC _HTRHADC high threshold re                                                                                                                                                                                                                                                                       | 0x00 53E9 |         | ADC _DB4RL       | ADC data buffer register 4 low   | 0x00 |

| 0x00 53ECADC _DB6RHADC data buffer register 6 high0x000x00 53EDADC _DB6RLADC data buffer register 6 low0x000x00 53EEADC _DB7RHADC data buffer register 7 high0x000x00 53F6ADC _DB7RLADC data buffer register 7 low0x000x00 53F1ADC _DB8RHADC data buffer register 8 high0x000x00 53F2ADC _DB8RLADC data buffer register 8 low0x000x00 53F3ADC _DB9RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4 to<br>0x00 53F4ADC _CSRADC control/status register 9 low0x000x00 53F4 to<br>0x00 53F4ADC _CCR1ADC control/status register 10x000x00 5401ADC _CR2ADC configuration register 10x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5406ADC _DRHADC Control/status register 10x000x00 5407ADC _DRHADC Configuration register 10x000x00 5408ADC _DRHADC Control/status register high0xXX0x00 5408ADC _DRHADC Configuration register 10x000x00 5409ADC _DRHADC Control/status register high0x000x00 5408ADC _DRHADC Configuration register 10x000x00 5406ADC _DRHADC Control/status register high0x000x00 5408ADC _DRHADC Control/status register high0x000x00 5409ADC _DRHADC Control/st                                                                                                                                                                                                                                                                                | 0x00 53EA | ADC     | ADC _DB5RH       | ADC data buffer register 5 high  | 0x00 |

| Ox00 53EDADC_DB6RLADC data buffer register 6 lowOx000x00 53EEADC_DB7RHADC data buffer register 7 high0x000x00 53FFADC_DB7RLADC data buffer register 7 low0x000x00 53F0ADC_DB8RHADC data buffer register 7 low0x000x00 53F1ADC_DB8RLADC data buffer register 8 high0x000x00 53F2ADC_DB8RLADC data buffer register 9 high0x000x00 53F3ADC_DB9RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC_CR1ADC configuration register 10x000x00 5401ADC_CR2ADC configuration register 20x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRHADC configuration register 10x000x00 5406ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register low0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 53EB |         | ADC _DB5RL       | ADC data buffer register 5 low   | 0x00 |

| Ox00 53EEADC _DB7RHADC data buffer register 7 highOx000x00 53FFADC _DB7RLADC data buffer register 7 high0x000x00 53F0ADC _DB8RHADC data buffer register 8 high0x000x00 53F1ADC _DB8RLADC data buffer register 8 low0x000x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CR1ADC configuration register 10x000x00 5401ADC _CR2ADC configuration register 20x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5405ADC _DRLADC Configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5406ADC _TDRHADC Schmitt trigger disable register<br>high0x000x00 5408ADC _TDRHADC Schmitt trigger disable register<br>low0x000x00 5409ADC _HTRHADC high threshold register high0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 53EC |         | ADC _DB6RH       | ADC data buffer register 6 high  | 0x00 |

| Ox00 53EFADC _DB7RLADC data buffer register 7 lowOx000x00 53F0ADC _DB8RHADC data buffer register 8 high0x000x00 53F1ADC _DB8RLADC data buffer register 8 high0x000x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC _CR1ADC configuration register 10x000x00 5402ADC _CR2ADC configuration register 20x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5406ADC _DRLADC Cchmitt trigger disable register0x000x00 5407ADC _TDRHADC Schmitt trigger disable register0x000x00 5408ADC _HTRHADC high threshold register high0xFF0x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 53ED |         | ADC _DB6RL       | ADC data buffer register 6 low   | 0x00 |

| ADC _DB8RHADC data buffer register 8 high0x000x00 53F1ADC _DB8RLADC data buffer register 8 high0x000x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFADC _CSRADC control/status register0x000x00 5400ADC _CR1ADC configuration register 10x000x00 5401ADC _CR2ADC configuration register 20x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRLADC data register high0xXX0x00 5406ADC _TDRHADC Schmitt trigger disable register0x000x00 5407ADC _TDRHADC Schmitt trigger disable register0x000x00 5408ADC _TTRHADC Schmitt trigger disable register0x000x00 5409ADC _HTRHADC high threshold register high0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 53EE |         | ADC _DB7RH       | ADC data buffer register 7 high  | 0x00 |

| ADC _DB8RLADC data buffer register 8 low0x000x00 53F1ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5402ADC_CR2ADC configuration register 20x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRLADC data register high0xXX0x00 5405ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRLADC Schmitt trigger disable register<br>high0x000x00 5408ADC _HTRHADC high threshold register high0x000x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00 53EF |         | ADC _DB7RL       | ADC data buffer register 7 low   | 0x00 |

| 0x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC _CR1ADC configuration register 10x000x00 5402ADC _CR2ADC configuration register 20x000x00 5403ADC _CR3ADC configuration register 30x000x00 5404ADC _DRHADC data register low0xXX0x00 5405ADC _DRLADC data register low0xXX0x00 5406ADC _TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC _TDRLADC Schmitt trigger disable register<br>low0x000x00 5408ADC _HTRHADC high threshold register high0xFF0x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00 53F0 |         | ADC _DB8RH       | ADC data buffer register 8 high  | 0x00 |

| 0x00 53F3ADC _DB9RLADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC _CR1ADC configuration register 10x000x00 5402ADC _CR2ADC configuration register 20x000x00 5403ADC _CR3ADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5406ADC _DRLADC data register low0xXX0x00 5407ADC _TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC _HTRLADC high threshold register high0x0FF0x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x00 53F1 |         | ADC _DB8RL       | ADC data buffer register 8 low   | 0x00 |

| 0x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x00 5400ADC_CSRADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5402ADC_CR2ADC configuration register 20x000x00 5403ADC_CR3ADC configuration register 30x000x00 5404ADC_DRHADC data register high0xXX0x00 5405ADC_DRLADC data register low0xXX0x00 5406ADC_TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register low0x070x00 5409ADC_HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 53F2 |         | ADC _DB9RH       | ADC data buffer register 9 high  | 0x00 |

| Ox00 53FF         ADC_CSR         ADC control/status register         Ox00           0x00 5401         ADC_CR1         ADC configuration register 1         0x00           0x00 5402         ADC_CR2         ADC configuration register 2         0x00           0x00 5403         ADC_DR1         ADC configuration register 3         0x00           0x00 5404         ADC_DRH         ADC data register high         0xXX           0x00 5405         ADC_DRL         ADC data register low         0x00           0x00 5406         ADC_TDRH         ADC Schmitt trigger disable register low         0x00           0x00 5407         ADC_TDRL         ADC Schmitt trigger disable register low         0x00           0x00 5408         ADC_HTRH         ADC high threshold register high         0xFF           0x00 5409         ADC_HTRL         ADC high threshold register low         0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x00 53F3 |         | ADC _DB9RL       | ADC data buffer register 9 low   | 0x00 |

| 0x00 5401ADC_CR1ADC configuration register 10x000x00 5402ADC_CR2ADC configuration register 20x000x00 5403ADC_CR3ADC configuration register 30x000x00 5404ADC_DRHADC data register high0xXX0x00 5405ADC_DRLADC data register low0xXX0x00 5406ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRLADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register high0xFF0x00 5409ADC_HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |         | Re               | eserved area (12 bytes)          |      |

| 0x00 5402       ADC_CR2       ADC configuration register 2       0x00         0x00 5403       ADC_CR3       ADC configuration register 3       0x00         0x00 5404       ADC_DRH       ADC data register high       0xXX         0x00 5405       ADC_DRL       ADC data register low       0xXX         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register low       0x00         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_HTRH       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 5400 |         | ADC _CSR         | ADC control/status register      | 0x00 |

| 0x00 5403ADC_CR3ADC configuration register 30x000x00 5404ADC_DRHADC data register high0xXX0x00 5405ADC_DRLADC data register low0xXX0x00 5406ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRLADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register low0xFF0x00 5409ADC_HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00 5401 |         | ADC_CR1          | ADC configuration register 1     | 0x00 |

| 0x00 5404       ADC_DRH       ADC data register high       0xXX         0x00 5405       ADC_DRL       ADC data register low       0xXX         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register high       0xXX         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5409       ADC_HTRH       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 5402 |         | ADC_CR2          | ADC configuration register 2     | 0x00 |

| 0x00 5405       ADC_DRL       ADC data register low       0xXX         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register high       0x00         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_HTRH       ADC high threshold register high       0xFF         0x00 5409       ADC_HTRL       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 5403 |         | ADC_CR3          | ADC configuration register 3     | 0x00 |

| ADC       ADC       ADC_TDRH       ADC Schmitt trigger disable register high       0x00         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register low       0x00         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_HTRH       ADC high threshold register high       0xFF         0x00 5409       ADC_HTRL       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 5404 |         | ADC_DRH          | ADC data register high           | 0xXX |

| 0x00 5406     ADC_TDRH     ADC Schmitt trigger disable register high     0x00       0x00 5407     ADC_TDRL     ADC Schmitt trigger disable register low     0x00       0x00 5408     ADC_HTRH     ADC high threshold register low     0x03       0x00 5409     ADC_HTRL     ADC high threshold register low     0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00 5405 |         | ADC_DRL          | ADC data register low            | 0xXX |

| 0x00 5407     ADC_TDRL     Iow     0x00       0x00 5408     ADC_HTRH     ADC high threshold register high     0xFF       0x00 5409     ADC_HTRL     ADC high threshold register low     0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00 5406 | ADC     | ADC_TDRH         |                                  | 0x00 |

| 0x00 5409 ADC_HTRL ADC high threshold register low 0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x00 5407 |         | ADC_TDRL         |                                  | 0x00 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x00 5408 |         | ADC _HTRH        | ADC high threshold register high | 0xFF |

| 0x00 540A ADC _LTRH ADC low threshold register high 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00 5409 |         | ADC_HTRL         | ADC high threshold register low  | 0x03 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x00 540A |         | ADC _LTRH        | ADC low threshold register high  | 0x00 |

| Table 11. General hardware register map (continued) |

|-----------------------------------------------------|

|-----------------------------------------------------|

# 8 Interrupt table

| Table 14. STM8A Interrupt table |                         |                                                  |                             |                     |                   |  |

|---------------------------------|-------------------------|--------------------------------------------------|-----------------------------|---------------------|-------------------|--|

| Priority                        | Source<br>block         | Description                                      | Interrupt vector<br>address | Wakeup<br>from Halt | Comments          |  |

| -                               | Reset                   | Reset                                            | 0x00 8000                   | Yes                 | User RESET vector |  |

| -                               | TRAP                    | SW interrupt                                     | 0x00 8004                   | -                   | -                 |  |

| 0                               | TLI                     | External top level interrupt                     | 0x00 8008                   | -                   | -                 |  |

| 1                               | AWU                     | Auto-wakeup from Halt                            | 0x00 800C                   | Yes                 | -                 |  |

| 2                               | Clock<br>controller     | Main clock controller                            | 0x00 8010                   | -                   | -                 |  |

| 3                               | MISC                    | Ext interrupt E0                                 | 0x00 8014                   | Yes                 | Port A interrupts |  |

| 4                               | MISC                    | Ext interrupt E1                                 | 0x00 8018                   | Yes                 | Port B interrupts |  |

| 5                               | MISC                    | Ext interrupt E2                                 | 0x00 801C                   | Yes                 | Port C interrupts |  |

| 6                               | MISC                    | Ext interrupt E3                                 | 0x00 8020                   | Yes                 | Port D interrupts |  |

| 7                               | MISC                    | Ext interrupt E4                                 | 0x00 8024                   | Yes                 | Port E interrupts |  |

| 8                               | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 9                               | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 10                              | SPI                     | End of transfer                                  | 0x00 8030                   | Yes                 | -                 |  |

| 11                              | Timer 1                 | Update/overflow/<br>trigger/break                | 0x00 8034                   | -                   | -                 |  |

| 12                              | Timer 1                 | Capture/compare                                  | 0x00 8038                   | -                   | -                 |  |

| 13                              | Timer 2                 | Update/overflow                                  | 0x00 803C                   | -                   | -                 |  |

| 14                              | Timer 2                 | Capture/compare                                  | 0x00 8040                   | -                   | -                 |  |

| 15                              | Timer 3                 | Update/overflow                                  | 0x00 8044                   | -                   | -                 |  |

| 16                              | Timer 3                 | Capture/compare                                  | 0x00 8048                   | -                   | -                 |  |

| 17                              | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 18                              | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 19                              | l <sup>2</sup> C        | I <sup>2</sup> C interrupts                      | 0x00 8054                   | Yes                 | -                 |  |

| 20                              | LINUART                 | Tx complete/error                                | 0x00 8058                   | -                   | -                 |  |

| 21                              | LINUART                 | Receive data full reg.                           | 0x00 805C                   | -                   | -                 |  |

| 22                              | ADC                     | End of conversion                                | 0x00 8060                   | -                   | -                 |  |

| 23                              | Timer 4                 | Update/overflow                                  | 0x00 8064                   | -                   | -                 |  |

| 24                              | EEPROM                  | End of Programming/<br>Write in not allowed area | 0x00 8068                   | -                   | -                 |  |

#### Table 14. STM8A interrupt table

1. All reserved and unused interrupts must be initialized with 'IRET' for robust programming.

| Table | 16. | Option | bvte | description |  |

|-------|-----|--------|------|-------------|--|

| Table |     | option | ~,   | 400011011   |  |

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|