#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | STM8A                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | -                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6246tdsssx |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |       | 10.3.7                | Reset pin characteristics                  |

|----|-------|-----------------------|--------------------------------------------|

|    |       | 10.3.8                | TIM 1, 2, 3, and 4 timer specifications    |

|    |       | 10.3.9                | SPI serial peripheral interface69          |

|    |       | 10.3.10               | I <sup>2</sup> C interface characteristics |

|    |       | 10.3.11               | 10-bit ADC characteristics                 |

|    |       | 10.3.12               | EMC characteristics                        |

| 11 | Pack  | age info              | ormation                                   |

|    | 11.1  | VFQFP                 | N32 package information 78                 |

|    | 11.2  | LQFP4                 | 8 package information                      |

|    | 11.3  | LQFP3                 | 2 package information                      |

|    | 11.4  | Therma                | Il characteristics                         |

|    |       | 11.4.1                | Reference document88                       |

|    |       | 11.4.2                | Selecting the product temperature range    |

| 12 | Orde  | ring info             | ormation                                   |

| 13 | STM   | 8 develo              | pment tools                                |

|    | 13.1  | Emulati               | on and in-circuit debugging tools          |

|    |       | 13.1.1                | STice key features                         |

|    | 13.2  | Softwar               | re tools                                   |

|    |       | 13.2.1                | STM8 toolset                               |

|    |       | 13.2.2                | C and assembly toolchains92                |

|    | 13.3  | Prograr               | nming tools                                |

| 14 | Revis | sion his <sup>.</sup> | tory                                       |

|    |       |                       | -                                          |

## 2 Description

The STM8AF6246, STM8AF6248, STM8AF6266 and STM8AF6268 automotive 8-bit microcontrollers offer from 16 to 32 Kbyte of Flash program memory and integrated true data EEPROM. They are referred to as medium density STM8A devices in STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

All devices of the STM8A product line provide the following benefits: reduced system cost, performance and robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, watchdog, and brown-out reset.

Device performance is ensured by a clock frequency of up to 16 MHz CPU and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8A family thanks to their advanced core which is made in a state-of-the art technology for automotive applications with 3.3 V to 5 V operating supply.

All STM8A and ST7 microcontrollers are supported by the same tools including STVD/STVP development environment, the STice emulator and a low-cost, third party incircuit debugging tool.

## 5 **Product overview**

This section describes the family features that are implemented in the products covered by this datasheet.

For more detailed information on each feature please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

## 5.1 STM8A central processing unit (CPU)

The 8-bit STM8A core is a modern CISC core and has been designed for code efficiency and performance. It contains 21 internal registers (six directly addressable in each execution context), 20 addressing modes including indexed indirect and relative addressing and 80 instructions.

### 5.1.1 Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus with single cycle fetching for most instructions

- X and Y 16-bit index registers, enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter with 16-Mbyte linear memory space

- 16-bit stack pointer with access to a 64 Kbyte stack

- 8-bit condition code register with seven condition flags for the result of the last instruction.

### 5.1.2 Addressing

- 20 addressing modes

- Indexed indirect addressing mode for look-up tables located anywhere in the address space

- Stack pointer relative addressing mode for efficient implementation of local variables and parameter passing

#### 5.1.3 Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

## 5.8 Analog-to-digital converter (ADC)

The STM8A products described in this datasheet contain a 10-bit successive approximation ADC with up to 16 multiplexed input channels, depending on the package.

The ADC name differs between the datasheet and STM8S series and STM8AF series 8-bit microcontrollers reference manual (see *Table 5*).

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| ADC                          | ADC1                                            |

#### **ADC** features

- 10-bit resolution

- Single and continuous conversion modes

- Programmable prescaler: f<sub>MASTER</sub> divided by 2 to 18

- Conversion trigger on timer events and external events

- Interrupt generation at end of conversion

- Selectable alignment of 10-bit data in 2 x 8 bit result register

- Shadow registers for data consistency

- ADC input range:  $V_{SSA} \le V_{IN} \le V_{DDA}$

- Analog watchdog

- Schmitt-trigger on analog inputs can be disabled to reduce power consumption

- Scan mode (single and continuous)

- Dedicated result register for each conversion channel

- Buffer mode for continuous conversion

Note: An additional AIN12 analog input is not selectable in ADC scan mode or with analog watchdog. Values converted from AIN12 are stored only into the ADC\_DRH/ADC\_DRL registers.

## 5.9 Communication interfaces

The following sections give a brief overview of the communication peripheral. Some peripheral names differ between the datasheet and STM8S series and STM8AF series 8-bit microcontrollers reference manual (see *Table 6*).

| Table 6. Communication | peripheral n | naming correspondence |

|------------------------|--------------|-----------------------|

|------------------------|--------------|-----------------------|

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| LINUART                      | UART2                                           |

| Table 10. 10 port hardware register map (continued) |        |                |                                   |                     |

|-----------------------------------------------------|--------|----------------|-----------------------------------|---------------------|

| Address                                             | Block  | Register label | Register name                     | Reset<br>status     |

| 0x00 5014                                           |        | PE_ODR         | Port E data output latch register | 0x00                |

| 0x00 5015                                           |        | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016                                           | Port E | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017                                           |        | PE_CR1         | Port E control register 1         | 0x00                |

| 0x00 5018                                           |        | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019                                           |        | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A                                           |        | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B                                           | Port F | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C                                           |        | PF_CR1         | Port F control register 1         | 0x00                |

| 0x00 501D                                           |        | PF_CR2         | Port F control register 2         | 0x00                |

| 0x00 501E                                           |        | PG_ODR         | Port G data output latch register | 0x00                |

| 0x00 501F                                           |        | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5020                                           | Port G | PG_DDR         | Port G data direction register    | 0x00                |

| 0x00 5021                                           |        | PG_CR1         | Port G control register 1         | 0x00                |

| 0x00 5022                                           |        | PG_CR2         | Port G control register 2         | 0x00                |

| Table 10. I/O port hardware register map (continued) |

|------------------------------------------------------|

|------------------------------------------------------|

1. Depends on the external circuitry.

| Table 11. General naturale register map |                          |                |                                                  |                 |

|-----------------------------------------|--------------------------|----------------|--------------------------------------------------|-----------------|

| Address                                 | Block                    | Register label | Register name                                    | Reset<br>status |

| 0x00 505A                               |                          | FLASH_CR1      | Flash control register 1                         | 0x00            |

| 0x00 505B                               |                          | FLASH_CR2      | Flash control register 2                         | 0x00            |

| 0x00 505C                               |                          | FLASH_NCR2     | Flash complementary control register 2           | 0xFF            |

| 0x00 505D                               | Flash                    | FLASH_FPR      | Flash protection register                        | 0x00            |

| 0x00 505E                               |                          | FLASH_NFPR     | Flash complementary protection register          | 0xFF            |

| 0x00 505F                               |                          | FLASH_IAPSR    | Flash in-application programming status register | 0x40            |

| 0x00 5060 to<br>0x00 5061               | Reserved area (2 bytes)  |                |                                                  |                 |

| 0x00 5062                               | Flash                    | FLASH_PUKR     | Flash Program memory unprotection register       | 0x00            |

| 0x00 5063                               | Reserved area (1 byte)   |                |                                                  |                 |

| 0x00 5064                               | Flash                    | FLASH_DUKR     | Data EEPROM unprotection register                | 0x00            |

| 0x00 5065 to<br>0x00 509F               | Reserved area (59 bytes) |                |                                                  |                 |

#### Table 11. General hardware register map

DocID14952 Rev 11

| Address                   | Block                   | Register label | Register name                   | Reset<br>status |  |

|---------------------------|-------------------------|----------------|---------------------------------|-----------------|--|

| 0x00 50F3                 | BEEP                    | BEEP_CSR       | BEEP control/status register    | 0x1F            |  |

| 0x00 50F4 to<br>0x00 50FF |                         | Re             | eserved area (12 bytes)         |                 |  |

| 0x00 5200                 |                         | SPI_CR1        | SPI control register 1          | 0x00            |  |

| 0x00 5201                 |                         | SPI_CR2        | SPI control register 2          | 0x00            |  |

| 0x00 5202                 |                         | SPI_ICR        | SPI interrupt control register  | 0x00            |  |

| 0x00 5203                 | SPI                     | SPI_SR         | SPI status register             | 0x02            |  |

| 0x00 5204                 | 581                     | SPI_DR         | SPI data register               | 0x00            |  |

| 0x00 5205                 |                         | SPI_CRCPR      | SPI CRC polynomial register     | 0x07            |  |

| 0x00 5206                 |                         | SPI_RXCRCR     | SPI Rx CRC register             | 0xFF            |  |

| 0x00 5207                 |                         | SPI_TXCRCR     | SPI Tx CRC register             | 0xFF            |  |

| 0x00 5208 to<br>0x00 520F | Reserved area (8 bytes) |                |                                 |                 |  |

| 0x00 5210                 |                         | I2C_CR1        | I2C control register 1          | 0x00            |  |

| 0x00 5211                 |                         | I2C_CR2        | I2C control register 2          | 0x00            |  |

| 0x00 5212                 |                         | I2C_FREQR      | I2C frequency register          | 0x00            |  |

| 0x00 5213                 |                         | I2C_OARL       | I2C own address register low    | 0x00            |  |

| 0x00 5214                 |                         | I2C_OARH       | I2C own address register high   | 0x00            |  |

| 0x00 5215                 |                         |                | Reserved area (1 byte)          |                 |  |

| 0x00 5216                 | I2C                     | I2C_DR         | I2C data register               | 0x00            |  |

| 0x00 5217                 | 120                     | I2C_SR1        | I2C status register 1           | 0x00            |  |

| 0x00 5218                 |                         | I2C_SR2        | I2C status register 2           | 0x00            |  |

| 0x00 5219                 |                         | I2C_SR3        | I2C status register 3           | 0x00            |  |

| 0x00 521A                 |                         | I2C_ITR        | I2C interrupt control register  | 0x00            |  |

| 0x00 521B                 |                         | I2C_CCRL       | I2C clock control register low  | 0x00            |  |

| 0x00 521C                 |                         | I2C_CCRH       | I2C clock control register high | 0x00            |  |

| 0x00 521D                 |                         | I2C_TRISER     | I2C TRISE register              | 0x02            |  |

| 0x00 521E to<br>0x00 523F |                         | Re             | eserved area (24 bytes)         |                 |  |

#### Table 11. General hardware register map (continued)

| Table 11. General hardware register map (continued) |       |                |                                           |                 |  |

|-----------------------------------------------------|-------|----------------|-------------------------------------------|-----------------|--|

| Address                                             | Block | Register label | Register name                             | Reset<br>status |  |

| 0x00 5265                                           |       | TIM1_CCR1H     | TIM1 capture/compare register 1 high      | 0x00            |  |

| 0x00 5266                                           |       | TIM1_CCR1L     | TIM1 capture/compare register 1 low       | 0x00            |  |

| 0x00 5267                                           |       | TIM1_CCR2H     | TIM1 capture/compare register 2 high      | 0x00            |  |

| 0x00 5268                                           |       | TIM1_CCR2L     | TIM1 capture/compare register 2 low       | 0x00            |  |

| 0x00 5269                                           |       | TIM1_CCR3H     | TIM1 capture/compare register 3 high      | 0x00            |  |

| 0x00 526A                                           | TIM1  | TIM1_CCR3L     | TIM1 capture/compare register 3 low       | 0x00            |  |

| 0x00 526B                                           |       | TIM1_CCR4H     | TIM1 capture/compare register 4 high      | 0x00            |  |

| 0x00 526C                                           |       | TIM1_CCR4L     | TIM1 capture/compare register 4 low       | 0x00            |  |

| 0x00 526D                                           |       | TIM1_BKR       | TIM1 break register                       | 0x00            |  |

| 0x00 526E                                           |       | TIM1_DTR       | TIM1 dead-time register                   | 0x00            |  |

| 0x00 526F                                           |       | TIM1_OISR      | TIM1 output idle state register           | 0x00            |  |

| 0x00 5270 to<br>0x00 52FF                           |       | Re             | eserved area (147 bytes)                  |                 |  |

| 0x00 5300                                           |       | TIM2_CR1       | TIM2 control register 1                   | 0x00            |  |

| 0x00 5301                                           |       | TIM2_IER       | TIM2 interrupt enable register            | 0x00            |  |

| 0x00 5302                                           |       | TIM2_SR1       | TIM2 status register 1                    | 0x00            |  |

| 0x00 5303                                           |       | TIM2_SR2       | TIM2 status register 2                    | 0x00            |  |

| 0x00 5304                                           |       | TIM2_EGR       | TIM2 event generation register            | 0x00            |  |

| 0x00 5305                                           |       | TIM2_CCMR1     | TIM2 capture/compare mode register 1      | 0x00            |  |

| 0x00 5306                                           |       | TIM2_CCMR2     | TIM2 capture/compare mode register 2      | 0x00            |  |

| 0x00 5307                                           |       | TIM2_CCMR3     | TIM2 capture/compare mode register 3      | 0x00            |  |

| 0x00 5308                                           |       | TIM2_CCER1     | TIM2 capture/compare enable register<br>1 | 0x00            |  |

| 0x00 5309                                           | TIM2  | TIM2_CCER2     | TIM2 capture/compare enable register 2    | 0x00            |  |

| 0x00 530A                                           |       | TIM2_CNTRH     | TIM2 counter high                         | 0x00            |  |

| 0x00 530B                                           |       | TIM2_CNTRL     | TIM2 counter low                          | 0x00            |  |

| 00 530C0x                                           |       | TIM2_PSCR      | TIM2 prescaler register                   | 0x00            |  |

| 0x00 530D                                           |       | TIM2_ARRH      | TIM2 auto-reload register high            | 0xFF            |  |

| 0x00 530E                                           |       | TIM2_ARRL      | TIM2 auto-reload register low             | 0xFF            |  |

| 0x00 530F                                           |       | TIM2_CCR1H     | TIM2 capture/compare register 1 high      | 0x00            |  |

| 0x00 5310                                           |       | TIM2_CCR1L     | TIM2 capture/compare register 1 low       | 0x00            |  |

| 0x00 5311                                           |       | TIM2_CCR2H     | TIM2 capture/compare reg. 2 high          | 0x00            |  |

| 0x00 5312                                           |       | TIM2_CCR2L     | TIM2 capture/compare register 2 low       | 0x00            |  |

| 0x00 5313                                           |       | TIM2_CCR3H     | TIM2 capture/compare register 3 high      | 0x00            |  |

# 8 Interrupt table

| Table 14. STM8A Interrupt table |                         |                                                  |                             |                     |                   |  |  |

|---------------------------------|-------------------------|--------------------------------------------------|-----------------------------|---------------------|-------------------|--|--|

| Priority                        | Source<br>block         | Description                                      | Interrupt vector<br>address | Wakeup<br>from Halt | Comments          |  |  |

| -                               | Reset                   | Reset                                            | 0x00 8000                   | Yes                 | User RESET vector |  |  |

| -                               | TRAP                    | SW interrupt                                     | 0x00 8004                   | -                   | -                 |  |  |

| 0                               | TLI                     | External top level interrupt                     | 0x00 8008                   | -                   | -                 |  |  |

| 1                               | AWU                     | Auto-wakeup from Halt                            | 0x00 800C                   | Yes                 | -                 |  |  |

| 2                               | Clock<br>controller     | Main clock controller                            | 0x00 8010                   | -                   | -                 |  |  |

| 3                               | MISC                    | Ext interrupt E0                                 | 0x00 8014                   | Yes                 | Port A interrupts |  |  |

| 4                               | MISC                    | Ext interrupt E1                                 | 0x00 8018                   | Yes                 | Port B interrupts |  |  |

| 5                               | MISC                    | Ext interrupt E2                                 | 0x00 801C                   | Yes                 | Port C interrupts |  |  |

| 6                               | MISC                    | Ext interrupt E3                                 | 0x00 8020                   | Yes                 | Port D interrupts |  |  |

| 7                               | MISC                    | Ext interrupt E4                                 | 0x00 8024                   | Yes                 | Port E interrupts |  |  |

| 8                               | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |  |

| 9                               | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |  |

| 10                              | SPI                     | End of transfer                                  | 0x00 8030                   | Yes                 | -                 |  |  |

| 11                              | Timer 1                 | Update/overflow/<br>trigger/break                | 0x00 8034                   | -                   | -                 |  |  |

| 12                              | Timer 1                 | Capture/compare                                  | 0x00 8038                   | -                   | -                 |  |  |

| 13                              | Timer 2                 | Update/overflow                                  | 0x00 803C                   | -                   | -                 |  |  |

| 14                              | Timer 2                 | Capture/compare                                  | 0x00 8040                   | -                   | -                 |  |  |

| 15                              | Timer 3                 | Update/overflow                                  | 0x00 8044                   | -                   | -                 |  |  |

| 16                              | Timer 3                 | Capture/compare                                  | 0x00 8048                   | -                   | -                 |  |  |

| 17                              | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |  |

| 18                              | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |  |

| 19                              | l <sup>2</sup> C        | I <sup>2</sup> C interrupts                      | 0x00 8054                   | Yes                 | -                 |  |  |

| 20                              | LINUART                 | Tx complete/error                                | 0x00 8058                   | -                   | -                 |  |  |

| 21                              | LINUART                 | Receive data full reg.                           | 0x00 805C                   | -                   | -                 |  |  |

| 22                              | ADC                     | End of conversion                                | 0x00 8060                   | -                   | -                 |  |  |

| 23                              | Timer 4                 | Update/overflow                                  | 0x00 8064                   | -                   | -                 |  |  |

| 24                              | EEPROM                  | End of Programming/<br>Write in not allowed area | 0x00 8068                   | -                   | -                 |  |  |

#### Table 14. STM8A interrupt table

1. All reserved and unused interrupts must be initialized with 'IRET' for robust programming.

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT12           | TMU_KEY 5 [7:0]: Temporary unprotection key 4<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                           |

| OPT13           | TMU_KEY 6 [7:0]: Temporary unprotection key 5           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |

| OPT14           | TMU_KEY 7 [7:0]: Temporary unprotection key 6           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |

| OPT15           | TMU_KEY 8 [7:0]: Temporary unprotection key 7           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |

| OPT16           | TMU_MAXATT [7:0]: TMU access failure counter         TMU_MAXATT can be initialized with the desired value only if TMU is disabled (TMU[3:0]=0101 in OPT6 option byte).         When TMU is enabled, any attempt to temporary remove the readout protection by using wrong key values increments the counter.         When the option byte value reaches 0x08, the Flash memory and data EEPROM are erased. |

| OPT17           | BL [7:0]: Bootloader enable<br>If this option byte is set to 0x55 (complementary value 0xAA) the<br>bootloader program is activated also in case of a programmed code<br>memory<br>(for more details, see the bootloader user manual, UM0560).                                                                                                                                                             |

#### Table 16. Option byte description (continued)

| Symbol                               | Ratings                                                                   | Max. | Unit |

|--------------------------------------|---------------------------------------------------------------------------|------|------|

| I <sub>VDDIO</sub>                   | Total current into $V_{DDIO}$ power lines (source) <sup>(1)(2)(3)</sup>   | 100  |      |

| I <sub>VSSIO</sub>                   | Total current out of $V_{SS IO}$ ground lines (sink) <sup>(1)(2)(3)</sup> | 100  |      |

| 1.                                   | Output current sunk by any I/O and control pin                            | 20   | mA   |

| IIO                                  | Output current source by any I/Os and control pin                         | -20  | IIIA |

| I <sub>INJ(PIN)</sub> <sup>(4)</sup> | Injected current on any pin                                               | ±10  |      |

| I <sub>INJ(TOT)</sub>                | Sum of injected currents                                                  | 50   |      |

#### Table 18. Current characteristics

1. All power (V\_{DD}, V\_{DDIO}, V\_{DDA}) and ground (V\_{SS}, V\_{SSIO}, V\_{SSA}) pins must always be connected to the external supply.

- 2. The total limit applies to the sum of operation and injected currents.

- 3.  $V_{\text{DDIO}}$  includes the sum of the positive injection currents.  $V_{\text{SSIO}}$  includes the sum of the negative injection currents.

- 4. This condition is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current allowed and the corresponding V<sub>IN</sub> maximum must always be respected.

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| TJ               | Maximum junction temperature | 160        | 0    |

#### Table 20. Operating lifetime<sup>(1)</sup>

| Symbol | Ratings                       | Value         | Unit    |

|--------|-------------------------------|---------------|---------|

| OLF    | Conforming to AEC-Q100 rev G  | -40 to 125 °C | Grade 1 |

|        | Conforming to AEC-Q 100 TeV G | -40 to 150 °C | Grade 0 |

1. For detailed mission profile analysis, please contact the nearest local ST Sales Office.

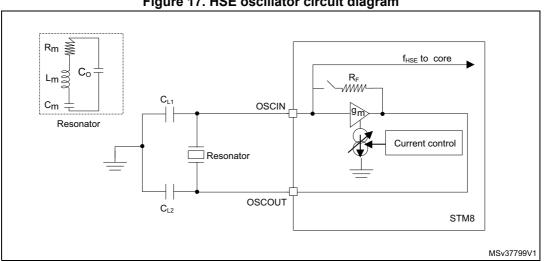

Figure 17. HSE oscillator circuit diagram

### HSE oscillator critical g<sub>m</sub> formula

The crystal characteristics have to be checked with the following formula:

g<sub>m</sub> » g<sub>mcrit</sub>

where  $g_{mcrit}$  can be calculated with the crystal parameters as follows:

$$g_{mcrit} = (2 \times \Pi \times {}^{f}HSE)^{2} \times R_{m}(2Co + C)^{2}$$

R<sub>m</sub>: Notional resistance (see crystal specification)

L<sub>m</sub>: Notional inductance (see crystal specification)

C<sub>m</sub>: Notional capacitance (see crystal specification)

Co: Shunt capacitance (see crystal specification)

$C_{1,1} = C_{1,2} = C$ : Grounded external capacitance

#### 10.3.4 Internal clock sources and timing characteristics

Subject to general operating conditions for V<sub>DD</sub> and T<sub>A</sub>.

#### High speed internal RC oscillator (HSI)

| Table 30. HSI oscillator characteristics | Table 30. | HSI | oscillator | characteristics |

|------------------------------------------|-----------|-----|------------|-----------------|

|------------------------------------------|-----------|-----|------------|-----------------|

| Symbol           | Parameter | Conditions | Min | Тур | Мах | Unit |

|------------------|-----------|------------|-----|-----|-----|------|

| f <sub>HSI</sub> | Frequency | -          | -   | 16  | -   | MHz  |

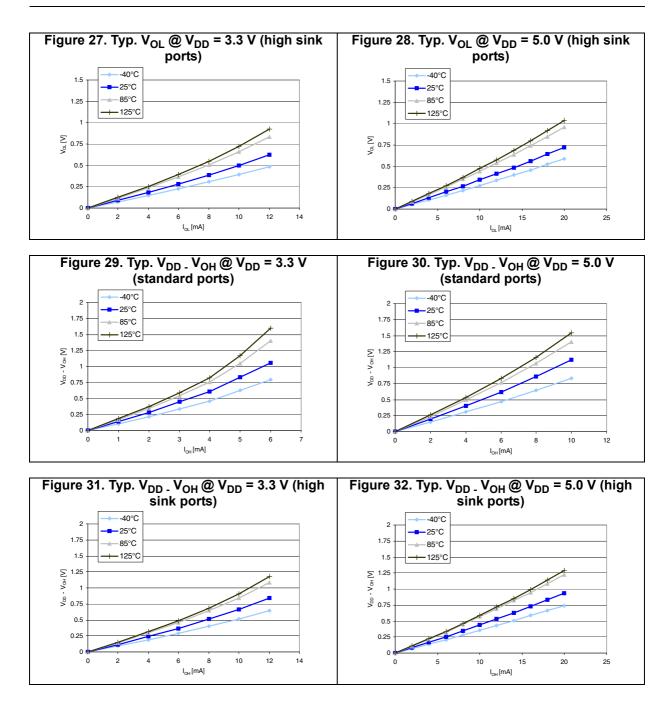

## 10.3.6 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage, using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                          | Parameter                                                         | Conditions                                                                              | Min                     | Тур                      | Мах                     | Unit |

|---------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------------------|------|

| $V_{IL}$                        | Input low level voltage                                           |                                                                                         | -0.3 V                  | -                        | 0.3 x V <sub>DD</sub>   |      |

| $V_{\text{IH}}$                 | Input high level voltage                                          | _                                                                                       | 0.7 x V <sub>DD</sub>   | -                        | V <sub>DD</sub> + 0.3 V |      |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                                         |                                                                                         | -                       | 0.1 x<br>V <sub>DD</sub> | -                       |      |

| M                               | Output high level voltage                                         | Standard I/0, V <sub>DD</sub> = 5 V,<br>I = 3 mA                                        | V <sub>DD</sub> - 0.5 V | -                        | -                       |      |

| V <sub>OH</sub>                 | output high level voltage                                         | Standard I/0, V <sub>DD</sub> = 3 V,<br>I = 1.5 mA                                      | V <sub>DD</sub> - 0.4 V | -                        | -                       | V    |

|                                 |                                                                   | High sink and true open<br>drain I/0, V <sub>DD</sub> = 5 V<br>I = 8 mA                 | -                       | -                        | 0.5                     |      |

| $V_{OL}$                        | Output low level voltage                                          | Standard I/0, V <sub>DD</sub> = 5 V<br>I = 3 mA                                         | -                       | -                        | 0.6                     |      |

|                                 |                                                                   | Standard I/0, V <sub>DD</sub> = 3 V<br>I = 1.5 mA                                       | -                       | -                        | 0.4                     |      |

| R <sub>pu</sub>                 | Pull-up resistor                                                  | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$                                                     | 35                      | 50                       | 65                      | kΩ   |

|                                 | Rise and fall time<br>(10% - 90%)                                 | Fast I/Os<br>Load = 50 pF                                                               | -                       | -                        | 35 <sup>(2)</sup>       | ns   |

|                                 |                                                                   | Standard and high sink I/Os<br>Load = 50 pF                                             | -                       | -                        | 125 <sup>(2)</sup>      |      |

| t <sub>R</sub> , t <sub>F</sub> |                                                                   | Fast I/Os<br>Load = 20 pF                                                               | -                       | -                        | 20 <sup>(2)</sup>       |      |

|                                 |                                                                   | Standard and high sink I/Os<br>Load = 20 pF                                             | -                       | -                        | 50 <sup>(2)</sup>       |      |

| l <sub>lkg</sub>                | Digital input pad leakage current                                 | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                        | -                       | -                        | ±1                      | μA   |

| 1                               | Analog input pad leakage current                                  | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>-40 °C < T <sub>A</sub> < 125 °C | -                       | -                        | ±250                    | nA   |

| l <sub>lkg ana</sub>            |                                                                   | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>-40 °C < T <sub>A</sub> < 150 °C | -                       | -                        | ±500                    |      |

| l <sub>lkg(inj)</sub>           | Leakage current in<br>adjacent I/O <sup>(3)</sup>                 | Injection current ±4 mA                                                                 | -                       | -                        | ±1 <sup>(3)</sup>       | μA   |

| I <sub>DDIO</sub>               | Total current on either<br>V <sub>DDIO</sub> or V <sub>SSIO</sub> | Including injection currents                                                            | -                       | -                        | 60                      | mA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

## 10.3.10 I<sup>2</sup>C interface characteristics

| Symbol                                     | Parameter                                               | Standard           | mode I <sup>2</sup> C | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    | Unit |  |

|--------------------------------------------|---------------------------------------------------------|--------------------|-----------------------|-------------------------------------------|--------------------|------|--|

| Symbol                                     |                                                         | Min <sup>(2)</sup> | Max <sup>(2)</sup>    | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                      | 4.7                | -                     | 1.3                                       | -                  | 110  |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                     | 4.0                | -                     | 0.6                                       | -                  | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                          | 250                | -                     | 100                                       | -                  |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                      | 0 <sup>(3)</sup>   | -                     | 0 <sup>(4)</sup>                          | 900 <sup>(3)</sup> |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time<br>(V <sub>DD</sub> = 3 to 5.5 V) | -                  | 1000                  | -                                         | 300                | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time<br>(V <sub>DD</sub> = 3 to 5.5 V) | -                  | 300                   | -                                         | 300                |      |  |

| t <sub>h(STA)</sub>                        | START condition hold time                               | 4.0                | -                     | 0.6                                       | -                  |      |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time                     | 4.7                | -                     | 0.6                                       | -                  |      |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time                               | 4.0                | -                     | 0.6                                       | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free)                 | 4.7                | -                     | 1.3                                       | -                  |      |  |

| Cb                                         | Capacitive load for each bus line                       | -                  | 400                   | -                                         | 400                | pF   |  |

### Table 39. I<sup>2</sup>C characteristics

1.  $f_{MASTER}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz)

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

### 10.3.12 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                         | Level/class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, T <sub>A</sub> = 25 °C,<br>f <sub>MASTER</sub> = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-2 | 3/B         |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>f <sub>MASTER</sub> = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-4          | 4/A         |

| Table | 12  | EMC | data |

|-------|-----|-----|------|

| rable | 4Z. |     | uala |

### **Electromagnetic interference (EMI)**

Emission tests conform to the IEC 61967-2 standard for test software, board layout and pin loading.

| r                                        |                                        |                                     |                   |    |           |  |  |  |

|------------------------------------------|----------------------------------------|-------------------------------------|-------------------|----|-----------|--|--|--|

|                                          | Conditions                             |                                     |                   |    |           |  |  |  |

| Symbol                                   | General conditions frequency band 8 16 | lax f <sub>CPU</sub> <sup>(1)</sup> |                   |    |           |  |  |  |

|                                          | General condition                      |                                     |                   | -  | 16<br>MHz |  |  |  |

| S <sub>EMI</sub> Peak level<br>EMI level |                                        | V <sub>DD</sub> = 5 V,              | 0.1 MHz to 30 MHz | 15 | 17        |  |  |  |

|                                          |                                        | 30 MHz to 130 MHz                   | 18                | 22 | dBµV      |  |  |  |

|                                          |                                        | 130 MHz to 1 GHz                    | -1                | 3  | υυμν      |  |  |  |

|                                          | EMI level                              | 61967-2                             | -                 | 2  | 2.5       |  |  |  |

| Table 4 | 13. E | EMI c | lata |

|---------|-------|-------|------|

|---------|-------|-------|------|

1. Data based on characterization results, not tested in production.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Table 44. | ESD abs | olute maximum | ratings |

|-----------|---------|---------------|---------|

|-----------|---------|---------------|---------|

| Symbol Ratings        |                                                       | Conditions                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model) | $T_A = 25^{\circ}C$ , conforming to JESD22-A114     | ЗA    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | $T_A = 25^{\circ}C$ , conforming to JESD22-C101     | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (Machine model)       | T <sub>A</sub> = 25°C, conforming to<br>JESD22-A115 | В     | 200                             |      |

1. Data based on characterization results, not tested in production

## 11 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

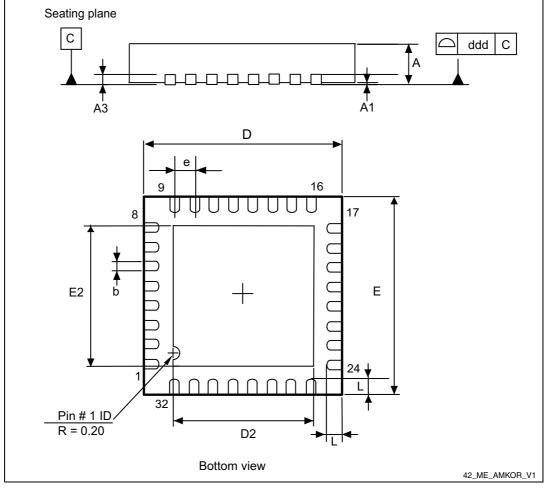

## 11.1 VFQFPN32 package information

Figure 42. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package outline

1. Drawing is not to scale.

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |  |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|--|--|

| Symbol | Min   | Тур         | Мах   | Min                   | Тур    | Max    |  |  |  |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |  |  |  |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |  |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |  |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |  |  |

| С      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |  |  |

| D      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |  |  |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |  |  |

| D3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |  |  |

| Е      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |  |  |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |  |  |

| E3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |  |  |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |  |  |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |  |  |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |  |  |  |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |  |  |

| CCC    | -     | -           | 0.080 | -                     | -      | 0.0031 |  |  |  |

| Table 47. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

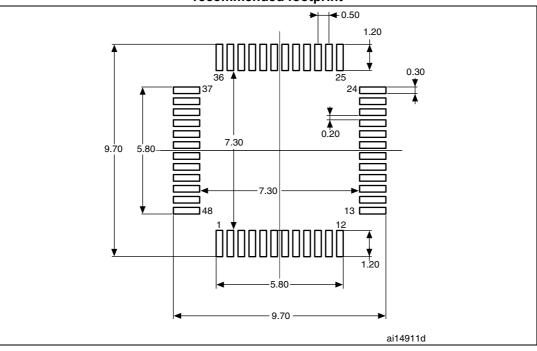

# Figure 46. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

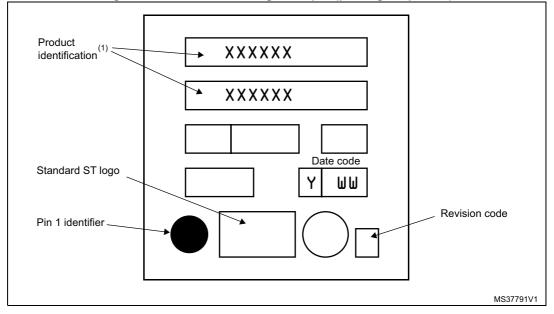

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 47. LQFP48 marking example (package top view)

## **12** Ordering information

| Example:                                | STM8A | F | 62 | 6 | 6 | Т | т | D | xxx <sup>(3)</sup> | ١ |

|-----------------------------------------|-------|---|----|---|---|---|---|---|--------------------|---|

| Product class                           |       |   | Ī  |   |   |   |   |   |                    | 1 |

| 8-bit automotive microcontroller        |       |   |    |   |   |   |   |   |                    |   |

|                                         |       |   |    |   |   |   |   |   |                    |   |

| Program memory type                     |       |   |    |   |   |   |   |   |                    |   |

| F = Flash + EEPROM                      |       |   |    |   |   |   |   |   |                    |   |

| P = FASTROM                             |       |   |    |   |   |   |   |   |                    |   |

| Device family                           |       |   |    |   |   |   |   |   |                    |   |

| 62 = Silicon rev X and rev W, LIN only  |       |   |    |   |   |   |   |   |                    |   |

|                                         |       |   |    |   |   |   |   |   |                    |   |

| Program memory size<br>4 = 16 Kbyte     |       |   |    |   |   |   |   |   |                    |   |

| 4 = 16 Kbyte<br>6 = 32 Kbyte            |       |   |    |   |   |   |   |   |                    |   |

| 0 – 32 Kbyle                            |       |   |    |   |   |   |   |   |                    |   |

| Pin count                               |       |   |    |   |   |   |   |   |                    |   |

| 6 = 32 pins                             |       |   |    |   |   |   |   |   |                    |   |

| 8 = 48 pins                             |       |   |    |   |   |   |   |   |                    |   |

| HSI accuracy                            |       |   |    |   |   |   |   |   |                    |   |

| Blank = ± 5 %                           |       |   |    |   |   |   |   |   |                    |   |

| I = ± 2.5 %                             |       |   |    |   |   |   |   |   |                    |   |

| Package type                            |       |   |    |   |   |   |   |   |                    |   |

| T = LQFP                                |       |   |    |   |   |   |   |   |                    |   |

| U = VFQFPN                              |       |   |    |   |   |   |   |   |                    |   |

| Temperature range                       |       |   |    |   |   |   |   |   |                    |   |

| A = -40 to 85 °C                        |       |   |    |   |   |   |   | _ |                    |   |

| C = -40 to 125 °C                       |       |   |    |   |   |   |   |   |                    |   |

| D = -40 to 150 °C                       |       |   |    |   |   |   |   |   |                    |   |

| Packing                                 |       |   |    |   |   |   |   |   |                    |   |

| Y = Tray                                |       |   |    |   |   |   |   |   |                    |   |

| U = Tube                                |       |   |    |   |   |   |   |   |                    |   |

| X = Tape and reel compliant with EIA 48 | 1-C   |   |    |   |   |   |   |   |                    |   |

#### Figure 51. STM8AF6246/48/66/68 ordering information scheme<sup>(1) (2)</sup>

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to <u>www.st.com</u> or contact the nearest ST Sales Office.

- 2. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

- Customer specific FASTROM code or custom device configuration. This field shows 'SSS' if the device contains a super set silicon, usually equipped with bigger memory and more I/Os. This silicon is supposed to be replaced later by the target silicon.

DocID14952 Rev 11