Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-VFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6246ucx |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

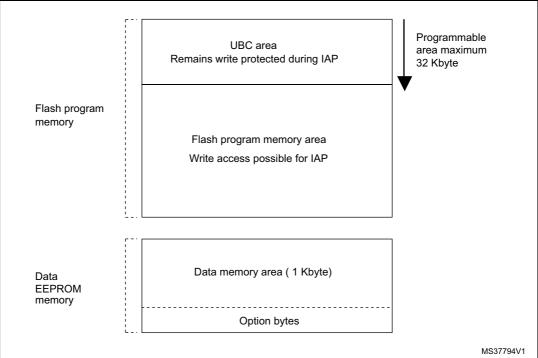

## 5.4.2 Write protection (WP)

Write protection in application mode is intended to avoid unintentional overwriting of the memory. The write protection can be removed temporarily by executing a specific sequence in the user software.

## 5.4.3 Protection of user boot code (UBC)

If the user chooses to update the Flash program memory using a specific boot code to perform in application programming (IAP), this boot code needs to be protected against unwanted modification.

In the STM8A a memory area of up to 32 Kbyte can be protected from overwriting at user option level. Other than the standard write protection, the UBC protection can exclusively be modified via the debug interface, the user software cannot modify the UBC protection status.

The UBC memory area contains the reset and interrupt vectors and its size can be adjusted in increments of 512 bytes by programming the UBC and NUBC option bytes (see Section 9: Option bytes on page 44).

Figure 2. Flash memory organization of STM8AF6246/48/66/68

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure. If the hardware watchdog feature is enabled through the device option bits, the watchdog is automatically enabled at power-on, and generates a reset unless the key register is written by software before the counter reaches the end of count.

#### 5.7.2 Auto-wakeup counter

This counter is used to cyclically wakeup the device in Active-halt mode. It can be clocked by the internal 128 kHz internal low-frequency RC oscillator or external clock.

LSI clock can be internally connected to TIM3 input capture channel 1 for calibration.

#### 5.7.3 Beeper

This function generates a rectangular signal in the range of 1, 2 or 4 kHz which can be output on a pin. This is useful when audible sounds without interference need to be generated for use in the application.

#### 5.7.4 Advanced control and general purpose timers

STM8A devices described in this datasheet, contain up to three 16-bit advanced control and general purpose timers providing nine CAPCOM channels in total. A CAPCOM channel can be used either as input compare, output compare or PWM channel. These timers are named TIM1, TIM2 and TIM3.

| Timer | Counter<br>width | Counter<br>type | Prescaler<br>factor           | Channels | Inverted outputs | Repetition counter | trigger<br>unit | External trigger | Break<br>input |

|-------|------------------|-----------------|-------------------------------|----------|------------------|--------------------|-----------------|------------------|----------------|

| TIM1  | 16-bit           | Up/down         | 1 to 65536                    | 4        | 3                | Yes                | Yes             | Yes              | Yes            |

| TIM2  | 16-bit           | Up              | 2 <sup>n</sup><br>n = 0 to 15 | 3        | None             | No                 | No              | No               | No             |

| TIM3  | 16-bit           | Up              | 2 <sup>n</sup><br>n = 0 to 15 | 2        | None             | No                 | No              | No               | No             |

#### Table 3. Advanced control and general purpose timers

#### UART mode

- Full duplex, asynchronous communications NRZ standard format (mark/space)

- High-precision baud rate generator

- A common programmable transmit and receive baud rates up to f<sub>MASTER</sub>/16

- Programmable data word length (8 or 9 bits) 1 or 2 stop bits parity control

- Separate enable bits for transmitter and receiver

- Error detection flags

- Reduced power consumption mode

- Multi-processor communication enter mute mode if address match does not occur

- Wakeup from mute mode (by idle line detection or address mark detection)

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line

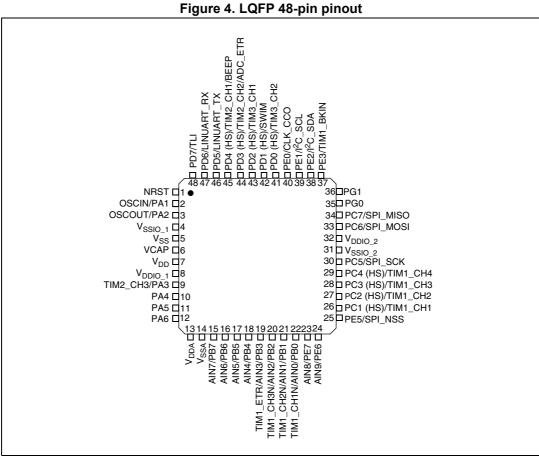

## 5.10 Input/output specifications

The product features four different I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

2. (HS) high sink capability.

Table 7. Legend/abbreviation

| Туре             | I= input, O                                                                                                                                                                                               | I= input, O = output, S = power supply                                                                                                                               |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Level            | Input                                                                                                                                                                                                     | CM = CMOS (standard for all I/Os)                                                                                                                                    |  |  |  |  |  |  |

|                  | Output                                                                                                                                                                                                    | Dutput HS = High sink (8 mA)                                                                                                                                         |  |  |  |  |  |  |

| Output speed     | O1 = Standard (up to 2 MHz)<br>O2 = Fast (up to 10 MHz)<br>O3 = Fast/slow programmability with slow as default state after reset<br>O4 = Fast/slow programmability with fast as default state after reset |                                                                                                                                                                      |  |  |  |  |  |  |

| Port and control | Input                                                                                                                                                                                                     | float = floating, wpu = weak pull-up                                                                                                                                 |  |  |  |  |  |  |

| configuration    | Output                                                                                                                                                                                                    | T = true open drain, OD = open drain, PP = push pull                                                                                                                 |  |  |  |  |  |  |

| Reset state      | Unless othe                                                                                                                                                                                               | state after reset release).<br>rwise specified, the pin state is the same during the reset phase (i.e.<br>") and after internal reset release (i.e. at reset state). |  |  |  |  |  |  |

| Pi     | -             |                             |      |          |      |                | •         |       | ,   |    |                                |                               |                                                      |

|--------|---------------|-----------------------------|------|----------|------|----------------|-----------|-------|-----|----|--------------------------------|-------------------------------|------------------------------------------------------|

| num    |               |                             |      |          | Inpu | t              |           | Out   | put |    | _                              |                               |                                                      |

| LQFP48 | VFQFPN/LQFP32 | Pin name                    | Type | floating | wpu  | Ext. interrupt | High sink | Speed | OD  | ЬР | Main function<br>(after reset) | Default alternate<br>function | Alternate<br>function after<br>remap<br>[option bit] |

| 1      | 1             | NRST                        | I/O  | -        | Х    | -              | -         | -     | -   | -  | Reset                          | •                             | -                                                    |

| 2      | 2             | PA1/OSCIN <sup>(3)</sup>    | I/O  | X        | Х    | -              | -         | 01    | Х   | Х  | Port A1                        | Resonator/crystal in          | -                                                    |

| 3      | 3             | PA2/OSCOUT                  | I/O  | X        | Х    | Х              | -         | 01    | Х   | Х  | Port A2                        | Resonator/crystal out         | -                                                    |

| 4      | -             | V <sub>SSIO_1</sub>         | S    | -        | -    | -              | -         | -     | -   | -  | I/O groun                      | d                             | -                                                    |

| 5      | 4             | V <sub>SS</sub>             | S    | -        | -    | -              | -         | -     | -   | -  | Digital gro                    | bund                          | -                                                    |

| 6      | 5             | VCAP                        | S    | -        | -    | -              | -         | -     | -   | -  | 1.8 V reg                      | ulator capacitor              | -                                                    |

| 7      | 6             | V <sub>DD</sub>             | S    | -        | -    | -              | -         | -     | -   | -  | Digital po                     | wer supply                    | -                                                    |

| 8      | 7             | V <sub>DDIO_1</sub>         | S    | -        | -    | -              | -         | -     | -   | -  | I/O power                      | supply                        | -                                                    |

| -      | 8             | PF4/AIN12 <sup>(4)(5)</sup> | I/O  | X        | Х    |                | -         | 01    | Х   | Х  | Port F4                        | Analog input 12               | -                                                    |

| 9      | -             | PA3/TIM2_CH3                | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port A3                        | Timer 2 - channel 3           | TIM3_CH1<br>[AFR1]                                   |

| 10     | -             | PA4                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A4                        |                               | -                                                    |

| 11     | -             | PA5                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A5                        |                               | -                                                    |

| 12     | -             | PA6                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A6                        |                               | -                                                    |

| 13     | 9             | V <sub>DDA</sub>            | S    | -        | -    | -              | -         | -     | -   | -  | Analog po                      | ower supply                   | -                                                    |

| 14     | 10            | V <sub>SSA</sub>            | S    | -        | -    | -              | -         | -     | -   | -  | Analog gr                      | ound                          | -                                                    |

| 15     | -             | PB7/AIN7                    | I/O  | Х        | Х    | Х              | -         | 01    | Х   | Х  | Port B7                        | Analog input 7                | -                                                    |

| 16     | -             | PB6/AIN6                    | I/O  | Х        | Х    | Х              | -         | 01    | Х   | Х  | Port B6                        | Analog input 6                | -                                                    |

| 17     | 11            | PB5/AIN5                    | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port B5                        | Analog input 5                | I <sup>2</sup> C_SDA<br>[AFR6]                       |

| 18     | 12            | PB4/AIN4                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B4                        | Analog input 4                | I <sup>2</sup> C_SCL<br>[AFR6]                       |

| 19     | 13            | PB3/AIN3                    | I/O  | x        | х    | х              | I         | 01    | х   | х  | Port B3                        | Analog input 3                | TIM1_ETR<br>[AFR5]                                   |

| 20     | 14            | PB2/AIN2                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B2                        | Analog input                  | TIM1_NCC3<br>[AFR5]                                  |

| 21     | 15            | PB1/AIN1                    | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port B1                        | Analog input 1                | TIM1_NCC2<br>[AFR5]                                  |

| 22     | 16            | PB0/AIN0                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B0                        | Analog input 0                | TIM1_NCC1<br>[AFR5]                                  |

| 23     | -             | PE7/AIN8                    | I/O  | X        | Х    |                | -         | 01    | Х   | Х  | Port E7                        | Analog input 8                | -                                                    |

| Table 8. STM8AF6246/48/66/68 ( | (32 Kbv | vte) micro | ocontroller | pin descri | ption <sup>(1)(2)</sup> |

|--------------------------------|---------|------------|-------------|------------|-------------------------|

|                                |         |            |             | pin acour  | puon                    |

|           |                                 |                | wale legister map (continued)     |                                |      |

|-----------|---------------------------------|----------------|-----------------------------------|--------------------------------|------|

| Address   | Block                           | Register label | Register name                     | Reset<br>status                |      |

| 0x00 5014 |                                 | PE_ODR         | Port E data output latch register | 0x00                           |      |

| 0x00 5015 |                                 | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup>            |      |

| 0x00 5016 | Port E                          | PE_DDR         | Port E data direction register    | 0x00                           |      |

| 0x00 5017 |                                 | PE_CR1         | Port E control register 1         | 0x00                           |      |

| 0x00 5018 | D18 PE_CR2 Port E control regis |                | Port E control register 2         | 0x00                           |      |

| 0x00 5019 |                                 | PF_ODR         | Port F data output latch register | 0x00                           |      |

| 0x00 501A |                                 | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup>            |      |

| 0x00 501B | Port F                          | Port F         | PF_DDR                            | Port F data direction register | 0x00 |

| 0x00 501C |                                 | PF_CR1         | Port F control register 1         | 0x00                           |      |

| 0x00 501D |                                 | PF_CR2         | Port F control register 2         | 0x00                           |      |

| 0x00 501E |                                 | PG_ODR         | Port G data output latch register | 0x00                           |      |

| 0x00 501F |                                 | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup>            |      |

| 0x00 5020 | Port G                          | PG_DDR         | Port G data direction register    | 0x00                           |      |

| 0x00 5021 |                                 | PG_CR1         | Port G control register 1         | 0x00                           |      |

| 0x00 5022 |                                 | PG_CR2         | Port G control register 2         | 0x00                           |      |

| Table 10. I/O port hardware register map (continued) |

|------------------------------------------------------|

|------------------------------------------------------|

1. Depends on the external circuitry.

| Address                   | Block | Register label           | Register name                                              | Reset<br>status |  |  |  |  |

|---------------------------|-------|--------------------------|------------------------------------------------------------|-----------------|--|--|--|--|

| 0x00 505A                 |       | FLASH_CR1                | Flash control register 1                                   | 0x00            |  |  |  |  |

| 0x00 505B                 |       | FLASH_CR2                | Flash control register 2                                   | 0x00            |  |  |  |  |

| 0x00 505C                 |       | FLASH_NCR2               | Flash complementary control register 2                     | 0xFF            |  |  |  |  |

| 0x00 505D                 | Flash | FLASH_FPR                | Flash protection register                                  | 0x00            |  |  |  |  |

| 0x00 505E                 |       | FLASH_NFPR               | Flash complementary protection register                    | 0xFF            |  |  |  |  |

| 0x00 505F                 |       | FLASH_IAPSR              | ASH_IAPSR Flash in-application programming status register |                 |  |  |  |  |

| 0x00 5060 to<br>0x00 5061 |       | R                        | eserved area (2 bytes)                                     |                 |  |  |  |  |

| 0x00 5062                 | Flash | FLASH_PUKR               | Flash Program memory unprotection register                 | 0x00            |  |  |  |  |

| 0x00 5063                 |       | F                        | Reserved area (1 byte)                                     |                 |  |  |  |  |

| 0x00 5064                 | Flash | FLASH_DUKR               | Data EEPROM unprotection register                          | 0x00            |  |  |  |  |

| 0x00 5065 to<br>0x00 509F |       | Reserved area (59 bytes) |                                                            |                 |  |  |  |  |

#### Table 11. General hardware register map

DocID14952 Rev 11

| A al al c                  | Option                | Option   | 10 | Option bits           7         6         5         4         3         2         1         0 |  |          |            |  |  |                |      |  |

|----------------------------|-----------------------|----------|----|-----------------------------------------------------------------------------------------------|--|----------|------------|--|--|----------------|------|--|

| Addr.                      | name                  | byte no. | 7  |                                                                                               |  |          |            |  |  |                |      |  |

| 0x00<br>480B               | TMU                   | OPT6     |    |                                                                                               |  | TM       | U[3:0]     |  |  |                | 0x00 |  |

| 0x00<br>480C               | TMO                   | NOPT6    |    | NTMU[3:0]                                                                                     |  |          |            |  |  |                |      |  |

| 0x00<br>480D               | Flash wait            | OPT7     |    | Reserved WAIT<br>STATE                                                                        |  |          |            |  |  |                |      |  |

| 0x00<br>480E               | states                | NOPT7    |    |                                                                                               |  | Reserve  | d          |  |  | NWAIT<br>STATE | 0xFF |  |

| 0x00<br>480F               |                       |          |    |                                                                                               |  | Reserved |            |  |  |                |      |  |

| 0x00<br>4810               |                       | OPT8     |    |                                                                                               |  | TMU_K    | EY 1 [7:0] |  |  |                | 0x00 |  |

| 0x00<br>4811               |                       | OPT9     |    |                                                                                               |  | TMU_K    | EY 2 [7:0] |  |  |                | 0x00 |  |

| 0x00<br>4812               |                       | OPT10    |    | TMU_KEY 3 [7:0]                                                                               |  |          |            |  |  |                |      |  |

| 0x00<br>4813               |                       | OPT11    |    | TMU_KEY 4 [7:0]                                                                               |  |          |            |  |  |                | 0x00 |  |

| 0x00<br>4814               | TMU                   | OPT12    |    | TMU_KEY 5 [7:0]                                                                               |  |          |            |  |  |                | 0x00 |  |

| 0x00<br>4815               |                       | OPT13    |    | TMU_KEY 6 [7:0]                                                                               |  |          |            |  |  |                | 0x00 |  |

| 0x00<br>4816               |                       | OPT14    |    |                                                                                               |  | TMU_K    | EY 7 [7:0] |  |  |                | 0x00 |  |

| 0x00<br>4817               |                       | OPT15    |    | TMU_KEY 8 [7:0]                                                                               |  |          |            |  |  |                |      |  |

| 0x00<br>4818               |                       | OPT16    |    | TMU_MAXATT [7:0]                                                                              |  |          |            |  |  |                |      |  |

| 0x00<br>4819<br>to<br>487D | Reserved              |          |    |                                                                                               |  |          |            |  |  |                |      |  |

| 0x00<br>487E               | Boot-                 | OPT17    |    |                                                                                               |  | BL       | [7:0]      |  |  |                | 0x00 |  |

| 0x00<br>487F               | loader <sup>(1)</sup> | NOPT17   |    |                                                                                               |  | NB       | L[7:0]     |  |  |                | 0xFF |  |

Table 15. Option bytes (continued)

1. This option consists of two bytes that must have a complementary value in order to be valid. If the option is invalid, it has no effect on EMC reset.

| Option byte no. | Description                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | HSITRIM: Trimming option for 16 MHz internal RC oscillator                                                                                      |

|                 | 0: 3-bit on-the-fly trimming (compatible with devices based on the 128K silicon)                                                                |

|                 | 1: 4-bit on-the-fly trimming                                                                                                                    |

|                 | LSI_EN: Low speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source   |

| OPT3            | IWDG_HW: Independent watchdog                                                                                                                   |

| UF 13           | <ul><li>0: IWDG independent watchdog activated by software</li><li>1: IWDG independent watchdog activated by hardware</li></ul>                 |

|                 | WWDG_HW: Window watchdog activation                                                                                                             |

|                 | <ul><li>0: WWDG window watchdog activated by software</li><li>1: WWDG window watchdog activated by hardware</li></ul>                           |

|                 | WWDG_HALT: Window watchdog reset on Halt                                                                                                        |

|                 | 0: No reset generated on Halt if WWDG active<br>1: Reset generated on Halt if WWDG active                                                       |

|                 | EXTCLK: External clock selection                                                                                                                |

|                 | 0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                              |

|                 | CKAWUSEL: Auto-wakeup unit/clock                                                                                                                |

| OPT4            | 0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU                                            |

|                 | PRSC[1:0]: AWU clock prescaler                                                                                                                  |

|                 | 00: Reserved<br>01: 16 MHz to 128 kHz prescaler                                                                                                 |

|                 | 10: 8 MHz to 128 kHz prescaler                                                                                                                  |

|                 | 11: 4 MHz to 128 kHz prescaler                                                                                                                  |

| 0.075           | HSECNT[7:0]: HSE crystal oscillator stabilization time                                                                                          |

| OPT5            | This configures the stabilization time to 0.5, 8, 128, and 2048 HSE cycles with corresponding option byte values of 0xE1, 0xD2, 0xB4, and 0x00. |

| 0.770           | TMU[3:0]: Enable temporary memory unprotection                                                                                                  |

| OPT6            | 0101: TMU disabled (permanent ROP).<br>Any other value: TMU enabled.                                                                            |

| OPT7            | Reserved                                                                                                                                        |

| OPT8            | TMU_KEY 1 [7:0]: Temporary unprotection key 0<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                |

|                 | TMU_KEY 2 [7:0]: Temporary unprotection key 1                                                                                                   |

| OPT9            | Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                 |

| OPT10           | TMU_KEY 3 [7:0]: Temporary unprotection key 2<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                |

|                 | TMU_KEY 4 [7:0]: Temporary unprotection key 3                                                                                                   |

| OPT11           | Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                 |

Table 16. Option byte description (continued)

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OPT12           | TMU_KEY 5 [7:0]: Temporary unprotection key 4<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| OPT13           | TMU_KEY 6 [7:0]: Temporary unprotection key 5           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| OPT14           | TMU_KEY 7 [7:0]: Temporary unprotection key 6           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| OPT15           | TMU_KEY 8 [7:0]: Temporary unprotection key 7<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| OPT16           | TMU_MAXATT [7:0]: TMU access failure counter         TMU_MAXATT can be initialized with the desired value only if TMU is disabled (TMU[3:0]=0101 in OPT6 option byte).         When TMU is enabled, any attempt to temporary remove the readout protection by using wrong key values increments the counter.         When the option byte value reaches 0x08, the Flash memory and data EEPROM are erased. |  |  |  |  |  |

| OPT17           | BL [7:0]: Bootloader enable<br>If this option byte is set to 0x55 (complementary value 0xAA) the<br>bootloader program is activated also in case of a programmed code<br>memory<br>(for more details, see the bootloader user manual, UM0560).                                                                                                                                                             |  |  |  |  |  |

#### Table 16. Option byte description (continued)

| r                   | General conditions for $v_{DD}$ apply, $T_A = -40$ to 55 °C |                                                                                |                |                                                          |                        |                    |      |  |

|---------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|----------------|----------------------------------------------------------|------------------------|--------------------|------|--|

|                     |                                                             |                                                                                | Conditi        |                                                          |                        |                    |      |  |

| Symbol              | Parameter                                                   | Main<br>voltage Flash<br>regulator mode <sup>(2)</sup><br>(MVR) <sup>(1)</sup> |                | Clock source and<br>specific<br>temperature<br>condition | Тур                    | Мах                | Unit |  |

|                     |                                                             |                                                                                | Power-         | Clocks stopped                                           | 5                      | 35 <sup>(3)</sup>  |      |  |

| I <sub>DD(H)</sub>  | Supply current in Halt mode                                 | Off                                                                            | down           | Clocks stopped,<br>T <sub>A</sub> = 25 °C                | 5                      | 25                 |      |  |

|                     | Supply current in Active-halt                               | On                                                                             | Power-<br>down | Ext. clock 16 MHz<br>f <sub>MASTER</sub> = 125 kHz       | 770 900 <sup>(3)</sup> |                    | μA   |  |

|                     | mode with regulator on                                      |                                                                                | down           | LSI clock 128 kHz                                        | 150                    | 230 <sup>(3)</sup> |      |  |

| I <sub>DD(AH)</sub> | Supply current in Active-halt                               |                                                                                | Power-         | LSI clock 128 kHz                                        | 25                     | 42 <sup>(3)</sup>  |      |  |

|                     | mode with regulator off                                     | Off                                                                            | down           | LSI clock 128 kHz,<br>T <sub>A</sub> = 25 °C             | 25                     | 30                 |      |  |

| t                   | Wakeup time from Active-<br>halt mode with regulator on     | On                                                                             | Operating      | T <sub>A</sub> = -40 to 150 °C                           | 10                     | 30 <sup>(3)</sup>  | μs   |  |

| t <sub>WU(AH)</sub> | Wakeup time from Active-<br>halt mode with regulator off    | Off                                                                            | mode           | i <sub>A</sub> = -το το 150° Ο                           | 50                     | 80 <sup>(3)</sup>  | μο   |  |

#### Table 24. Total current consumption in Halt and Active-halt modes. General conditions for $V_{DD}$ apply, $T_A = -40$ to 55 °C

1. Configured by the REGAH bit in the CLK\_ICKR register.

2. Configured by the AHALT bit in the FLASH\_CR1 register.

3. Data based on characterization results. Not tested in production.

#### Current consumption for on-chip peripherals

| Table 25. Oscillator | current consumption |

|----------------------|---------------------|

|----------------------|---------------------|

| Symbol   | Parameter                                                      | Con                                   | ditions                   | Тур  | Max <sup>(1)</sup>        | Unit |   |  |

|----------|----------------------------------------------------------------|---------------------------------------|---------------------------|------|---------------------------|------|---|--|

|          | Quartz or                                                      |                                       | f <sub>OSC</sub> = 24 MHz | 1    | 2.0 <sup>(3)</sup>        |      |   |  |

|          |                                                                | ceramic<br>resonator,                 |                           |      | f <sub>OSC</sub> = 16 MHz | 0.6  | - |  |

|          | CL = 33 pF<br>HSE oscillator current                           | f <sub>OSC</sub> = 8 MHz              | 0.57                      | -    | mA                        |      |   |  |

| IDD(OSC) | consumption <sup>(2)</sup>                                     | nption <sup>(2)</sup> Quartz or       | f <sub>OSC</sub> = 24 MHz | 0.5  | 1.0 <sup>(3)</sup>        | ШA   |   |  |

|          | ceramic<br>resonator,<br>CL = 33 pF<br>V <sub>DD</sub> = 3.3 V | f <sub>OSC</sub> = 16 MHz             | 0.25                      | -    |                           |      |   |  |

|          |                                                                | CL = 33 pF<br>V <sub>DD</sub> = 3.3 V | f <sub>OSC</sub> = 8 MHz  | 0.18 | -                         |      |   |  |

1. During startup, the oscillator current consumption may reach 6 mA.

2. The supply current of the oscillator can be further optimized by selecting a high quality resonator with small  $R_m$  value. Refer to crystal manufacturer for more details

3. Informative data.

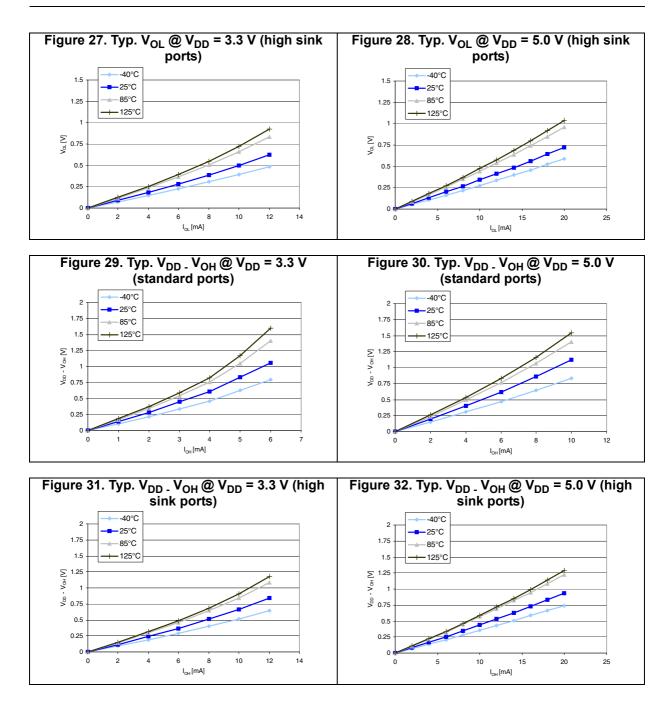

## 10.3.6 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage, using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                          | Parameter                                                         | Conditions                                                                              | Min                     | Тур                      | Мах                     | Unit |

|---------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------------------|------|

| $V_{IL}$                        | Input low level voltage                                           |                                                                                         | -0.3 V                  | -                        | 0.3 x V <sub>DD</sub>   |      |

| V <sub>IH</sub>                 | Input high level voltage                                          | _                                                                                       | 0.7 x V <sub>DD</sub>   | -                        | V <sub>DD</sub> + 0.3 V |      |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                                         |                                                                                         | -                       | 0.1 x<br>V <sub>DD</sub> | -                       |      |

| M                               | Output high level voltage                                         | Standard I/0, V <sub>DD</sub> = 5 V,<br>I = 3 mA                                        | V <sub>DD</sub> - 0.5 V | -                        | -                       |      |

| V <sub>OH</sub>                 | output high level voltage                                         | Standard I/0, V <sub>DD</sub> = 3 V,<br>I = 1.5 mA                                      | V <sub>DD</sub> - 0.4 V | -                        | -                       | V    |

|                                 |                                                                   | High sink and true open<br>drain I/0, V <sub>DD</sub> = 5 V<br>I = 8 mA                 | -                       | -                        | 0.5                     |      |

| $V_{OL}$                        | Output low level voltage                                          | Standard I/0, V <sub>DD</sub> = 5 V<br>I = 3 mA                                         | -                       | -                        | 0.6                     |      |

|                                 |                                                                   | Standard I/0, V <sub>DD</sub> = 3 V<br>I = 1.5 mA                                       | -                       | -                        | 0.4                     |      |

| R <sub>pu</sub>                 | Pull-up resistor                                                  | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$                                                     | 35                      | 50                       | 65                      | kΩ   |

|                                 | Rise and fall time<br>(10% - 90%)                                 | Fast I/Os<br>Load = 50 pF                                                               | -                       | -                        | 35 <sup>(2)</sup>       |      |

|                                 |                                                                   | Standard and high sink I/Os<br>Load = 50 pF                                             | -                       | -                        | 125 <sup>(2)</sup>      | ns   |

| ι <sub>R</sub> , ι <sub>F</sub> |                                                                   | Fast I/Os<br>Load = 20 pF                                                               | -                       | -                        | 20 <sup>(2)</sup>       | 115  |

|                                 |                                                                   | Standard and high sink I/Os<br>Load = 20 pF                                             | -                       | -                        | 50 <sup>(2)</sup>       |      |

| l <sub>lkg</sub>                | Digital input pad leakage current                                 | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                        | -                       | -                        | ±1                      | μA   |

| 1                               | Analog input pad leakage                                          | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>-40 °C < T <sub>A</sub> < 125 °C | -                       | -                        | ±250                    | ~    |

| l <sub>Ikg ana</sub>            | current                                                           | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>-40 °C < T <sub>A</sub> < 150 °C | -                       | -                        | ±500                    | nA   |

| l <sub>lkg(inj)</sub>           | Leakage current in<br>adjacent I/O <sup>(3)</sup>                 | Injection current ±4 mA                                                                 | -                       | -                        | ±1 <sup>(3)</sup>       | μA   |

| I <sub>DDIO</sub>               | Total current on either<br>V <sub>DDIO</sub> or V <sub>SSIO</sub> | Including injection currents                                                            | -                       | -                        | 60                      | mA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

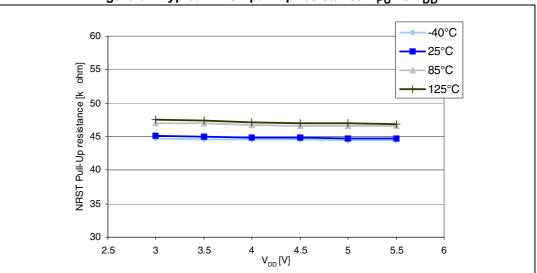

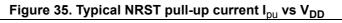

Figure 34. Typical NRST pull-up resistance  $R_{PU}$  vs  $V_{DD}$

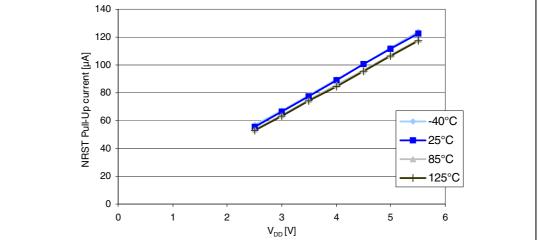

The reset network shown in *Figure 36* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below  $V_{IL(NRST)}$  max (see *Table 36: NRST pin characteristics*), otherwise the reset is not taken into account internally.

Figure 36. Recommended reset pin protection

DocID14952 Rev 11

### **Electromagnetic interference (EMI)**

Emission tests conform to the IEC 61967-2 standard for test software, board layout and pin loading.

|        |                                                      |                                           | Conditions        |                                     |           |      |

|--------|------------------------------------------------------|-------------------------------------------|-------------------|-------------------------------------|-----------|------|

| Symbol | Parameter                                            |                                           | Monitored         | Max f <sub>CPU</sub> <sup>(1)</sup> |           | Unit |

|        |                                                      | General conditions                        | frequency band    | 8<br>MHz                            | 16<br>MHz |      |

|        |                                                      | V <sub>DD</sub> = 5 V,                    | 0.1 MHz to 30 MHz | 15                                  | 17        |      |

| e      | Peak level                                           | T <sub>A</sub> = 25 °C,<br>LQFP80 package | 30 MHz to 130 MHz | 18                                  | 22        | dBµV |

| SEMI   | S <sub>EMI</sub> LQFP80 package<br>conforming to IEC | 130 MHz to 1 GHz                          | -1                | 3                                   | ubμv      |      |

|        | EMI level                                            | 61967-2                                   | -                 | 2                                   | 2.5       |      |

| Table 4 | 13. E | EMI c | lata |

|---------|-------|-------|------|

|---------|-------|-------|------|

1. Data based on characterization results, not tested in production.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Table 44. | ESD | absolute | maximum | ratings |

|-----------|-----|----------|---------|---------|

|-----------|-----|----------|---------|---------|

| Symbol                | Ratings                                               | Conditions                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model) | $T_A = 25^{\circ}C$ , conforming to JESD22-A114     | ЗA    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | $T_A = 25^{\circ}C$ , conforming to JESD22-C101     | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (Machine model)       | T <sub>A</sub> = 25°C, conforming to<br>JESD22-A115 | В     | 200                             |      |

1. Data based on characterization results, not tested in production

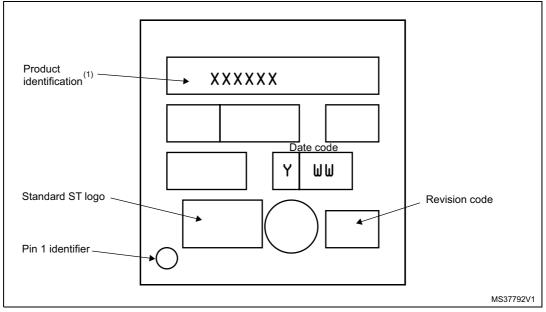

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

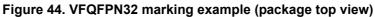

| Currence of |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|-------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol      | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А           | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1          | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2          | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b           | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| С           | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D           | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1          | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3          | -     | 5.500       | -     | -      | 0.2165                | -      |

| Е           | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| E1          | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| E3          | -     | 5.500       | -     | -      | 0.2165                | -      |

| е           | -     | 0.500       | -     | -      | 0.0197                | -      |

| L           | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1          | -     | 1.000       | -     | -      | 0.0394                | -      |

| k           | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| CCC         | -     | -           | 0.080 | -      | -                     | 0.0031 |

| Table 47. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 11.3 LQFP32 package information

Figure 48. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Currence of |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|-------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol      | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| А           | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1          | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2          | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b           | 0.300 | 0.370       | 0.450 | 0.0118 | 0.0146                | 0.0177 |

| С           | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D           | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1          | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3          | -     | 5.600       | -     | -      | 0.2205                | -      |

| Е           | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| E1          | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| E3          | -     | 5.600       | -     | -      | 0.2205                | -      |

| е           | -     | 0.800       | -     | -      | 0.0315                | -      |

| L           | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1          | -     | 1.000       | -     | -      | 0.0394                | -      |

| k           | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| CCC         | -     | -           | 0.100 | -      | -                     | 0.0039 |

| Table 48. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# **12** Ordering information

| Example:                                | STM8A | F | 62 | 6 | 6 | Т | т | D | xxx <sup>(3)</sup> | ١ |

|-----------------------------------------|-------|---|----|---|---|---|---|---|--------------------|---|

| Product class                           |       |   | I  |   |   |   |   |   |                    | 1 |

| 8-bit automotive microcontroller        |       |   |    |   |   |   |   |   |                    |   |

|                                         |       |   |    |   |   |   |   |   |                    |   |

| Program memory type                     |       |   |    |   |   |   |   |   |                    |   |

| F = Flash + EEPROM                      |       |   |    |   |   |   |   |   |                    |   |

| P = FASTROM                             |       |   |    |   |   |   |   |   |                    |   |

| Device family                           |       |   |    |   |   |   |   |   |                    |   |

| 62 = Silicon rev X and rev W, LIN only  |       |   |    |   |   |   |   |   |                    |   |

|                                         |       |   |    |   |   |   |   |   |                    |   |

| Program memory size<br>4 = 16 Kbyte     |       |   |    |   |   |   |   |   |                    |   |

| 4 = 16 Kbyte<br>6 = 32 Kbyte            |       |   |    |   |   |   |   |   |                    |   |

| 0 – 32 Kbyle                            |       |   |    |   |   |   |   |   |                    |   |

| Pin count                               |       |   |    |   |   |   |   |   |                    |   |

| 6 = 32 pins                             |       |   |    |   |   |   |   |   |                    |   |

| 8 = 48 pins                             |       |   |    |   |   |   |   |   |                    |   |

| HSI accuracy                            |       |   |    |   |   |   |   |   |                    |   |

| Blank = ± 5 %                           |       |   |    |   |   |   |   |   |                    |   |

| I = ± 2.5 %                             |       |   |    |   |   |   |   |   |                    |   |

| Package type                            |       |   |    |   |   |   |   |   |                    |   |

| T = LQFP                                |       |   |    |   |   |   |   |   |                    |   |

| U = VFQFPN                              |       |   |    |   |   |   |   |   |                    |   |

| Temperature range                       |       |   |    |   |   |   |   |   |                    |   |

| A = -40 to 85 °C                        |       |   |    |   |   |   |   | _ |                    |   |

| C = -40 to 125 °C                       |       |   |    |   |   |   |   |   |                    |   |

| D = -40 to 150 °C                       |       |   |    |   |   |   |   |   |                    |   |

| Packing                                 |       |   |    |   |   |   |   |   |                    |   |

| Y = Tray                                |       |   |    |   |   |   |   |   |                    | _ |

| U = Tube                                |       |   |    |   |   |   |   |   |                    |   |

| X = Tape and reel compliant with EIA 48 | 1-C   |   |    |   |   |   |   |   |                    |   |

#### Figure 51. STM8AF6246/48/66/68 ordering information scheme<sup>(1) (2)</sup>

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to <u>www.st.com</u> or contact the nearest ST Sales Office.

- 2. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

- Customer specific FASTROM code or custom device configuration. This field shows 'SSS' if the device contains a super set silicon, usually equipped with bigger memory and more I/Os. This silicon is supposed to be replaced later by the target silicon.

DocID14952 Rev 11

# 13 STM8 development tools

Development tools for the STM8A microcontrollers include the

- STice emulation system offering tracing and code profiling

- STVD high-level language debugger including assembler and visual development environment seamless integration of third party C compilers.

- STVP Flash programming software

In addition, the STM8A comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

# 13.1 Emulation and in-circuit debugging tools

The STM8 tool line includes the STice emulation system offering a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8A application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full-featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including tracing, profiling and code coverage analysis to help detect execution bottlenecks and dead code.

In addition, STice offers in-circuit debugging and programming of STM8A microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows users to order exactly what they need to meet their development requirements and to adapt their emulation system to support existing and future ST microcontrollers.

## 13.1.1 STice key features

- Program and data trace recording up to 128 K records

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Real-time read/write of all device resources during emulation

- Occurrence and time profiling and code coverage analysis (new features)

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- USB 2.0 high speed interface to host PC

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows users to specify the components they need to meet their development requirements and adapt to future requirements.

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.