Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-VFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6246ucy |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |       | 10.3.7                | Reset pin characteristics                  |

|----|-------|-----------------------|--------------------------------------------|

|    |       | 10.3.8                | TIM 1, 2, 3, and 4 timer specifications    |

|    |       | 10.3.9                | SPI serial peripheral interface69          |

|    |       | 10.3.10               | I <sup>2</sup> C interface characteristics |

|    |       | 10.3.11               | 10-bit ADC characteristics                 |

|    |       | 10.3.12               | EMC characteristics                        |

| 11 | Pack  | age info              | ormation                                   |

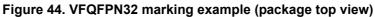

|    | 11.1  | VFQFP                 | N32 package information 78                 |

|    | 11.2  | LQFP4                 | 8 package information                      |

|    | 11.3  | LQFP3                 | 2 package information                      |

|    | 11.4  | Therma                | Il characteristics                         |

|    |       | 11.4.1                | Reference document88                       |

|    |       | 11.4.2                | Selecting the product temperature range    |

| 12 | Orde  | ring info             | ormation                                   |

| 13 | STM   | 8 develo              | pment tools                                |

|    | 13.1  | Emulati               | on and in-circuit debugging tools          |

|    |       | 13.1.1                | STice key features                         |

|    | 13.2  | Softwar               | re tools                                   |

|    |       | 13.2.1                | STM8 toolset                               |

|    |       | 13.2.2                | C and assembly toolchains92                |

|    | 13.3  | Prograr               | nming tools                                |

| 14 | Revis | sion his <sup>.</sup> | tory                                       |

|    |       |                       | -                                          |

# 5 **Product overview**

This section describes the family features that are implemented in the products covered by this datasheet.

For more detailed information on each feature please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

# 5.1 STM8A central processing unit (CPU)

The 8-bit STM8A core is a modern CISC core and has been designed for code efficiency and performance. It contains 21 internal registers (six directly addressable in each execution context), 20 addressing modes including indexed indirect and relative addressing and 80 instructions.

# 5.1.1 Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus with single cycle fetching for most instructions

- X and Y 16-bit index registers, enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter with 16-Mbyte linear memory space

- 16-bit stack pointer with access to a 64 Kbyte stack

- 8-bit condition code register with seven condition flags for the result of the last instruction.

# 5.1.2 Addressing

- 20 addressing modes

- Indexed indirect addressing mode for look-up tables located anywhere in the address space

- Stack pointer relative addressing mode for efficient implementation of local variables and parameter passing

#### 5.1.3 Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

## 5.4.2 Write protection (WP)

Write protection in application mode is intended to avoid unintentional overwriting of the memory. The write protection can be removed temporarily by executing a specific sequence in the user software.

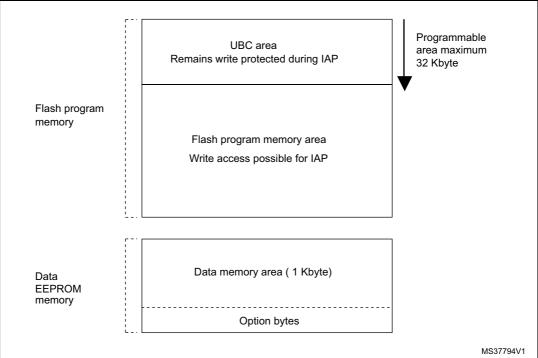

## 5.4.3 Protection of user boot code (UBC)

If the user chooses to update the Flash program memory using a specific boot code to perform in application programming (IAP), this boot code needs to be protected against unwanted modification.

In the STM8A a memory area of up to 32 Kbyte can be protected from overwriting at user option level. Other than the standard write protection, the UBC protection can exclusively be modified via the debug interface, the user software cannot modify the UBC protection status.

The UBC memory area contains the reset and interrupt vectors and its size can be adjusted in increments of 512 bytes by programming the UBC and NUBC option bytes (see Section 9: Option bytes on page 44).

Figure 2. Flash memory organization of STM8AF6246/48/66/68

| Pi<br>num |               |                          |      |          | Inpu | t              |           | Out   | put              |    |                                |                               |                                                      |

|-----------|---------------|--------------------------|------|----------|------|----------------|-----------|-------|------------------|----|--------------------------------|-------------------------------|------------------------------------------------------|

| LQFP48    | VFQFPN/LQFP32 | Pin name                 | Type | floating | ndw  | Ext. interrupt | High sink | Speed | OD               | ЪР | Main function<br>(after reset) | Default alternate<br>function | Alternate<br>function after<br>remap<br>[option bit] |

| 24        |               | PE6/AIN9                 | I/O  | Х        | Х    | Х              | -         | 01    | Х                | Х  | Port E7                        | Analog input 9                | -                                                    |

| 25        | 17            | PE5/SPI_NSS              | I/O  | Х        | Х    | Х              | -         | 01    | Х                | Х  | Port E5                        | SPI master/slave select       | -                                                    |

| 26        | 18            | PC1/TIM1_CH1             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C1                        | Timer 1 - channel 1           | -                                                    |

| 27        | 19            | PC2/TIM1_CH2             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C2                        | Timer 1- channel 2            | -                                                    |

| 28        | 20            | PC3/TIM1_CH3             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C3                        | Timer 1 - channel 3           | -                                                    |

| 29        | 21            | PC4/TIM1_CH4             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C4                        | Timer 1 - channel 4           | -                                                    |

| 30        | 22            | PC5/SPI_SCK              | I/O  | Х        | Х    | Х              |           | O3    | Х                | Х  | Port C5                        | SPI clock                     | -                                                    |

| 31        | -             | V <sub>SSIO_2</sub>      | S    | -        | -    | -              | -         | -     | -                | -  | I/O groun                      | d                             | -                                                    |

| 32        | -             | V <sub>DDIO_2</sub>      | S    | -        | -    | -              | -         | -     | -                | -  | I/O power                      | supply                        | -                                                    |

| 33        | 23            | PC6/SPI_MOSI             | I/O  | x        | х    | х              | -         | O3    | х                | х  | Port C6                        | SPI master out/<br>slave in   | -                                                    |

| 34        | 24            | PC7/SPI_MISO             | I/O  | Х        | Х    | Х              | -         | O3    | Х                | Х  | Port C7                        | SPI master in/ slave out      | -                                                    |

| 35        | -             | PG0                      | I/O  | Х        | Х    | -              | -         | 01    | Х                | Х  | Port G0                        | -                             | -                                                    |

| 36        | -             | PG1                      | I/O  | Х        | Х    | -              | -         | 01    | Х                | Х  | Port G1                        | -                             | -                                                    |

| 37        | -             | PE3/TIM1_BKIN            | I/O  | Х        | Х    | Х              | -         | 01    | Х                | Х  | Port E3                        | Timer 1 - break input         | -                                                    |

| 38        | -             | PE2/I <sup>2</sup> C_SDA | I/O  | Χ        | -    | Х              | -         | 01    | T <sup>(6)</sup> | -  | Port E2                        | I <sup>2</sup> C data         | -                                                    |

| 39        | -             | PE1/I <sup>2</sup> C_SCL | I/O  | Χ        | -    | Х              | -         | 01    | T <sup>(6)</sup> | -  | Port E1                        | I <sup>2</sup> C clock        | -                                                    |

| 40        | -             | PE0/CLK_CCO              | I/O  | x        | х    | х              | -         | O3    | х                | х  | Port E0                        | Configurable clock<br>output  | -                                                    |

| 41        | 25            | PD0/TIM3_CH2             | I/O  | x        | x    | х              | HS        | O3    | x                | х  | Port D0                        | Timer 3 - channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 42        | 26            | PD1/SWIM <sup>(7)</sup>  | I/O  | Х        | X    | Х              | HS        | O4    | Х                | Х  | Port D1                        | SWIM data interface           | -                                                    |

| 43        | 27            | PD2/TIM3_CH1             | I/O  | x        | х    | х              | HS        | O3    | х                | х  | Port D2                        | Timer 3 - channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 44        | 28            | PD3/TIM2_CH2             | I/O  | x        | х    | х              | HS        | O3    | х                | х  | Port D3                        | Timer 2 - channel 2           | ADC_ETR<br>[AFR0]                                    |

| 45        | 29            | PD4/TIM2_CH1/<br>BEEP    | I/O  | x        | х    | х              | HS        | O3    | х                | х  | Port D4                        | Timer 2 - channel 1           | BEEP output<br>[AFR7]                                |

| 46        | 30            | PD5/<br>LINUART_TX       | I/O  | x        | х    | Х              | -         | 01    | х                | х  | Port D5                        | LINUART data transmit         | -                                                    |

| Table 8. STM8AF6246/48/66/68 (32 Kbyte) microcontroller pin description <sup>(1)(2)</sup> (conti |

|--------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|

|           |            |                | raware register map (continued)   |                     |

|-----------|------------|----------------|-----------------------------------|---------------------|

| Address   | Block      | Register label | Register label Register name      |                     |

| 0x00 5014 |            | PE_ODR         |                                   |                     |

| 0x00 5015 |            | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016 | Port E     | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017 | ) 5017 PE_ |                | Port E control register 1         | 0x00                |

| 0x00 5018 |            | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019 |            | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A |            | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B | Port F     | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C |            | PF_CR1         | Port F control register 1         | 0x00                |

| 0x00 501D |            | PF_CR2         | Port F control register 2         | 0x00                |

| 0x00 501E |            | PG_ODR         | Port G data output latch register | 0x00                |

| 0x00 501F |            | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5020 | Port G     | PG_DDR         | Port G data direction register    | 0x00                |

| 0x00 5021 |            | PG_CR1         | Port G control register 1         | 0x00                |

| 0x00 5022 |            | PG_CR2         | Port G control register 2         | 0x00                |

| Table 10. I/O port hardware register map (continued) |

|------------------------------------------------------|

|------------------------------------------------------|

1. Depends on the external circuitry.

| Address                   | Block | Register label Register name                                                                       |                                                  | Reset<br>status |  |  |

|---------------------------|-------|----------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|--|--|

| 0x00 505A                 |       | FLASH_CR1                                                                                          | Flash control register 1                         | 0x00            |  |  |

| 0x00 505B                 |       | FLASH_CR2                                                                                          | Flash control register 2                         | 0x00            |  |  |

| 0x00 505C                 |       | FLASH_NCR2                                                                                         | Flash complementary control register 2           | 0xFF            |  |  |

| 0x00 505D                 | Flash | FLASH_FPR                                                                                          | Flash protection register                        | 0x00            |  |  |

| 0x00 505E                 |       | FLASH_NFPR                                                                                         | Flash complementary protection register          | 0xFF            |  |  |

| 0x00 505F                 |       | FLASH_IAPSR                                                                                        | Flash in-application programming status register | 0x40            |  |  |

| 0x00 5060 to<br>0x00 5061 |       | Reserved area (2 bytes)                                                                            |                                                  |                 |  |  |

| 0x00 5062                 | Flash | FLASH_PUKR                                                                                         | Flash Program memory unprotection register       | 0x00            |  |  |

| 0x00 5063                 |       | Reserved area (1 byte)                                                                             |                                                  |                 |  |  |

| 0x00 5064                 | Flash | lash FLASH_DUKR Data EEPROM unprotection register                                                  |                                                  |                 |  |  |

| 0x00 5065 to<br>0x00 509F |       | Flash     FLASH_DUKR     Data EEPROM unprotection register     0x00       Reserved area (59 bytes) |                                                  |                 |  |  |

#### Table 11. General hardware register map

| A al al c                  | Option                | Option   |   |                         | - | Optio    | on bits | - |  |               | Factory            |

|----------------------------|-----------------------|----------|---|-------------------------|---|----------|---------|---|--|---------------|--------------------|

| Addr.                      | name                  | byte no. | 7 |                         |   |          |         |   |  |               | default<br>setting |

| 0x00<br>480B               | TMU                   | OPT6     |   | TMU[3:0]                |   |          |         |   |  | 0x00          |                    |

| 0x00<br>480C               | TMO                   | NOPT6    |   |                         |   | NTM      | 1U[3:0] |   |  |               | 0xFF               |

| 0x00<br>480D               | Flash wait            | OPT7     |   |                         |   | Reserve  | d       |   |  | WAIT<br>STATE | 0x00               |

| 0x00<br>480E               | states                | NOPT7    |   | Reserved NWAIT<br>STATE |   |          |         |   |  | 0xFF          |                    |

| 0x00<br>480F               |                       |          |   |                         |   | Reserved |         |   |  |               |                    |

| 0x00<br>4810               |                       | OPT8     |   | TMU_KEY 1 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4811               |                       | OPT9     |   | TMU_KEY 2 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4812               |                       | OPT10    |   | TMU_KEY 3 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4813               |                       | OPT11    |   | TMU_KEY 4 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4814               | TMU                   | OPT12    |   | TMU_KEY 5 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4815               |                       | OPT13    |   | TMU_KEY 6 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4816               |                       | OPT14    |   | TMU_KEY 7 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4817               |                       | OPT15    |   | TMU_KEY 8 [7:0]         |   |          |         |   |  | 0x00          |                    |

| 0x00<br>4818               |                       | OPT16    |   | TMU_MAXATT [7:0]        |   |          |         |   |  | 0xC7          |                    |

| 0x00<br>4819<br>to<br>487D |                       | ·        |   |                         |   | Reserved |         |   |  |               |                    |

| 0x00<br>487E               | Boot-                 | OPT17    |   |                         |   | BL       | [7:0]   |   |  |               | 0x00               |

| 0x00<br>487F               | loader <sup>(1)</sup> | NOPT17   |   |                         |   | NB       | L[7:0]  |   |  |               | 0xFF               |

Table 15. Option bytes (continued)

1. This option consists of two bytes that must have a complementary value in order to be valid. If the option is invalid, it has no effect on EMC reset.

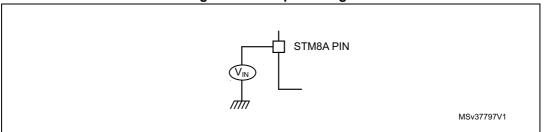

### 10.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 7.

#### Figure 7. Pin input voltage

# 10.2 Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                           | Min                                                              | Мах                   | Unit |  |

|------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|-----------------------|------|--|

| V <sub>DDx</sub> - V <sub>SS</sub> | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                                                             | 6.5                   | V    |  |

| V                                  | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3                                            | 6.5                   | V    |  |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3                                            | V <sub>DD</sub> + 0.3 | v    |  |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           | -                                                                | 50                    | mV   |  |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins                  | -                                                                | 50                    | IIIV |  |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   | see Absolute maximum ra<br>(electrical sensitivity) o<br>page 76 |                       | •    |  |

Table 17. Voltage characteristics

1. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

| Symbol                               | Ratings                                                                   | Max. | Unit |

|--------------------------------------|---------------------------------------------------------------------------|------|------|

| I <sub>VDDIO</sub>                   | Total current into $V_{DDIO}$ power lines (source) <sup>(1)(2)(3)</sup>   | 100  |      |

| I <sub>VSSIO</sub>                   | Total current out of $V_{SS IO}$ ground lines (sink) <sup>(1)(2)(3)</sup> | 100  |      |

| 1.                                   | Output current sunk by any I/O and control pin                            | 20   | mA   |

| IIO                                  | Output current source by any I/Os and control pin                         | -20  | IIIA |

| I <sub>INJ(PIN)</sub> <sup>(4)</sup> | Injected current on any pin                                               | ±10  |      |

| I <sub>INJ(TOT)</sub>                | Sum of injected currents                                                  | 50   |      |

#### Table 18. Current characteristics

1. All power (V\_{DD}, V\_{DDIO}, V\_{DDA}) and ground (V\_{SS}, V\_{SSIO}, V\_{SSA}) pins must always be connected to the external supply.

- 2. The total limit applies to the sum of operation and injected currents.

- 3.  $V_{\text{DDIO}}$  includes the sum of the positive injection currents.  $V_{\text{SSIO}}$  includes the sum of the negative injection currents.

- 4. This condition is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current allowed and the corresponding V<sub>IN</sub> maximum must always be respected.

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| TJ               | Maximum junction temperature | 160        | 0    |

#### Table 20. Operating lifetime<sup>(1)</sup>

| Symbol | Ratings                      | Value         | Unit    |

|--------|------------------------------|---------------|---------|

| OLF    | Conforming to AEC-Q100 rev G | -40 to 125 °C | Grade 1 |

|        |                              | -40 to 150 °C | Grade 0 |

1. For detailed mission profile analysis, please contact the nearest local ST Sales Office.

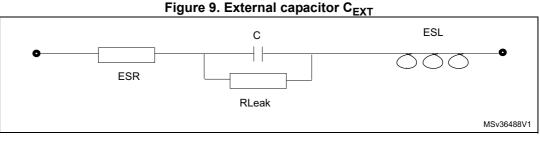

# 10.3.1 VCAP external capacitor

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 21*. Care should be taken to limit the series inductance to less than 15 nH.

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

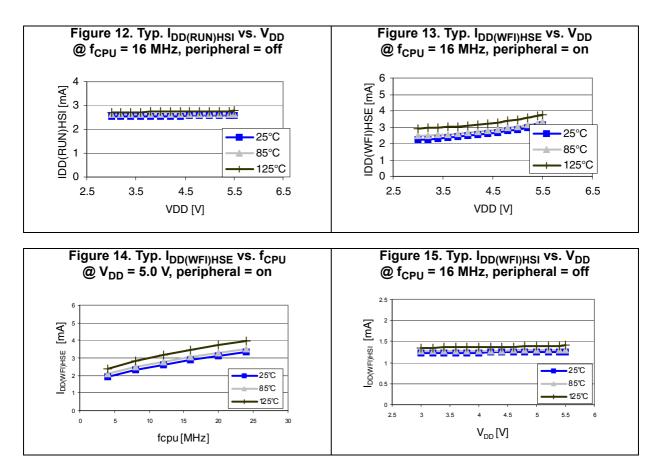

# 10.3.2 Supply current characteristics

The current consumption is measured as described in *Figure 6 on page 49* and *Figure 7 on page 50*.

If not explicitly stated, general conditions of temperature and voltage apply.

| General conditions for $v_{DD}$ apply, $I_A = -40$ to 150 °C |                                                           |                                                                                                |                                                 |      |                     |    |  |

|--------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------|------|---------------------|----|--|

| Symbol                                                       | Parameter                                                 | Condi                                                                                          | Тур                                             | Max  | Unit                |    |  |

|                                                              |                                                           | All peripherals                                                                                | f <sub>CPU</sub> = 16 MHz                       | 7.4  | 14                  |    |  |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>                          | Supply current in                                         | clocked, code<br>executed from Flash                                                           | f <sub>CPU</sub> = 8 MHz                        | 4.0  | 7.4 <sup>(2)</sup>  |    |  |

| 'DD(RUN)`                                                    | Run mode                                                  | program memory,<br>HSE external clock                                                          | f <sub>CPU</sub> = 4 MHz                        | 2.4  | 4.1 <sup>(2)</sup>  |    |  |

|                                                              |                                                           | (without resonator)                                                                            | f <sub>CPU</sub> = 2 MHz                        | 1.5  | 2.5                 |    |  |

|                                                              |                                                           | All peripherals                                                                                | f <sub>CPU</sub> = 16 MHz                       | 3.7  | 5.0                 |    |  |

| (1)                                                          | Supply<br>current in<br>Run mode                          | clocked, code<br>executed from RAM<br>and EEPROM, HSE<br>external clock<br>(without resonator) | f <sub>CPU</sub> = 8 MHz                        | 2.2  | 3.0 <sup>(2)</sup>  |    |  |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>                          |                                                           |                                                                                                | f <sub>CPU</sub> = 4 MHz                        | 1.4  | 2.0 <sup>(2)</sup>  |    |  |

|                                                              |                                                           |                                                                                                | f <sub>CPU</sub> = 2 MHz                        | 1.0  | 1.5                 | mA |  |

|                                                              | Supply<br>current in<br>Wait mode                         | nt in peripherals off, HSE                                                                     | f <sub>CPU</sub> = 16 MHz                       | 1.65 | 2.5                 |    |  |

| I <sub>DD(WFI)</sub> <sup>(1)</sup>                          |                                                           |                                                                                                | f <sub>CPU</sub> = 8 MHz                        | 1.15 | 1.9 <sup>(2)</sup>  |    |  |

| 'DD(WFI)`´                                                   |                                                           |                                                                                                | f <sub>CPU</sub> = 4 MHz                        | 0.90 | 1.6 <sup>(2)</sup>  |    |  |

|                                                              |                                                           |                                                                                                | f <sub>CPU</sub> = 2 MHz                        | 0.80 | 1.5                 |    |  |

| (1)                                                          | Supply f <sub>CPU</sub> scaled down, all peripherals off, |                                                                                                | Ext. clock 16 MHz<br>f <sub>CPU</sub> = 125 kHz | 1.50 | 1.95                |    |  |

| I <sub>DD(SLOW)</sub> <sup>(1)</sup>                         | current in<br>Slow mode                                   | code executed from RAM                                                                         | LSI internal RC<br>f <sub>CPU</sub> = 128 kHz   | 1.50 | 1.80 <sup>(2)</sup> |    |  |

Table 23. Total current consumption in Run, Wait and Slow mode. General conditions for  $V_{DD}$  apply,  $T_A = -40$  to 150 °C

1. The current due to I/O utilization is not taken into account in these values.

2. Values not tested in production. Design guidelines only.

# 10.3.3 External clock sources and timing characteristics

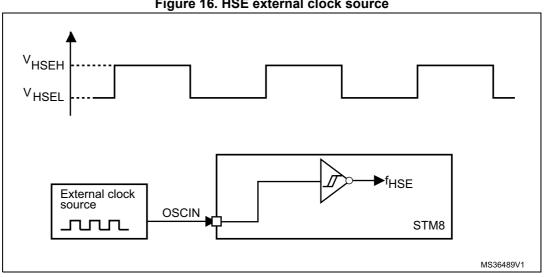

#### HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                               | Conditions                         | Min                   | Тур | Max                   | Unit |  |

|-----------------------|-----------------------------------------|------------------------------------|-----------------------|-----|-----------------------|------|--|

| f <sub>HSE_ext</sub>  | User external clock source<br>frequency | T <sub>A</sub> is -40 to<br>150 °C | 0 <sup>(1)</sup>      | -   | 16                    | MHz  |  |

| $V_{HSEdHL}$          | Comparator hysteresis                   | -                                  | $0.1 \times V_{DD}$   | -   | -                     |      |  |

| V <sub>HSEH</sub>     | OSCIN input pin high level voltage      | -                                  | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |  |

| V <sub>HSEL</sub>     | OSCIN input pin low level voltage       | -                                  | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> |      |  |

| I <sub>LEAK_HSE</sub> | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$         | -1                    | -   | +1                    | μA   |  |

Table 28. HSE user external clock characteristics

1. In CSS is used, the external clock must have a frequency above 500 kHz.

Figure 16. HSE external clock source

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied using a crystal/ceramic resonator oscillator of up to 16 MHz. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Table 29. HSE oscillator | characteristics |

|--------------------------|-----------------|

|--------------------------|-----------------|

| Symbol                              | Parameter                    | Conditions                       | Min | Тур | Мах | Unit |

|-------------------------------------|------------------------------|----------------------------------|-----|-----|-----|------|

| R <sub>F</sub>                      | Feedback resistor            | -                                | -   | 220 | -   | kΩ   |

| $C_{L1}/C_{L2}^{(1)}$               | Recommended load capacitance | -                                | -   | -   | 20  | pF   |

| 9 <sub>m</sub>                      | Oscillator transconductance  | -                                | 5   | -   | -   | mA/V |

| t <sub>SU(HSE)</sub> <sup>(2)</sup> | Startup time                 | V <sub>DD</sub> is<br>stabilized | -   | 2.8 | -   | ms   |

1. The oscillator needs two load capacitors,  $C_{L1}$  and  $C_{L2}$ , to act as load for the crystal. The total load capacitance ( $C_{load}$ ) is  $(C_{L1} * C_{L2})/(C_{L1} + C_{L2})$ . If  $C_{L1} = C_{L2}$ ,  $C_{load} = C_{L1} / 2$ . Some oscillators have built-in load capacitors,  $C_{L1}$  and  $C_{L2}$ .

2. This value is the startup time, measured from the moment it is enabled (by software) until a stabilized 16 MHz oscillation is reached. It can vary with the crystal type that is used.

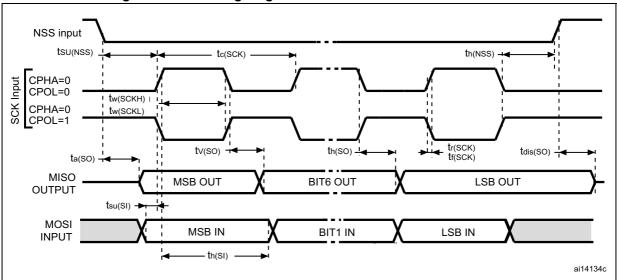

#### **Electrical characteristics**

- 3. Values based on design simulation and/or characterization results, and not tested in production.

- 4. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

- 5. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

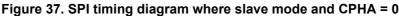

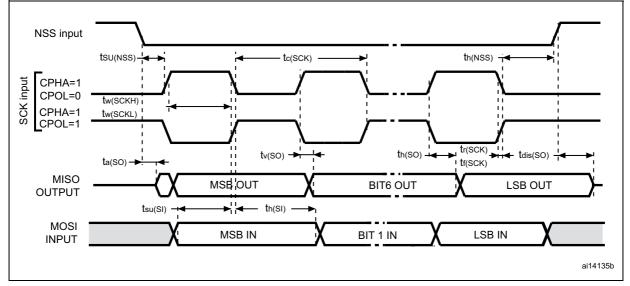

#### Figure 38. SPI timing diagram where slave mode and CPHA = 1

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

# 10.3.10 I<sup>2</sup>C interface characteristics

| Symbol                                     | Parameter                                                                                                                        | Standard           | mode I <sup>2</sup> C | Fast mod                            | Unit               |      |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-------------------------------------|--------------------|------|--|

| Symbol                                     | Falameter                                                                                                                        | Min <sup>(2)</sup> | Max <sup>(2)</sup>    | Min <sup>(2)</sup>                  | Max <sup>(2)</sup> | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                                                                               | 4.7                | -                     | 1.3                                 | -                  | 110  |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                                                                              | 4.0                | -                     | 0.6                                 | -                  | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                                                                                   | 250                | -                     | 100                                 | -                  |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                                                                               | 0 <sup>(3)</sup>   | -                     | 0 <sup>(4)</sup> 900 <sup>(3)</sup> |                    |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time         -         1000         -           (V <sub>DD</sub> = 3 to 5.5 V)         -         1000         - |                    | 300                   | ns                                  |                    |      |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time<br>(V <sub>DD</sub> = 3 to 5.5 V)                                                                          | -                  | 300                   | -                                   | 300                | 300  |  |

| t <sub>h(STA)</sub>                        | START condition hold time                                                                                                        | 4.0                | -                     | 0.6                                 | -                  |      |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time                                                                                              | 4.7                | -                     | 0.6                                 | -                  |      |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time                                                                                                        | 4.0                | -                     | 0.6                                 | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free)                                                                                          | 4.7                | -                     | 1.3                                 | -                  |      |  |

| Cb                                         | Capacitive load for each bus line                                                                                                | -                  | 400                   | -                                   | 400                | pF   |  |

# Table 39. I<sup>2</sup>C characteristics

1.  $f_{MASTER}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz)

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

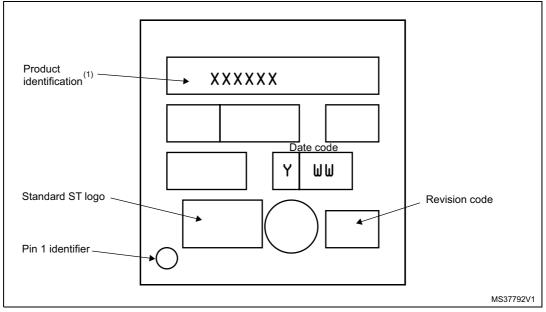

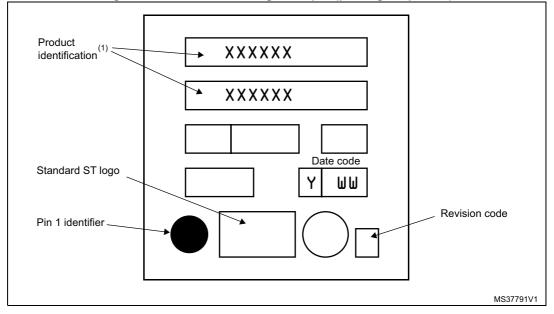

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

# 11.2 LQFP48 package information

SEATING PLANE A2 ŨŦŨŦŨŦŨŦĬĦŮ<del>Ÿ</del>ŨŦŨŦŨŦŨŦŎŹ F 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 24 37 Œ b Œ <u>ш</u> ш Ē ----------£ 48 13 12 e 5B\_ME\_V2

Figure 45. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

# Figure 46. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 47. LQFP48 marking example (package top view)

# **12** Ordering information

| Example:                                | STM8A | F | 62 | 6 | 6 | Т | т | D | xxx <sup>(3)</sup> | ١ |

|-----------------------------------------|-------|---|----|---|---|---|---|---|--------------------|---|

| Product class                           |       |   | Ī  |   |   |   |   |   |                    | 1 |

| 8-bit automotive microcontroller        |       |   |    |   |   |   |   |   |                    |   |

|                                         |       |   |    |   |   |   |   |   |                    |   |

| Program memory type                     |       |   |    |   |   |   |   |   |                    |   |

| F = Flash + EEPROM                      |       |   |    |   |   |   |   |   |                    |   |

| P = FASTROM                             |       |   |    |   |   |   |   |   |                    |   |

| Device family                           |       |   |    |   |   |   |   |   |                    |   |

| 62 = Silicon rev X and rev W, LIN only  |       |   |    |   |   |   |   |   |                    |   |

|                                         |       |   |    |   |   |   |   |   |                    |   |

| Program memory size<br>4 = 16 Kbyte     |       |   |    |   |   |   |   |   |                    |   |

| 4 = 16 Kbyte<br>6 = 32 Kbyte            |       |   |    |   |   |   |   |   |                    |   |

| 0 – 52 Kbyle                            |       |   |    |   |   |   |   |   |                    |   |

| Pin count                               |       |   |    |   |   |   |   |   |                    |   |

| 6 = 32 pins                             |       |   |    |   |   |   |   |   |                    |   |

| 8 = 48 pins                             |       |   |    |   |   |   |   |   |                    |   |

| HSI accuracy                            |       |   |    |   |   |   |   |   |                    |   |

| Blank = ± 5 %                           |       |   |    |   |   |   |   |   |                    |   |

| I = ± 2.5 %                             |       |   |    |   |   |   |   |   |                    |   |

| Package type                            |       |   |    |   |   |   |   |   |                    |   |

| T = LQFP                                |       |   |    |   |   |   |   |   |                    |   |

| U = VFQFPN                              |       |   |    |   |   |   |   |   |                    |   |

| Temperature range                       |       |   |    |   |   |   |   |   |                    |   |

| A = -40 to 85 °C                        |       |   |    |   |   |   |   | _ |                    |   |

| C = -40 to 125 °C                       |       |   |    |   |   |   |   |   |                    |   |

| D = -40 to 150 °C                       |       |   |    |   |   |   |   |   |                    |   |

| Packing                                 |       |   |    |   |   |   |   |   |                    |   |

| Y = Tray                                |       |   |    |   |   |   |   |   |                    |   |

| U = Tube                                |       |   |    |   |   |   |   |   |                    |   |

| X = Tape and reel compliant with EIA 48 | 1-C   |   |    |   |   |   |   |   |                    |   |

#### Figure 51. STM8AF6246/48/66/68 ordering information scheme<sup>(1) (2)</sup>

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to <u>www.st.com</u> or contact the nearest ST Sales Office.

- 2. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

- Customer specific FASTROM code or custom device configuration. This field shows 'SSS' if the device contains a super set silicon, usually equipped with bigger memory and more I/Os. This silicon is supposed to be replaced later by the target silicon.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Jan-2011 | 5        | <ul> <li>Modified references to reference manual, and Flash programming manual in the whole document.</li> <li>Added reference to AEC Q100 standard on cover page.</li> <li>Renamed timer types as follows: <ul> <li>Auto-reload timer to general purpose timer</li> <li>Multipurpose timer to advanced control timer</li> <li>System timer to basic timer</li> </ul> </li> <li>Introduced concept of medium density Flash program memory. Updated timer names in <i>Figure: STM8A block diagram</i>.</li> <li>Added TMU brief description in <i>Section: Flash program and data EEPROM</i>, and updated TMU_MAXATT description in <i>Table: Option byte description</i>.</li> <li>Updated clock sources in clock controller features. Changed 16MHZTRIM0 to HSITRIM bit in <i>Section: User trimming</i>.</li> <li>Added Table: Peripheral clock gating bits.</li> <li>Updated Section: Low-power operating modes.</li> <li>Added Table: ADC naming and Table: Communication peripheral naming correspondence.</li> <li>Added Note 1 related AIN12 pin in Section: Analog-to-digital converter (ADC) and Table: STM8AF61xx/62xx (32 Kbyte) microcontroller pin description.</li> <li>Updated SPI data rate to 10 Mbit/s or f<sub>MASTER</sub>/2 in Section: Serial peripheral interface (SPI).</li> <li>Added reset state in Table: Legend/abbreviation.</li> <li>Table: STM8AF61xx/62xx (32 Kbyte) microcontroller pin description: added Note 7 related to PD1/SWIM, modified Note 6, corrected wpu input for PE1 and PE2, and renamed TIMn_CCx and TIMn_NCCx to TIMn_CHx and TIMn_CHxN, respectively.</li> <li>Section: Register map:</li> <li>Replaced tables describing register maps and reset values for nonvolatile memory, global configuration, reset status, clock controller, interrupt controller, timers, communication interfaces, and ADC, by Table: General hardware register map.</li> </ul> |

Table 50. Document revision history (continued)

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Jul-2012 | 6<br>(continued) | <ul> <li>Section: Reset pin characteristics: updated text below Figure: Typical NRST pull-up current Ipu vs VDD.</li> <li>Figure: Recommended reset pin protection: updated unit of capacitor.</li> <li>Table: SPI characteristics: updated SCK high and low time conditions and values.</li> <li>Figure: SPI timing diagram - master mode: replaced 'SCK input' signals with 'SCK output' signals.</li> <li>Updated Table: VFQFPN 32-lead very thin fine pitch quad flat no-lead package mechanical data, Table: LQFP 48-pin low profile quad flat package mechanical data.</li> <li>Replaced Figure: LQFP 48-pin low profile quad flat package (7 x 7) and Figure: LQFP 32-pin low profile quad flat package (7 x 7).</li> <li>Added Figure: LQFP 48-pin recommended footprint and Figure: LQFP 32-pin recommended footprint.</li> <li>Figure: Ordering information scheme(1): added footnote 1, added "xxx" and footnote 2, updated example and device family; added FASTROM.</li> <li>Section: C and assembly toolchains: added www.iar.com</li> </ul> |

| 04-Apr-2014 | 7                | <ul> <li>Updated:</li> <li>Table: Device summary,</li> <li>Table: STM8AF62xx product line-up,</li> <li>Table: STM8AF/H61xx product line-up.</li> <li>SPI description in Features.</li> <li>The typical and maximum values for t<sub>TEMP</sub> reset release delay in <i>Table: Operating conditions at power-up/power-down.</i></li> <li>The symbol for NRST Input not filtered pulse duration in <i>Table: NRST pin characteristics</i></li> <li>The address and comment of Reset interrupt in <i>Table: STM8A interrupt table.</i></li> <li>Added the three footnotes to <i>Figure VFQFPN 32-lead very thin fine pitch quad flat no-lead package (5 x 5).</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

| 24-Jun-2014 | 8                | Updated <i>Table: HSI oscillator characteristics.</i><br>Added HSI accuracy and removed temperature range B in <i>Figure:</i><br><i>Ordering information scheme(1).</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12-Nov-2014 | 9                | Updates in <i>Table: HSI oscillator characteristics</i> (HSI oscillator accuracy (factory calibrated) values) and <i>Figure: Ordering information scheme(1)</i> (changed the value for I).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 50. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved