Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusNot For New DesignsCore ProcessorSTM8ACore Size8-BitSpeed16MHzConnectivityIPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O25Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Core Size8-BitSpeed16MHzConnectivityI²C, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O25Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                     |  |

| Speed16MHzConnectivityI²C, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O25Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                   |  |

| ConnectivityIPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O25Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                             |  |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O25Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                                                                     |  |

| Number of I/O25Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                                                                                                                     |  |

| Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                                                                                                                                    |  |

| Program Memory TypeFLASHEEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                                                                                                                                                                     |  |

| EEPROM Size1K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                                                                                                                                                                                             |  |

| RAM Size2K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                                                                                                                                                                                                              |  |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 7x10b                                                                                                                                                                                                                                                                            |  |

| Data Converters A/D 7x10b                                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                        |  |

| Oscillator Type Internal                                                                                                                                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                        |  |

| Operating Temperature -40°C ~ 125°C (TA)                                                                                                                                                                                                                                                                                               |  |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                            |  |

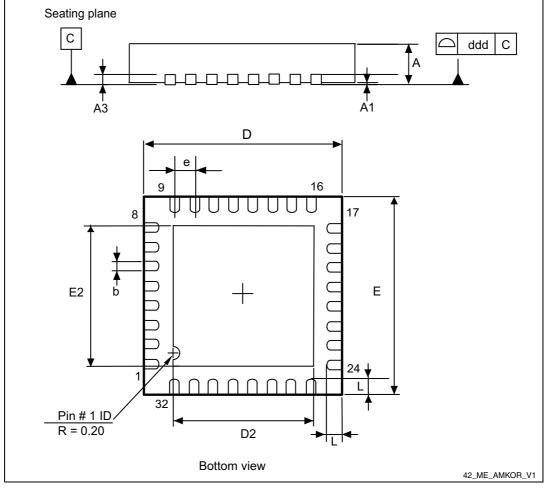

| Package / Case 32-LQFP                                                                                                                                                                                                                                                                                                                 |  |

| Supplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                                                                                   |  |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6266tcx                                                                                                                                                                                                                                                     |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |       | 10.3.7                | Reset pin characteristics                  |

|----|-------|-----------------------|--------------------------------------------|

|    |       | 10.3.8                | TIM 1, 2, 3, and 4 timer specifications    |

|    |       | 10.3.9                | SPI serial peripheral interface69          |

|    |       | 10.3.10               | I <sup>2</sup> C interface characteristics |

|    |       | 10.3.11               | 10-bit ADC characteristics                 |

|    |       | 10.3.12               | EMC characteristics                        |

| 11 | Pack  | age info              | ormation                                   |

|    | 11.1  | VFQFP                 | N32 package information 78                 |

|    | 11.2  | LQFP4                 | 8 package information                      |

|    | 11.3  | LQFP3                 | 2 package information                      |

|    | 11.4  | Therma                | Il characteristics                         |

|    |       | 11.4.1                | Reference document88                       |

|    |       | 11.4.2                | Selecting the product temperature range    |

| 12 | Orde  | ring info             | ormation                                   |

| 13 | STM   | 8 develo              | pment tools                                |

|    | 13.1  | Emulati               | on and in-circuit debugging tools          |

|    |       | 13.1.1                | STice key features                         |

|    | 13.2  | Softwar               | re tools                                   |

|    |       | 13.2.1                | STM8 toolset                               |

|    |       | 13.2.2                | C and assembly toolchains92                |

|    | 13.3  | Prograr               | nming tools                                |

| 14 | Revis | sion his <sup>.</sup> | tory                                       |

|    |       |                       | -                                          |

### 5.4.2 Write protection (WP)

Write protection in application mode is intended to avoid unintentional overwriting of the memory. The write protection can be removed temporarily by executing a specific sequence in the user software.

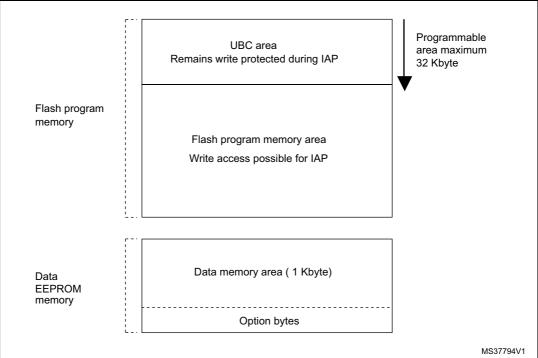

### 5.4.3 Protection of user boot code (UBC)

If the user chooses to update the Flash program memory using a specific boot code to perform in application programming (IAP), this boot code needs to be protected against unwanted modification.

In the STM8A a memory area of up to 32 Kbyte can be protected from overwriting at user option level. Other than the standard write protection, the UBC protection can exclusively be modified via the debug interface, the user software cannot modify the UBC protection status.

The UBC memory area contains the reset and interrupt vectors and its size can be adjusted in increments of 512 bytes by programming the UBC and NUBC option bytes (see Section 9: Option bytes on page 44).

Figure 2. Flash memory organization of STM8AF6246/48/66/68

## 5.5.2 16 MHz high-speed internal RC oscillator (HSI)

- Default clock after reset 2 MHz (16 MHz/8)

- Fast wakeup time

### **User trimming**

The register CLK\_HSITRIMR with three trimming bits plus one additional bit for the sign permits frequency tuning by the application program. The adjustment range covers all possible frequency variations versus supply voltage and temperature. This trimming does not change the initial production setting.

For reason of compatibility with other devices from the STM8A family, a special mode with only two trimming bits plus sign can be selected. This selection is controlled with the HSITRIM0 bit in the option byte registers OPT3 and NOPT3.

### UART mode

- Full duplex, asynchronous communications NRZ standard format (mark/space)

- High-precision baud rate generator

- A common programmable transmit and receive baud rates up to f<sub>MASTER</sub>/16

- Programmable data word length (8 or 9 bits) 1 or 2 stop bits parity control

- Separate enable bits for transmitter and receiver

- Error detection flags

- Reduced power consumption mode

- Multi-processor communication enter mute mode if address match does not occur

- Wakeup from mute mode (by idle line detection or address mark detection)

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line

## 5.10 Input/output specifications

The product features four different I/O types:

- Standard I/O 2 MHz

- Fast I/O up to 10 MHz

- High sink 8 mA, 2 MHz

- True open drain (I<sup>2</sup>C interface)

To decrease EMI (electromagnetic interference), high sink I/Os have a limited maximum slew rate. The rise and fall times are similar to those of standard I/Os.

The analog inputs are equipped with a low leakage analog switch. Additionally, the schmitttrigger input stage on the analog I/Os can be disabled in order to reduce the device standby consumption.

STM8A I/Os are designed to withstand current injection. For a negative injection current of 4 mA, the resulting leakage current in the adjacent input does not exceed 1  $\mu$ A. Thanks to this feature, external protection diodes against current injection are no longer required.

| Pi<br>num |               |                          |      |          | Inpu | t              |           | Out   | put              |    |                                |                               |                                                      |

|-----------|---------------|--------------------------|------|----------|------|----------------|-----------|-------|------------------|----|--------------------------------|-------------------------------|------------------------------------------------------|

| LQFP48    | VFQFPN/LQFP32 | Pin name                 | Type | floating | ndw  | Ext. interrupt | High sink | Speed | OD               | ЪР | Main function<br>(after reset) | Default alternate<br>function | Alternate<br>function after<br>remap<br>[option bit] |

| 24        |               | PE6/AIN9                 | I/O  | Х        | Х    | Х              | -         | 01    | Х                | Х  | Port E7                        | Analog input 9                | -                                                    |

| 25        | 17            | PE5/SPI_NSS              | I/O  | Х        | Х    | Х              | -         | 01    | Х                | Х  | Port E5                        | SPI master/slave select       | -                                                    |

| 26        | 18            | PC1/TIM1_CH1             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C1                        | Timer 1 - channel 1           | -                                                    |

| 27        | 19            | PC2/TIM1_CH2             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C2                        | Timer 1- channel 2            | -                                                    |

| 28        | 20            | PC3/TIM1_CH3             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C3                        | Timer 1 - channel 3           | -                                                    |

| 29        | 21            | PC4/TIM1_CH4             | I/O  | Х        | Х    | Х              | HS        | O3    | Х                | Х  | Port C4                        | Timer 1 - channel 4           | -                                                    |

| 30        | 22            | PC5/SPI_SCK              | I/O  | Х        | Х    | Х              |           | O3    | Х                | Х  | Port C5                        | SPI clock                     | -                                                    |

| 31        | -             | V <sub>SSIO_2</sub>      | S    | -        | -    | -              | -         | -     | -                | -  | I/O groun                      | d                             | -                                                    |

| 32        | -             | V <sub>DDIO_2</sub>      | S    | -        | -    | -              | -         | -     | -                | -  | I/O power                      | supply                        | -                                                    |

| 33        | 23            | PC6/SPI_MOSI             | I/O  | x        | х    | х              | -         | O3    | х                | х  | Port C6                        | SPI master out/<br>slave in   | -                                                    |

| 34        | 24            | PC7/SPI_MISO             | I/O  | Х        | Х    | Х              | -         | O3    | Х                | Х  | Port C7                        | SPI master in/ slave out      | -                                                    |

| 35        | -             | PG0                      | I/O  | Х        | Х    | -              | -         | 01    | Х                | Х  | Port G0                        | -                             | -                                                    |

| 36        | -             | PG1                      | I/O  | Х        | Х    | -              | -         | 01    | Х                | Х  | Port G1                        | -                             | -                                                    |

| 37        | -             | PE3/TIM1_BKIN            | I/O  | Х        | Х    | Х              | -         | 01    | Х                | Х  | Port E3                        | Timer 1 - break input         | -                                                    |

| 38        | -             | PE2/I <sup>2</sup> C_SDA | I/O  | Χ        | -    | Х              | -         | 01    | T <sup>(6)</sup> | -  | Port E2                        | I <sup>2</sup> C data         | -                                                    |

| 39        | -             | PE1/I <sup>2</sup> C_SCL | I/O  | Χ        | -    | Х              | -         | 01    | T <sup>(6)</sup> | -  | Port E1                        | I <sup>2</sup> C clock        | -                                                    |

| 40        | -             | PE0/CLK_CCO              | I/O  | x        | х    | х              | -         | O3    | х                | х  | Port E0                        | Configurable clock<br>output  | -                                                    |

| 41        | 25            | PD0/TIM3_CH2             | I/O  | x        | x    | х              | HS        | O3    | x                | х  | Port D0                        | Timer 3 - channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 42        | 26            | PD1/SWIM <sup>(7)</sup>  | I/O  | Х        | X    | Х              | HS        | O4    | Х                | Х  | Port D1                        | SWIM data interface           | -                                                    |

| 43        | 27            | PD2/TIM3_CH1             | I/O  | x        | х    | х              | HS        | O3    | х                | х  | Port D2                        | Timer 3 - channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 44        | 28            | PD3/TIM2_CH2             | I/O  | x        | х    | х              | HS        | O3    | х                | х  | Port D3                        | Timer 2 - channel 2           | ADC_ETR<br>[AFR0]                                    |

| 45        | 29            | PD4/TIM2_CH1/<br>BEEP    | I/O  | x        | х    | х              | HS        | O3    | х                | х  | Port D4                        | Timer 2 - channel 1           | BEEP output<br>[AFR7]                                |

| 46        | 30            | PD5/<br>LINUART_TX       | I/O  | x        | х    | Х              | -         | 01    | х                | х  | Port D5                        | LINUART data transmit         | -                                                    |

| Table 8. STM8AF6246/48/66/68 (32 Kbyte) microcontroller pin description <sup>(1)(2)</sup> (conti |

|--------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|

| Flash program<br>memory size | Flash program<br>memory end<br>address | RAM size | RAM end<br>address | Stack roll-over<br>address |  |

|------------------------------|----------------------------------------|----------|--------------------|----------------------------|--|

| 32K                          | 0x00 0FFFF                             | 2K       | 0x00 07FF          | 0×00 0600                  |  |

| 16K                          | 0x00 0BFFF                             | 21       | 0x00 0777          | 0x00 0600                  |  |

Table 9. Memory model for the devices covered in this datasheet

# 7.2 Register map

Г

Т

In this section the memory and register map of the devices covered by this datasheet is described. For a detailed description of the functionality of the registers, refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016.

| Address   | Block  | Reset<br>status |                                   |                     |

|-----------|--------|-----------------|-----------------------------------|---------------------|

| 0x00 5000 |        | PA_ODR          | Port A data output latch register | 0x00                |

| 0x00 5001 |        | PA_IDR          | Port A input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5002 | Port A | PA_DDR          | Port A data direction register    | 0x00                |

| 0x00 5003 |        | PA_CR1          | Port A control register 1         | 0x00                |

| 0x00 5004 |        | PA_CR2          | Port A control register 2         | 0x00                |

| 0x00 5005 |        | PB_ODR          | Port B data output latch register | 0x00                |

| 0x00 5006 |        | PB_IDR          | Port B input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5007 | Port B | PB_DDR          | Port B data direction register    | 0x00                |

| 0x00 5008 |        | PB_CR1          | Port B control register 1         | 0x00                |

| 0x00 5009 |        | PB_CR2          | Port B control register 2         | 0x00                |

| 0x00 500A |        | PC_ODR          | Port C data output latch register | 0x00                |

| 0x00 500B |        | PB_IDR          | Port C input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 500C | Port C | PC_DDR          | Port C data direction register    | 0x00                |

| 0x00 500D |        | PC_CR1          | Port C control register 1         | 0x00                |

| 0x00 500E |        | PC_CR2          | Port C control register 2         | 0x00                |

| 0x00 500F |        | PD_ODR          | Port D data output latch register | 0x00                |

| 0x00 5010 |        | PD_IDR          | Port D input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5011 | Port D | PD_DDR          | Port D data direction register    | 0x00                |

| 0x00 5012 |        | PD_CR1          | Port D control register 1         | 0x02                |

| 0x00 5013 |        | PD_CR2          | Port D control register 2         | 0x00                |

Table 10. I/O port hardware register map

٦

Т

| · · · · · · · · · · · · · · · · · · · | Table 11. General hardware register map (continued) |                                                |                                            |                     |  |  |  |  |

|---------------------------------------|-----------------------------------------------------|------------------------------------------------|--------------------------------------------|---------------------|--|--|--|--|

| Address                               | Block                                               | Register label                                 | Register name                              | Reset<br>status     |  |  |  |  |

| 0x00 50A0                             |                                                     | EXTI_CR1                                       | External interrupt control register 1      | 0x00                |  |  |  |  |

| 0x00 50A1                             | ITC                                                 | EXTI_CR2                                       | External interrupt control register 2      | 0x00                |  |  |  |  |

| 0x00 50A2 to<br>0x00 50B2             |                                                     | Re                                             | eserved area (17 bytes)                    |                     |  |  |  |  |

| 0x00 50B3                             | RST                                                 | RST_SR                                         | Reset status register                      | 0xXX <sup>(1)</sup> |  |  |  |  |

| 0x00 50B4 to<br>0x00 50BF             | Reserved area (12 bytes)                            |                                                |                                            |                     |  |  |  |  |

| 0x00 50C0                             |                                                     | CLK_ICKR                                       | Internal clock control register            | 0x01                |  |  |  |  |

| 0x00 50C1                             | CLK                                                 | CLK_ECKR                                       | External clock control register            | 0x00                |  |  |  |  |

| 0x00 50C2                             |                                                     | Reserved area (1 byte)                         |                                            |                     |  |  |  |  |

| 0x00 50C3                             |                                                     | CLK_CMSR                                       | Clock master status register               | 0xE1                |  |  |  |  |

| 0x00 50C4                             |                                                     | CLK_SWR                                        | Clock master switch register               | 0xE1                |  |  |  |  |

| 0x00 50C5                             |                                                     | CLK_SWCR                                       | Clock switch control register              | 0xXX                |  |  |  |  |

| 0x00 50C6                             |                                                     | CLK_CKDIVR                                     | Clock divider register                     | 0x18                |  |  |  |  |

| 0x00 50C7                             | CLK                                                 | CLK_PCKENR1 Peripheral clock gating register 1 |                                            | 0xFF                |  |  |  |  |

| 0x00 50C8                             |                                                     | CLK_CSSR                                       | Clock security system register             | 0x00                |  |  |  |  |

| 0x00 50C9                             |                                                     | CLK_CCOR                                       | Configurable clock control register        | 0x00                |  |  |  |  |

| 0x00 50CA                             |                                                     | CLK_PCKENR2                                    | Peripheral clock gating register 2         | 0xFF                |  |  |  |  |

| 0x00 50CB                             |                                                     | F                                              | Reserved area (1 byte)                     | 1                   |  |  |  |  |

| 0x00 50CC                             |                                                     | CLK_HSITRIMR                                   | HSI clock calibration trimming register    | 0x00                |  |  |  |  |

| 0x00 50CD                             | CLK                                                 | CLK_SWIMCCR                                    | SWIM clock control register                | 0bXXXX<br>XXX0      |  |  |  |  |

| 0x00 50CE<br>to 0x00 50D0             |                                                     | R                                              | eserved area (3 bytes)                     |                     |  |  |  |  |

| 0x00 50D1                             |                                                     | WWDG_CR                                        | WWDG control register                      | 0x7F                |  |  |  |  |

| 0x00 50D2                             | WWDG                                                | WWDG_WR                                        | WWDR window register                       | 0x7F                |  |  |  |  |

| 0x00 50D3 to<br>0x00 50DF             |                                                     | Re                                             | eserved area (13 bytes)                    | L                   |  |  |  |  |

| 0x00 50E0                             |                                                     | IWDG_KR                                        | IWDG key register                          | 0xXX <sup>(2)</sup> |  |  |  |  |

| 0x00 50E1                             | IWDG                                                | IWDG_PR                                        | IWDG prescaler register                    | 0x00                |  |  |  |  |

| 0x00 50E2                             |                                                     | IWDG_RLR                                       | IWDG reload register                       | 0xFF                |  |  |  |  |

| 0x00 50E3 to<br>0x00 50EF             |                                                     | Re                                             | eserved area (13 bytes)                    |                     |  |  |  |  |

| 0x00 50F0                             |                                                     | AWU_CSR1                                       | AWU control/status register 1              | 0x00                |  |  |  |  |

| 0x00 50F1                             | AWU                                                 | AWU_APR                                        | AWU asynchronous prescaler buffer register | 0x3F                |  |  |  |  |

| 0x00 50F2                             |                                                     | AWU_TBR                                        | AWU timebase selection register            | 0x00                |  |  |  |  |

|                 | •• • • • •          | <i>( (</i> <b>) )</b> |

|-----------------|---------------------|-----------------------|

| Table 11. Gener | al hardware registe | er map (continued)    |

| AddressBlockRegister labelRegister nameRest status0x00 5300ADC_DB0RHADC data buffer register 0 high0x000x00 5321ADC_DB0RLADC data buffer register 1 high0x000x00 5323ADC_DB1RLADC data buffer register 1 high0x000x00 5324ADC_DB1RLADC data buffer register 1 high0x000x00 5355ADC_DB1RLADC data buffer register 1 high0x000x00 5356ADC_DB3RLADC data buffer register 2 high0x000x00 5357ADC_DB3RLADC data buffer register 3 high0x000x00 5368ADC_DB3RLADC data buffer register 4 high0x000x00 5369ADC_DB3RLADC data buffer register 4 high0x000x00 5360ADC_DB4RLADC data buffer register 4 high0x000x00 5361ADC_DB5RLADC data buffer register 5 high0x000x00 5362ADC_DB5RLADC data buffer register 5 high0x000x00 5362ADC_DB5RLADC data buffer register 6 high0x000x00 5376ADC_DB7RLADC data buffer register 7 high0x000x00 5376ADC_DB8RLADC data buffer register 7 h                                                                                                                                                                                                                                                                                       |           | Table 1 | 1. General hardw | /are register map (continued)    |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------------------|----------------------------------|------|

| 0x00 53E1         ADC_DB0RL         ADC data buffer register 0 low         0x00           0x00 53E2         ADC_DB1RH         ADC data buffer register 1 high         0x00           0x00 53E3         ADC_DB1RL         ADC data buffer register 1 high         0x00           0x00 53E4         ADC_DB2RH         ADC data buffer register 2 high         0x00           0x00 53E5         ADC_DB3RL         ADC data buffer register 2 high         0x00           0x00 53E6         ADC_DB3RL         ADC data buffer register 3 high         0x00           0x00 53E8         ADC_DB4RL         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB5RL         ADC data buffer register 4 low         0x00           0x00 53E8         ADC_DB6RL         ADC data buffer register 5 high         0x00           0x00 53E8         ADC_DB6RL         ADC data buffer register 6 high         0x00           0x00 53E8         ADC_DB7RL         ADC data buffer register 6 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 8 high         0x00           0x00 53F3                                                                                                     | Address   | Block   | Register label   | Register name                    |      |

| 0x00 53E2         ADC_DB1RH         ADC data buffer register 1 high         0x00           0x00 53E3         ADC_DB1RL         ADC data buffer register 1 low         0x00           0x00 53E4         ADC_DB2RH         ADC data buffer register 2 high         0x00           0x00 53E5         ADC_DB2RL         ADC data buffer register 2 high         0x00           0x00 53E6         ADC_DB3RH         ADC data buffer register 3 high         0x00           0x00 53E7         ADC_DB4RH         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB4RL         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB5RL         ADC data buffer register 5 high         0x00           0x00 53E8         ADC_DB6RL         ADC data buffer register 5 low         0x00           0x00 53E8         ADC_DB7RL         ADC data buffer register 6 high         0x00           0x00 53E9         ADC_DB7RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 9 high         0x00           0x00 53F5                                                                                                     | 0x00 53E0 |         | ADC _DB0RH       | ADC data buffer register 0 high  | 0x00 |

| 0x00 53E3         ADC_DB1RL         ADC data buffer register 1 low         0x00           0x00 53E4         ADC_DB2RH         ADC data buffer register 2 high         0x00           0x00 53E5         ADC_DB2RL         ADC data buffer register 2 low         0x00           0x00 53E6         ADC_DB3RH         ADC data buffer register 3 high         0x00           0x00 53E7         ADC_DB3RL         ADC data buffer register 3 low         0x00           0x00 53E8         ADC_DB4RH         ADC data buffer register 4 high         0x00           0x00 53E8         ADC_DB5RH         ADC data buffer register 4 low         0x00           0x00 53E8         ADC_DB5RH         ADC data buffer register 5 low         0x00           0x00 53E8         ADC_DB5RL         ADC data buffer register 6 high         0x00           0x00 53E6         ADC_DB6RH         ADC data buffer register 6 high         0x00           0x00 53E6         ADC_DB7RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 7 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 8 high         0x00           0x00 53F1         ADC_DB8RL         ADC data buffer register 9 high         0x00           0x00 53F3 <td>0x00 53E1</td> <td></td> <td>ADC _DB0RL</td> <td>ADC data buffer register 0 low</td> <td>0x00</td> | 0x00 53E1 |         | ADC _DB0RL       | ADC data buffer register 0 low   | 0x00 |

| 0x00 53E4<br>0x00 53E5<br>0x00 53E5ADC _DB2RHADC data buffer register 2 high0x000x00 53E6<br>0x00 53E7<br>0x00 53E8<br>0x00 53E8<br>0x00 53E8ADC _DB3RHADC data buffer register 3 high0x000x00 53E8<br>0x00 53E8<br>0x00 53E8ADC _DB4RHADC data buffer register 3 high0x000x00 53E6<br>0x00 53E8<br>0x00 53E8ADC _DB4RHADC data buffer register 4 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 4 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6<br>0x00 53E6ADC _DB6RHADC data buffer register 6 high0x000x00 53E6<br>0x00 53E6ADC _DB7RHADC data buffer register 6 high0x000x00 53E7<br>0x00 53F1ADC _DB7RHADC data buffer register 7 high0x000x00 53F1<br>0x00 53F2ADC _DB8RHADC data buffer register 7 high0x000x00 53F3ADC _DB8RHADC data buffer register 8 high0x000x00 53F4 to<br>0x00 53F4<br>0x00 53F4ADC _DB8RHADC control/status register0x000x00 53F4 to<br>0x00 53F4ADC _CR1ADC configuration register 10x000x00 5400<br>0x00 5401ADC _CR2ADC configuration register 20x000x00 5403<br>0x00 5404ADC _DRHADC configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5407ADC _DRHADC configuration register 10x000x00 5408ADC _TDRHADC Configuration register 10x0                                                                                                                                                                     | 0x00 53E2 |         | ADC _DB1RH       | ADC data buffer register 1 high  | 0x00 |

| ADC _DB2RLADC data buffer register 2 low0x000x00 53E6ADC _DB3RHADC data buffer register 3 high0x000x00 53E7ADC _DB3RLADC data buffer register 3 low0x000x00 53E8ADC _DB4RHADC data buffer register 4 high0x000x00 53E9ADC _DB5RHADC data buffer register 4 low0x000x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6ADC _DB5RLADC data buffer register 5 low0x000x00 53E6ADC _DB5RLADC data buffer register 6 high0x000x00 53E6ADC _DB6RHADC data buffer register 7 low0x000x00 53E6ADC _DB6RLADC data buffer register 7 high0x000x00 53E6ADC _DB7RHADC data buffer register 7 low0x000x00 53F1ADC _DB7RLADC data buffer register 7 low0x000x00 53F2ADC _DB7RLADC data buffer register 8 low0x000x00 53F3ADC _DB8RHADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53F6ADC _DB9RLADC data buffer register 9 low0x000x00 53F4ADC _CRSRADC control/status register0x000x00 5402ADC_CR2ADC configuration register 10x000x00 5403ADC_DRHADC data register low0xXX0x00 5404ADC_CR3ADC configuration register 30x000x00 5405ADC_CR3ADC configuration register 10x000x00 5406ADC_DRHADC data register low0xXX0x00 5406 </td <td>0x00 53E3</td> <td></td> <td>ADC _DB1RL</td> <td>ADC data buffer register 1 low</td> <td>0x00</td>                                                                                                                                                                                       | 0x00 53E3 |         | ADC _DB1RL       | ADC data buffer register 1 low   | 0x00 |

| 0x00 53E6<br>0x00 53E7ADC _DB3RHADC data buffer register 3 high0x000x00 53E8<br>0x00 53E9ADC _DB4RHADC data buffer register 4 high0x000x00 53E8<br>0x00 53E4ADC _DB4RLADC data buffer register 4 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6<br>0x00 53E6ADC _DB5RHADC data buffer register 5 high0x000x00 53E6<br>0x00 53E6ADC _DB6RHADC data buffer register 6 high0x000x00 53E6<br>0x00 53E6ADC _DB6RHADC data buffer register 6 high0x000x00 53E7<br>0x00 53E6ADC _DB7RHADC data buffer register 7 high0x000x00 53F1<br>0x00 53F1ADC _DB7RHADC data buffer register 7 high0x000x00 53F2ADC _DB7RHADC data buffer register 8 high0x000x00 53F3ADC _DB7RHADC data buffer register 8 high0x000x00 53F3ADC _DB7RHADC data buffer register 9 high0x000x00 53F3ADC _DB7RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4ADC _DB9RHADC control/status register0x000x00 5402ADC _CR3ADC configuration register 10x000x00 5403ADC_CR3ADC configuration register 30x000x00 5404ADC_DRHADC data register high0xXX0x00 5405ADC_DRHADC data register low0xXX0x00 5406ADC_DRHADC configuration register 30x000x00 5406ADC_DRHADC data register                                                                                                                                                                                                                                            | 0x00 53E4 |         | ADC _DB2RH       | ADC data buffer register 2 high  | 0x00 |

| 0x00 53E7ADC _DB3RLADC data buffer register 3 low0x000x00 53E8ADC _DB4RHADC data buffer register 4 low0x000x00 53E4ADC _DB4RLADC data buffer register 4 low0x000x00 53E6ADC _DB5RHADC data buffer register 5 low0x000x00 53E6ADC _DB6RHADC data buffer register 5 low0x000x00 53E7ADC _DB6RHADC data buffer register 6 low0x000x00 53E7ADC _DB6RHADC data buffer register 7 low0x000x00 53F6ADC _DB7RHADC data buffer register 7 low0x000x00 53F7ADC _DB8RLADC data buffer register 7 low0x000x00 53F1ADC _DB8RHADC data buffer register 8 low0x000x00 53F2ADC _DB8RHADC data buffer register 9 low0x000x00 53F4ADC _DB8RLADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53F7ADC _DB9RLADC control/status register0x000x00 5400ADC _CR3ADC configuration register 10x000x00 5401ADC_CR2ADC configuration register 30x000x00 5405ADC_DRHADC data register low0xXX0x00 5406ADC_DRHADC Configuration register 10x000x00 5407ADC_DRHADC Configuration register 10x000x00 5408ADC_DRHADC Control/status register0x000x00 5408ADC_DRHADC Configuration register 30x000x00 5407ADC_DRHADC Configuration register 10x000x00                                                                                                                                                                                                                                                                                                           | 0x00 53E5 |         | ADC _DB2RL       | ADC data buffer register 2 low   | 0x00 |

| 0x00 53E8<br>0x00 53E9ADC _DB4RHADC data buffer register 4 high0x000x00 53E4ADC _DB4RLADC data buffer register 4 low0x000x00 53E4ADC _DB5RHADC data buffer register 5 low0x000x00 53E6ADC _DB6RHADC data buffer register 5 low0x000x00 53E7ADC _DB6RHADC data buffer register 6 high0x000x00 53E7ADC _DB7RHADC data buffer register 7 high0x000x00 53F1ADC _DB7RHADC data buffer register 7 low0x000x00 53F2ADC _DB8RHADC data buffer register 7 low0x000x00 53F3ADC _DB8RHADC data buffer register 8 high0x000x00 53F4ADC _DB8RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F7ADC _DB9RHADC data buffer register 9 high0x000x00 5400ADC _DB9RLADC data buffer register 9 high0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRHADC Cata register low0xXX0x00 5406ADC_DRHADC Cata buffer register 10x000x00 5407ADC_DRHADC Cata register low0xXX0x00 5408ADC_DRHADC Configuration register 10x000x00 5408ADC_DRHADC Configuration register 10x000x00 5407ADC_DRHADC Configuration register 10x00 <tr< td=""><td>0x00 53E6</td><td></td><td>ADC _DB3RH</td><td>ADC data buffer register 3 high</td><td>0x00</td></tr<>                                                                                                                                                                                 | 0x00 53E6 |         | ADC _DB3RH       | ADC data buffer register 3 high  | 0x00 |

| ADCADCADCADCADCADCADC0x0053E3ADCADCDB5RHADC data buffer register 5 high0x000x0053E3ADCDB5RLADC data buffer register 5 low0x000x0053E0ADCDB6RHADC data buffer register 6 low0x000x0053E1ADCDB6RLADC data buffer register 6 low0x000x0053E2ADCDB7RHADC data buffer register 7 low0x000x0053E7ADCDB7RHADC data buffer register 7 low0x000x0053F3ADCDB8RHADC data buffer register 8 low0x000x0053F3ADCDB8RLADC data buffer register 8 low0x000x0053F4ADCADCDB8RLADC data buffer register 9 low0x000x0053F4ADCADCDB9RHADC data buffer register 9 low0x000x0053F4ADCADCDB9RLADC cata buffer register 9 low0x000x0053F4ADCADCCSRADC control/status register0x000x0053F4ADCADCCR2ADC configuration register 10x000x0053F4ADCADC_CR3ADC configuration register 20x000x005400ADCADC_CR3ADC configuration register 10x000x005403ADC_DRHADC data register high0xXX0x005406ADC_DRLADC control/status register0x00<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00 53E7 |         | ADC _DB3RL       | ADC data buffer register 3 low   | 0x00 |

| ADCADC_DBSRHADC data buffer register 5 high0x000x00 53EAADC_DBSRLADC data buffer register 5 low0x000x00 53EBADC_DB6RLADC data buffer register 6 high0x000x00 53EDADC_DB6RLADC data buffer register 6 low0x000x00 53EDADC_DB7RHADC data buffer register 7 high0x000x00 53EFADC_DB7RLADC data buffer register 7 low0x000x00 53F0ADC_DB7RLADC data buffer register 7 low0x000x00 53F1ADC_DB8RHADC data buffer register 8 high0x000x00 53F2ADC_DB8RLADC data buffer register 8 low0x000x00 53F3ADC_DB9RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4ADC_DB9RLADC data buffer register 9 high0x000x00 5400ADC_CR3ADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRLADC configuration register 10x000x00 5406ADC_DRLADC Control/status register0x000x00 5407ADC_DRHADC control/status register high0xXX0x00 5408ADC_TDRHADC control/status register high0xXX0x00 5408ADC_DRLADC control/status register high0xXX0x00 5407ADC_TDRHADC control/status register high0x000x00 5408ADC_TDRHADC control/status register high0x00 <tr< td=""><td>0x00 53E8</td><td></td><td>ADC _DB4RH</td><td>ADC data buffer register 4 high</td><td>0x00</td></tr<>                                                                                                                                                                                | 0x00 53E8 |         | ADC _DB4RH       | ADC data buffer register 4 high  | 0x00 |

| ADC _DB5RHADC data buffer register 5 high0x000x00 53EBADC _DB5RLADC data buffer register 5 low0x000x00 53ECADC _DB6RHADC data buffer register 6 high0x000x00 53EDADC _DB6RLADC data buffer register 6 low0x000x00 53EDADC _DB7RHADC data buffer register 7 high0x000x00 53F1ADC _DB7RHADC data buffer register 7 high0x000x00 53F2ADC _DB8RHADC data buffer register 8 high0x000x00 53F3ADC _DB8RHADC data buffer register 8 high0x000x00 53F4 to<br>0x00 53F4 to<br>0x00 5402ADC _CSRADC control/status register 9 high0x000x00 5402ADC _CR2ADC configuration register 10x000x00 5403ADC _CR3ADC configuration register 30x000x00 5404ADC _DRHADC data puffer register 10x000x00 5406ADC _CR3ADC configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5407ADC _DRHADC configuration register high0xXX0x00 5408ADC _TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC _TDRHADC Schmitt trigger disable register high0x000x00 5408ADC _HTRHADC high threshold re                                                                                                                                                                                                                                                                        | 0x00 53E9 |         | ADC _DB4RL       | ADC data buffer register 4 low   | 0x00 |

| 0x00 53ECADC _DB6RHADC data buffer register 6 high0x000x00 53EDADC _DB6RLADC data buffer register 6 low0x000x00 53EEADC _DB7RHADC data buffer register 7 high0x000x00 53F6ADC _DB7RLADC data buffer register 7 low0x000x00 53F1ADC _DB8RHADC data buffer register 8 high0x000x00 53F2ADC _DB8RLADC data buffer register 8 low0x000x00 53F3ADC _DB9RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4 to<br>0x00 53F4ADC _CSRADC control/status register 9 low0x000x00 53F4 to<br>0x00 53F4ADC _CCR1ADC configuration register 10x000x00 5401ADC _CR2ADC configuration register 20x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5406ADC _DRHADC Control/status register 00x000x00 5407ADC _DRHADC Configuration register 10x000x00 5408ADC _DRHADC Control/status register high0xXX0x00 5408ADC _DRHADC Configuration register 10x000x00 5409ADC _DRHADC Control/status register high0x000x00 5408ADC _DRHADC Configuration register 10x000x00 5406ADC _DRHADC Control/status register high0x000x00 5408ADC _DRHADC Control/status register high0x000x00 5409ADC _DRHADC Control/sta                                                                                                                                                                                                                                                                                 | 0x00 53EA | ADC     | ADC _DB5RH       | ADC data buffer register 5 high  | 0x00 |

| Ox00 53EDADC_DB6RLADC data buffer register 6 lowOx000x00 53EEADC_DB7RHADC data buffer register 7 high0x000x00 53FFADC_DB7RLADC data buffer register 7 low0x000x00 53F0ADC_DB8RHADC data buffer register 7 low0x000x00 53F1ADC_DB8RLADC data buffer register 8 high0x000x00 53F2ADC_DB8RLADC data buffer register 9 high0x000x00 53F3ADC_DB9RHADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC_CR1ADC configuration register 10x000x00 5401ADC_CR2ADC configuration register 20x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRHADC configuration register 10x000x00 5406ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register low0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 53EB |         | ADC _DB5RL       | ADC data buffer register 5 low   | 0x00 |

| Ox00 53EEADC _DB7RHADC data buffer register 7 highOx000x00 53FFADC _DB7RLADC data buffer register 7 high0x000x00 53F0ADC _DB8RHADC data buffer register 8 high0x000x00 53F1ADC _DB8RLADC data buffer register 8 low0x000x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CR1ADC configuration register 10x000x00 5401ADC _CR2ADC configuration register 20x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5405ADC _DRLADC Configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5406ADC _DRHADC configuration register 10x000x00 5406ADC _TDRHADC Schmitt trigger disable register<br>high0x000x00 5408ADC _TDRHADC Schmitt trigger disable register<br>low0x000x00 5409ADC _HTRHADC high threshold register high0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 53EC |         | ADC _DB6RH       | ADC data buffer register 6 high  | 0x00 |

| Ox00 53EFADC _DB7RLADC data buffer register 7 lowOx000x00 53F0ADC _DB8RHADC data buffer register 8 high0x000x00 53F1ADC _DB8RLADC data buffer register 8 high0x000x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC _CR1ADC configuration register 10x000x00 5402ADC _CR2ADC configuration register 20x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5406ADC _DRLADC Cchmitt trigger disable register0x000x00 5407ADC _TDRHADC Schmitt trigger disable register0x000x00 5408ADC _HTRHADC high threshold register high0xFF0x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 53ED |         | ADC _DB6RL       | ADC data buffer register 6 low   | 0x00 |

| ADC _DB8RHADC data buffer register 8 high0x000x00 53F1ADC _DB8RLADC data buffer register 8 high0x000x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFADC _CSRADC control/status register0x000x00 5400ADC _CR1ADC configuration register 10x000x00 5401ADC _CR2ADC configuration register 20x000x00 5403ADC _DRHADC configuration register 30x000x00 5404ADC _DRLADC data register high0xXX0x00 5406ADC _TDRHADC Schmitt trigger disable register0x000x00 5407ADC _TDRHADC Schmitt trigger disable register0x000x00 5408ADC _TTRHADC Schmitt trigger disable register0x000x00 5409ADC _HTRHADC high threshold register high0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x00 53EE |         | ADC _DB7RH       | ADC data buffer register 7 high  | 0x00 |

| ADC _DB8RLADC data buffer register 8 low0x000x00 53F1ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 high0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5402ADC_CR2ADC configuration register 20x000x00 5403ADC_DRHADC configuration register 30x000x00 5404ADC_DRLADC data register high0xXX0x00 5405ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRLADC Schmitt trigger disable register<br>high0x000x00 5408ADC _HTRHADC high threshold register high0x000x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 53EF |         | ADC _DB7RL       | ADC data buffer register 7 low   | 0x00 |

| 0x00 53F2ADC _DB9RHADC data buffer register 9 high0x000x00 53F3ADC _DB9RLADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC _CR1ADC configuration register 10x000x00 5402ADC _CR2ADC configuration register 20x000x00 5403ADC _CR3ADC configuration register 30x000x00 5404ADC _DRHADC data register low0xXX0x00 5405ADC _DRLADC data register low0xXX0x00 5406ADC _TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC _TDRLADC Schmitt trigger disable register<br>low0x000x00 5408ADC _HTRHADC high threshold register high0xFF0x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 53F0 |         | ADC _DB8RH       | ADC data buffer register 8 high  | 0x00 |

| 0x00 53F3ADC _DB9RLADC data buffer register 9 low0x000x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x000x00 5400ADC _CSRADC control/status register0x000x00 5401ADC _CR1ADC configuration register 10x000x00 5402ADC _CR2ADC configuration register 20x000x00 5403ADC _CR3ADC configuration register 30x000x00 5404ADC _DRHADC data register high0xXX0x00 5406ADC _DRLADC data register low0xXX0x00 5407ADC _TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC _HTRLADC high threshold register high0x0FF0x00 5409ADC _HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 53F1 |         | ADC _DB8RL       | ADC data buffer register 8 low   | 0x00 |

| 0x00 53F4 to<br>0x00 53FFReserved area (12 bytes)0x00 5400ADC_CSRADC control/status register0x000x00 5401ADC_CR1ADC configuration register 10x000x00 5402ADC_CR2ADC configuration register 20x000x00 5403ADC_CR3ADC configuration register 30x000x00 5404ADC_DRHADC data register high0xXX0x00 5405ADC_DRLADC data register low0xXX0x00 5406ADC_TDRHADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register low0x070x00 5409ADC_HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 53F2 |         | ADC _DB9RH       | ADC data buffer register 9 high  | 0x00 |

| Ox00 53FF         ADC_CSR         ADC control/status register         Ox00           0x00 5401         ADC_CR1         ADC configuration register 1         0x00           0x00 5402         ADC_CR2         ADC configuration register 2         0x00           0x00 5403         ADC_DR1         ADC configuration register 3         0x00           0x00 5404         ADC_DRH         ADC data register high         0xXX           0x00 5405         ADC_DRL         ADC data register low         0x00           0x00 5406         ADC_TDRH         ADC Schmitt trigger disable register low         0x00           0x00 5407         ADC_TDRL         ADC Schmitt trigger disable register low         0x00           0x00 5408         ADC_HTRH         ADC high threshold register high         0xFF           0x00 5409         ADC_HTRL         ADC high threshold register low         0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 53F3 |         | ADC _DB9RL       | ADC data buffer register 9 low   | 0x00 |

| 0x00 5401ADC_CR1ADC configuration register 10x000x00 5402ADC_CR2ADC configuration register 20x000x00 5403ADC_CR3ADC configuration register 30x000x00 5404ADC_DRHADC data register high0xXX0x00 5405ADC_DRLADC data register low0xXX0x00 5406ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRLADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register high0xFF0x00 5409ADC_HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |         | Re               | eserved area (12 bytes)          |      |

| 0x00 5402       ADC_CR2       ADC configuration register 2       0x00         0x00 5403       ADC_CR3       ADC configuration register 3       0x00         0x00 5404       ADC_DRH       ADC data register high       0xXX         0x00 5405       ADC_DRL       ADC data register low       0xXX         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register low       0x00         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_HTRH       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 5400 |         | ADC _CSR         | ADC control/status register      | 0x00 |

| 0x00 5403ADC_CR3ADC configuration register 30x000x00 5404ADC_DRHADC data register high0xXX0x00 5405ADC_DRLADC data register low0xXX0x00 5406ADC_TDRHADC Schmitt trigger disable register<br>high0x000x00 5407ADC_TDRLADC Schmitt trigger disable register<br>low0x000x00 5408ADC_HTRHADC high threshold register low0xFF0x00 5409ADC_HTRLADC high threshold register low0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 5401 |         | ADC_CR1          | ADC configuration register 1     | 0x00 |

| 0x00 5404       ADC_DRH       ADC data register high       0xXX         0x00 5405       ADC_DRL       ADC data register low       0xXX         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register high       0xXX         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5409       ADC_HTRH       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 5402 |         | ADC_CR2          | ADC configuration register 2     | 0x00 |

| 0x00 5405       ADC_DRL       ADC data register low       0xXX         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register high       0x00         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_HTRH       ADC high threshold register high       0xFF         0x00 5409       ADC_HTRL       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 5403 |         | ADC_CR3          | ADC configuration register 3     | 0x00 |

| ADC       ADC       ADC_TDRH       ADC Schmitt trigger disable register high       0x00         0x00 5406       ADC_TDRH       ADC Schmitt trigger disable register low       0x00         0x00 5407       ADC_TDRL       ADC Schmitt trigger disable register low       0x00         0x00 5408       ADC_HTRH       ADC high threshold register high       0xFF         0x00 5409       ADC_HTRL       ADC high threshold register low       0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 5404 |         | ADC_DRH          | ADC data register high           | 0xXX |

| 0x00 5406     ADC_TDRH     ADC Schmitt trigger disable register high     0x00       0x00 5407     ADC_TDRL     ADC Schmitt trigger disable register low     0x00       0x00 5408     ADC_HTRH     ADC high threshold register low     0x03       0x00 5409     ADC_HTRL     ADC high threshold register low     0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 5405 | ADC     | ADC_DRL          | ADC data register low            | 0xXX |

| 0x00 5407     ADC_TDRL     Iow     0x00       0x00 5408     ADC_HTRH     ADC high threshold register high     0xFF       0x00 5409     ADC_HTRL     ADC high threshold register low     0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 5406 |         | ADC_TDRH         |                                  | 0x00 |

| 0x00 5409 ADC_HTRL ADC high threshold register low 0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x00 5407 |         | ADC_TDRL         |                                  | 0x00 |