Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6266tcy |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           | flat package mechanical data                            | 79 |

|-----------|---------------------------------------------------------|----|

| Table 47. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |    |

|           | mechanical data                                         | 33 |

| Table 48. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package |    |

|           | mechanical data                                         | 36 |

| Table 49. | Thermal characteristics                                 | 38 |

| Table 50. | Document revision history                               | 94 |

# List of figures

| Figure 1.  | STM8AF6246/48/66/68 block diagram                                                            | 12 |

|------------|----------------------------------------------------------------------------------------------|----|

| Figure 2.  | Flash memory organization of STM8AF6246/48/66/68                                             |    |

| Figure 3.  | VFQFPN/LQFP 32-pin pinout                                                                    |    |

| Figure 4.  | LQFP 48-pin pinout.                                                                          |    |

| Figure 5.  | Register and memory map of STM8A products                                                    |    |

| Figure 6.  | Pin loading conditions.                                                                      |    |

| Figure 7.  | Pin input voltage                                                                            |    |

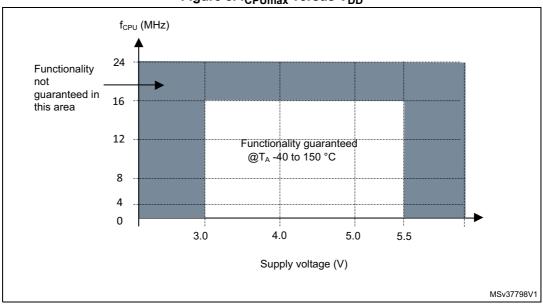

| Figure 8.  | f <sub>CPUmax</sub> versus V <sub>DD</sub>                                                   |    |

| Figure 9.  | External capacitor C <sub>FXT</sub>                                                          |    |

| Figure 10. | Typ. I <sub>DD(RUN)HSE</sub> vs. V <sub>DD</sub> @f <sub>CPU</sub> = 16 MHz, peripheral = on | 56 |

| Figure 11. | Typ. $I_{DD(RUN)HSE}$ vs. $f_{CPU}$ @ $V_{DD}$ = 5.0 V, peripheral = on                      | 56 |

| Figure 12. | Typ. $I_{DD(RUN)HSI}$ vs. $V_{DD}$ @ $f_{CPU}$ = 16 MHz, peripheral = off                    | 57 |

| Figure 13. | Typ. $I_{DD(WFI)HSE}$ vs. $V_{DD}$ @ $f_{CPU}$ = 16 MHz, peripheral = on                     | 57 |

| Figure 14. | Typ. $I_{DD(WFI)HSE}$ vs. $f_{CPU}$ @ $V_{DD}$ = 5.0 V, peripheral = on                      | 57 |

| Figure 15. | Typ. $I_{DD(WFI)HSI}$ vs. $V_{DD}$ @ $f_{CPU}$ = 16 MHz, peripheral = off                    | 57 |

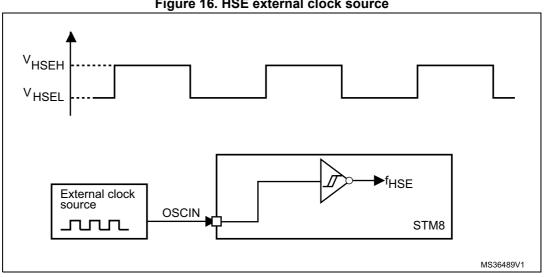

| Figure 16. | HSE external clock source                                                                    | 58 |

| Figure 17. | HSE oscillator circuit diagram                                                               |    |

| Figure 18. | Typical HSI frequency vs V <sub>DD</sub>                                                     |    |

| Figure 19. | Typical LSI frequency vs V <sub>DD</sub>                                                     |    |

| Figure 20. | Typical V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ four temperatures           |    |

| Figure 21. | Typical pull-up resistance R <sub>PU</sub> vs V <sub>DD</sub> @ four temperatures            |    |

| Figure 22. | Typical pull-up current I <sub>pu</sub> vs V <sub>DD</sub> @ four temperatures               |    |

| Figure 23. | Typ. $V_{OL} @ V_{DD} = 3.3 V$ (standard ports).                                             |    |

| Figure 24. | Typ. $V_{OL} @ V_{DD} = 5.0 V$ (standard ports).                                             |    |

| Figure 25. | Typ. $V_{OL} @ V_{DD} = 3.3 V$ (true open drain ports)                                       |    |

| Figure 26. | Typ. $V_{OL} @ V_{DD} = 5.0 V$ (true open drain ports)                                       |    |

| Figure 27. | Typ. $V_{OL} @ V_{DD} = 3.3 V$ (high sink ports)                                             |    |

| Figure 28. | Typ. $V_{OL} @ V_{DD} = 5.0 V$ (high sink ports)                                             |    |

| Figure 29. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 V$ (standard ports).                                    |    |

| Figure 30. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5.0 V$ (standard ports).                                    |    |

| Figure 31. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 V$ (high sink ports)                                    |    |

| Figure 32. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5.0 V$ (high sink ports)                                    |    |

| Figure 33. | Typical NRST V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ four temperatures      |    |

| Figure 34. | Typical NRST pull-up resistance R <sub>PU</sub> vs V <sub>DD</sub>                           |    |

| Figure 35. | Typical NRST pull-up current I <sub>pu</sub> vs V <sub>DD</sub>                              |    |

| Figure 36. | Recommended reset pin protection                                                             |    |

| Figure 37. | SPI timing diagram where slave mode and CPHA = 0                                             |    |

| Figure 38. | SPI timing diagram where slave mode and CPHA = 1                                             | 70 |

| Figure 39. | SPI timing diagram - master mode                                                             |    |

| Figure 40. | Typical application with ADC                                                                 | 73 |

| Figure 41. | ADC accuracy characteristics                                                                 | 74 |

| Figure 42. | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad                    |    |

| U          | flat package outline                                                                         | 78 |

| Figure 43. | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad                    |    |

| -          | flat package recommended footprint                                                           | 80 |

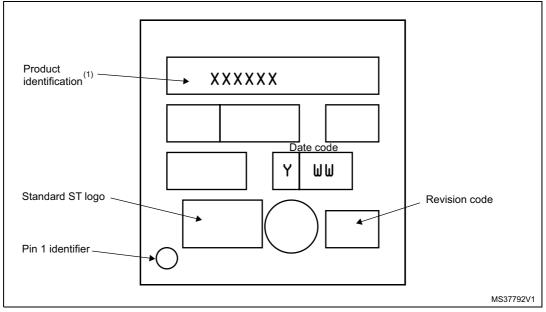

| Figure 44. | VFQFPN32 marking example (package top view)                                                  | 81 |

| Figure 45. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                              |    |

| Figure 46. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                                      |    |

## 1 Introduction

This datasheet refers to the STM8AF6246, STM8AF6248, STM8AF6266 and STM8AF6268 products with 16 to 32 Kbyte of Flash program memory.

In the order code, the letter 'F' refers to product versions with data EEPROM and 'H' refers to product versions without data EEPROM. The identifiers 'F' and 'H' do not coexist in a given order code.

The datasheet contains the description of family features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8 Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

| Address   | Block                            | Register label | Register name                     | Reset<br>status     |

|-----------|----------------------------------|----------------|-----------------------------------|---------------------|

| 0x00 5014 |                                  | PE_ODR         | Port E data output latch register | 0x00                |

| 0x00 5015 |                                  | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016 | Port E                           | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017 |                                  | PE_CR1         | Port E control register 1         | 0x00                |

| 0x00 5018 |                                  | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019 |                                  | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A |                                  | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B | Port F                           | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C | PF_CR1 Port F control registe    |                | Port F control register 1         | 0x00                |

| 0x00 501D |                                  | PF_CR2         | Port F control register 2         | 0x00                |

| 0x00 501E |                                  | PG_ODR         | Port G data output latch register | 0x00                |

| 0x00 501F |                                  | PG_IDR         | Port G input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5020 | Port G                           | PG_DDR         | Port G data direction register    | 0x00                |

| 0x00 5021 |                                  | PG_CR1         | PG_CR1 Port G control register 1  |                     |

| 0x00 5022 | PG_CR2 Port G control register 2 |                | 0x00                              |                     |

| Table 10. I/O port hardware register map (continued) |

|------------------------------------------------------|

|------------------------------------------------------|

1. Depends on the external circuitry.

| Address                   | Block                    | Block Register label Register name                    |                                                  | Reset<br>status |

|---------------------------|--------------------------|-------------------------------------------------------|--------------------------------------------------|-----------------|

| 0x00 505A                 |                          | FLASH_CR1                                             | Flash control register 1                         | 0x00            |

| 0x00 505B                 |                          | FLASH_CR2                                             | Flash control register 2                         | 0x00            |

| 0x00 505C                 |                          | FLASH_NCR2                                            | Flash complementary control register 2           | 0xFF            |

| 0x00 505D                 | Flash                    | FLASH_FPR                                             | Flash protection register                        | 0x00            |

| 0x00 505E                 |                          | FLASH_NFPR                                            | Flash complementary protection register          | 0xFF            |

| 0x00 505F                 |                          | FLASH_IAPSR                                           | Flash in-application programming status register | 0x40            |

| 0x00 5060 to<br>0x00 5061 |                          | Reserved area (2 bytes)                               |                                                  |                 |

| 0x00 5062                 | Flash                    | FLASH_PUKR Flash Program memory unprotection register |                                                  | 0x00            |

| 0x00 5063                 | Reserved area (1 byte)   |                                                       |                                                  |                 |

| 0x00 5064                 | Flash                    | Flash FLASH_DUKR Data EEPROM unprotection register    |                                                  | 0x00            |

| 0x00 5065 to<br>0x00 509F | Reserved area (59 bytes) |                                                       |                                                  |                 |

### Table 11. General hardware register map

DocID14952 Rev 11

| Table 11. General hardware register map (continued) |                                    |                               |                                            |                     |

|-----------------------------------------------------|------------------------------------|-------------------------------|--------------------------------------------|---------------------|

| Address                                             | Block Register label Register name |                               | Reset<br>status                            |                     |

| 0x00 50A0                                           | EXTI_CR1                           |                               | External interrupt control register 1      | 0x00                |

| 0x00 50A1                                           | ITC                                | EXTI_CR2                      | External interrupt control register 2      | 0x00                |

| 0x00 50A2 to<br>0x00 50B2                           | Reserved area (17 bytes)           |                               |                                            |                     |

| 0x00 50B3                                           | RST                                | RST_SR                        | Reset status register                      | 0xXX <sup>(1)</sup> |

| 0x00 50B4 to<br>0x00 50BF                           |                                    | Re                            | eserved area (12 bytes)                    |                     |

| 0x00 50C0                                           |                                    | CLK_ICKR                      | Internal clock control register            | 0x01                |

| 0x00 50C1                                           | CLK                                | CLK_ECKR                      | External clock control register            | 0x00                |

| 0x00 50C2                                           |                                    | F                             | Reserved area (1 byte)                     |                     |

| 0x00 50C3                                           |                                    | CLK_CMSR                      | Clock master status register               | 0xE1                |

| 0x00 50C4                                           |                                    | CLK_SWR                       | Clock master switch register               | 0xE1                |

| 0x00 50C5                                           |                                    | CLK_SWCR                      | Clock switch control register              | 0xXX                |

| 0x00 50C6                                           |                                    | CLK_CKDIVR                    | Clock divider register                     | 0x18                |

| 0x00 50C7                                           | CLK                                | CLK_PCKENR1                   | Peripheral clock gating register 1         | 0xFF                |

| 0x00 50C8                                           |                                    | CLK_CSSR                      | Clock security system register             | 0x00                |

| 0x00 50C9                                           |                                    | CLK_CCOR                      | Configurable clock control register        | 0x00                |

| 0x00 50CA                                           |                                    | CLK_PCKENR2                   | Peripheral clock gating register 2         | 0xFF                |

| 0x00 50CB                                           | Reserved area (1 byte)             |                               | 1                                          |                     |

| 0x00 50CC                                           |                                    | CLK_HSITRIMR                  | HSI clock calibration trimming register    | 0x00                |

| 0x00 50CD                                           | CLK                                | CLK_SWIMCCR                   | SWIM clock control register                | 0bXXXX<br>XXX0      |

| 0x00 50CE<br>to 0x00 50D0                           | Reserved area (3 bytes)            |                               |                                            |                     |

| 0x00 50D1                                           |                                    | WWDG_CR WWDG control register |                                            | 0x7F                |

| 0x00 50D2                                           | WWDG                               | WWDG_WR                       | WWDR window register                       | 0x7F                |

| 0x00 50D3 to<br>0x00 50DF                           | Reserved area (13 bytes)           |                               | L                                          |                     |

| 0x00 50E0                                           |                                    | IWDG_KR                       | IWDG key register                          | 0xXX <sup>(2)</sup> |

| 0x00 50E1                                           | IWDG                               | IWDG_PR                       | IWDG prescaler register                    | 0x00                |

| 0x00 50E2                                           |                                    | IWDG_RLR                      | IWDG reload register                       | 0xFF                |

| 0x00 50E3 to<br>0x00 50EF                           | Reserved area (13 bytes)           |                               |                                            |                     |

| 0x00 50F0                                           |                                    | AWU_CSR1                      | AWU control/status register 1              | 0x00                |

| 0x00 50F1                                           | AWU                                | AWU_APR                       | AWU asynchronous prescaler buffer register | 0x3F                |

| 0x00 50F2                                           |                                    | AWU_TBR                       | AWU timebase selection register            | 0x00                |

|                 | •• • • • •          | <i>( (</i> <b>) )</b> |

|-----------------|---------------------|-----------------------|

| Table 11. Gener | al hardware registe | er map (continued)    |

| Address                   | Block | ck Register label Register name |                                           | Reset<br>status |

|---------------------------|-------|---------------------------------|-------------------------------------------|-----------------|

| 0x00 7F81 to<br>0x00 7F8F |       |                                 | Reserved area (15 bytes)                  |                 |

| 0x00 7F90                 |       | DM_BK1RE                        | DM breakpoint 1 register extended byte    | 0xFF            |

| 0x00 7F91                 |       | DM_BK1RH                        | DM breakpoint 1 register high byte        | 0xFF            |

| 0x00 7F92                 |       | DM_BK1RL                        | DM breakpoint 1 register low byte         | 0xFF            |

| 0x00 7F93                 |       | DM_BK2RE                        | DM breakpoint 2 register extended byte    | 0xFF            |

| 0x00 7F94                 |       | DM_BK2RH                        | DM breakpoint 2 register high byte        | 0xFF            |

| 0x00 7F95                 | DM    | DM_BK2RL                        | DM breakpoint 2 register low byte         | 0xFF            |

| 0x00 7F96                 |       | DM_CR1                          | DM debug module control register 1        | 0x00            |

| 0x00 7F97                 |       | DM_CR2                          | DM debug module control register 2        | 0x00            |

| 0x00 7F98                 |       | DM_CSR1                         | DM debug module control/status register 1 | 0x10            |

| 0x00 7F99                 |       | DM_CSR2                         | DM debug module control/status register 2 | 0x00            |

| 0x00 7F9A                 |       | DM_ENFCTR                       | DM enable function register               | 0xFF            |

| 0x00 7F9B to<br>0x00 7F9F |       |                                 | Reserved area (5 bytes)                   |                 |

## Table 12. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

2. Product dependent value, see Figure 5: Register and memory map of STM8A products.

|           |       | Table 15. Tempor             | ary memory unprotection registers                         |                 |

|-----------|-------|------------------------------|-----------------------------------------------------------|-----------------|

| Address   | Block | Register label Register name |                                                           | Reset<br>status |

| 0x00 5800 |       | TMU_K1                       | Temporary memory unprotection key register 1              | 0x00            |

| 0x00 5801 |       | TMU_K2                       | Temporary memory unprotection key register 2              | 0x00            |

| 0x00 5802 |       | TMU_K3                       | Temporary memory unprotection key register 3              | 0x00            |

| 0x00 5803 |       | TMU_K4                       | Temporary memory unprotection key register 4              | 0x00            |

| 0x00 5804 | TMU   | TMU_K5                       | Temporary memory unprotection key register 5              | 0x00            |

| 0x00 5805 |       | TMU_K6                       | Temporary memory unprotection key register 6              | 0x00            |

| 0x00 5806 |       | TMU_K7                       | Temporary memory unprotection key register 7              | 0x00            |

| 0x00 5807 |       | TMU_K8                       | Temporary memory unprotection key register 8              | 0x00            |

| 0x00 5808 |       | TMU_CSR                      | Temporary memory unprotection control and status register | 0x00            |

#### Table 13. Temporary memory unprotection registers

| Option byte no. | Description                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | HSITRIM: Trimming option for 16 MHz internal RC oscillator                                                                                      |

|                 | 0: 3-bit on-the-fly trimming (compatible with devices based on the 128K silicon)                                                                |

|                 | 1: 4-bit on-the-fly trimming                                                                                                                    |

|                 | LSI_EN: Low speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source   |

| OPT3            | IWDG_HW: Independent watchdog                                                                                                                   |

| UF 13           | <ul><li>0: IWDG independent watchdog activated by software</li><li>1: IWDG independent watchdog activated by hardware</li></ul>                 |

|                 | WWDG_HW: Window watchdog activation                                                                                                             |

|                 | <ul><li>0: WWDG window watchdog activated by software</li><li>1: WWDG window watchdog activated by hardware</li></ul>                           |

|                 | WWDG_HALT: Window watchdog reset on Halt                                                                                                        |

|                 | 0: No reset generated on Halt if WWDG active<br>1: Reset generated on Halt if WWDG active                                                       |

|                 | EXTCLK: External clock selection                                                                                                                |

| OPT4            | 0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                              |

|                 | CKAWUSEL: Auto-wakeup unit/clock                                                                                                                |

|                 | 0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU                                            |

|                 | PRSC[1:0]: AWU clock prescaler                                                                                                                  |

|                 | 00: Reserved<br>01: 16 MHz to 128 kHz prescaler                                                                                                 |

|                 | 10: 8 MHz to 128 kHz prescaler                                                                                                                  |

|                 | 11: 4 MHz to 128 kHz prescaler                                                                                                                  |

| 0.075           | HSECNT[7:0]: HSE crystal oscillator stabilization time                                                                                          |

| OPT5            | This configures the stabilization time to 0.5, 8, 128, and 2048 HSE cycles with corresponding option byte values of 0xE1, 0xD2, 0xB4, and 0x00. |

| 0.770           | TMU[3:0]: Enable temporary memory unprotection                                                                                                  |

| OPT6            | 0101: TMU disabled (permanent ROP).<br>Any other value: TMU enabled.                                                                            |

| OPT7            | Reserved                                                                                                                                        |

| OPT8            | TMU_KEY 1 [7:0]: Temporary unprotection key 0<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                |

|                 | TMU_KEY 2 [7:0]: Temporary unprotection key 1                                                                                                   |

| OPT9            | Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                 |

| OPT10           | TMU_KEY 3 [7:0]: Temporary unprotection key 2<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                |

|                 | TMU_KEY 4 [7:0]: Temporary unprotection key 3                                                                                                   |

| OPT11           | Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                 |

Table 16. Option byte description (continued)

| Symbol                               | Ratings                                                                   | Max. | Unit |

|--------------------------------------|---------------------------------------------------------------------------|------|------|

| I <sub>VDDIO</sub>                   | Total current into $V_{DDIO}$ power lines (source) <sup>(1)(2)(3)</sup>   | 100  |      |

| I <sub>VSSIO</sub>                   | Total current out of $V_{SS IO}$ ground lines (sink) <sup>(1)(2)(3)</sup> | 100  |      |

| 1.                                   | Output current sunk by any I/O and control pin                            | 20   | mA   |

| Ι <sub>ΙΟ</sub>                      | Output current source by any I/Os and control pin                         | -20  | IIIA |

| I <sub>INJ(PIN)</sub> <sup>(4)</sup> | Injected current on any pin                                               | ±10  |      |

| I <sub>INJ(TOT)</sub>                | Sum of injected currents                                                  | 50   |      |

#### Table 18. Current characteristics

1. All power (V\_{DD}, V\_{DDIO}, V\_{DDA}) and ground (V\_{SS}, V\_{SSIO}, V\_{SSA}) pins must always be connected to the external supply.

- 2. The total limit applies to the sum of operation and injected currents.

- 3.  $V_{\text{DDIO}}$  includes the sum of the positive injection currents.  $V_{\text{SSIO}}$  includes the sum of the negative injection currents.

- 4. This condition is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current allowed and the corresponding V<sub>IN</sub> maximum must always be respected.

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| TJ               | Maximum junction temperature | 160        | 0    |

## Table 20. Operating lifetime<sup>(1)</sup>

| Symbol | Ratings                      | Value         | Unit    |

|--------|------------------------------|---------------|---------|

| OLF    | Conforming to AEC-Q100 rev G | -40 to 125 °C | Grade 1 |

|        |                              | -40 to 150 °C | Grade 0 |

1. For detailed mission profile analysis, please contact the nearest local ST Sales Office.

## 10.3 Operating conditions

| Table 21. General operating conditions |                                                      |                          |     |      |      |

|----------------------------------------|------------------------------------------------------|--------------------------|-----|------|------|

| Symbol                                 | Parameter                                            | Conditions               | Min | Мах  | Unit |

| f <sub>CPU</sub>                       | Internal CPU clock frequency                         | $T_A$ = -40 °C to 150 °C | 0   | 16   | MHz  |

| V <sub>DD/</sub> V <sub>DDIO</sub>     | Standard operating voltage                           | -                        | 3.0 | 5.5  | V    |

| (1)                                    | C <sub>EXT</sub> : capacitance of external capacitor | -                        | 470 | 3300 | nF   |

| $V_{CAP}^{(1)}$                        | ESR of external capacitor                            | at 1 MHz <sup>(2)</sup>  | -   | 0.3  | Ω    |

|                                        | ESL of external capacitor                            |                          | -   | 15   | nH   |

|                                        | Power dissipation (all temperature ranges)           | LQFP32                   | -   | 85   |      |

| PD                                     |                                                      | VFQFPN32                 | -   | 200  | mW   |

|                                        |                                                      | LQFP48                   | -   | 88   |      |

|                                        |                                                      | Suffix A                 |     | 85   | °C   |

| T <sub>A</sub>                         | Ambient temperature                                  | Suffix C                 |     | 125  |      |

|                                        |                                                      | Suffix D                 | 40  | 150  |      |

| TJ                                     |                                                      | Suffix A                 | -40 | 90   | U    |

|                                        | Junction temperature range                           | Suffix C                 |     | 130  |      |

|                                        |                                                      | Suffix D                 |     | 155  |      |

Table 21. General operating conditions

1. Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter maximum value must be respected for the full application range.

2. This frequency of 1 MHz as a condition for  $V_{CAP}$  parameters is given by design of internal regulator.

## Figure 8. f<sub>CPUmax</sub> versus V<sub>DD</sub>

Figure 16. HSE external clock source

## HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied using a crystal/ceramic resonator oscillator of up to 16 MHz. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Table 29. HSE osci | llator characteristics |

|--------------------|------------------------|

|--------------------|------------------------|

| Symbol                              | Parameter                    | Conditions                       | Min | Тур | Мах | Unit |

|-------------------------------------|------------------------------|----------------------------------|-----|-----|-----|------|

| R <sub>F</sub>                      | Feedback resistor            | -                                | -   | 220 | -   | kΩ   |

| $C_{L1}/C_{L2}^{(1)}$               | Recommended load capacitance | -                                | -   | -   | 20  | pF   |

| 9 <sub>m</sub>                      | Oscillator transconductance  | -                                | 5   | -   | -   | mA/V |

| t <sub>SU(HSE)</sub> <sup>(2)</sup> | Startup time                 | V <sub>DD</sub> is<br>stabilized | -   | 2.8 | -   | ms   |

1. The oscillator needs two load capacitors,  $C_{L1}$  and  $C_{L2}$ , to act as load for the crystal. The total load capacitance ( $C_{load}$ ) is  $(C_{L1} * C_{L2})/(C_{L1} + C_{L2})$ . If  $C_{L1} = C_{L2}$ ,  $C_{load} = C_{L1} / 2$ . Some oscillators have built-in load capacitors,  $C_{L1}$  and  $C_{L2}$ .

2. This value is the startup time, measured from the moment it is enabled (by software) until a stabilized 16 MHz oscillation is reached. It can vary with the crystal type that is used.

## 10.3.8 TIM 1, 2, 3, and 4 timer specifications

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Table 37. TIM 1 | 2, 3, and 4 electrical specified | ications |

|-----------------|----------------------------------|----------|

|-----------------|----------------------------------|----------|

| Symbol           | Parameter                                     | Conditions | Min | Тур | Max | Unit |

|------------------|-----------------------------------------------|------------|-----|-----|-----|------|

| f <sub>EXT</sub> | Timer external clock frequency <sup>(1)</sup> | -          | -   | -   | 16  | MHz  |

1. Not tested in production. On 64 Kbyte devices, the frequency is limited to 16 MHz.

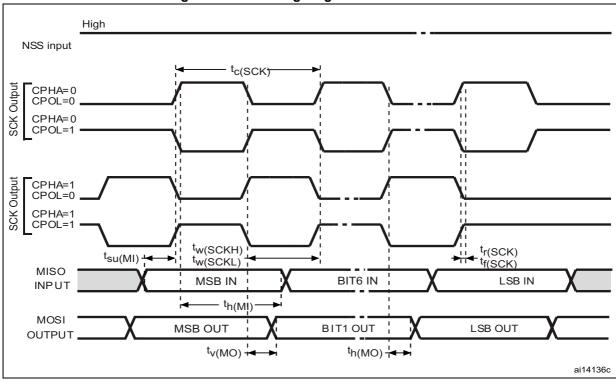

## 10.3.9 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 38* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                                  | Conditions                      |                                  | Min                      | Мах                      | Unit |

|----------------------------------------------------------------------------|--------------------------------------------|---------------------------------|----------------------------------|--------------------------|--------------------------|------|

|                                                                            |                                            | Master mode                     |                                  | 0                        | 10                       |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency                        | Slave mode                      | V <sub>DD</sub> < 4.5 V          | 0                        | 6 <sup>(1)</sup>         | MHz  |

|                                                                            |                                            | Slave mode                      | V <sub>DD</sub> = 4.5 V to 5.5 V | 0                        | 8 <sup>(1)</sup>         |      |

| t <sub>r(SCK</sub> )<br>t <sub>f(SCK)</sub>                                | SPI clock rise and fall time               | Capacitive load: C =            | = 30 pF                          | -                        | 25 <sup>(2)</sup>        |      |

| t <sub>su(NSS)</sub> <sup>(3)</sup>                                        | NSS setup time                             | Slave mode                      |                                  | 4 * t <sub>MASTER</sub>  | -                        |      |

| t <sub>h(NSS)</sub> <sup>(3)</sup>                                         | NSS hold time                              | Slave mode                      |                                  | 70                       | -                        |      |

| t <sub>w(SCKH)</sub> <sup>(3)</sup><br>t <sub>w(SCKL)</sub> <sup>(3)</sup> | SCK high and low time                      | Master mode                     |                                  | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |

| t <sub>su(MI)</sub> (3)                                                    | Data input setup time                      | Master mode                     |                                  | 5                        | -                        |      |

| $t_{su(SI)}^{(3)}$                                                         | Data input setup time                      | Slave mode                      |                                  | 5                        | -                        |      |

| t <sub>h(MI)</sub> <sup>(3)</sup><br>t <sub>h(SI)</sub> <sup>(3)</sup>     | Data input hold time                       | Master mode                     |                                  | 7                        | -                        | ns   |

| $t_{h(SI)}^{(3)}$                                                          |                                            | Slave mode                      |                                  | 10                       | -                        |      |

| t <sub>a(SO)</sub> (3)(4)                                                  | Data output access time                    | Slave mode                      |                                  | -                        | 3* t <sub>MASTER</sub>   |      |

| t <sub>dis(SO)</sub> <sup>(3)(5)</sup>                                     | Data output disable time                   | Slave mode                      |                                  | 25                       |                          |      |

| + (3)                                                                      | (SO) <sup>(3)</sup> Data output valid time | Slave mode                      | V <sub>DD</sub> < 4.5 V          | -                        | 75                       |      |

| t <sub>v(SO)</sub> (°)                                                     |                                            | (after enable edge)             | V <sub>DD</sub> = 4.5 V to 5.5 V | -                        | 53                       | 1    |

| t <sub>v(MO)</sub> <sup>(3)</sup>                                          | Data output valid time                     | Master mode (after enable edge) |                                  | -                        | 30                       |      |

| t <sub>h(SO)</sub> <sup>(3)</sup>                                          | Data output hold time                      | Slave mode (after enable edge)  |                                  | 31                       | -                        |      |

| t <sub>h(MO)</sub> <sup>(3)</sup>                                          | Data output hold time                      | Master mode (after              | enable edge)                     | 12                       | -                        |      |

| Table 38. SPI ch | aracteristics |

|------------------|---------------|

|------------------|---------------|

1.  $f_{SCK} < f_{MASTER}/2$ .

2. The pad has to be configured accordingly (fast mode).

Figure 39. SPI timing diagram - master mode

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

## 10.3.12 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                         | Level/class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, T <sub>A</sub> = 25 °C,<br>f <sub>MASTER</sub> = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-2 | 3/B         |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>f <sub>MASTER</sub> = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-4          | 4/A         |

| Table | 12  | EMC | data |

|-------|-----|-----|------|

| rable | 4Z. |     | uala |

## **Electromagnetic interference (EMI)**

Emission tests conform to the IEC 61967-2 standard for test software, board layout and pin loading.

| Symbol           |                   | Conditions                                |                   |                                     |           |      |

|------------------|-------------------|-------------------------------------------|-------------------|-------------------------------------|-----------|------|

|                  | Parameter         |                                           | Monitored         | Max f <sub>CPU</sub> <sup>(1)</sup> |           | Unit |

|                  |                   | General conditions                        | frequency band    | 8<br>MHz                            | 16<br>MHz |      |

| S <sub>EMI</sub> |                   | V <sub>DD</sub> = 5 V,                    | 0.1 MHz to 30 MHz | 15                                  | 17        |      |

|                  | Peak level        | T <sub>A</sub> = 25 °C,<br>LQFP80 package | 30 MHz to 130 MHz | 18                                  | 22        | dBµV |

|                  | conforming to IEC |                                           | 130 MHz to 1 GHz  | -1                                  | 3         | ubμv |

|                  | EMI level         | 61967-2                                   | -                 | 2                                   | 2.5       | ]    |

| Table 4 | 13. E | EMI c | lata |

|---------|-------|-------|------|

|---------|-------|-------|------|

1. Data based on characterization results, not tested in production.

### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

## Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Table 44. | ESD abs | olute maximum | ratings |

|-----------|---------|---------------|---------|

|-----------|---------|---------------|---------|

| Symbol                | Ratings                                               | Conditions                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model) | $T_A = 25^{\circ}C$ , conforming to JESD22-A114     | ЗA    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | $T_A = 25^{\circ}C$ , conforming to JESD22-C101     | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (Machine model)       | T <sub>A</sub> = 25°C, conforming to<br>JESD22-A115 | В     | 200                             |      |

1. Data based on characterization results, not tested in production

### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |  |

|--------|-----------------------|-------------------------|----------------------|--|

| LU     |                       | $T_A = 25 \ ^\circ C$   |                      |  |

|        | Static latch-up class | T <sub>A</sub> = 85 °C  |                      |  |

|        |                       | T <sub>A</sub> = 125 °C | A                    |  |

|        |                       | T <sub>A</sub> = 150 °C |                      |  |

| Table 4 | 5. Electrical | sensitivities |

|---------|---------------|---------------|

|---------|---------------|---------------|

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

## 11.4 Thermal characteristics

In case the maximum chip junction temperature (T<sub>Jmax</sub>) specified in *Table 21: General operating conditions on page 52* is exceeded, the functionality of the device cannot be guaranteed.

$T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

Where:

- $T_{Amax}$  is the maximum ambient temperature in  $^{\circ}C$

- O<sub>JA</sub> is the package junction-to-ambient thermal resistance in ° C/W

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax} (P_{Dmax} = P_{INTmax} + P_{I/Omax})$

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins Where:

$\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma \; (\mathsf{V}_\mathsf{OL} * \mathsf{I}_\mathsf{OL}) + \Sigma ((\mathsf{V}_\mathsf{DD} - \mathsf{V}_\mathsf{OH}) * \mathsf{I}_\mathsf{OH}),$

taking into account the actual  $V_{OL}/I_{OL}$  and  $V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                 | Value | Unit |

|---------------|-----------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 48 - 7 x 7 mm | 57    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 32 - 7 x 7 mm | 59    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>VFQFPN32           | 25    | °C/W |

Table 49. Thermal characteristics<sup>(1)</sup>

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

## 11.4.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

## 11.4.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the order code (see *Section 12: Ordering information*).

The following example shows how to calculate the temperature range needed for a given application.

## 13 STM8 development tools

Development tools for the STM8A microcontrollers include the

- STice emulation system offering tracing and code profiling

- STVD high-level language debugger including assembler and visual development environment seamless integration of third party C compilers.

- STVP Flash programming software

In addition, the STM8A comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

## 13.1 Emulation and in-circuit debugging tools

The STM8 tool line includes the STice emulation system offering a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8A application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full-featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including tracing, profiling and code coverage analysis to help detect execution bottlenecks and dead code.

In addition, STice offers in-circuit debugging and programming of STM8A microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows users to order exactly what they need to meet their development requirements and to adapt their emulation system to support existing and future ST microcontrollers.

## 13.1.1 STice key features

- Program and data trace recording up to 128 K records

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Real-time read/write of all device resources during emulation

- Occurrence and time profiling and code coverage analysis (new features)

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- USB 2.0 high speed interface to host PC

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows users to specify the components they need to meet their development requirements and adapt to future requirements.

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

# 14 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Aug-2008 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10-Aug-2009 | 2        | Document revised as the following:<br>Updated <i>Features</i> ;<br>Updated <i>Table: Device summary</i> ;<br>Updated <i>Section: Product line-up</i> ;<br>Changed <i>Section: Product overview</i> ;<br>Updated <i>Section: Pinouts and pin description</i> ;<br>Changed <i>Section: Register map</i> ;<br>Updated <i>Section: Register map</i> ;<br>Updated <i>Section: Interrupt table</i> ;<br>Updated <i>Section: Option bytes</i> ;<br>Updated <i>Section: Electrical characteristics</i> ;<br>Updated <i>Section: Package information</i> ;<br>Updated <i>Section: Ordering information</i> ;<br>Added <i>Section: STM8 development tools</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22-Oct-2009 | 3        | Adapted Table: STM8AF61xx/62xx (32 Kbyte) microcontroller pin<br>description.<br>Added Section: LIN header error when automatic resynchronization<br>is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 08-Jul-2010 | 4        | Updated title on cover page.<br>Added VFQFPN32 5x 5 mm package.<br>Added STM8AF62xx devices, and modified cover page header to<br>clarify the part numbers covered by the datasheets. Updated <i>Note 1</i><br>below <i>Table: Device summary.</i><br>Updated D temperature range to -40 to 150°C.<br>Content of <i>Section: Product overview</i> reorganized.<br>Renamed <i>Section: Memory and register map</i> , and content merged<br>with Register map section.<br>Renamed BL_EN and NBL_EN, BL and NBL, respectively, in <i>Table:</i><br><i>Option bytes.</i><br>Added <i>Table: Operating lifetime.</i><br>Added CEXT and P <sub>D</sub> (power dissipation) in <i>Table: General operating</i><br><i>conditions</i> , and <i>Section: VCAP external capacitor.</i><br>Suffix D maximum junction temperature (T <sub>J</sub> ) updated in <i>Table:</i><br><i>General operating conditions.</i><br>Update tvDD in <i>Table: Operating conditions at power-up/power-down.</i><br>Moved <i>Table: Typical peripheral current consumption VDD = 5.0 V</i> to<br><i>Section: Current consumption for on-chip peripherals</i> and removed<br>I <sub>DD(CAN)</sub> .<br>Updated <i>Section: STM8 development tools.</i> |

## Table 50. Document revision history

| Date        |                  | Table 50. Document revision history (continued)       Revision       Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date        | 1764121011       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|             | 5<br>(continued) | Renamed Fast Active Halt mode to Active-halt mode with regulator<br>on, and Slow Active Halt mode to Active-halt mode with regulator off.<br>Updated <i>Table: Total current consumption in Halt and Active-halt</i><br><i>modes. General conditions for VDD apply, TA</i> = -40 to 55 °C, in<br>particular I <sub>DD(FAH)</sub> and I <sub>DD(SAH)</sub> renamed I <sub>DD(AH)</sub> ; t <sub>WU(FAH)</sub> and<br>t <sub>WU(SAH)</sub> renamed t <sub>WU(AH)</sub> , and temperature condition added.<br>Removed I <sub>DD(USART)</sub> from <i>Table: Typical peripheral current</i><br><i>consumption VDD</i> = 5.0 V. |  |  |

| 31-Jan-2011 |                  | Updated general conditions in <i>Section: Memory characteristics</i> .<br>Modified $T_{WE}$ maximum value in <i>Table: Flash program memory</i> and <i>Table: Data memory</i> .<br>Update $I_{lkg ana}$ maximum value for $T_A$ ranging from -40 to 150 °C in                                                                                                                                                                                                                                                                                                                                                              |  |  |

|             |                  | Table: I/O static characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|             |                  | Added $t_{IFP(NRST)}$ and renamed $V_{F(NRST)} t_{IFP}$ in <i>Table: NRST pin characteristics</i> . Added recommendations concerning NRST pin level above <i>Figure: Recommended reset pin protection,</i> and updated external capacitor value.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|             |                  | Added Raisonance compiler in Section: Software tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|             |                  | Moved know limitations to separate errata sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|             |                  | Updated wildcards of document part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|             |                  | <i>Table: Device summary: u</i> pdated the footnotes to all STM8AF61xx part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|             |                  | Section: Introduction: small text change in first paragraph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|             | 2 6              | <i>Table:</i> STM8AF62xx product line-up: added "P" version for all order codes; updated RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|             |                  | <i>Table: STM8AF/H61xx product line-up</i> : added "P" version for all order codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|             |                  | <i>Figure: STM8A block diagram</i> : updated POR, BOR and WDG; updated LINUART input; added legend.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|             |                  | Section: Flash program and data EEPROM: removed non relevant bullet points and added a sentence about the factory programmer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 18-Jul-2012 |                  | Table: Peripheral clock gating bit assignments in CLK_PCKENR1/2 registers: updated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|             |                  | ADC features: updated ADC input range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|             |                  | <i>Table: Memory model for the devices covered in this datasheet:</i> updated 16 Kbyte and 8 Kbyte information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |