Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | •                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6266uay |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |       | 10.3.7                | Reset pin characteristics                  |

|----|-------|-----------------------|--------------------------------------------|

|    |       | 10.3.8                | TIM 1, 2, 3, and 4 timer specifications    |

|    |       | 10.3.9                | SPI serial peripheral interface69          |

|    |       | 10.3.10               | I <sup>2</sup> C interface characteristics |

|    |       | 10.3.11               | 10-bit ADC characteristics                 |

|    |       | 10.3.12               | EMC characteristics                        |

| 11 | Pack  | age info              | ormation                                   |

|    | 11.1  | VFQFP                 | N32 package information 78                 |

|    | 11.2  | LQFP4                 | 8 package information                      |

|    | 11.3  | LQFP3                 | 2 package information                      |

|    | 11.4  | Therma                | Il characteristics                         |

|    |       | 11.4.1                | Reference document88                       |

|    |       | 11.4.2                | Selecting the product temperature range    |

| 12 | Orde  | ring info             | ormation                                   |

| 13 | STM   | 8 develo              | pment tools                                |

|    | 13.1  | Emulati               | on and in-circuit debugging tools          |

|    |       | 13.1.1                | STice key features                         |

|    | 13.2  | Softwar               | re tools                                   |

|    |       | 13.2.1                | STM8 toolset                               |

|    |       | 13.2.2                | C and assembly toolchains92                |

|    | 13.3  | Prograr               | nming tools                                |

| 14 | Revis | sion his <sup>.</sup> | tory                                       |

|    |       |                       | -                                          |

## 1 Introduction

This datasheet refers to the STM8AF6246, STM8AF6248, STM8AF6266 and STM8AF6268 products with 16 to 32 Kbyte of Flash program memory.

In the order code, the letter 'F' refers to product versions with data EEPROM and 'H' refers to product versions without data EEPROM. The identifiers 'F' and 'H' do not coexist in a given order code.

The datasheet contains the description of family features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8 Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

# 3 Product line-up

| Order code   | Package         | Medium<br>density<br>Flash<br>program<br>memory<br>(byte) | RAM<br>(byte) | Data EE<br>(byte) | 10-bit<br>A/D ch. | Timers<br>(IC/OC/PWM)                    | Serial<br>interfaces   | l/0<br>wakeup<br>pins |

|--------------|-----------------|-----------------------------------------------------------|---------------|-------------------|-------------------|------------------------------------------|------------------------|-----------------------|

| STM8AF/P6268 | LQFP48          | 32 K                                                      |               | 1 K               |                   | 1x8-bit: TIM4<br>3x16-bit: TIM1,         | LIN(UART),             |                       |

| STM8AF/P6248 | (7x7)           | 16 K                                                      |               | 0.5 K             | 10                | TIM2, TIM3<br>(9/9/9)                    | SPI, I <sup>2</sup> C  | 38/35                 |

| STM8AF/P6266 | 32 K            |                                                           | 1 K           |                   | 1x8-bit: TIM4     |                                          |                        |                       |

| STM8AF/P6246 | LQFP32<br>(7x7) | 16 K                                                      | 2 K           | 0.5 K             | 7                 | 3x16-bit: TIM1,<br>TIM2, TIM3<br>(8/8/8) | LIN(UART),<br>SPI, I²C | 25/23                 |

| STM8AF/P6266 |                 | 32 K                                                      |               | 1 K               |                   | 1x8-bit: TIM4                            |                        |                       |

| STM8AF/P6246 | VFQFPN32        | 16 K                                                      |               | 0.5 K             | 7                 | 3x16-bit: TIM1,<br>TIM2, TIM3<br>(8/8/8) | LIN(UART),<br>SPI, I²C | 25/23                 |

### Table 1. STM8AF6246/48/66/68 product line-up

## 5.6 Low-power operating modes

For efficient power management, the application can be put in one of four different low power modes. Users can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

Wait mode

In this mode, the CPU is stopped but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

• Active-halt mode with regulator on

In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in Active-halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

• Active-halt mode with regulator off

This mode is the same as Active-halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

Halt mode

CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

In all modes the CPU and peripherals remain permanently powered on, the system clock is applied only to selected modules. The RAM content is preserved and the brown-out reset circuit remains activated.

## 5.7 Timers

### 5.7.1 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications. The watchdog timer activity is controlled by the application program or option bytes. Once the watchdog is activated, it cannot be disabled by the user program without going through reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application timing perfectly. The application software must refresh the counter before time-out and during a limited time window. If the counter is refreshed outside this time window, a reset is issued.

### 5.9.1 Serial peripheral interface (SPI)

The devices covered by this datasheet contain one SPI. The SPI is available on all the supported packages.

- Maximum speed: 10 Mbit/s or f<sub>MASTER</sub>/2 both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave mode/master mode management by hardware or software for both master and slave

- Programmable clock polarity and phase

- Programmable data order with MSB-first or LSB-first shifting

- Dedicated transmission and reception flags with interrupt capability

- SPI bus busy status flag

- Hardware CRC feature for reliable communication:

- CRC value can be transmitted as last byte in Tx mode

- CRC error checking for last received byte

## 5.9.2 Inter integrated circuit (I<sup>2</sup>C) interface

The devices covered by this datasheet contain one  $I^2C$  interface. The interface is available on all the supported packages.

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

- Status flags:

- Transmitter/receiver mode flag

- End-of-byte transmission flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost condition for master mode

- Acknowledgment failure after address/data transmission

- Detection of misplaced start or stop condition

- Overrun/underrun if clock stretching is disabled

## 6 Pinouts and pin description

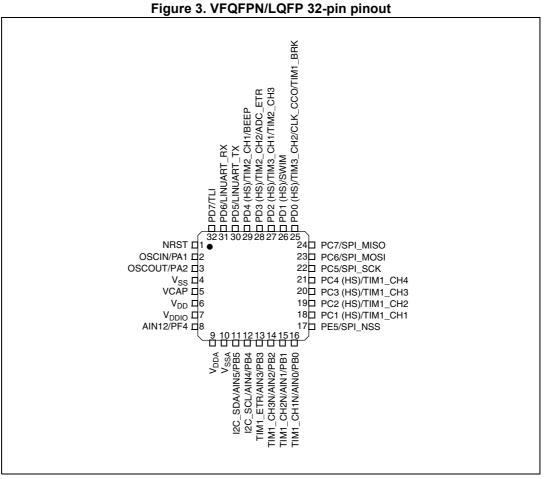

## 6.1 Package pinouts

1. (HS) high sink capability.

| Address                   | Block                    | Register label | Register name                   | Reset<br>status |  |  |

|---------------------------|--------------------------|----------------|---------------------------------|-----------------|--|--|

| 0x00 50F3                 | BEEP                     | BEEP_CSR       | BEEP control/status register    | 0x1F            |  |  |

| 0x00 50F4 to<br>0x00 50FF |                          | Re             | eserved area (12 bytes)         |                 |  |  |

| 0x00 5200                 |                          | SPI_CR1        | SPI control register 1          | 0x00            |  |  |

| 0x00 5201                 |                          | SPI_CR2        | SPI control register 2          | 0x00            |  |  |

| 0x00 5202                 |                          | SPI_ICR        | SPI interrupt control register  | 0x00            |  |  |

| 0x00 5203                 | SPI                      | SPI_SR         | SPI status register             | 0x02            |  |  |

| 0x00 5204                 |                          | SPI_DR         | SPI data register               | 0x00            |  |  |

| 0x00 5205                 |                          | SPI_CRCPR      | SPI CRC polynomial register     | 0x07            |  |  |

| 0x00 5206                 |                          | SPI_RXCRCR     | SPI Rx CRC register             | 0xFF            |  |  |

| 0x00 5207                 |                          | SPI_TXCRCR     | SPI Tx CRC register             | 0xFF            |  |  |

| 0x00 5208 to<br>0x00 520F | Reserved area (8 bytes)  |                |                                 |                 |  |  |

| 0x00 5210                 |                          | I2C_CR1        | I2C control register 1          | 0x00            |  |  |

| 0x00 5211                 |                          | I2C_CR2        | I2C control register 2          | 0x00            |  |  |

| 0x00 5212                 |                          | I2C_FREQR      | I2C frequency register          | 0x00            |  |  |

| 0x00 5213                 |                          | I2C_OARL       | I2C own address register low    | 0x00            |  |  |

| 0x00 5214                 |                          | I2C_OARH       | I2C own address register high   | 0x00            |  |  |

| 0x00 5215                 |                          |                | Reserved area (1 byte)          |                 |  |  |

| 0x00 5216                 | I2C                      | I2C_DR         | I2C data register               | 0x00            |  |  |

| 0x00 5217                 | 120                      | I2C_SR1        | I2C status register 1           | 0x00            |  |  |

| 0x00 5218                 |                          | I2C_SR2        | I2C status register 2           | 0x00            |  |  |

| 0x00 5219                 |                          | I2C_SR3        | I2C status register 3           | 0x00            |  |  |

| 0x00 521A                 |                          | I2C_ITR        | I2C interrupt control register  | 0x00            |  |  |

| 0x00 521B                 |                          | I2C_CCRL       | I2C clock control register low  | 0x00            |  |  |

| 0x00 521C                 |                          | I2C_CCRH       | I2C clock control register high | 0x00            |  |  |

| 0x00 521D                 |                          | I2C_TRISER     | I2C TRISE register              | 0x02            |  |  |

| 0x00 521E to<br>0x00 523F | Reserved area (24 bytes) |                |                                 |                 |  |  |

#### Table 11. General hardware register map (continued)

|                           | Table 11. General hardware register map (continued) |                         |                                           |                 |  |  |  |  |

|---------------------------|-----------------------------------------------------|-------------------------|-------------------------------------------|-----------------|--|--|--|--|

| Address                   | Block                                               | Register label          | Register name                             | Reset<br>status |  |  |  |  |

| 0x00 5240                 |                                                     | UART2_SR                | LINUART status register                   | 0xC0            |  |  |  |  |

| 0x00 5241                 |                                                     | UART2_DR                | LINUART data register                     | 0xXX            |  |  |  |  |

| 0x00 5242                 |                                                     | UART2_BRR1              | LINUART baud rate register 1              | 0x00            |  |  |  |  |

| 0x00 5243                 |                                                     | UART2_BRR2              | LINUART baud rate register 2              | 0x00            |  |  |  |  |

| 0x00 5244                 | LINUART                                             | UART2_CR1               | LINUART control register 1                | 0x00            |  |  |  |  |

| 0x00 5245                 |                                                     | UART2_CR2               | LINUART control register 2                | 0x00            |  |  |  |  |

| 0x00 5246                 |                                                     | UART2_CR3               | LINUART control register 3                | 0x00            |  |  |  |  |

| 0x00 5247                 |                                                     | UART2_CR4               | LINUART control register 4                | 0x00            |  |  |  |  |

| 0x00 5248                 |                                                     |                         | Reserved                                  |                 |  |  |  |  |

| 0x00 5249                 |                                                     | UART2_CR6               | LINUART control register 6                | 0x00            |  |  |  |  |

| 0x00 524A to<br>0x00 524F |                                                     | Reserved area (6 bytes) |                                           |                 |  |  |  |  |

| 0x00 5250                 |                                                     | TIM1_CR1                | TIM1 control register 1                   | 0x00            |  |  |  |  |

| 0x00 5251                 |                                                     | TIM1_CR2                | TIM1 control register 2                   | 0x00            |  |  |  |  |

| 0x00 5252                 |                                                     | TIM1_SMCR               | TIM1 slave mode control register          | 0x00            |  |  |  |  |

| 0x00 5253                 |                                                     | TIM1_ETR                | TIM1 external trigger register            | 0x00            |  |  |  |  |

| 0x00 5254                 |                                                     | TIM1_IER                | TIM1 Interrupt enable register            | 0x00            |  |  |  |  |

| 0x00 5255                 |                                                     | TIM1_SR1                | TIM1 status register 1                    | 0x00            |  |  |  |  |

| 0x00 5256                 |                                                     | TIM1_SR2                | TIM1 status register 2                    | 0x00            |  |  |  |  |

| 0x00 5257                 |                                                     | TIM1_EGR                | TIM1 event generation register            | 0x00            |  |  |  |  |

| 0x00 5258                 |                                                     | TIM1_CCMR1              | TIM1 capture/compare mode register 1      | 0x00            |  |  |  |  |

| 0x00 5259                 |                                                     | TIM1_CCMR2              | TIM1 capture/compare mode register 2      | 0x00            |  |  |  |  |

| 0x00 525A                 |                                                     | TIM1_CCMR3              | TIM1 capture/compare mode register 3      | 0x00            |  |  |  |  |

| 0x00 525B                 | TIM1                                                | TIM1_CCMR4              | TIM1 capture/compare mode register 4      | 0x00            |  |  |  |  |

| 0x00 525C                 |                                                     | TIM1_CCER1              | TIM1 capture/compare enable register<br>1 | 0x00            |  |  |  |  |

| 0x00 525D                 |                                                     | TIM1_CCER2              | TIM1 capture/compare enable register 2    | 0x00            |  |  |  |  |

| 0x00 525E                 |                                                     | TIM1_CNTRH              | TIM1 counter high                         | 0x00            |  |  |  |  |

| 0x00 525F                 |                                                     | TIM1_CNTRL              | TIM1 counter low                          | 0x00            |  |  |  |  |

| 0x00 5260                 |                                                     | TIM1_PSCRH              | TIM1 prescaler register high              | 0x00            |  |  |  |  |

| 0x00 5261                 |                                                     | TIM1_PSCRL              | TIM1 prescaler register low               | 0x00            |  |  |  |  |

| 0x00 5262                 |                                                     | TIM1_ARRH               | TIM1 auto-reload register high            | 0xFF            |  |  |  |  |

| 0x00 5263                 |                                                     | TIM1_ARRL               | TIM1 auto-reload register low             | 0xFF            |  |  |  |  |

| 0x00 5264                 |                                                     | TIM1_RCR                | TIM1 repetition counter register          | 0x00            |  |  |  |  |

Table 11. General hardware register map (continued)

## 8 Interrupt table

| Table 14. STM8A Interrupt table |                         |                                                  |                             |                     |                   |  |

|---------------------------------|-------------------------|--------------------------------------------------|-----------------------------|---------------------|-------------------|--|

| Priority                        | Source<br>block         | Description                                      | Interrupt vector<br>address | Wakeup<br>from Halt | Comments          |  |

| -                               | Reset                   | Reset                                            | 0x00 8000                   | Yes                 | User RESET vector |  |

| -                               | TRAP                    | SW interrupt                                     | 0x00 8004                   | -                   | -                 |  |

| 0                               | TLI                     | External top level interrupt                     | 0x00 8008                   | -                   | -                 |  |

| 1                               | AWU                     | Auto-wakeup from Halt                            | 0x00 800C                   | Yes                 | -                 |  |

| 2                               | Clock<br>controller     | Main clock controller                            | 0x00 8010                   | -                   | -                 |  |

| 3                               | MISC                    | Ext interrupt E0                                 | 0x00 8014                   | Yes                 | Port A interrupts |  |

| 4                               | MISC                    | Ext interrupt E1                                 | 0x00 8018                   | Yes                 | Port B interrupts |  |

| 5                               | MISC                    | Ext interrupt E2                                 | 0x00 801C                   | Yes                 | Port C interrupts |  |

| 6                               | MISC                    | Ext interrupt E3                                 | 0x00 8020                   | Yes                 | Port D interrupts |  |

| 7                               | MISC                    | Ext interrupt E4                                 | 0x00 8024                   | Yes                 | Port E interrupts |  |

| 8                               | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 9                               | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 10                              | SPI                     | End of transfer                                  | 0x00 8030                   | Yes                 | -                 |  |

| 11                              | Timer 1                 | Update/overflow/<br>trigger/break                | 0x00 8034                   | -                   | -                 |  |

| 12                              | Timer 1                 | Capture/compare                                  | 0x00 8038                   | -                   | -                 |  |

| 13                              | Timer 2                 | Update/overflow                                  | 0x00 803C                   | -                   | -                 |  |

| 14                              | Timer 2                 | Capture/compare                                  | 0x00 8040                   | -                   | -                 |  |

| 15                              | Timer 3                 | Update/overflow                                  | 0x00 8044                   | -                   | -                 |  |

| 16                              | Timer 3                 | Capture/compare                                  | 0x00 8048                   | -                   | -                 |  |

| 17                              | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 18                              | Reserved <sup>(1)</sup> | -                                                | -                           | -                   | -                 |  |

| 19                              | l <sup>2</sup> C        | I <sup>2</sup> C interrupts                      | 0x00 8054                   | Yes                 | -                 |  |

| 20                              | LINUART                 | Tx complete/error                                | 0x00 8058                   | -                   | -                 |  |

| 21                              | LINUART                 | Receive data full reg.                           | 0x00 805C                   | -                   | -                 |  |

| 22                              | ADC                     | End of conversion                                | 0x00 8060                   | -                   | -                 |  |

| 23                              | Timer 4                 | Update/overflow                                  | 0x00 8064                   | -                   | -                 |  |

| 24                              | EEPROM                  | End of Programming/<br>Write in not allowed area | 0x00 8068                   | -                   | -                 |  |

#### Table 14. STM8A interrupt table

1. All reserved and unused interrupts must be initialized with 'IRET' for robust programming.

## 9 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated block of the memory. Each option byte has to be stored twice, for redundancy, in a regular form (OPTx) and a complemented one (NOPTx), except for the ROP (read-out protection) option byte and option bytes 8 to 16.

Option bytes can be modified in ICP mode (via SWIM) by accessing the EEPROM address shown in *Table 15: Option bytes* below.

Option bytes can also be modified 'on the fly' by the application in IAP mode, except the ROP and UBC options that can only be toggled in ICP mode (via SWIM).

Refer to the STM8 Flash programming manual (PM0051) and STM8 SWIM communication protocol and debug module user manual (UM0470) for information on SWIM programming procedures.

| Addr.        | Option                          | Option   |           | Option bits       |           |           |             | Factory default |              |               |         |

|--------------|---------------------------------|----------|-----------|-------------------|-----------|-----------|-------------|-----------------|--------------|---------------|---------|

| Auur.        | name                            | byte no. | 7         | 6                 | 5         | 4         | 3           | 2               | 1            | 0             | setting |

| 0x00<br>4800 | Read-out<br>protection<br>(ROP) | OPT0     |           | ROP[7:0]          |           |           |             |                 |              | 0x00          |         |

| 0x00<br>4801 | User boot                       | OPT1     | Rese      | Reserved UBC[5:0] |           |           |             | 0x00            |              |               |         |

| 0x00<br>4802 | (UBC)                           | NOPT1    | Rese      | Reserved          |           |           |             | C[5:0]          |              |               | 0xFF    |

| 0x00<br>4803 | Alternate<br>function           | OPT2     | AFR7      | AFR6              | AFR5      | AFR4      | AFR3        | AFR2            | AFR1         | AFR0          | 0x00    |

| 0x00<br>4804 | remapping<br>(AFR)              | NOPT2    | NAFR<br>7 | NAFR<br>6         | NAFR<br>5 | NAFR<br>4 | NAFR<br>3   | NAFR<br>2       | NAFR<br>1    | NAFR<br>0     | 0xFF    |

| 0x00<br>4805 | Watchdog                        | OPT3     |           | Reserved          |           |           | LSI<br>_EN  | IWDG<br>_HW     | WWDG<br>_HW  | WWDG<br>_HALT | 0x00    |

| 0x00<br>4806 | option                          | NOPT3    |           |                   |           |           | NLSI<br>_EN | NIWDG<br>_HW    | NWWD<br>G_HW | NWWG<br>_HALT | 0xFF    |

| 0x00<br>4807 | Clock                           | OPT4     |           | Reserved          |           |           |             | CKAWU<br>SEL    | PRS<br>C1    | PRS<br>C0     | 0x00    |

| 0x00<br>4808 | option                          | NOPT4    | Reserved  |                   |           |           | NEXT<br>CLK | NCKAW<br>USEL   | NPR<br>SC1   | NPR<br>SC0    | 0xFF    |

| 0x00<br>4809 | HSE clock                       | OPT5     |           | HSECNT[7:0]       |           |           |             |                 |              | 0x00          |         |

| 0x00<br>480A | startup                         | NOPT5    |           |                   |           | NHSE      | CNT[7:0]    |                 |              |               | 0xFF    |

#### Table 15. Option bytes

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT12           | TMU_KEY 5 [7:0]: Temporary unprotection key 4<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                           |

| OPT13           | TMU_KEY 6 [7:0]: Temporary unprotection key 5           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |

| OPT14           | TMU_KEY 7 [7:0]: Temporary unprotection key 6           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |

| OPT15           | TMU_KEY 8 [7:0]: Temporary unprotection key 7           Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                                                                                                                                                                                                                    |

| OPT16           | TMU_MAXATT [7:0]: TMU access failure counter         TMU_MAXATT can be initialized with the desired value only if TMU is disabled (TMU[3:0]=0101 in OPT6 option byte).         When TMU is enabled, any attempt to temporary remove the readout protection by using wrong key values increments the counter.         When the option byte value reaches 0x08, the Flash memory and data EEPROM are erased. |

| OPT17           | BL [7:0]: Bootloader enable<br>If this option byte is set to 0x55 (complementary value 0xAA) the<br>bootloader program is activated also in case of a programmed code<br>memory<br>(for more details, see the bootloader user manual, UM0560).                                                                                                                                                             |

#### Table 16. Option byte description (continued)

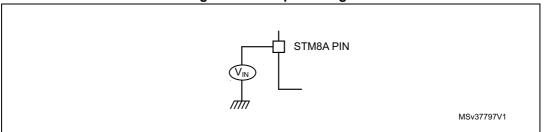

### 10.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 7.

#### Figure 7. Pin input voltage

## 10.2 Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

|                                    | U                                                                 |                       |                                            |      |

|------------------------------------|-------------------------------------------------------------------|-----------------------|--------------------------------------------|------|

| Symbol                             | Ratings                                                           | Min                   | Max                                        | Unit |

| V <sub>DDx</sub> - V <sub>SS</sub> | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                  | 6.5                                        | V    |

| V                                  | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3 | 6.5                                        | V    |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3                      | v    |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           | -                     | 50                                         | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins                  | -                     | 50                                         | IIIV |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   |                       | ite maximum<br>cal sensitivity)<br>page 76 | •    |

Table 17. Voltage characteristics

1. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

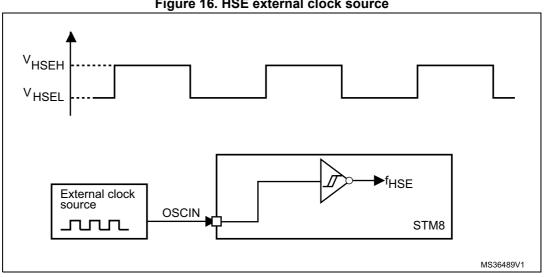

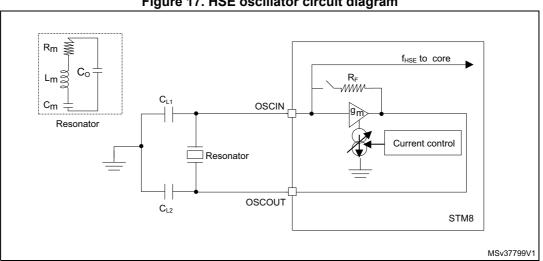

Figure 16. HSE external clock source

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied using a crystal/ceramic resonator oscillator of up to 16 MHz. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Table 29. HSE osci | llator characteristics |

|--------------------|------------------------|

|--------------------|------------------------|

| Symbol                              | Parameter                    | Conditions                       | Min | Тур | Мах | Unit |

|-------------------------------------|------------------------------|----------------------------------|-----|-----|-----|------|

| R <sub>F</sub>                      | Feedback resistor            | -                                | -   | 220 | -   | kΩ   |

| $C_{L1}/C_{L2}^{(1)}$               | Recommended load capacitance | -                                | -   | -   | 20  | pF   |

| 9 <sub>m</sub>                      | Oscillator transconductance  | -                                | 5   | -   | -   | mA/V |

| t <sub>SU(HSE)</sub> <sup>(2)</sup> | Startup time                 | V <sub>DD</sub> is<br>stabilized | -   | 2.8 | -   | ms   |

1. The oscillator needs two load capacitors,  $C_{L1}$  and  $C_{L2}$ , to act as load for the crystal. The total load capacitance ( $C_{load}$ ) is  $(C_{L1} * C_{L2})/(C_{L1} + C_{L2})$ . If  $C_{L1} = C_{L2}$ ,  $C_{load} = C_{L1} / 2$ . Some oscillators have built-in load capacitors,  $C_{L1}$  and  $C_{L2}$ .

2. This value is the startup time, measured from the moment it is enabled (by software) until a stabilized 16 MHz oscillation is reached. It can vary with the crystal type that is used.

Figure 17. HSE oscillator circuit diagram

### HSE oscillator critical g<sub>m</sub> formula

The crystal characteristics have to be checked with the following formula:

g<sub>m</sub> » g<sub>mcrit</sub>

where  $g_{mcrit}$  can be calculated with the crystal parameters as follows:

$$g_{mcrit} = (2 \times \Pi \times {}^{f}HSE)^{2} \times R_{m}(2Co + C)^{2}$$

R<sub>m</sub>: Notional resistance (see crystal specification)

L<sub>m</sub>: Notional inductance (see crystal specification)

C<sub>m</sub>: Notional capacitance (see crystal specification)

Co: Shunt capacitance (see crystal specification)

$C_{1,1} = C_{1,2} = C$ : Grounded external capacitance

#### 10.3.4 Internal clock sources and timing characteristics

Subject to general operating conditions for V<sub>DD</sub> and T<sub>A</sub>.

#### High speed internal RC oscillator (HSI)

| Table 30. HSI oscillator characteristics | Table 30. | HSI | oscillator | characteristics |

|------------------------------------------|-----------|-----|------------|-----------------|

|------------------------------------------|-----------|-----|------------|-----------------|

| Symbol           | Parameter | Conditions | Min | Тур | Мах | Unit |

|------------------|-----------|------------|-----|-----|-----|------|

| f <sub>HSI</sub> | Frequency | -          | -   | 16  | -   | MHz  |

## 10.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

|                         |                                                       | -                      |                             |     |                     |      |

|-------------------------|-------------------------------------------------------|------------------------|-----------------------------|-----|---------------------|------|

| Symbol                  | Parameter                                             | Conditions             | Min                         | Тур | Max                 | Unit |

| V <sub>IL(NRST)</sub>   | NRST input low level voltage <sup>(1)</sup>           | -                      | $V_{SS}$                    | -   | $0.3 \times V_{DD}$ |      |

| V <sub>IH(NRST)</sub>   | NRST input high level voltage <sup>(1)</sup>          | -                      | $0.7 	ext{ x V}_{	ext{DD}}$ | -   | V <sub>DD</sub>     | V    |

| V <sub>OL(NRST)</sub>   | NRST output low level voltage <sup>(1)</sup>          | I <sub>OL</sub> = 3 mA | -                           | -   | 0.6                 |      |

| R <sub>PU(NRST)</sub>   | NRST pull-up resistor                                 | -                      | 30                          | 40  | 60                  | kΩ   |

| t <sub>IFP</sub>        | NRST input filtered pulse <sup>(1)</sup>              | -                      | 85                          | -   | 315                 |      |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse duration <sup>(2)</sup> | -                      | 500                         | -   | -                   | ns   |

1. Data based on characterization results, not tested in production.

2. Data guaranteed by design, not tested in production.

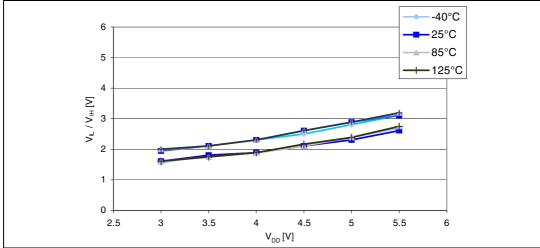

## Figure 33. Typical NRST $V_{IL}$ and $V_{IH}$ vs $V_{DD}$ @ four temperatures

### 10.3.8 TIM 1, 2, 3, and 4 timer specifications

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Table 37. TIM 1 | 2, 3, and 4 electrical specified | ications |

|-----------------|----------------------------------|----------|

|-----------------|----------------------------------|----------|

| Symbol           | Parameter                                     | Conditions | Min | Тур | Max | Unit |

|------------------|-----------------------------------------------|------------|-----|-----|-----|------|

| f <sub>EXT</sub> | Timer external clock frequency <sup>(1)</sup> | -          | -   | -   | 16  | MHz  |

1. Not tested in production. On 64 Kbyte devices, the frequency is limited to 16 MHz.

#### 10.3.9 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 38* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                    | Conditions                                                     |                                  | Min                      | Мах                      | Unit |

|----------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------|----------------------------------|--------------------------|--------------------------|------|

|                                                                            |                              | Master mode                                                    |                                  | 0                        | 10                       |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency          | Slave mode                                                     | V <sub>DD</sub> < 4.5 V          | 0                        | 6 <sup>(1)</sup>         | MHz  |

|                                                                            |                              | Slave mode                                                     | V <sub>DD</sub> = 4.5 V to 5.5 V | 0                        | 8 <sup>(1)</sup>         |      |

| t <sub>r(SCK</sub> )<br>t <sub>f(SCK)</sub>                                | SPI clock rise and fall time | Capacitive load: C = 30 pF                                     |                                  | -                        | 25 <sup>(2)</sup>        |      |

| t <sub>su(NSS)</sub> <sup>(3)</sup>                                        | NSS setup time               | Slave mode                                                     |                                  | 4 * t <sub>MASTER</sub>  | -                        |      |

| t <sub>h(NSS)</sub> <sup>(3)</sup>                                         | NSS hold time                | Slave mode                                                     |                                  | 70                       | -                        |      |

| t <sub>w(SCKH)</sub> <sup>(3)</sup><br>t <sub>w(SCKL)</sub> <sup>(3)</sup> | SCK high and low time        | Master mode                                                    |                                  | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |

| t <sub>su(MI)</sub> (3)                                                    | Data input setup time        | Master mode                                                    |                                  | 5                        | -                        | -    |

| $t_{su(SI)}^{(3)}$                                                         | Data input setup time        | Slave mode                                                     |                                  | 5                        | -                        |      |

| t <sub>h(MI)</sub> (3)                                                     | Data input hold time         | Master mode                                                    |                                  | 7                        | -                        | ns   |

| t <sub>h(MI)</sub> (3)<br>t <sub>h(SI)</sub> (3)                           | Data input hold time         | Slave mode                                                     |                                  | 10                       | -                        |      |

| t <sub>a(SO)</sub> (3)(4)                                                  | Data output access time      | Slave mode                                                     |                                  | -                        | 3* t <sub>MASTER</sub>   |      |

| t <sub>dis(SO)</sub> <sup>(3)(5)</sup>                                     | Data output disable time     | Slave mode                                                     |                                  | 25                       |                          |      |

| + (3)                                                                      | Data autaut valid tima       | Slave mode                                                     | V <sub>DD</sub> < 4.5 V          | -                        | 75                       |      |

| t <sub>v(SO)</sub> <sup>(3)</sup>                                          | Data output valid time       | (after enable edge) $V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}$ |                                  | -                        | 53                       |      |

| t <sub>v(MO)</sub> <sup>(3)</sup>                                          | Data output valid time       | Master mode (after enable edge)                                |                                  | -                        | 30                       |      |

| t <sub>h(SO)</sub> <sup>(3)</sup>                                          | Data output hold time        | Slave mode (after e                                            | nable edge)                      | 31                       | -                        |      |

| t <sub>h(MO)</sub> <sup>(3)</sup>                                          | Data output hold time        | Master mode (after enable edge)                                |                                  | 12                       | -                        |      |

| Table 38. SPI ch | aracteristics |

|------------------|---------------|

|------------------|---------------|

1.  $f_{SCK} < f_{MASTER}/2$ .

2. The pad has to be configured accordingly (fast mode).

### 10.3.12 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                         | Level/class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, T <sub>A</sub> = 25 °C,<br>f <sub>MASTER</sub> = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-2 | 3/B         |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>f <sub>MASTER</sub> = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-4          | 4/A         |

| Table | 12  | EMC | data |

|-------|-----|-----|------|

| rable | 4Z. |     | uala |

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

|        |                       | $T_A = 25 \ ^\circ C$   |                      |

| LU     | Static lateb up along | T <sub>A</sub> = 85 °C  | ٨                    |

| LU     | Static latch-up class | T <sub>A</sub> = 125 °C | A                    |

|        | -                     | T <sub>A</sub> = 150 °C |                      |

| Table 4 | 5. Electrical | sensitivities |

|---------|---------------|---------------|

|---------|---------------|---------------|

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

## 11.2 LQFP48 package information

SEATING PLANE A2 ŨŦŨŦŨŦŨŦĬĦŮ<del>Ÿ</del>ŨŦŨŦŨŦŨŦŎŹ F 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 24 37 Œ b Œ <u>ш</u> ш Ē ----------£ 48 13 12 e 5B\_ME\_V2

Figure 45. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.