Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 38                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 10x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6268tax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet refers to the STM8AF6246, STM8AF6248, STM8AF6266 and STM8AF6268 products with 16 to 32 Kbyte of Flash program memory.

In the order code, the letter 'F' refers to product versions with data EEPROM and 'H' refers to product versions without data EEPROM. The identifiers 'F' and 'H' do not coexist in a given order code.

The datasheet contains the description of family features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8 Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

# 5.5.3 128 kHz low-speed internal RC oscillator (LSI)

The frequency of this clock is 128 kHz and it is independent from the main clock. It drives the independent watchdog or the AWU wakeup timer.

In systems which do not need independent clock sources for the watchdog counters, the 128 kHz signal can be used as the system clock. This configuration has to be enabled by setting an option byte (OPT3/OPT3N, bit LSI\_EN).

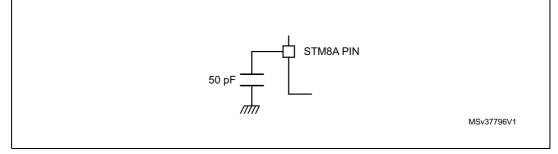

# 5.5.4 16 MHz high-speed external crystal oscillator (HSE)

The external high-speed crystal oscillator can be selected to deliver the main clock in normal Run mode. It operates with quartz crystals and ceramic resonators.

- Frequency range: 1 MHz to 16 MHz

- Crystal oscillation mode: preferred fundamental

- I/Os: standard I/O pins multiplexed with OSCIN, OSCOUT

# 5.5.5 External clock input

An external clock signal can be applied to the OSCIN input pin of the crystal oscillator. The frequency range is 0 to 16 MHz.

# 5.5.6 Clock security system (CSS)

The clock security system protects against a system stall in case of an external crystal clock failure.

In case of a clock failure an interrupt is generated and the high-speed internal clock (HSI) is automatically selected with a frequency of 2 MHz (16 MHz/8).

| Bit     | Periphera<br>I clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock |

|---------|----------------------|---------|---------------------|---------|---------------------|---------|---------------------|

| PCKEN17 | TIM1                 | PCKEN13 | LINUART             | PCKEN27 | Reserved            | PCKEN23 | ADC                 |

| PCKEN16 | TIM3                 | PCKEN12 | Reserved            | PCKEN26 | Reserved            | PCKEN22 | AWU                 |

| PCKEN15 | TIM2                 | PCKEN11 | SPI                 | PCKEN25 | Reserved            | PCKEN21 | Reserved            |

| PCKEN14 | TIM4                 | PCKEN10 | l <sup>2</sup> C    | PCKEN24 | Reserved            | PCKEN20 | Reserved            |

#### Table 2. Peripheral clock gating bit assignments in CLK\_PCKENR1/2 registers

# 5.6 Low-power operating modes

For efficient power management, the application can be put in one of four different low power modes. Users can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

Wait mode

In this mode, the CPU is stopped but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

• Active-halt mode with regulator on

In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in Active-halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

• Active-halt mode with regulator off

This mode is the same as Active-halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

Halt mode

CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

In all modes the CPU and peripherals remain permanently powered on, the system clock is applied only to selected modules. The RAM content is preserved and the brown-out reset circuit remains activated.

# 5.7 Timers

# 5.7.1 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications. The watchdog timer activity is controlled by the application program or option bytes. Once the watchdog is activated, it cannot be disabled by the user program without going through reset.

# Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application timing perfectly. The application software must refresh the counter before time-out and during a limited time window. If the counter is refreshed outside this time window, a reset is issued.

# TIM1: Advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and bridge driver.

- 16-bit up, down and up/down AR (auto-reload) counter with 16-bit fractional prescaler.

- Four independent CAPCOM channels configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Trigger module which allows the interaction of TIM1 with other on-chip peripherals. In the present implementation it is possible to trigger the ADC upon a timer event.

- External trigger to change the timer behavior depending on external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Interrupt sources: 4 x input capture/output compare, 1 x overflow/update, 1 x break

# TIM2 and TIM3: 16-bit general purpose timers

- 16-bit auto-reload up-counter

- 15-bit prescaler adjustable to fixed power of two ratios 1...32768

- Timers with three or two individually configurable CAPCOM channels

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

# 5.7.5 Basic timer

The typical usage of this timer (TIM4) is the generation of a clock tick.

| Table | ٨  | TIMA    |

|-------|----|---------|

| lable | 4. | 1 11114 |

| Timer | Counter<br>width | Counter<br>type | Prescaler<br>factor          | Channels | Inverted outputs | Repetition counter | trigger<br>unit | External trigger | Break<br>input |

|-------|------------------|-----------------|------------------------------|----------|------------------|--------------------|-----------------|------------------|----------------|

| TIM4  | 8-bit            | Up              | 2 <sup>n</sup><br>n = 0 to 7 | 0        | None             | No                 | No              | No               | No             |

- 8-bit auto-reload, adjustable prescaler ratio to any power of two from 1 to 128

- Clock source: master clock

- Interrupt source: 1 x overflow/update

|                           | Table 11. General hardware register map (continued) |                |                                           |                 |  |  |  |  |

|---------------------------|-----------------------------------------------------|----------------|-------------------------------------------|-----------------|--|--|--|--|

| Address                   | Block                                               | Register label | Register name                             | Reset<br>status |  |  |  |  |

| 0x00 5240                 |                                                     | UART2_SR       | LINUART status register                   | 0xC0            |  |  |  |  |

| 0x00 5241                 |                                                     | UART2_DR       | LINUART data register                     | 0xXX            |  |  |  |  |

| 0x00 5242                 |                                                     | UART2_BRR1     | LINUART baud rate register 1              | 0x00            |  |  |  |  |

| 0x00 5243                 |                                                     | UART2_BRR2     | LINUART baud rate register 2              | 0x00            |  |  |  |  |

| 0x00 5244                 |                                                     | UART2_CR1      | LINUART control register 1                | 0x00            |  |  |  |  |

| 0x00 5245                 | LINUART                                             | UART2_CR2      | LINUART control register 2                | 0x00            |  |  |  |  |

| 0x00 5246                 |                                                     | UART2_CR3      | LINUART control register 3                | 0x00            |  |  |  |  |

| 0x00 5247                 |                                                     | UART2_CR4      | LINUART control register 4                | 0x00            |  |  |  |  |

| 0x00 5248                 |                                                     |                | Reserved                                  |                 |  |  |  |  |

| 0x00 5249                 |                                                     | UART2_CR6      | LINUART control register 6                | 0x00            |  |  |  |  |

| 0x00 524A to<br>0x00 524F |                                                     | R              | eserved area (6 bytes)                    |                 |  |  |  |  |

| 0x00 5250                 |                                                     | TIM1_CR1       | TIM1 control register 1                   | 0x00            |  |  |  |  |

| 0x00 5251                 |                                                     | TIM1_CR2       | TIM1 control register 2                   | 0x00            |  |  |  |  |

| 0x00 5252                 |                                                     | TIM1_SMCR      | TIM1 slave mode control register          | 0x00            |  |  |  |  |

| 0x00 5253                 |                                                     | TIM1_ETR       | TIM1 external trigger register            | 0x00            |  |  |  |  |

| 0x00 5254                 |                                                     | TIM1_IER       | TIM1 Interrupt enable register            | 0x00            |  |  |  |  |

| 0x00 5255                 |                                                     | TIM1_SR1       | TIM1 status register 1                    | 0x00            |  |  |  |  |

| 0x00 5256                 |                                                     | TIM1_SR2       | TIM1 status register 2                    | 0x00            |  |  |  |  |

| 0x00 5257                 |                                                     | TIM1_EGR       | TIM1 event generation register            | 0x00            |  |  |  |  |

| 0x00 5258                 |                                                     | TIM1_CCMR1     | TIM1 capture/compare mode register 1      | 0x00            |  |  |  |  |

| 0x00 5259                 |                                                     | TIM1_CCMR2     | TIM1 capture/compare mode register 2      | 0x00            |  |  |  |  |

| 0x00 525A                 |                                                     | TIM1_CCMR3     | TIM1 capture/compare mode register 3      | 0x00            |  |  |  |  |

| 0x00 525B                 | TIM1                                                | TIM1_CCMR4     | TIM1 capture/compare mode register 4      | 0x00            |  |  |  |  |

| 0x00 525C                 |                                                     | TIM1_CCER1     | TIM1 capture/compare enable register<br>1 | 0x00            |  |  |  |  |

| 0x00 525D                 |                                                     | TIM1_CCER2     | TIM1 capture/compare enable register 2    | 0x00            |  |  |  |  |

| 0x00 525E                 |                                                     | TIM1_CNTRH     | TIM1 counter high                         | 0x00            |  |  |  |  |

| 0x00 525F                 |                                                     | TIM1_CNTRL     | TIM1 counter low                          | 0x00            |  |  |  |  |

| 0x00 5260                 |                                                     | TIM1_PSCRH     | TIM1 prescaler register high              | 0x00            |  |  |  |  |

| 0x00 5261                 |                                                     | TIM1_PSCRL     | TIM1 prescaler register low               | 0x00            |  |  |  |  |

| 0x00 5262                 |                                                     | TIM1_ARRH      | TIM1 auto-reload register high            | 0xFF            |  |  |  |  |

| 0x00 5263                 |                                                     | TIM1_ARRL      | TIM1 auto-reload register low             | 0xFF            |  |  |  |  |

| 0x00 5264                 |                                                     | TIM1_RCR       | TIM1 repetition counter register          | 0x00            |  |  |  |  |

Table 11. General hardware register map (continued)

| Address                   | Block                       | Register label | bel Register name                  |      |  |  |

|---------------------------|-----------------------------|----------------|------------------------------------|------|--|--|

| 0x00 540B                 |                             | ADC_LTRL       | ADC low threshold register low     | 0x00 |  |  |

| 0x00 540C                 |                             | ADC _AWSRH     | ADC watchdog status register high  | 0x00 |  |  |

| 0x00 540D                 | ADC ADC_AWSRL<br>ADC _AWCRH |                | ADC watchdog status register low   | 0x00 |  |  |

| 0x00 540E                 |                             |                | ADC watchdog control register high | 0x00 |  |  |

| 0x00 540F                 |                             | ADC _AWCRL     | ADC watchdog control register low  | 0x00 |  |  |

| 0x00 5410 to<br>0x00 541F | Reserved area (16 bytes)    |                |                                    |      |  |  |

Table 11. General hardware register map (continued)

1. Depends on the previous reset source.

2. Write only register.

### Table 12. CPU/SWIM/debug module/interrupt controller registers

| Address                   | Block                         | Register label | Register name                          | Reset<br>status     |

|---------------------------|-------------------------------|----------------|----------------------------------------|---------------------|

| 0x00 7F00                 |                               | А              | Accumulator                            | 0x00                |

| 0x00 7F01                 |                               | PCE            | Program counter extended               | 0x00                |

| 0x00 7F02                 |                               | PCH            | Program counter high                   | 0x80                |

| 0x00 7F03                 |                               | PCL            | Program counter low                    | 0x00                |

| 0x00 7F04                 |                               | ХН             | X index register high                  | 0x00                |

| 0x00 7F05                 | CPU <sup>(1)</sup>            | XL             | X index register low                   | 0x00                |

| 0x00 7F06                 |                               | YH             | Y index register high                  | 0x00                |

| 0x00 7F07                 |                               | YL             | Y index register low                   | 0x00                |

| 0x00 7F08                 |                               | SPH            | Stack pointer high                     | 0x17 <sup>(2)</sup> |

| 0x00 7F09                 | 9 SPL Stack pointer low       |                | 0xFF                                   |                     |

| 0x00 7F0A                 | 0A CC Condition code register |                | Condition code register                | 0x28                |

| 0x00 7F0B to<br>0x00 7F5F |                               |                | Reserved area (85 bytes)               |                     |

| 0x00 7F60                 | CPU                           | CFG_GCR        | Global configuration register          | 0x00                |

| 0x00 7F70                 |                               | ITC_SPR1       | Interrupt software priority register 1 | 0xFF                |

| 0x00 7F71                 |                               | ITC_SPR2       | Interrupt software priority register 2 | 0xFF                |

| 0x00 7F72                 | ITC                           | ITC_SPR3       | Interrupt software priority register 3 | 0xFF                |

| 0x00 7F73                 | ne                            | ITC_SPR4       | Interrupt software priority register 4 | 0xFF                |

| 0x00 7F74                 |                               | ITC_SPR5       | Interrupt software priority register 5 | 0xFF                |

| 0x00 7F75                 |                               | ITC_SPR6       | Interrupt software priority register 6 | 0xFF                |

| 0x00 7F76 to<br>0x00 7F79 |                               |                | Reserved area (4 bytes)                |                     |

| 0x00 7F80                 | SWIM                          | SWIM_CSR       | SWIM control status register           | 0x00                |

| Option byte no. | Description                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | HSITRIM: Trimming option for 16 MHz internal RC oscillator                                                                                      |

|                 | 0: 3-bit on-the-fly trimming (compatible with devices based on the 128K silicon)                                                                |

|                 | 1: 4-bit on-the-fly trimming                                                                                                                    |

|                 | LSI_EN: Low speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source   |

| OPT3            | IWDG_HW: Independent watchdog                                                                                                                   |

| UF 13           | <ul><li>0: IWDG independent watchdog activated by software</li><li>1: IWDG independent watchdog activated by hardware</li></ul>                 |

|                 | WWDG_HW: Window watchdog activation                                                                                                             |

|                 | <ul><li>0: WWDG window watchdog activated by software</li><li>1: WWDG window watchdog activated by hardware</li></ul>                           |

|                 | WWDG_HALT: Window watchdog reset on Halt                                                                                                        |

|                 | 0: No reset generated on Halt if WWDG active<br>1: Reset generated on Halt if WWDG active                                                       |

|                 | EXTCLK: External clock selection                                                                                                                |

|                 | 0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                              |

|                 | CKAWUSEL: Auto-wakeup unit/clock                                                                                                                |

| OPT4            | 0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU                                            |

|                 | PRSC[1:0]: AWU clock prescaler                                                                                                                  |

|                 | 00: Reserved<br>01: 16 MHz to 128 kHz prescaler                                                                                                 |

|                 | 10: 8 MHz to 128 kHz prescaler                                                                                                                  |

|                 | 11: 4 MHz to 128 kHz prescaler                                                                                                                  |

| 0.075           | HSECNT[7:0]: HSE crystal oscillator stabilization time                                                                                          |

| OPT5            | This configures the stabilization time to 0.5, 8, 128, and 2048 HSE cycles with corresponding option byte values of 0xE1, 0xD2, 0xB4, and 0x00. |

| 0.770           | TMU[3:0]: Enable temporary memory unprotection                                                                                                  |

| OPT6            | 0101: TMU disabled (permanent ROP).<br>Any other value: TMU enabled.                                                                            |

| OPT7            | Reserved                                                                                                                                        |

| OPT8            | TMU_KEY 1 [7:0]: Temporary unprotection key 0<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                |

|                 | TMU_KEY 2 [7:0]: Temporary unprotection key 1                                                                                                   |

| OPT9            | Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                 |

| OPT10           | TMU_KEY 3 [7:0]: Temporary unprotection key 2<br>Temporary unprotection key: Must be different from 0x00 or 0xFF                                |

|                 | TMU_KEY 4 [7:0]: Temporary unprotection key 3                                                                                                   |

| OPT11           | Temporary unprotection key: Must be different from 0x00 or 0xFF                                                                                 |

Table 16. Option byte description (continued)

# **10** Electrical characteristics

# 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

# 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = -40$  °C,  $T_A = 25$  °C, and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

# 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5.0$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

# 10.1.3 Typical curves

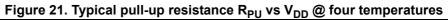

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 10.1.4 Loading capacitor

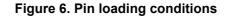

The loading conditions used for pin parameter measurement are shown in *Figure 6*.

Figure 17. HSE oscillator circuit diagram

# HSE oscillator critical g<sub>m</sub> formula

The crystal characteristics have to be checked with the following formula:

g<sub>m</sub> » g<sub>mcrit</sub>

where  $g_{mcrit}$  can be calculated with the crystal parameters as follows:

$$g_{mcrit} = (2 \times \Pi \times {}^{f}HSE)^{2} \times R_{m}(2Co + C)^{2}$$

R<sub>m</sub>: Notional resistance (see crystal specification)

L<sub>m</sub>: Notional inductance (see crystal specification)

C<sub>m</sub>: Notional capacitance (see crystal specification)

Co: Shunt capacitance (see crystal specification)

$C_{1,1} = C_{1,2} = C$ : Grounded external capacitance

#### 10.3.4 Internal clock sources and timing characteristics

Subject to general operating conditions for V<sub>DD</sub> and T<sub>A</sub>.

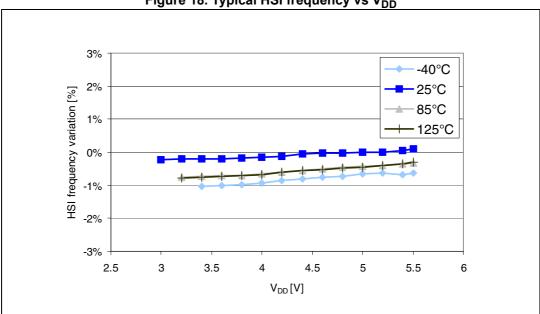

#### High speed internal RC oscillator (HSI)

| Table 30. HSI oscillator characteristics | Table 30. | HSI | oscillator | characteristics |

|------------------------------------------|-----------|-----|------------|-----------------|

|------------------------------------------|-----------|-----|------------|-----------------|

| Symbol           | Parameter | Conditions | Min | Тур | Мах | Unit |

|------------------|-----------|------------|-----|-----|-----|------|

| f <sub>HSI</sub> | Frequency | -          | -   | 16  | -   | MHz  |

| Symbol               | Parameter                                       | Conditions                                                                                                         | Min                 | Тур | Мах                | Unit |

|----------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|-----|--------------------|------|

|                      | HSI oscillator user                             | Trimmed by the application                                                                                         | -1 <sup>(1)</sup>   | -   | 1 <sup>(1)</sup>   |      |

|                      | trimming accuracy                               | for any V <sub>DD</sub> and T <sub>A</sub> conditions                                                              | -0.5 <sup>(1)</sup> | -   | 0.5 <sup>(1)</sup> |      |

|                      | HSI oscillator accuracy<br>(factory calibrated) | $3.0 V \le V_{DD} \le 5.5 V$ ,<br>-40 °C $\le T_A \le 150 °C$                                                      | -5                  | -   | 5                  | %    |

|                      |                                                 | $\begin{array}{l} 3.0V \leq \! V_{DD} \leq \! 5.5V, \\ -40^\circ C \leq \! T_A \leq \! 125 \ ^\circ C \end{array}$ | -2.5 <sup>(2)</sup> | -   | 2.5 <sup>(2)</sup> |      |

| t <sub>su(HSI)</sub> | HSI oscillator wakeup time                      | -                                                                                                                  | -                   | -   | 2 <sup>(3)</sup>   | μs   |

Table 30. HSI oscillator characteristics

1. Depending on option byte setting (OPT3 and NOPT3)

2. These values are guaranteed for STM8AF62x6ITx order codes only.

3. Guaranteed by characterization, not tested in production

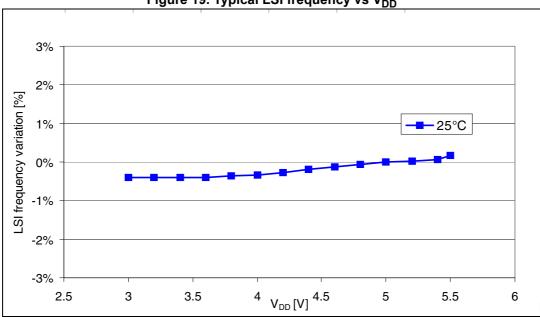

# Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

Table 31. LSI oscillator characteristics

| Symbol               | Parameter                  | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                  | -          | 112 | 128 | 144              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time | -          | -   | -   | 7 <sup>(1)</sup> | μs   |

1. Data based on characterization results, not tested in production.

Figure 19. Typical LSI frequency vs V<sub>DD</sub>

- 2. Guaranteed by design.

- 3. Data based on characterization results, not tested in production.

# 10.3.8 TIM 1, 2, 3, and 4 timer specifications

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Table 37. TIM 1 | 2, 3, and 4 electrical specified | ications |

|-----------------|----------------------------------|----------|

|-----------------|----------------------------------|----------|

| Symbol           | Parameter                                     | Conditions | Min | Тур | Max | Unit |

|------------------|-----------------------------------------------|------------|-----|-----|-----|------|

| f <sub>EXT</sub> | Timer external clock frequency <sup>(1)</sup> | -          | -   | -   | 16  | MHz  |

1. Not tested in production. On 64 Kbyte devices, the frequency is limited to 16 MHz.

# 10.3.9 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 38* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                    | Cond                                                            | ditions                          | Min                      | Мах                      | Unit |   |  |

|----------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------|----------------------------------|--------------------------|--------------------------|------|---|--|

|                                                                            |                              | Master mode                                                     |                                  | 0                        | 10                       |      |   |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency          | Slave mode                                                      | V <sub>DD</sub> < 4.5 V          | 0                        | 6 <sup>(1)</sup>         | MHz  |   |  |

|                                                                            |                              | Slave mode                                                      | V <sub>DD</sub> = 4.5 V to 5.5 V | 0                        | 8 <sup>(1)</sup>         |      |   |  |

| t <sub>r(SCK</sub> )<br>t <sub>f(SCK)</sub>                                | SPI clock rise and fall time | Capacitive load: C = 30 pF                                      |                                  | -                        | 25 <sup>(2)</sup>        |      |   |  |

| t <sub>su(NSS)</sub> <sup>(3)</sup>                                        | NSS setup time               | Slave mode                                                      |                                  | 4 * t <sub>MASTER</sub>  | -                        |      |   |  |

| t <sub>h(NSS)</sub> <sup>(3)</sup>                                         | NSS hold time                | Slave mode                                                      |                                  | 70                       | -                        |      |   |  |

| t <sub>w(SCKH)</sub> <sup>(3)</sup><br>t <sub>w(SCKL)</sub> <sup>(3)</sup> | SCK high and low time        | Master mode                                                     |                                  | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |   |  |

| t <sub>su(MI)</sub> (3)                                                    | Data input setup time        | Master mode                                                     | Master mode                      |                          | -                        |      |   |  |

| $t_{su(SI)}^{(3)}$                                                         | Data input setup time        | Slave mode                                                      |                                  | Slave mode               |                          | 5    | - |  |

| t <sub>h(MI)</sub> <sup>(3)</sup><br>t <sub>h(SI)</sub> <sup>(3)</sup>     | Data input hold time         | Master mode                                                     | Master mode                      |                          | -                        | ns   |   |  |

| $t_{h(SI)}^{(3)}$                                                          |                              | Slave mode                                                      |                                  | 10                       | -                        |      |   |  |

| t <sub>a(SO)</sub> (3)(4)                                                  | Data output access time      | Slave mode                                                      |                                  | -                        | 3* t <sub>MASTER</sub>   |      |   |  |

| t <sub>dis(SO)</sub> <sup>(3)(5)</sup>                                     | Data output disable time     | Slave mode                                                      |                                  | 25                       |                          |      |   |  |

| t <sub>v(SO)</sub> <sup>(3)</sup>                                          | Data output valid time       | Slave mode                                                      | V <sub>DD</sub> < 4.5 V          | -                        | 75                       |      |   |  |

| v(SO) <sup>۲۷</sup>                                                        |                              | (after enable edge) $V_{DD} = 4.5 \text{ V to } 5.10 \text{ J}$ |                                  | -                        | 53                       |      |   |  |

| t <sub>v(MO)</sub> <sup>(3)</sup>                                          | Data output valid time       | Master mode (after enable edge)                                 |                                  | -                        | 30                       |      |   |  |

| t <sub>h(SO)</sub> <sup>(3)</sup>                                          | Data output hold time        | Slave mode (after enable edge)                                  |                                  | 31                       | -                        |      |   |  |

| t <sub>h(MO)</sub> <sup>(3)</sup>                                          | Data output hold time        | Master mode (after                                              | enable edge)                     | 12                       | -                        |      |   |  |

| Table 38. SPI ch | aracteristics |

|------------------|---------------|

|------------------|---------------|

1.  $f_{SCK} < f_{MASTER}/2$ .

2. The pad has to be configured accordingly (fast mode).

# 10.3.10 I<sup>2</sup>C interface characteristics

| Symbol                                     | Parameter                                               | Standard           | mode I <sup>2</sup> C | Fast mod           | Unit               |      |  |

|--------------------------------------------|---------------------------------------------------------|--------------------|-----------------------|--------------------|--------------------|------|--|

| Symbol                                     | Falameter                                               | Min <sup>(2)</sup> | Max <sup>(2)</sup>    | Min <sup>(2)</sup> | Max <sup>(2)</sup> | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                      | 4.7                | -                     | 1.3                | -                  | 110  |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                     | 4.0                | -                     | 0.6                | -                  | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                          | 250                | -                     | 100                | -                  |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                      | 0 <sup>(3)</sup>   | -                     | 0 <sup>(4)</sup>   | 900 <sup>(3)</sup> |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time<br>(V <sub>DD</sub> = 3 to 5.5 V) | -                  | 1000                  | -                  | 300                | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time<br>(V <sub>DD</sub> = 3 to 5.5 V) | -                  | 300                   | -                  | 300                |      |  |

| t <sub>h(STA)</sub>                        | START condition hold time                               | 4.0                | -                     | 0.6                | -                  |      |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time                     | 4.7                | -                     | 0.6                | -                  |      |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time                               | 4.0                | -                     | 0.6                | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free)                 | 4.7                | -                     | 1.3                | -                  |      |  |

| Cb                                         | Capacitive load for each bus line                       | -                  | 400                   | -                  | 400                | pF   |  |

# Table 39. I<sup>2</sup>C characteristics

1.  $f_{MASTER}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz)

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

# **Electromagnetic interference (EMI)**

Emission tests conform to the IEC 61967-2 standard for test software, board layout and pin loading.

|                  |                                      | Conditions         |                                   |                                     |           |      |      |

|------------------|--------------------------------------|--------------------|-----------------------------------|-------------------------------------|-----------|------|------|

| Symbol           | Parameter                            |                    | Monitored                         | Max f <sub>CPU</sub> <sup>(1)</sup> |           | Unit |      |

|                  |                                      | General conditions | frequency band                    | 8<br>MHz                            | 16<br>MHz |      |      |

|                  |                                      |                    | Peak level $T_A = 25 ^{\circ}C$ , | 0.1 MHz to 30 MHz                   | 15        | 17   |      |

| e                | Peak level                           |                    |                                   | 30 MHz to 130 MHz                   | 18        | 22   | dBµV |

| S <sub>EMI</sub> | EMI LQFP80 package conforming to IEC | 130 MHz to 1 GHz   | -1                                | 3                                   | υσμν      |      |      |

|                  | EMI level                            | 61967-2            | -                                 | 2                                   | 2.5       |      |      |

| Table 4 | 13. E | EMI c | lata |

|---------|-------|-------|------|

|---------|-------|-------|------|

1. Data based on characterization results, not tested in production.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Table 44. | ESD | absolute | maximum | ratings |

|-----------|-----|----------|---------|---------|

|-----------|-----|----------|---------|---------|

| Symbol                | Ratings                                               | Conditions                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model) | $T_A = 25^{\circ}C$ , conforming to JESD22-A114     | ЗA    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | $T_A = 25^{\circ}C$ , conforming to JESD22-C101     | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (Machine model)       | T <sub>A</sub> = 25°C, conforming to<br>JESD22-A115 | В     | 200                             |      |

1. Data based on characterization results, not tested in production

| Cumb al | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|---------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol  | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А       | 0.800       | 0.900 | 1.000 | 0.0315                | 0.0354 | 0.0394 |

| A1      | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| A3      | -           | 0.200 | -     | -                     | 0.0079 | -      |

| b       | 0.180       | 0.250 | 0.300 | 0.0071                | 0.0098 | 0.0118 |

| D       | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| D2      | 3.500       | 3.600 | 3.700 | 0.1378                | 0.1417 | 0.1457 |

| E       | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| E2      | 3.500       | 3.600 | 3.700 | 0.1378                | 0.1417 | 0.1457 |

| е       | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L       | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| ddd     | -           | -     | 0.050 | -                     | -      | 0.0020 |

# Table 46. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quadflat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| Currence of |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|-------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol      | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А           | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1          | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2          | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b           | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| С           | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D           | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1          | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3          | -     | 5.500       | -     | -      | 0.2165                | -      |

| Е           | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| E1          | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| E3          | -     | 5.500       | -     | -      | 0.2165                | -      |

| е           | -     | 0.500       | -     | -      | 0.0197                | -      |

| L           | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1          | -     | 1.000       | -     | -      | 0.0394                | -      |

| k           | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| CCC         | -     | -           | 0.080 | -      | -                     | 0.0031 |

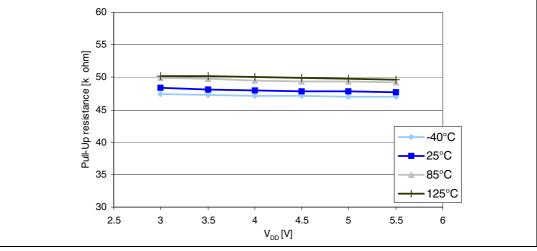

| Table 47. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 49. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

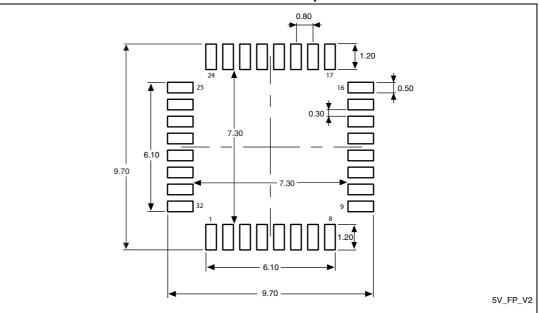

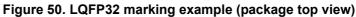

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

# 14 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Aug-2008 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10-Aug-2009 | 2        | Document revised as the following:<br>Updated <i>Features</i> ;<br>Updated <i>Table: Device summary</i> ;<br>Updated <i>Section: Product line-up</i> ;<br>Changed <i>Section: Product overview</i> ;<br>Updated <i>Section: Pinouts and pin description</i> ;<br>Changed <i>Section: Register map</i> ;<br>Updated <i>Section: Register map</i> ;<br>Updated <i>Section: Interrupt table</i> ;<br>Updated <i>Section: Option bytes</i> ;<br>Updated <i>Section: Electrical characteristics</i> ;<br>Updated <i>Section: Package information</i> ;<br>Updated <i>Section: Ordering information</i> ;<br>Added <i>Section: STM8 development tools</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22-Oct-2009 | 3        | Adapted Table: STM8AF61xx/62xx (32 Kbyte) microcontroller pin<br>description.<br>Added Section: LIN header error when automatic resynchronization<br>is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 08-Jul-2010 | 4        | Updated title on cover page.<br>Added VFQFPN32 5x 5 mm package.<br>Added STM8AF62xx devices, and modified cover page header to<br>clarify the part numbers covered by the datasheets. Updated <i>Note 1</i><br>below <i>Table: Device summary.</i><br>Updated D temperature range to -40 to 150°C.<br>Content of <i>Section: Product overview</i> reorganized.<br>Renamed <i>Section: Memory and register map</i> , and content merged<br>with Register map section.<br>Renamed BL_EN and NBL_EN, BL and NBL, respectively, in <i>Table:</i><br><i>Option bytes.</i><br>Added <i>Table: Operating lifetime.</i><br>Added CEXT and P <sub>D</sub> (power dissipation) in <i>Table: General operating</i><br><i>conditions</i> , and <i>Section: VCAP external capacitor.</i><br>Suffix D maximum junction temperature (T <sub>J</sub> ) updated in <i>Table:</i><br><i>General operating conditions.</i><br>Update tvDD in <i>Table: Operating conditions at power-up/power-down.</i><br>Moved <i>Table: Typical peripheral current consumption VDD = 5.0 V</i> to<br><i>Section: Current consumption for on-chip peripherals</i> and removed<br>I <sub>DD(CAN)</sub> .<br>Updated <i>Section: STM8 development tools.</i> |

## Table 50. Document revision history

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | 1764121011       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 31-Jan-2011 | 5<br>(continued) | Renamed Fast Active Halt mode to Active-halt mode with regulator<br>on, and Slow Active Halt mode to Active-halt mode with regulator off.<br>Updated <i>Table: Total current consumption in Halt and Active-halt</i><br><i>modes. General conditions for VDD apply, TA</i> = -40 to 55 °C, in<br>particular I <sub>DD(FAH)</sub> and I <sub>DD(SAH)</sub> renamed I <sub>DD(AH)</sub> ; t <sub>WU(FAH)</sub> and<br>t <sub>WU(SAH)</sub> renamed t <sub>WU(AH)</sub> , and temperature condition added.<br>Removed I <sub>DD(USART)</sub> from <i>Table: Typical peripheral current</i><br><i>consumption VDD</i> = 5.0 V. |

|             |                  | Updated general conditions in <i>Section: Memory characteristics</i> .<br>Modified $T_{WE}$ maximum value in <i>Table: Flash program memory</i> and <i>Table: Data memory</i> .<br>Update $I_{lkg ana}$ maximum value for $T_A$ ranging from -40 to 150 °C in                                                                                                                                                                                                                                                                                                                                                              |

|             |                  | Table: I/O static characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                  | Added $t_{IFP(NRST)}$ and renamed $V_{F(NRST)} t_{IFP}$ in <i>Table: NRST pin characteristics</i> . Added recommendations concerning NRST pin level above <i>Figure: Recommended reset pin protection,</i> and updated external capacitor value.                                                                                                                                                                                                                                                                                                                                                                           |

|             |                  | Added Raisonance compiler in Section: Software tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |                  | Moved know limitations to separate errata sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 6                | Updated wildcards of document part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18-Jul-2012 |                  | <i>Table: Device summary: u</i> pdated the footnotes to all STM8AF61xx part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |                  | Section: Introduction: small text change in first paragraph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |                  | <i>Table:</i> STM8AF62xx product line-up: added "P" version for all order codes; updated RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                  | <i>Table: STM8AF/H61xx product line-up</i> : added "P" version for all order codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                  | <i>Figure: STM8A block diagram</i> : updated POR, BOR and WDG; updated LINUART input; added legend.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                  | Section: Flash program and data EEPROM: removed non relevant bullet points and added a sentence about the factory programmer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |                  | Table: Peripheral clock gating bit assignments in CLK_PCKENR1/2 registers: updated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                  | ADC features: updated ADC input range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |                  | <i>Table: Memory model for the devices covered in this datasheet:</i> updated 16 Kbyte and 8 Kbyte information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                  | <i>Table: Option bytes</i> : updated factory default setting for NOPT17; added footnote <i>1</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                  | Section: Minimum and maximum values: T <sub>A</sub> = -40 °C (not 40 °C).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             |                  | Table: General operating conditions: updated V <sub>CAP</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                  | Table: Total current consumption in Run, Wait and Slow mode General conditions for VDD apply, TA = -40 to 150 °C: updated conditions for $I_{DD(RUN)}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                  | <i>Table: I/O static characteristics</i> : added new condition and new max values for rise and fall time; updated the footnote.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 50. Document revision history (continued)