Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 38                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 10x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6268tay |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |       | 10.3.7                | Reset pin characteristics                  |

|----|-------|-----------------------|--------------------------------------------|

|    |       | 10.3.8                | TIM 1, 2, 3, and 4 timer specifications    |

|    |       | 10.3.9                | SPI serial peripheral interface69          |

|    |       | 10.3.10               | I <sup>2</sup> C interface characteristics |

|    |       | 10.3.11               | 10-bit ADC characteristics                 |

|    |       | 10.3.12               | EMC characteristics                        |

| 11 | Pack  | age info              | ormation                                   |

|    | 11.1  | VFQFP                 | N32 package information 78                 |

|    | 11.2  | LQFP4                 | 8 package information                      |

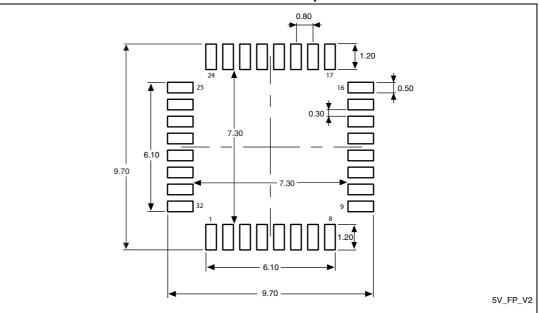

|    | 11.3  | LQFP3                 | 2 package information                      |

|    | 11.4  | Therma                | Il characteristics                         |

|    |       | 11.4.1                | Reference document88                       |

|    |       | 11.4.2                | Selecting the product temperature range    |

| 12 | Orde  | ring info             | ormation                                   |

| 13 | STM   | 8 develo              | pment tools                                |

|    | 13.1  | Emulati               | on and in-circuit debugging tools          |

|    |       | 13.1.1                | STice key features                         |

|    | 13.2  | Softwar               | re tools                                   |

|    |       | 13.2.1                | STM8 toolset                               |

|    |       | 13.2.2                | C and assembly toolchains92                |

|    | 13.3  | Prograr               | nming tools                                |

| 14 | Revis | sion his <sup>.</sup> | tory                                       |

|    |       |                       | -                                          |

|           | flat package mechanical data                            | 79 |

|-----------|---------------------------------------------------------|----|

| Table 47. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |    |

|           | mechanical data                                         | 33 |

| Table 48. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package |    |

|           | mechanical data                                         | 36 |

| Table 49. | Thermal characteristics                                 | 38 |

| Table 50. | Document revision history                               | 94 |

#### TIM1: Advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and bridge driver.

- 16-bit up, down and up/down AR (auto-reload) counter with 16-bit fractional prescaler.

- Four independent CAPCOM channels configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Trigger module which allows the interaction of TIM1 with other on-chip peripherals. In the present implementation it is possible to trigger the ADC upon a timer event.

- External trigger to change the timer behavior depending on external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Interrupt sources: 4 x input capture/output compare, 1 x overflow/update, 1 x break

#### TIM2 and TIM3: 16-bit general purpose timers

- 16-bit auto-reload up-counter

- 15-bit prescaler adjustable to fixed power of two ratios 1...32768

- Timers with three or two individually configurable CAPCOM channels

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

#### 5.7.5 Basic timer

The typical usage of this timer (TIM4) is the generation of a clock tick.

| Table | ٨  | TIMA    |

|-------|----|---------|

| lable | 4. | 1 11114 |

| Timer | Counter<br>width | Counter<br>type | Prescaler<br>factor          | Channels | Inverted outputs | Repetition counter | trigger<br>unit | External trigger | Break<br>input |

|-------|------------------|-----------------|------------------------------|----------|------------------|--------------------|-----------------|------------------|----------------|

| TIM4  | 8-bit            | Up              | 2 <sup>n</sup><br>n = 0 to 7 | 0        | None             | No                 | No              | No               | No             |

- 8-bit auto-reload, adjustable prescaler ratio to any power of two from 1 to 128

- Clock source: master clock

- Interrupt source: 1 x overflow/update

# 5.8 Analog-to-digital converter (ADC)

The STM8A products described in this datasheet contain a 10-bit successive approximation ADC with up to 16 multiplexed input channels, depending on the package.

The ADC name differs between the datasheet and STM8S series and STM8AF series 8-bit microcontrollers reference manual (see *Table 5*).

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| ADC                          | ADC1                                            |

#### **ADC** features

- 10-bit resolution

- Single and continuous conversion modes

- Programmable prescaler: f<sub>MASTER</sub> divided by 2 to 18

- Conversion trigger on timer events and external events

- Interrupt generation at end of conversion

- Selectable alignment of 10-bit data in 2 x 8 bit result register

- Shadow registers for data consistency

- ADC input range:  $V_{SSA} \le V_{IN} \le V_{DDA}$

- Analog watchdog

- Schmitt-trigger on analog inputs can be disabled to reduce power consumption

- Scan mode (single and continuous)

- Dedicated result register for each conversion channel

- Buffer mode for continuous conversion

Note: An additional AIN12 analog input is not selectable in ADC scan mode or with analog watchdog. Values converted from AIN12 are stored only into the ADC\_DRH/ADC\_DRL registers.

## 5.9 Communication interfaces

The following sections give a brief overview of the communication peripheral. Some peripheral names differ between the datasheet and STM8S series and STM8AF series 8-bit microcontrollers reference manual (see *Table 6*).

| Table 6. Communication | peripheral n | naming correspondence |

|------------------------|--------------|-----------------------|

|------------------------|--------------|-----------------------|

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| LINUART                      | UART2                                           |

## 5.9.1 Serial peripheral interface (SPI)

The devices covered by this datasheet contain one SPI. The SPI is available on all the supported packages.

- Maximum speed: 10 Mbit/s or f<sub>MASTER</sub>/2 both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave mode/master mode management by hardware or software for both master and slave

- Programmable clock polarity and phase

- Programmable data order with MSB-first or LSB-first shifting

- Dedicated transmission and reception flags with interrupt capability

- SPI bus busy status flag

- Hardware CRC feature for reliable communication:

- CRC value can be transmitted as last byte in Tx mode

- CRC error checking for last received byte

## 5.9.2 Inter integrated circuit (I<sup>2</sup>C) interface

The devices covered by this datasheet contain one  $I^2C$  interface. The interface is available on all the supported packages.

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

- Status flags:

- Transmitter/receiver mode flag

- End-of-byte transmission flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost condition for master mode

- Acknowledgment failure after address/data transmission

- Detection of misplaced start or stop condition

- Overrun/underrun if clock stretching is disabled

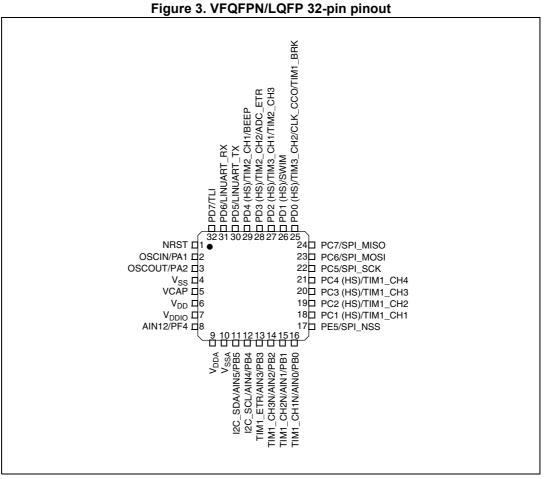

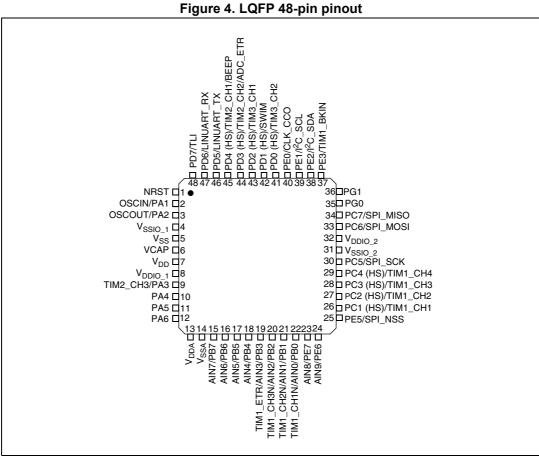

# 6 Pinouts and pin description

## 6.1 Package pinouts

1. (HS) high sink capability.

2. (HS) high sink capability.

Table 7. Legend/abbreviation

| Туре             | I= input, O = output, S = power supply                                                                                                                                                                                                          |                                                      |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|--|--|--|

| Level            | Input                                                                                                                                                                                                                                           | ut CM = CMOS (standard for all I/Os)                 |  |  |  |  |  |  |  |

|                  | Output                                                                                                                                                                                                                                          | HS = High sink (8 mA)                                |  |  |  |  |  |  |  |

| Output speed     | <ul> <li>O1 = Standard (up to 2 MHz)</li> <li>O2 = Fast (up to 10 MHz)</li> <li>O3 = Fast/slow programmability with slow as default state after reset</li> <li>O4 = Fast/slow programmability with fast as default state after reset</li> </ul> |                                                      |  |  |  |  |  |  |  |

| Port and control | Input                                                                                                                                                                                                                                           | float = floating, wpu = weak pull-up                 |  |  |  |  |  |  |  |

| configuration    | Output                                                                                                                                                                                                                                          | T = true open drain, OD = open drain, PP = push pull |  |  |  |  |  |  |  |

| Reset state      | state after reset release).<br>erwise specified, the pin state is the same during the reset phase (i.e.<br>t") and after internal reset release (i.e. at reset state).                                                                          |                                                      |  |  |  |  |  |  |  |

| Pi     | -             |                             |      |          |      |                |           |       |     |    |                                |                               |                                                      |

|--------|---------------|-----------------------------|------|----------|------|----------------|-----------|-------|-----|----|--------------------------------|-------------------------------|------------------------------------------------------|

| num    |               |                             |      |          | Inpu | t              |           | Out   | put |    | _                              |                               |                                                      |

| LQFP48 | VFQFPN/LQFP32 | Pin name                    | Type | floating | wpu  | Ext. interrupt | High sink | Speed | OD  | ЬР | Main function<br>(after reset) | Default alternate<br>function | Alternate<br>function after<br>remap<br>[option bit] |

| 1      | 1             | NRST                        | I/O  | -        | X    | -              | -         | -     | -   | -  | Reset                          | •                             | -                                                    |

| 2      | 2             | PA1/OSCIN <sup>(3)</sup>    | I/O  | X        | Х    | -              | -         | 01    | Х   | Х  | Port A1                        | Resonator/crystal in          | -                                                    |

| 3      | 3             | PA2/OSCOUT                  | I/O  | X        | Х    | Х              | -         | 01    | Х   | Х  | Port A2                        | Resonator/crystal out         | -                                                    |

| 4      | -             | V <sub>SSIO_1</sub>         | S    | -        | -    | -              | -         | -     | -   | -  | I/O groun                      | d                             | -                                                    |

| 5      | 4             | V <sub>SS</sub>             | S    | -        | -    | -              | -         | -     | -   | -  | Digital gro                    | bund                          | -                                                    |

| 6      | 5             | VCAP                        | S    | -        | -    | -              | -         | -     | -   | -  | 1.8 V reg                      | ulator capacitor              | -                                                    |

| 7      | 6             | V <sub>DD</sub>             | S    | -        | -    | -              | -         | -     | -   | -  | Digital po                     | wer supply                    | -                                                    |

| 8      | 7             | V <sub>DDIO_1</sub>         | S    | -        | -    | -              | -         | -     | -   | -  | I/O power                      | supply                        | -                                                    |

| -      | 8             | PF4/AIN12 <sup>(4)(5)</sup> | I/O  | X        | Х    |                | -         | 01    | Х   | Х  | Port F4                        | Analog input 12               | -                                                    |

| 9      | -             | PA3/TIM2_CH3                | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port A3                        | Timer 2 - channel 3           | TIM3_CH1<br>[AFR1]                                   |

| 10     | -             | PA4                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A4                        |                               | -                                                    |

| 11     | -             | PA5                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A5                        |                               | -                                                    |

| 12     | -             | PA6                         | I/O  | Х        | Х    | Х              | -         | O3    | Х   | Х  | Port A6                        |                               | -                                                    |

| 13     | 9             | V <sub>DDA</sub>            | S    | -        | -    | -              | -         | -     | -   | -  | Analog po                      | ower supply                   | -                                                    |

| 14     | 10            | V <sub>SSA</sub>            | S    | -        | -    | -              | -         | -     | -   | -  | Analog gr                      | ound                          | -                                                    |

| 15     | -             | PB7/AIN7                    | I/O  | Х        | Х    | Х              | -         | 01    | Х   | Х  | Port B7                        | Analog input 7                | -                                                    |

| 16     | -             | PB6/AIN6                    | I/O  | Х        | Х    | Х              | -         | 01    | Х   | Х  | Port B6                        | Analog input 6                | -                                                    |

| 17     | 11            | PB5/AIN5                    | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port B5                        | Analog input 5                | I <sup>2</sup> C_SDA<br>[AFR6]                       |

| 18     | 12            | PB4/AIN4                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B4                        | Analog input 4                | I <sup>2</sup> C_SCL<br>[AFR6]                       |

| 19     | 13            | PB3/AIN3                    | I/O  | x        | х    | х              | I         | 01    | х   | х  | Port B3                        | Analog input 3                | TIM1_ETR<br>[AFR5]                                   |

| 20     | 14            | PB2/AIN2                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B2                        | Analog input                  | TIM1_NCC3<br>[AFR5]                                  |

| 21     | 15            | PB1/AIN1                    | I/O  | x        | х    | Х              | -         | 01    | х   | х  | Port B1 Analog input 1         |                               | TIM1_NCC2<br>[AFR5]                                  |

| 22     | 16            | PB0/AIN0                    | I/O  | x        | х    | х              | -         | 01    | х   | х  | Port B0 Analog input 0         |                               | TIM1_NCC1<br>[AFR5]                                  |

| 23     | -             | PE7/AIN8                    | I/O  | X        | Х    |                | -         | 01    | Х   | Х  | Port E7                        | Analog input 8                | -                                                    |

| Table 8. STM8AF6246/48/66/68 ( | (32 Kbv | vte) micro | ocontroller | pin descri | ption <sup>(1)(2)</sup> |

|--------------------------------|---------|------------|-------------|------------|-------------------------|

|                                |         |            |             | pin acour  | puon                    |

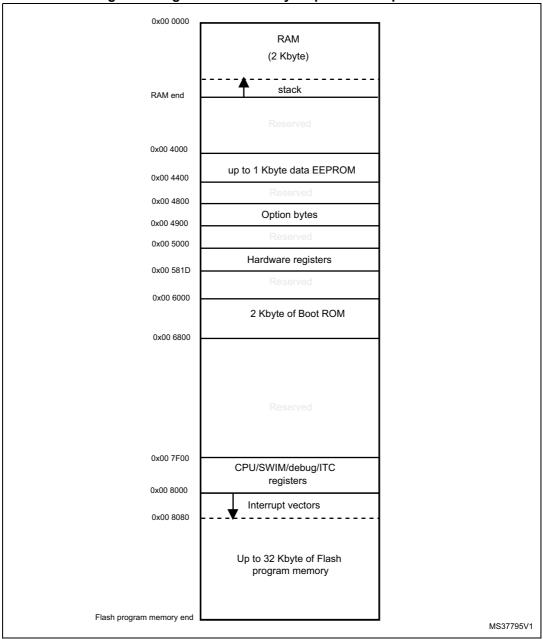

# 7 Memory and register map

## 7.1 Memory map

| Address                   | Block Register label F  |                          | Register name                             | Reset<br>status |

|---------------------------|-------------------------|--------------------------|-------------------------------------------|-----------------|

| 0x00 7F81 to<br>0x00 7F8F |                         | Reserved area (15 bytes) |                                           |                 |

| 0x00 7F90                 |                         | DM_BK1RE                 | DM breakpoint 1 register extended byte    | 0xFF            |

| 0x00 7F91                 |                         | DM_BK1RH                 | DM breakpoint 1 register high byte        | 0xFF            |

| 0x00 7F92                 |                         | DM_BK1RL                 | DM breakpoint 1 register low byte         | 0xFF            |

| 0x00 7F93                 |                         | DM_BK2RE                 | DM breakpoint 2 register extended byte    | 0xFF            |

| 0x00 7F94                 |                         | DM_BK2RH                 | DM breakpoint 2 register high byte        | 0xFF            |

| 0x00 7F95                 | DM                      | DM_BK2RL                 | DM breakpoint 2 register low byte         | 0xFF            |

| 0x00 7F96                 |                         | DM_CR1                   | DM debug module control register 1        | 0x00            |

| 0x00 7F97                 |                         | DM_CR2                   | DM debug module control register 2        | 0x00            |

| 0x00 7F98                 |                         | DM_CSR1                  | DM debug module control/status register 1 | 0x10            |

| 0x00 7F99                 |                         | DM_CSR2                  | DM debug module control/status register 2 | 0x00            |

| 0x00 7F9A                 |                         | DM_ENFCTR                | DM enable function register               | 0xFF            |

| 0x00 7F9B to<br>0x00 7F9F | Reserved area (5 bytes) |                          |                                           |                 |

#### Table 12. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

2. Product dependent value, see Figure 5: Register and memory map of STM8A products.

| Table 13. Temporary memory unprotection registers |       |                              |                                                           |                 |

|---------------------------------------------------|-------|------------------------------|-----------------------------------------------------------|-----------------|

| Address                                           | Block | Register label Register name |                                                           | Reset<br>status |

| 0x00 5800                                         |       | TMU_K1                       | Temporary memory unprotection key register 1              | 0x00            |

| 0x00 5801                                         |       | TMU_K2                       | Temporary memory unprotection key register 2              | 0x00            |

| 0x00 5802                                         |       | TMU_K3                       | Temporary memory unprotection key register 3              | 0x00            |

| 0x00 5803                                         |       | TMU_K4                       | Temporary memory unprotection key register 4              | 0x00            |

| 0x00 5804                                         | TMU   | TMU_K5                       | Temporary memory unprotection key register 5              | 0x00            |

| 0x00 5805                                         |       | TMU_K6                       | Temporary memory unprotection key register 6              | 0x00            |

| 0x00 5806                                         |       | TMU_K7                       | Temporary memory unprotection key register 7              | 0x00            |

| 0x00 5807                                         |       | TMU_K8                       | Temporary memory unprotection key register 8              | 0x00            |

| 0x00 5808                                         |       | TMU_CSR                      | Temporary memory unprotection control and status register | 0x00            |

#### Table 13. Temporary memory unprotection registers

# **10** Electrical characteristics

## 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = -40$  °C,  $T_A = 25$  °C, and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

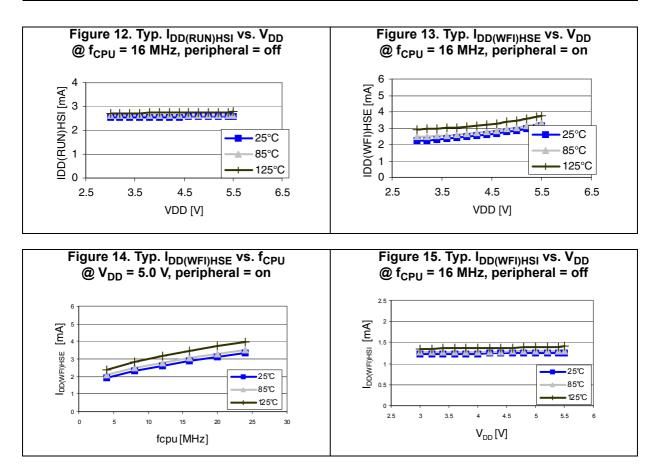

#### 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5.0$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

#### 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 10.1.4 Loading capacitor

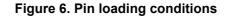

The loading conditions used for pin parameter measurement are shown in *Figure 6*.

#### 10.1.5 Pin input voltage

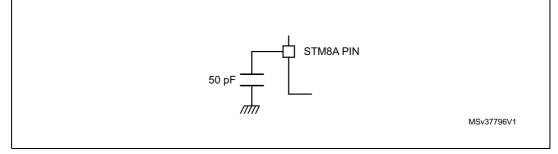

The input voltage measurement on a pin of the device is described in Figure 7.

#### Figure 7. Pin input voltage

# 10.2 Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| ······································ |                                                                   |                       |                                            |      |  |

|----------------------------------------|-------------------------------------------------------------------|-----------------------|--------------------------------------------|------|--|

| Symbol                                 | Ratings                                                           | Min                   | Max                                        | Unit |  |

| V <sub>DDx</sub> - V <sub>SS</sub>     | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                  | 6.5                                        | V    |  |

| V                                      | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3 | 6.5                                        | V    |  |

| V <sub>IN</sub>                        | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3                      | v    |  |

| V <sub>DDx</sub> - V <sub>DD</sub>     | Variations between different power pins                           | -                     | 50                                         | mV   |  |

| V <sub>SSx</sub> - V <sub>SS</sub>     | Variations between all the different ground pins                  | -                     | 50                                         | IIIV |  |

| V <sub>ESD</sub>                       | Electrostatic discharge voltage                                   |                       | ite maximum<br>cal sensitivity)<br>page 76 | •    |  |

Table 17. Voltage characteristics

1. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

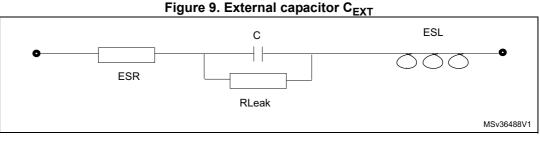

## 10.3.1 VCAP external capacitor

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 21*. Care should be taken to limit the series inductance to less than 15 nH.

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

## 10.3.2 Supply current characteristics

The current consumption is measured as described in *Figure 6 on page 49* and *Figure 7 on page 50*.

If not explicitly stated, general conditions of temperature and voltage apply.

| General conditions for $v_{DD}$ apply, $I_A = -40$ to 150 °C |                                                           |                                                            |                                               |      |                     |      |

|--------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------|------|---------------------|------|

| Symbol                                                       | Parameter                                                 | Conditions                                                 |                                               | Тур  | Мах                 | Unit |

|                                                              |                                                           | All peripherals                                            | f <sub>CPU</sub> = 16 MHz                     | 7.4  | 14                  |      |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>                          | Supply current in                                         | clocked, code<br>executed from Flash                       | f <sub>CPU</sub> = 8 MHz                      | 4.0  | 7.4 <sup>(2)</sup>  |      |

| DD(RUN)                                                      | Run mode                                                  | program memory,<br>HSE external clock                      | f <sub>CPU</sub> = 4 MHz                      | 2.4  | 4.1 <sup>(2)</sup>  |      |

|                                                              |                                                           | (without resonator)                                        | f <sub>CPU</sub> = 2 MHz                      | 1.5  | 2.5                 |      |

|                                                              |                                                           | All peripherals                                            | f <sub>CPU</sub> = 16 MHz                     | 3.7  | 5.0                 |      |

| I <sub>DD(RUN)</sub> <sup>(1)</sup>                          | Supply current in                                         | nt in and EEPROM HSE                                       | f <sub>CPU</sub> = 8 MHz                      | 2.2  | 3.0 <sup>(2)</sup>  |      |

| 'DD(RUN)`                                                    | Run mode                                                  |                                                            | f <sub>CPU</sub> = 4 MHz                      | 1.4  | 2.0 <sup>(2)</sup>  |      |

|                                                              |                                                           |                                                            | f <sub>CPU</sub> = 2 MHz                      | 1.0  | 1.5                 | mA   |

|                                                              |                                                           |                                                            | f <sub>CPU</sub> = 16 MHz                     | 1.65 | 2.5                 |      |

| I <sub>DD(WFI)</sub> <sup>(1)</sup>                          | Supply current in                                         | CPU stopped, all<br>peripherals off, HSE<br>external clock | f <sub>CPU</sub> = 8 MHz                      | 1.15 | 1.9 <sup>(2)</sup>  |      |

| 'DD(WFI)`´                                                   |                                                           |                                                            | f <sub>CPU</sub> = 4 MHz                      | 0.90 | 1.6 <sup>(2)</sup>  |      |

|                                                              |                                                           |                                                            | f <sub>CPU</sub> = 2 MHz                      | 0.80 | 1.5                 |      |

| (1)                                                          | Supply f <sub>CPU</sub> scaled down, all peripherals off, | Ext. clock 16 MHz<br>f <sub>CPU</sub> = 125 kHz            | 1.50                                          | 1.95 |                     |      |

| I <sub>DD(SLOW)</sub> <sup>(1)</sup>                         | current in<br>Slow mode                                   | code executed from RAM                                     | LSI internal RC<br>f <sub>CPU</sub> = 128 kHz | 1.50 | 1.80 <sup>(2)</sup> |      |

Table 23. Total current consumption in Run, Wait and Slow mode. General conditions for  $V_{DD}$  apply,  $T_A = -40$  to 150 °C

1. The current due to I/O utilization is not taken into account in these values.

2. Values not tested in production. Design guidelines only.

DocID14952 Rev 11

## 10.3.3 External clock sources and timing characteristics

#### HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                               | Conditions                         | Min                   | Тур | Max                   | Unit |

|-----------------------|-----------------------------------------|------------------------------------|-----------------------|-----|-----------------------|------|

| f <sub>HSE_</sub> ext | User external clock source<br>frequency | T <sub>A</sub> is -40 to<br>150 °C | 0 <sup>(1)</sup>      | -   | 16                    | MHz  |

| V <sub>HSEdHL</sub>   | Comparator hysteresis                   | -                                  | 0.1 x V <sub>DD</sub> | -   | -                     |      |

| V <sub>HSEH</sub>     | OSCIN input pin high level voltage      | -                                  | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | v    |

| V <sub>HSEL</sub>     | OSCIN input pin low level voltage       | -                                  | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> |      |

| ILEAK_HSE             | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$         | -1                    | -   | +1                    | μA   |

1. In CSS is used, the external clock must have a frequency above 500 kHz.

## 10.3.6 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage, using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                          | Parameter                                                                                                                                                                                                                  | Conditions                                                                              | Min                     | Тур                      | Мах                     | Unit |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------------------|------|

| $V_{IL}$                        | Input low level voltage                                                                                                                                                                                                    |                                                                                         | -0.3 V                  | -                        | 0.3 x V <sub>DD</sub>   |      |

| V <sub>IH</sub>                 | Input high level voltage                                                                                                                                                                                                   | _                                                                                       | 0.7 x V <sub>DD</sub>   | -                        | V <sub>DD</sub> + 0.3 V |      |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                                                                                                                                                                                                  |                                                                                         | -                       | 0.1 x<br>V <sub>DD</sub> | -                       |      |

| M                               | Output high level voltage                                                                                                                                                                                                  | Standard I/0, V <sub>DD</sub> = 5 V,<br>I = 3 mA                                        | V <sub>DD</sub> - 0.5 V | -                        | -                       |      |

| V <sub>OH</sub>                 | output high level voltage                                                                                                                                                                                                  | Standard I/0, V <sub>DD</sub> = 3 V,<br>I = 1.5 mA                                      | V <sub>DD</sub> - 0.4 V | -                        | -                       | V    |

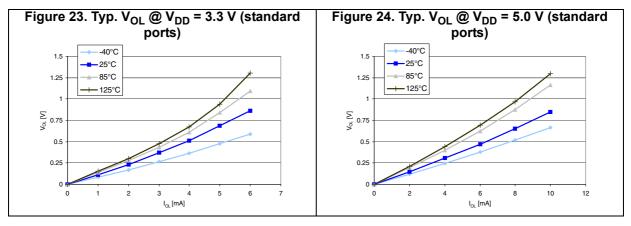

|                                 |                                                                                                                                                                                                                            | High sink and true open<br>drain I/0, V <sub>DD</sub> = 5 V<br>I = 8 mA                 | -                       | -                        | 0.5                     |      |

| $V_{OL}$                        | I = 3 mÅ                                                                                                                                                                                                                   | Standard I/0, V <sub>DD</sub> = 5 V<br>I = 3 mA                                         | -                       | -                        | 0.6                     |      |

|                                 |                                                                                                                                                                                                                            | Standard I/0, V <sub>DD</sub> = 3 V<br>I = 1.5 mA                                       | -                       | -                        | 0.4                     |      |

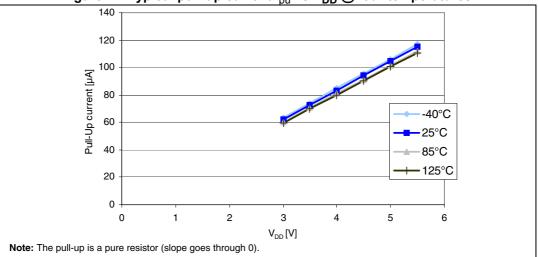

| R <sub>pu</sub>                 | Pull-up resistor                                                                                                                                                                                                           | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$                                                     | 35                      | 50                       | 65                      | kΩ   |

|                                 |                                                                                                                                                                                                                            | Fast I/Os<br>Load = 50 pF                                                               | -                       | -                        | 35 <sup>(2)</sup>       |      |

|                                 | Rise and fall time                                                                                                                                                                                                         | Standard and high sink I/Os<br>Load = 50 pF                                             | -                       | -                        | 125 <sup>(2)</sup>      | 20   |

| t <sub>R</sub> , t <sub>F</sub> | (10% - 90%)                                                                                                                                                                                                                | Fast I/Os<br>Load = 20 pF                                                               | -                       | -                        | 20 <sup>(2)</sup>       | ns   |

|                                 |                                                                                                                                                                                                                            | Standard and high sink I/Os<br>Load = 20 pF                                             | -                       | -                        | 50 <sup>(2)</sup>       |      |

| l <sub>lkg</sub>                | Digital input pad leakage current                                                                                                                                                                                          | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                        | -                       | -                        | ±1                      | μA   |

| . Analog input pa               | ha Analog input pad leakage $ \begin{array}{c} V_{SS} \leq V_{IN} \leq V_{DD} \\ -40 \ ^{\circ}C < T_A < 125 \ ^{\circ}C \\ \hline V_{SS} \leq V_{IN} \leq V_{DD} \\ -40 \ ^{\circ}C < T_A < 150 \ ^{\circ}C \end{array} $ | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>-40 °C < T <sub>A</sub> < 125 °C | -                       | -                        | ±250                    | 24   |

| l <sub>Ikg ana</sub>            |                                                                                                                                                                                                                            | -                                                                                       | -                       | ±500                     | nA                      |      |

| l <sub>lkg(inj)</sub>           | Leakage current in<br>adjacent I/O <sup>(3)</sup>                                                                                                                                                                          | Injection current ±4 mA                                                                 | -                       | -                        | ±1 <sup>(3)</sup>       | μA   |

| I <sub>DDIO</sub>               | Total current on either<br>V <sub>DDIO</sub> or V <sub>SSIO</sub>                                                                                                                                                          | Including injection currents                                                            | -                       | -                        | 60                      | mA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

Figure 22. Typical pull-up current  $I_{pu}$  vs  $V_{DD}$  @ four temperatures

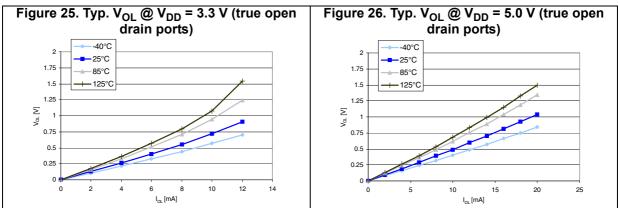

#### Typical output level curves

*Figure 23* to *Figure 32* show typical output level curves measured with output on a single pin.

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

|        |                       | $T_A = 25 \ ^\circ C$   |                      |

| LU     |                       | T <sub>A</sub> = 85 °C  | ٨                    |

| LU     | Static latch-up class | T <sub>A</sub> = 125 °C | A                    |

|        |                       | T <sub>A</sub> = 150 °C |                      |

| Table 4 | 5. Electrical | sensitivities |

|---------|---------------|---------------|

|---------|---------------|---------------|

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

# Figure 49. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

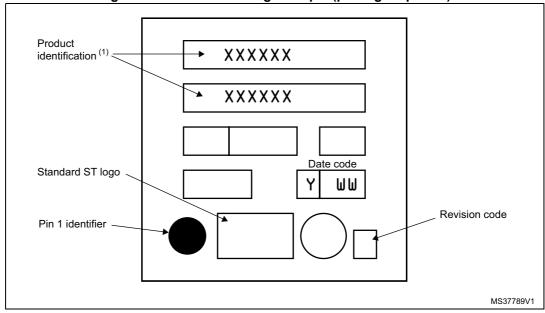

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Jan-2011 | 5        | <ul> <li>Modified references to reference manual, and Flash programming manual in the whole document.</li> <li>Added reference to AEC Q100 standard on cover page.</li> <li>Renamed timer types as follows: <ul> <li>Auto-reload timer to general purpose timer</li> <li>Multipurpose timer to advanced control timer</li> <li>System timer to basic timer</li> </ul> </li> <li>Introduced concept of medium density Flash program memory. Updated timer names in <i>Figure: STM8A block diagram</i>.</li> <li>Added TMU brief description in <i>Section: Flash program and data EEPROM</i>, and updated TMU_MAXATT description in <i>Table: Option byte description</i>.</li> <li>Updated clock sources in clock controller features. Changed 16MHZTRIM0 to HSITRIM bit in <i>Section: User trimming</i>.</li> <li>Added Table: Peripheral clock gating bits.</li> <li>Updated Section: Low-power operating modes.</li> <li>Added Table: ADC naming and Table: Communication peripheral naming correspondence.</li> <li>Added Note 1 related AIN12 pin in Section: Analog-to-digital converter (ADC) and Table: STM8AF61xx/62xx (32 Kbyte) microcontroller pin description.</li> <li>Updated SPI data rate to 10 Mbit/s or f<sub>MASTER</sub>/2 in Section: Serial peripheral interface (SPI).</li> <li>Added reset state in Table: Legend/abbreviation.</li> <li>Table: STM8AF61xx/62xx (32 Kbyte) microcontroller pin description: added Note 7 related to PD1/SWIM, modified Note 6, corrected wpu input for PE1 and PE2, and renamed TIMn_CCx and TIMn_NCCx to TIMn_CHx and TIMn_CHxN, respectively.</li> <li>Section: Register map:</li> <li>Replaced tables describing register maps and reset values for nonvolatile memory, global configuration, reset status, clock controller, interrupt controller, timers, communication interfaces, and ADC, by Table: General hardware register map.</li> </ul> |

Table 50. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID14952 Rev 11