Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | 8032                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, UART/USART, USB                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 46                                                                     |

| Program Memory Size        | 288KB (288K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 4x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/upsd3254a-40u6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

57

# Contents

| 1 | UPSD  | 325xx d   | escription                     |

|---|-------|-----------|--------------------------------|

|   | 1.1   | 52-pin pa | ackage I/O port 15             |

| 2 | Archi | tecture o | overview                       |

|   | 2.1   | Memory    | organization                   |

|   | 2.2   | Register  | s                              |

|   |       | 2.2.1     | Accumulator                    |

|   |       | 2.2.2     | B register                     |

|   |       | 2.2.3     | Stack pointer                  |

|   |       | 2.2.4     | Program counter                |

|   |       | 2.2.5     | Program status word            |

|   |       | 2.2.6     | Registers R0~R7                |

|   |       | 2.2.7     | Data pointer register          |

|   | 2.3   | Program   | memory                         |

|   | 2.4   | Data me   | mory 19                        |

|   | 2.5   | RAM       |                                |

|   | 2.6   | XRAM-D    | DC 20                          |

|   | 2.7   | XRAM-P    | SD 20                          |

|   | 2.8   | SFR       |                                |

|   | 2.9   | Addressi  | ing modes                      |

|   |       | 2.9.1     | Direct addressing              |

|   |       | 2.9.2     | Indirect addressing            |

|   |       | 2.9.3     | Register addressing            |

|   |       | 2.9.4     | Register-specific addressing   |

|   |       | 2.9.5     | Immediate constants addressing |

|   |       | 2.9.6     | Indexed addressing             |

|   | 2.10  | Arithmet  | ic instructions                |

|   | 2.11  | Logical i | nstructions                    |

|   | 2.12  | Data trar | nsfers                         |

|   |       | 2.12.1    | Internal RAM                   |

|   |       | 2.12.2    | External RAM                   |

|   |       | 2.12.3    | Lookup tables                  |

|   | 2.13  | Boolean   | instructions                   |

# 1 UPSD325xx description

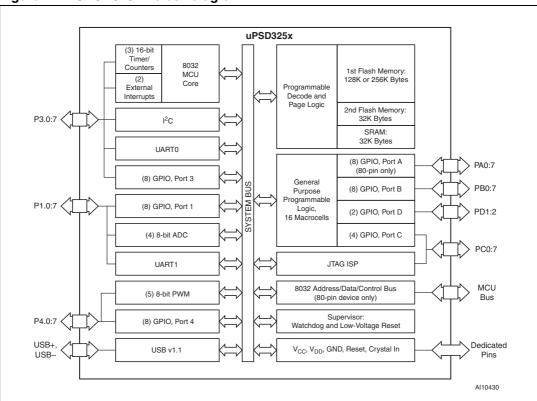

The UPSD325xx Series combines a fast 8051-based microcontroller with a flexible memory structure, programmable logic, and a rich peripheral mix including USB, to form an ideal embedded controller. At its core is an industry-standard 8032 MCU operating up to 40MHz.

A JTAG serial interface is used for In-System Programming (ISP) in as little as 10 seconds, perfect for manufacturing and lab development.

The USB 1.1 low-speed interface has one Control endpoint and two Interrupt endpoints suitable for HID class drivers.

The 8032 core is coupled to Programmable System Device (PSD) architecture to optimize the 8032 memory structure, offering two independent banks of Flash memory that can be placed at virtually any address within 8032 program or data address space, and easily paged beyond 64 Kbytes using on-chip programmable decode logic.

Dual Flash memory banks provide a robust solution for remote product updates in the field through In-Application Programming (IAP). Dual Flash banks also support EEPROM emulation, eliminating the need for external EEPROM chips.

General purpose programmable logic (PLD) is included to build an endless variety of gluelogic, saving external logic devices. The PLD is configured using the software development tool, PSDsoft Express, available from the web at **www.st.com/psm**, at no charge.

The UPSD325xx also includes supervisor functions such as a programmable watchdog timer and low-voltage reset.

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

57

Figure 1. UPSD325xx block diagram

The LJMP instruction encodes the destination address as a 16-bit constant. The instruction is 3 bytes long, consisting of the opcode and two address bytes. The destination address can be anywhere in the 64K Program Memory space.

The AJMP instruction encodes the destination address as an 11-bit constant. The instruction is 2 bytes long, consisting of the opcode, which itself contains 3 of the 11 address bits, followed by another byte containing the low 8 bits of the destination address. When the instruction is executed, these 11 bits are simply substituted for the low 11 bits in the PC. The high 5 bits stay the same. Hence the destination has to be within the same 2K block as the instruction following the AJMP.

In all cases the programmer specifies the destination address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the destination address into the correct format for the given instruction. If the format required by the instruction will not support the distance to the specified destination address, a "Destination out of range" message is written into the List file.

The JMP @A+DPTR instruction supports case jumps. The destination address is computed at execution time as the sum of the 16-bit DPTR register and the Accumulator. Typically. DPTR is set up with the address of a jump table. In a 5-way branch, for ex-ample, an integer 0 through 4 is loaded into the Accumulator. The code to be executed might be as follows:

MOV DPTR,#JUMP TABLE MOV A,INDEX\_NUMBER RL A JMP @A+DPTR

The RL A instruction converts the index number (0 through 4) to an even number on the range 0 through 8, because each entry in the jump table is 2 bytes long:

JUMP TABLE: AJMP CASE 0 AJMP CASE 1 AJMP CASE 2 AJMP CASE 3 AJMP CASE 4

*Table 13* shows a single "CALL addr" instruction, but there are two of them, LCALL and ACALL, which differ in the format in which the subroutine address is given to the CPU. CALL is a generic mnemonic which can be used if the programmer does not care which way the address is encoded.

The LCALL instruction uses the 16-bit address format, and the subroutine can be anywhere in the 64K Program Memory space. The ACALL instruction uses the 11-bit format, and the subroutine must be in the same 2K block as the instruction following the ACALL.

In any case, the programmer specifies the subroutine address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the address into the correct format for the given instructions.

Subroutines should end with a RET instruction, which returns execution to the instruction following the CALL.

RETI is used to return from an interrupt service routine. The only difference between RET and RETI is that RETI tells the interrupt control system that the interrupt in progress is done.

| 머고          | Den Neme | Bit Register Name |      |      |      |       |      |                   |        |                | 0                            |

|-------------|----------|-------------------|------|------|------|-------|------|-------------------|--------|----------------|------------------------------|

| SFR<br>Addr | Reg Name | 7                 | 6    | 5    | 4    | 3     | 2    | 1                 | 0      | Reset<br>Value | Comments                     |

| A1          | PWMCON   | PWML              | PWMP | PWME | CFG4 | CFG3  | CFG2 | CFG1              | CFG0   | 00             | PWM Control<br>Polarity      |

| A2          | PWM0     |                   |      |      |      |       |      |                   |        | 00             | PWM0<br>Output Duty<br>Cycle |

| A3          | PWM1     |                   |      |      |      |       |      |                   |        | 00             | PWM1<br>Output Duty<br>Cycle |

| A4          | PWM2     |                   |      |      |      |       |      |                   |        | 00             | PWM2<br>Output Duty<br>Cycle |

| A5          | PWM3     |                   |      |      |      |       |      |                   |        | 00             | PWM3<br>Output Duty<br>Cycle |

| A6          | WDRST    |                   |      |      |      |       |      |                   |        | 00             | Watch Dog<br>Reset           |

| A7          | IEA      | EDDC              |      |      | ES2  |       |      | El <sup>2</sup> C | EUSB   | 00             | Interrupt<br>Enable (2nd)    |

| A8          | IE       | EA                | -    | ET2  | ES   | ET1   | EX1  | ET0               | EX0    | 00             | Interrupt<br>Enable          |

| A9          |          |                   |      |      |      |       |      |                   |        |                |                              |

| AA          | PWM4P    |                   |      |      |      |       |      |                   |        | 00             | PWM 4<br>Period              |

| AB          | PWM4W    |                   |      |      |      |       |      |                   |        | 00             | PWM 4 Pulse<br>Width         |

| AE          | WDKEY    |                   |      |      |      |       |      |                   |        | 00             | Watch Dog<br>Key Register    |

| B0          | P3       |                   |      |      |      |       |      |                   |        | FF             | Port 3                       |

| B1          | PSCL0L   |                   |      |      |      |       |      |                   |        | 00             | Prescaler 0<br>Low (8-bit)   |

| B2          | PSCL0H   |                   |      |      |      |       |      |                   |        | 00             | Prescaler 0<br>High (8-bit)  |

| В3          | PSCL1L   |                   |      |      |      |       |      |                   |        | 00             | Prescaler 1<br>Low (8-bit)   |

| B4          | PSCL1H   |                   |      |      |      |       |      |                   |        | 00             | Prescaler 1<br>High (8-bit)  |

| B7          | IPA      | PDDC              |      |      | PS2  |       |      | PI2C              | PUSB   | 00             | Interrupt<br>Priority (2nd)  |

| B8          | IP       |                   |      | PT2  | PS   | PT1   | PX1  | PT0               | PX0    | 00             | Interrupt<br>Priority        |

| C0          | P4       |                   |      |      |      |       |      |                   |        | FF             | New Port 4                   |

| C8          | T2CON    | TF2               | EXF2 | RCLK | TCLK | EXEN2 | TR2  | C/T2              | CP/RL2 | 00             | Timer 2<br>Control           |

## Table 16. List of all SFRs (continued)

| Bit | Symbol | Timer  | Function                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

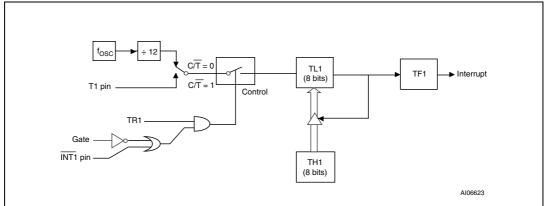

| 7   | Gate   |        | Gating control when set. Timer/Counter 1 is enabled only while INT1 pin is High and TR1 control pin is set. When cleared, Timer 1 is enabled whenever TR1 control bit is set                                                                                                                                                                                                                                      |

| 6   | C/T    |        | Timer or Counter selector, cleared for timer operation (input from internal system clock); set for counter operation (input from T1 input pin)                                                                                                                                                                                                                                                                    |

| 5   | M1     | Timer1 | (M1,M0)=(0,0): 13-bit Timer/Counter, TH1, with TL1 as 5-bit prescaler                                                                                                                                                                                                                                                                                                                                             |

| 4   | MO     |        | <ul> <li>(M1,M0)=(0,1): 16-bit Timer/Counter. TH1 and TL1 are cascaded. There is no prescaler.</li> <li>(M1,M0)=(1,0): 8-bit auto-reload Timer/Counter. TH1 holds a value which is to be reloaded into TL1 each time it overflows</li> <li>(M1,M0)=(1,1): Timer/Counter 1 stopped</li> </ul>                                                                                                                      |

| 3   | Gate   |        | Gating control when set. Timer/Counter 0 is enabled only while INT0 pin is High and TR0 control pin is set. When cleared, Timer 0 is enabled whenever TR0 control bit is set                                                                                                                                                                                                                                      |

| 2   | C/T    |        | Timer or Counter selector, cleared for timer operation (input from internal system clock); set for counter operation (input from T0 input pin)                                                                                                                                                                                                                                                                    |

| 1   | M1     | Timer0 | (M1,M0)=(0,0): 13-bit Timer/Counter, TH0, with TL0 as 5-bit prescaler                                                                                                                                                                                                                                                                                                                                             |

| 0   | MO     | Timero | <ul> <li>(M1,M0)=(0,1): 16-bit Timer/Counter. TH0 and TL0 are cascaded. There is no prescaler.</li> <li>(M1,M0)=(1,0): 8-bit auto-reload Timer/Counter. TH0 holds a value which is to be reloaded into TL0 each time it overflows</li> <li>(M1,M0)=(1,1): TL0 is an 8-bit Timer/Counter controlled by the standard TImer 0 control bits. TH0 is an 8-bit timer only controlled by Timer 1 control bits</li> </ul> |

Table 39.

Description of the TMOD bits

#### 11.1.3 Mode 2

57

Mode 2 configures the Timer register as an 8-bit Counter (TL1) with automatic reload, as shown in *Figure 22*. Overflow from TL1 not only sets TF1, but also reloads TL1 with the contents of TH1, which is preset by software. The reload leaves TH1 unchanged. Mode 2 operation is the same for Timer/Counter 0.

Figure 22. Timer/counter mode 2: 8-bit Auto-reload

# 20 PSD module register description and address offset

*Table 84* shows the offset addresses to the PSD module registers relative to the CSIOP base address. The CSIOP space is the 256 bytes of address that is allocated by the user to the internal PSD module registers. *Table 84* provides brief descriptions of the registers in CSIOP space. The following section gives a more detailed description.

| Register Name                           | Port A | Port B | Port C | Port D | Other <sup>(1)</sup> | Description                                                                                                         |

|-----------------------------------------|--------|--------|--------|--------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Data In                                 | 00     | 01     | 10     | 11     |                      | Reads Port pin as input, MCU I/O Input mode                                                                         |

| Control                                 | 02     | 03     |        |        |                      | Selects mode between MCU I/O or<br>Address Out                                                                      |

| Data Out                                | 04     | 05     | 12     | 13     |                      | Stores data for output to Port pins,<br>MCU I/O Output mode                                                         |

| Direction                               | 06     | 07     | 14     | 15     |                      | Configures Port pin as input or output                                                                              |

| Drive Select                            | 08     | 09     | 16     | 17     |                      | Configures Port pins as either CMOS<br>or Open Drain on some pins, while<br>selecting high slew rate on other pins. |

| Input Macrocell                         | 0A     | 0B     | 18     |        |                      | Reads Input Macrocells                                                                                              |

| Enable Out                              | 0C     | 0D     | 1A     | 1B     |                      | Reads the status of the output enable to the I/O Port driver                                                        |

| Output Macrocells<br>AB                 | 20     | 20     |        |        |                      | READ – reads output of macrocells AB<br>WRITE – loads macrocell flip-flops                                          |

| Output Macrocells<br>BC                 |        | 21     | 21     |        |                      | READ – reads output of macrocells BC<br>WRITE – loads macrocell flip-flops                                          |

| Mask Macrocells<br>AB                   | 22     | 22     |        |        |                      | Blocks writing to the Output Macrocells<br>AB                                                                       |

| Mask Macrocells<br>BC                   |        | 23     | 23     |        |                      | Blocks writing to the Output Macrocells<br>BC                                                                       |

| Primary Flash<br>Protection             |        |        |        |        | C0                   | Read-only – Primary Flash Sector<br>Protection                                                                      |

| Secondary Flash<br>memory<br>Protection |        |        |        |        | C2                   | Read-only – PSD module Security and<br>Secondary Flash memory Sector<br>Protection                                  |

| PMMR0                                   |        |        |        |        | B0                   | Power Management Register 0                                                                                         |

| PMMR2                                   |        |        |        |        | B4                   | Power Management Register 2                                                                                         |

| Page                                    |        |        |        |        | E0                   | Page Register                                                                                                       |

| VM                                      |        |        |        |        | E2                   | Places PSD module memory areas in<br>Program and/or Data space on an<br>individual basis.                           |

Table 84. Register address offset

1. Other registers that are not part of the I/O ports.

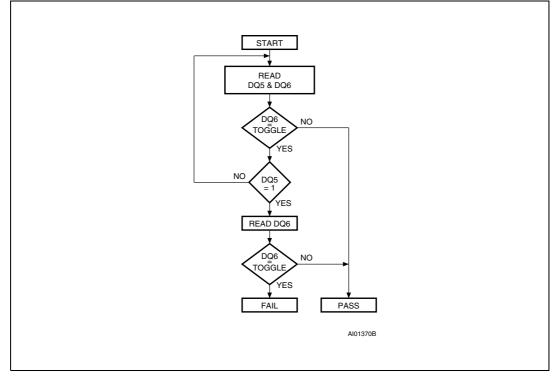

It is suggested (as with all Flash memories) to read the location again after the embedded programming algorithm has completed, to compare the byte that was written to Flash memory with the byte that was intended to be written.

When using the Data Toggle method after an Erase cycle, *Figure 52* still applies. the Toggle Flag bit (DQ6) toggles until the Erase cycle is complete. A 1 on the Error Flag bit (DQ5) indicates a time-out condition on the Erase cycle; a '0' indicates no error. The MCU can read any location within the sector being erased to get the Toggle Flag bit (DQ6) and the Error Flag bit (DQ5).

PSDsoft Express generates ANSI C code functions which implement these Data Toggling algorithms.

#### Figure 52. Data toggle flowchart

#### 22.6.3 Unlock Bypass

The Unlock Bypass instructions allow the system to program bytes to the Flash memories faster than using the standard Program instruction. The Unlock Bypass mode is entered by first initiating two Unlock cycles. This is followed by a third WRITE cycle containing the Unlock Bypass code, 20h (as shown in *Table 85*).

The Flash memory then enters the Unlock Bypass mode. A two-cycle Unlock Bypass Program instruction is all that is required to program in this mode. The first cycle in this instruction contains the Unlock Bypass Program code, A0h. The second cycle contains the program address and data. Additional data is programmed in the same manner. These instructions dispense with the initial two Unlock cycles required in the standard Program instruction, resulting in faster total Flash memory programming.

During the Unlock Bypass mode, only the Unlock Bypass Program and Unlock Bypass Reset Flash instructions are valid.

Suspend Sector Erase is accepted only during an Erase cycle and defaults to READ mode. A Suspend Sector Erase instruction executed during an Erase time-out period, in addition to suspending the Erase cycle, terminates the time out period.

The Toggle Flag bit (DQ6) stops toggling when the internal logic is suspended. The status of this bit must be monitored at an address within the Flash memory sector being erased. The Toggle Flag bit (DQ6) stops toggling between  $0.1\mu$ s and  $15\mu$ s after the Suspend Sector Erase instruction has been executed. The Flash memory is then automatically set to READ mode.

If an Suspend Sector Erase instruction was executed, the following rules apply:

- Attempting to read from a Flash memory sector that was being erased outputs invalid data.

- Reading from a Flash sector that was *not* being erased is valid.

- The Flash memory *cannot* be programmed, and only responds to Resume Sector Erase and Reset Flash instructions (READ is an operation and is allowed).

- If a Reset Flash instruction is received, data in the Flash memory sector that was being erased is invalid.

#### 22.7.4 Resume Sector Erase

If a Suspend Sector Erase instruction was previously executed, the erase cycle may be resumed with this instruction. The Resume Sector Erase instruction consists of writing 030h to any address while an appropriate Sector Select (FS0-FS7 or CSBOOT0-CSBOOT3) is High. (See *Table 85*.)

## 22.8 Specific features

#### 22.8.1 Flash memory sector protect

Each primary and secondary Flash memory sector can be separately protected against Program and Erase cycles. Sector Protection provides additional data security because it disables all Program or Erase cycles. This mode can be activated through the JTAG Port or a Device Programmer.

Sector protection can be selected for each sector using the PSDsoft Express Configuration program. This automatically protects selected sectors when the device is programmed through the JTAG Port or a Device Programmer. Flash memory sectors can be unprotected to allow updating of their contents using the JTAG Port or a Device Programmer. The MCU can read (but cannot change) the sector protection bits.

Any attempt to program or erase a protected Flash memory sector is ignored by the device. The Verify operation results in a READ of the protected data. This allows a guarantee of the retention of the Protection status.

The sector protection status can be read by the MCU through the Flash memory protection registers (in the CSIOP block). See *Table 87* and *Table 88*.

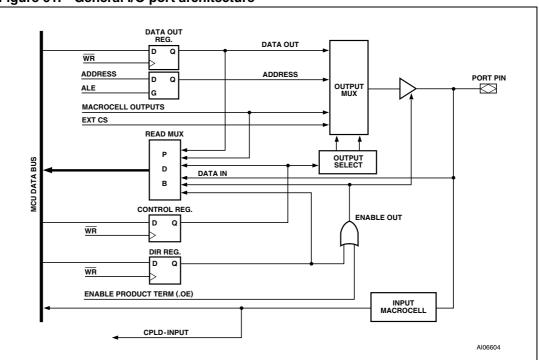

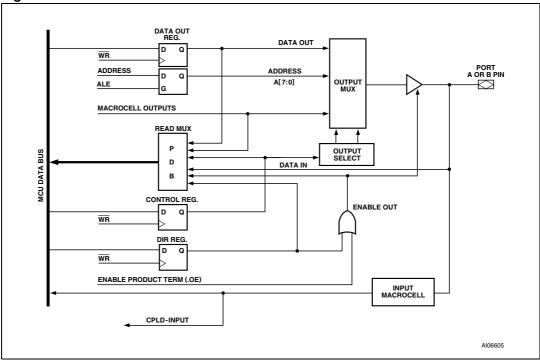

Figure 61. General I/O port architecture

The Port pin's tri-state output driver enable is controlled by a two input OR gate whose inputs come from the CPLD AND Array enable product term and the Direction Register. If the enable product term of any of the Array outputs are not defined and that port pin is not defined as a CPLD output in the PSDsoft, then the Direction Register has sole control of the buffer that drives the port pin.

The contents of these registers can be altered by the MCU. The Port Data Buffer (PDB) feedback path allows the MCU to check the contents of the registers.

Ports A, B, and C have embedded Input Macrocells (IMC). The Input Macrocells (IMC) can be configured as latches, registers, or direct inputs to the PLDs. The latches and registers are clocked by Address Strobe (ALE) or a product term from the PLD AND Array. The outputs from the Input Macrocells (IMC) drive the PLD input bus and can be read by the MCU. See *Figure 60*.

# 24.2 Port operating modes

The I/O Ports have several modes of operation. Some modes can be defined using PSDsoft, some by the MCU writing to the Control Registers in CSIOP space, and some by both. The modes that can only be defined using PSDsoft must be programmed into the device and cannot be changed unless the device is reprogrammed. The modes that can be changed by the MCU can be done so dynamically at run-time. The PLD I/O, Data Port, Address Input, and Peripheral I/O modes are the only modes that must be defined before programming the device. All other modes can be changed by the MCU at run-time. See Application Note *AN1171* for more detail.

*Table 93* summarizes which modes are available on each port. *Table 96* shows how and where the different modes are configured. Each of the port operating modes are described in the following sections.

## 24.8 Port configuration registers (PCR)

Each Port has a set of Port Configuration Registers (PCR) used for configuration. The contents of the registers can be accessed by the MCU through normal READ/WRITE bus cycles at the addresses given in *Table 84*. The addresses in *Table 84* are the offsets in hexadecimal from the base of the CSIOP register.

The pins of a port are individually configurable and each bit in the register controls its respective pin. For example, Bit 0 in a register refers to Bit 0 of its port. The three Port Configuration Registers (PCR), shown in *Table 96*, are used for setting the Port configurations. The default Power-up state for each register in *Table 96* is 00h.

#### 24.8.1 Control register

Any bit reset to '0' in the Control Register sets the corresponding port pin to MCU I/O mode, and a '1' sets it to Address Out mode. The default mode is MCU I/O. Only Ports A and B have an associated Control Register.

#### 24.8.2 Direction register

The Direction Register, in conjunction with the output enable (except for Port D), controls the direction of data flow in the I/O Ports. Any bit set to '1' in the Direction Register causes the corresponding pin to be an output, and any bit set to '0' causes it to be an input. The default mode for all port pins is input.

*Figure 63* and *Figure 64* show the Port Architecture diagrams for Ports A/B and C, respectively. The direction of data flow for Ports A, B, and C are controlled not only by the direction register, but also by the output enable product term from the PLD AND Array. If the output enable product term is not active, the Direction Register has sole control of a given pin's direction.

An example of a configuration for a Port with the three least significant bits set to output and the remainder set to input is shown in *Table 99*. Since Port D only contains two pins (shown in *Figure 66*), the Direction Register for Port D has only two bits active.

#### 24.8.3 Drive Select register

The Drive Select Register configures the pin driver as Open Drain or CMOS for some port pins, and controls the slew rate for the other port pins. An external pull-up resistor should be used for pins configured as Open Drain.

A pin can be configured as Open Drain if its corresponding bit in the Drive Select Register is set to a '1.' The default pin drive is CMOS.

Note: The slew rate is a measurement of the rise and fall times of an output. A higher slew rate means a faster output response and may create more electrical noise. A pin operates in a high slew rate when the corresponding bit in the Drive Register is set to '1.' The default rate is slow slew.

*Table 100* shows the Drive Register for Ports A, B, C, and D. It summarizes which pins can be configured as Open Drain outputs and which pins the slew rate can be set for.

# 24.10 Ports A and B – functionality and structure

Ports A and B have similar functionality and structure, as shown in *Figure 63*. The two ports can be configured to perform one or more of the following functions:

- MCU I/O mode

- CPLD Output Macrocells McellAB7-McellAB0 can be connected to Port A or Port B. McellBC7-McellBC0 can be connected to Port B or Port C.

- CPLD Input Via the Input Macrocells (IMC).

- Latched Address output Provide latched address output as per Table 95.

- Open Drain/Slew Rate pins PA3-PA0 and PB3-PB0 can be configured to fast slew rate, pins PA7-PA4 and PB7-PB4 can be configured to Open Drain mode.

- Peripheral mode Port A only (80-pin package)

#### Figure 63. Port A and Port B structure

# 24.11 Port C – functionality and structure

Port C can be configured to perform one or more of the following functions (see *Figure 64*):

- MCU I/O mode

- CPLD Output McellBC7-McellBC0 outputs can be connected to Port B or Port C.

- CPLD Input via the Input Macrocells (IMC)

- In-System Programming (ISP) JTAG pins (TMS, TCK, TDI, TDO) are dedicated pins for device programming. (See Section 27: Programming in-circuit using the JTAG serial interface, for more information on JTAG programming.)

- Open Drain Port C pins can be configured in Open Drain mode

Port C does not support Address Out mode, and therefore no Control Register is required.

# 27 Programming in-circuit using the JTAG serial interface

The JTAG Serial Interface pins (TMS, TCK, TDI, and TDO) are dedicated pins on Port C (see *Table 107*). All memory blocks (primary and secondary Flash memory), PLD logic, and PSD module Configuration Register Bits may be programmed through the JTAG Serial Interface block. A blank device can be mounted on a printed circuit board and programmed using JTAG.

The standard JTAG signals (IEEE 1149.1) are TMS, TCK, TDI, and TDO. Two additional signals, TSTAT and TERR, are optional JTAG extensions used to speed up Program and Erase cycles.

By default, on a blank device (as shipped from the factory or after erasure), four pins on Port *C* are the basic JTAG signals TMS, TCK, TDI, and TDO.

# 27.1 Standard JTAG Signals

At power-up, the standard JTAG pins are inputs, waiting for a JTAG serial command from an external JTAG controller device (such as FlashLINK or Automated Test Equipment). When the enabling command is received, TDO becomes an output and the JTAG channel is fully functional. The same command that enables the JTAG channel may optionally enable the two additional JTAG signals, TSTAT and TERR.

The RESET input to the uPS3200 should be active during JTAG programming. The active RESET puts the MCU module into RESET mode while the PSD module is being programmed. See Application Note AN1153 for more details on JTAG In-System Programming (ISP).

UPSD325xx devices support JTAG In-System-Configuration (ISC) commands, but not Boundary Scan. The PSDsoft Express software tool and FlashLINK JTAG programming cable implement the JTAG In-System-Configuration (ISC) commands.

| Port C Pin | JTAG Signals | Description           |

|------------|--------------|-----------------------|

| PC0        | TMS          | Mode Select           |

| PC1        | ТСК          | Clock                 |

| PC3        | TSTAT        | Status (optional)     |

| PC4        | TERR         | Error Flag (optional) |

| PC5        | TDI          | Serial Data In        |

| PC6        | TDO          | Serial Data Out       |

# 27.2 JTAG extensions

TSTAT and TERR are two JTAG extension signals enabled by an "ISC\_ENABLE" command received over the four standard JTAG signals (TMS, TCK, TDI, and TDO). They are used to speed Program and Erase cycles by indicating status on uPDS signals instead of having to

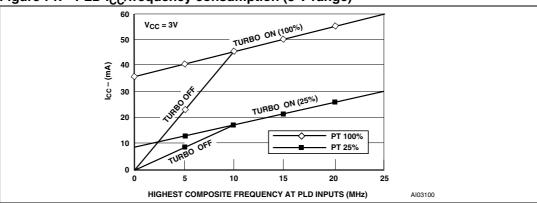

#### Figure 71. PLD I<sub>CC</sub>/frequency consumption (3 V range)

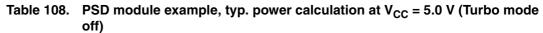

|               | Conditions                 |                                       |  |  |  |  |  |  |

|---------------|----------------------------|---------------------------------------|--|--|--|--|--|--|

|               | MCU clock frequency        | = 12 MHz                              |  |  |  |  |  |  |

| Highest Comp  | oosite PLD input frequency |                                       |  |  |  |  |  |  |

|               | (Freq PLD)                 | = 8 MHz                               |  |  |  |  |  |  |

| MCU ALE free  | quency (Freq ALE)          | = 2 MHz                               |  |  |  |  |  |  |

|               | % Flash memory access      | = 80%                                 |  |  |  |  |  |  |

|               | % SRAM access              | = 15%                                 |  |  |  |  |  |  |

|               | % I/O access               | = 5% (no additional power above base) |  |  |  |  |  |  |

| Operational m | odes                       |                                       |  |  |  |  |  |  |

|               | % Normal                   | = 40%                                 |  |  |  |  |  |  |

|               | % Power-down mode          | = 60%                                 |  |  |  |  |  |  |

| Number of pro | oduct terms used           |                                       |  |  |  |  |  |  |

|               | (from fitter report)       | = 45 PT                               |  |  |  |  |  |  |

|               | % of total product terms   | = 45/182 = 24.7%                      |  |  |  |  |  |  |

|               | Turbo mode                 | = Off                                 |  |  |  |  |  |  |

| Symbol                                     | Param                          | neter           | Test conditions (in addition to those in <i>Table 113</i> )            | Min. | Тур. | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Unit                 |

|--------------------------------------------|--------------------------------|-----------------|------------------------------------------------------------------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| I <sub>FR</sub>                            | XTAL feedbac<br>current (XTAL1 |                 | XTAL1 = V <sub>CC</sub><br>XTAL2 = V <sub>SS</sub>                     | -20  |      | -50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | μΑ                   |

| ILI                                        | Input leakage current          |                 | $V_{SS} < V_{IN} < V_{CC}$                                             | -1   |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | μA                   |

| I <sub>LO</sub>                            | Output leakag                  | e current       | $0.45 < V_{OUT} < V_{CC}$                                              | -10  |      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | μA                   |

| I <sub>PD</sub> <sup>(1)</sup>             | Power-down m                   | ode             | V <sub>CC</sub> = 5.5 V<br>LVD logic disabled                          |      |      | 250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | μA                   |

|                                            |                                |                 | LVD logic enabled                                                      |      |      | -50       μA         1       μA         10       μA         250       μA         380       μA         30       mA         10       mA         380       μA         30       mA         10       mA         30       mA         10       mA         30       mA         20       mA         62       mA         30       mA         700       μA/PT <sup>(3)</sup> 700       mA         0       mA         0       mA         0       mA         330       mA         330       mA         0       mA         330       mA         0       mA | μA                   |

|                                            | Active (12 MHz                 | z)              | V <sub>CC</sub> = 5 V                                                  |      | 20   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                   |

| I <sub>CC_CPU</sub><br>(2,3,6)             | Idle (12 MHz)                  |                 | $v_{CC} = 5 v$                                                         |      | 8    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                   |

|                                            | Active (24 MHz)                |                 |                                                                        |      | 30   | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                   |

|                                            | Idle (24 MHz)                  |                 | $V_{\rm CC} = 5 V$                                                     |      | 15   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                   |

|                                            | Active (40 MHz)                |                 |                                                                        |      | 40   | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                   |

|                                            | Idle (40 MHz)                  |                 | $V_{CC} = 5 V$                                                         |      | 20   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                   |

|                                            |                                | PLD Only        | $\begin{array}{l} PLD\_TURBO = Off, \\ f = 0 \; MHz^{(4)} \end{array}$ |      | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | μΑ/ΡΤ <sup>(5)</sup> |

| ICC PSD                                    | Operating                      |                 | PLD_TURBO = On,<br>f = 0 MHz                                           |      | 400  | 700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | µA/PT                |

| I <sub>CC_PSD</sub><br>(DC) <sup>(6)</sup> | supply current                 | Flash<br>memory | During Flash memory<br>WRITE/Erase Only                                |      | 15   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mA                   |

|                                            |                                | memory          | Read-only, f = 0 MHz                                                   |      | 0    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mA                   |

|                                            |                                | SRAM            | f = 0 MHz                                                              |      | 0    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mA                   |

|                                            | PLD AC Base                    |                 |                                                                        |      | No   | ote 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| I <sub>CC_PSD</sub><br>(AC) <sup>(6)</sup> | Flash memory                   | AC adder        |                                                                        |      | 2.5  | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | mA/MHz               |

|                                            | SRAM AC add                    | er              |                                                                        |      | 1.5  | 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | mA/MHz               |

Table 118. DC characteristics (5 V devices) (continued)

I<sub>PD</sub> (Power-down mode) is measured with: XTAL1=V<sub>SS</sub>; XTAL2=not connected; RESET=V<sub>CC</sub>; Port 0 =V<sub>CC</sub>; all other pins are disconnected. PLD not in Turbo mode.

I<sub>CC\_CPU</sub> (active mode) is measured with: <u>XTAL1</u> driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub>+0.5 V, V<sub>IH</sub> = Vcc - 0.5 V, XTAL2 = not connected; <u>RESET=V<sub>SS</sub></u>; Port 0=V<sub>CC</sub>; all other pins are disconnected. I<sub>CC</sub> would be slightly higher if a crystal oscillator is used (approximately 1mA).

- I<sub>CC\_CPU</sub> (Idle mode) is measured with: XTAL1 driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub>+0.5 V, V<sub>IH</sub> = V<sub>CC</sub>- 0.5 V, XTAL2 = not connected; Port 0 = V<sub>CC</sub>;

- 4.  $\overline{\text{RESET}}=V_{CC}$ ; all other pins are disconnected.

- 5. PLD is in non-Turbo mode and none of the inputs are switching.

- 6. See *Figure 70* for the PLD current calculation.

- 7. I/O current = 0 mA, all I/O pins are disconnected.

| Symbol             | Parameter <sup>(1)</sup> | 24 MHz ( | oscillator | Variable osc<br>= 8 to 2 | Unit                  |    |

|--------------------|--------------------------|----------|------------|--------------------------|-----------------------|----|

|                    |                          | Min.     | Max.       | Min.                     | Max.                  | 1  |

| t <sub>RLRH</sub>  | Oscillator period        |          |            | 41.7                     | 125                   | ns |

| t <sub>WLWH</sub>  | High time                |          |            | 12                       | $t_{CLCL} - t_{CLCX}$ | ns |

| t <sub>LLAX2</sub> | Low time                 |          |            | 12                       | $t_{CLCL} - t_{CLCX}$ | ns |

| t <sub>RHDX</sub>  | Rise time                |          |            |                          | 12                    | ns |

| t <sub>RHDX</sub>  | Fall time                |          |            |                          | 12                    | ns |

Table 123. External clock drive (with the 3 V MCU module)

Conditions (in addition to those in *Table 114*, V<sub>CC</sub> = 3.0 to 3.6 V): V<sub>SS</sub> = 0 V; C<sub>L</sub> for Port 0, ALE and PSEN output is 100 pF, for 5 V devices, and 50 pF for 3 V devices; C<sub>L</sub> for other outputs is 80 pF, for 5 V devices, and 50 pF for 3 V devices)

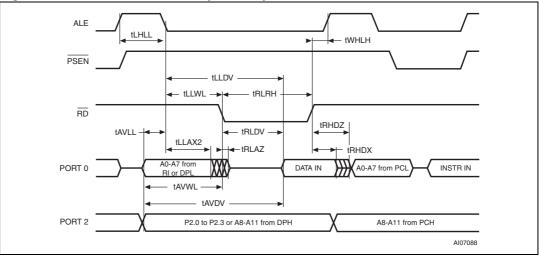

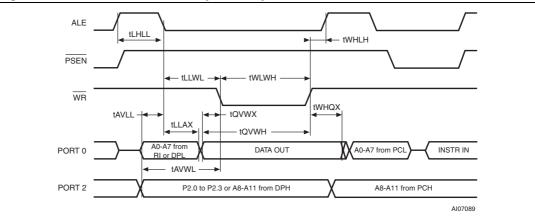

Figure 74. External data memory Read cycle

Figure 75. External data memory Write cycle

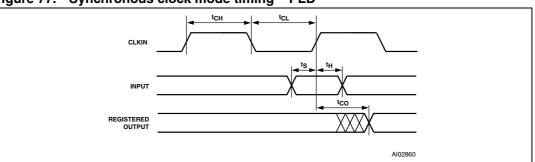

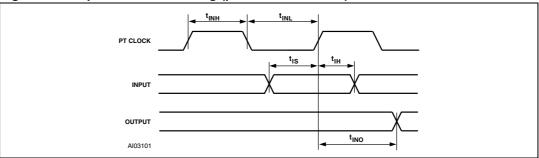

#### Figure 77. Synchronous clock mode timing – PLD

| Symbol           | Parameter                                               | Conditions                              | Min. | Max. | PT<br>Aloc | Turbo<br>Off | Slew<br>rate <sup>(1)</sup> | Unit |

|------------------|---------------------------------------------------------|-----------------------------------------|------|------|------------|--------------|-----------------------------|------|

|                  | Maximum frequency<br>external feedback                  | 1/(t <sub>S</sub> +t <sub>CO</sub> )    |      | 40.0 |            |              |                             | MHz  |

| f <sub>MAX</sub> | Maximum frequency internal feedback (f <sub>CNT</sub> ) | 1/(t <sub>S</sub> +t <sub>CO</sub> -10) |      | 66.6 |            |              |                             | MHz  |

|                  | Maximum frequency pipelined data                        | 1/(t <sub>CH</sub> +t <sub>CL</sub> )   |      | 83.3 |            |              |                             | MHz  |

| t <sub>S</sub>   | Input setup time                                        |                                         | 12   |      | + 2        | + 10         |                             | ns   |

| t <sub>H</sub>   | Input hold time                                         |                                         | 0    |      |            |              |                             | ns   |

| t <sub>CH</sub>  | Clock high time                                         | Clock input                             | 6    |      |            |              |                             | ns   |

| t <sub>CL</sub>  | Clock low time                                          | Clock input                             | 6    |      |            |              |                             | ns   |

| t <sub>CO</sub>  | Clock to output delay                                   | Clock input                             |      | 13   |            |              | - 2                         | ns   |

| t <sub>ARD</sub> | CPLD array delay                                        | Any macrocell                           |      | 11   | + 2        |              |                             | ns   |

| t <sub>MIN</sub> | Minimum clock period <sup>(2)</sup>                     | t <sub>CH</sub> +t <sub>CL</sub>        | 12   |      |            |              |                             | ns   |

1. Fast Slew Rate output available on PA3-PA0, PB3-PB0, and PD2-PD1. Decrement times by given amount.

2. CLKIN (PD1)  $t_{CLCL} = t_{CH} + t_{CL}$ .

| Symbol           | Parameter                                                  | Conditions                            | Min. | Max. | PT<br>aloc | Turbo<br>off | Slew<br>rate <sup>(1)</sup> | Unit |

|------------------|------------------------------------------------------------|---------------------------------------|------|------|------------|--------------|-----------------------------|------|

| f <sub>MAX</sub> | Maximum frequency<br>external feedback                     | $1/(t_S+t_{CO})$                      |      | 22.2 |            |              |                             | MHz  |

|                  | Maximum frequency<br>internal feedback (f <sub>CNT</sub> ) | $1/(t_{S}+t_{CO}-10)$                 |      | 28.5 |            |              |                             | MHz  |

|                  | Maximum frequency pipelined data                           | 1/(t <sub>CH</sub> +t <sub>CL</sub> ) |      | 40.0 |            |              |                             | MHz  |

| t <sub>S</sub>   | Input setup time                                           |                                       | 20   |      | + 4        | + 20         |                             | ns   |

| t <sub>H</sub>   | Input hold time                                            |                                       | 0    |      |            |              |                             | ns   |

| t <sub>CH</sub>  | Clock high time                                            | Clock input                           | 15   |      |            |              |                             | ns   |

| t <sub>CL</sub>  | Clock low time                                             | Clock input                           | 10   |      |            |              |                             | ns   |

| t <sub>CO</sub>  | Clock to output delay                                      | Clock input                           |      | 25   |            |              | - 6                         | ns   |

| t <sub>ARD</sub> | CPLD array delay                                           | Any<br>macrocell                      |      | 25   | + 4        |              |                             | ns   |

| t <sub>MIN</sub> | Minimum clock period <sup>(2)</sup>                        | t <sub>CH</sub> +t <sub>CL</sub>      | 25   |      |            |              |                             | ns   |

Table 130. CPLD macrocell synchronous clock mode timing (3 V devices)

1. Fast Slew Rate output available on PA3-PA0, PB3-PB0, and PD2-PD1. Decrement times by given amount.

2. CLKIN (PD1)  $t_{CLCL} = t_{CH} + t_{CL}$ .

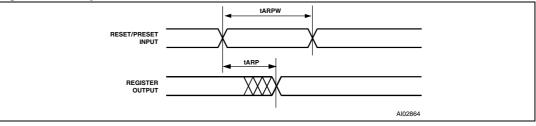

#### Figure 78. Asynchronous Reset / Preset

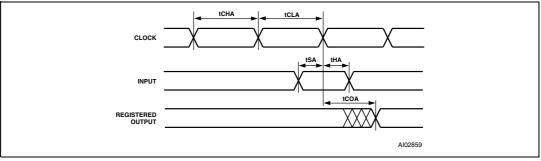

#### Figure 79. Asynchronous clock mode timing (product term clock)

#### Figure 80. Input macrocell timing (product term clock)

#### Table 133. Input macrocell timing (5 V devices)

| Symbol           | Parameter                        | Conditions | Min. | Max. | PT<br>aloc | Turbo<br>Off | Unit |

|------------------|----------------------------------|------------|------|------|------------|--------------|------|

| t <sub>IS</sub>  | Input setup time                 | (Note 1)   | 0    |      |            |              | ns   |

| t <sub>IH</sub>  | Input hold time                  | (Note 1)   | 15   |      |            | + 10         | ns   |

| t <sub>INH</sub> | NIB input high time              | (Note 1)   | 9    |      |            |              | ns   |

| t <sub>INL</sub> | NIB input low time               | (Note 1)   | 9    |      |            |              | ns   |

| t <sub>INO</sub> | NIB input to combinatorial delay | (Note 1)   |      | 34   | + 2        | + 10         | ns   |

1. Inputs from Port A, B, and C relative to register/ latch clock from the PLD. ALE/AS latch timings refer to  $t_{AVLX}$  and  $t_{LXAX}$ .

| Table 134. | Input macrocell | timing (3 V | devices) |

|------------|-----------------|-------------|----------|

|------------|-----------------|-------------|----------|

| Symbol           | Parameter                        | Conditions | Min. | Max. | PT<br>aloc | Turbo<br>Off | Unit |

|------------------|----------------------------------|------------|------|------|------------|--------------|------|

| t <sub>IS</sub>  | Input setup time                 | (Note 1)   | 0    |      |            |              | ns   |

| t <sub>IH</sub>  | Input hold time                  | (Note 1)   | 25   |      |            | + 20         | ns   |

| t <sub>INH</sub> | NIB input high time              | (Note 1)   | 12   |      |            |              | ns   |

| t <sub>INL</sub> | NIB input low time               | (Note 1)   | 12   |      |            |              | ns   |

| t <sub>INO</sub> | NIB input to combinatorial delay | (Note 1)   |      | 46   | + 4        | + 20         | ns   |

Inputs from Port A, B, and C relative to register/latch clock from the PLD. ALE latch timings refer to t<sub>AVLX</sub> and t<sub>LXAX</sub>.

| Symbol             | Parameter                                                         | Min.    | Тур. | Max. | Unit   |

|--------------------|-------------------------------------------------------------------|---------|------|------|--------|

|                    | Flash Program                                                     |         | 8.5  |      | S      |

|                    | Flash Bulk Erase <sup>(1)</sup> (pre-programmed)                  |         | 3    | 30   | S      |

|                    | Flash Bulk Erase (not pre-programmed)                             |         | 5    |      | S      |

| t <sub>WHQV3</sub> | Sector Erase (pre-programmed)                                     |         | 1    | 30   | S      |

| t <sub>WHQV2</sub> | Sector Erase (not pre-programmed)                                 |         | 2.2  |      | S      |

| t <sub>WHQV1</sub> | Byte Program                                                      |         | 14   | 150  | μs     |

|                    | Program / Erase Cycles (per Sector)                               | 100,000 |      |      | cycles |

| t <sub>WHWLO</sub> | Sector Erase Time-Out                                             |         | 100  |      | μs     |

| t <sub>Q7VQV</sub> | DQ7 Valid to Output (DQ7-DQ0) Valid (Data Polling) <sup>(2)</sup> |         |      | 30   | ns     |

1. Programmed to all zero before erase.

2. The polling status, DQ7, is valid  $t_{Q7VQV}$  time units before the data byte, DQ0-DQ7, is valid for reading.

Table 136.

Program, Write and Erase times (3 V devices)

| Symbol             | Parameter                                                         | Min.    | Тур. | Max. | Unit   |

|--------------------|-------------------------------------------------------------------|---------|------|------|--------|

|                    | Flash Program                                                     |         | 8.5  |      | S      |

|                    | Flash Bulk Erase <sup>(1)</sup> (pre-programmed)                  |         | 3    | 30   | S      |

|                    | Flash Bulk Erase (not pre-programmed)                             |         | 5    |      | S      |

| t <sub>WHQV3</sub> | Sector Erase (pre-programmed)                                     |         | 1    | 30   | S      |

| t <sub>WHQV2</sub> | Sector Erase (not pre-programmed)                                 |         | 2.2  |      | S      |

| t <sub>WHQV1</sub> | Byte Program                                                      |         | 14   | 150  | μs     |

|                    | Program / Erase Cycles (per Sector)                               | 100,000 |      |      | cycles |

| t <sub>WHWLO</sub> | Sector Erase Time-Out                                             |         | 100  |      | μs     |

| t <sub>Q7VQV</sub> | DQ7 Valid to Output (DQ7-DQ0) Valid (Data Polling) <sup>(2)</sup> |         |      | 30   | ns     |

1. Programmed to all zero before erase.

2. The polling status, DQ7, is valid  $t_{Q7VQV}$  time units before the data byte, DQ0-DQ7, is valid for reading.